## Interfacing the DP8420A/21A/22A to the NS32008/016/C016/ 032/132

INTRODUCTION

This application note explains interfacing the DP8420A/21A/22A to the National Semiconductor 32C016. Two different designs are shown and explained. It is assumed the reader is familiar with the NS32C016 access cycles and the DP8420A/21A/22A modes of operation. This application note is written for the NS32C016, but is also valid for the NS32008/016/032/132.

## DESIGN DESCRIPTION

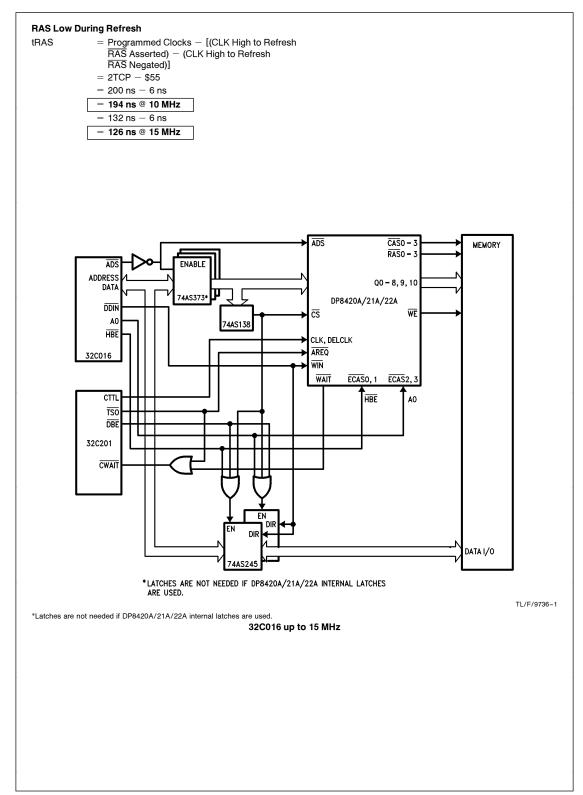

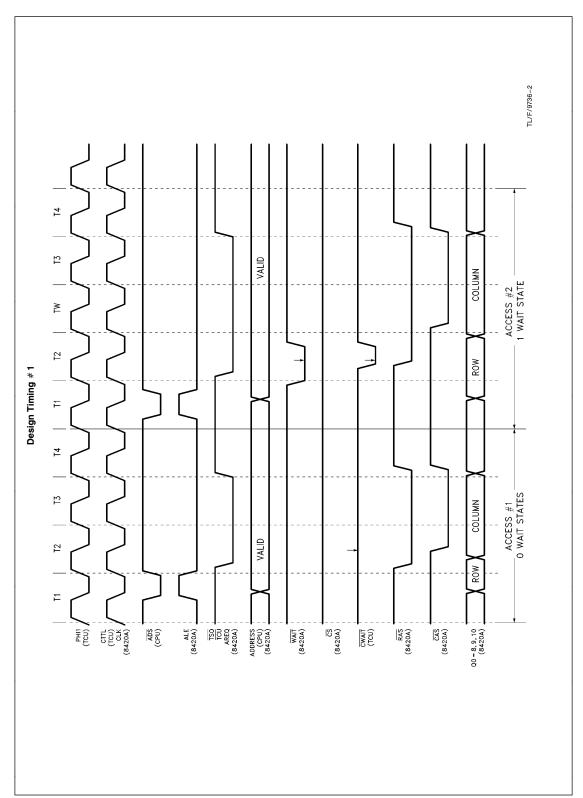

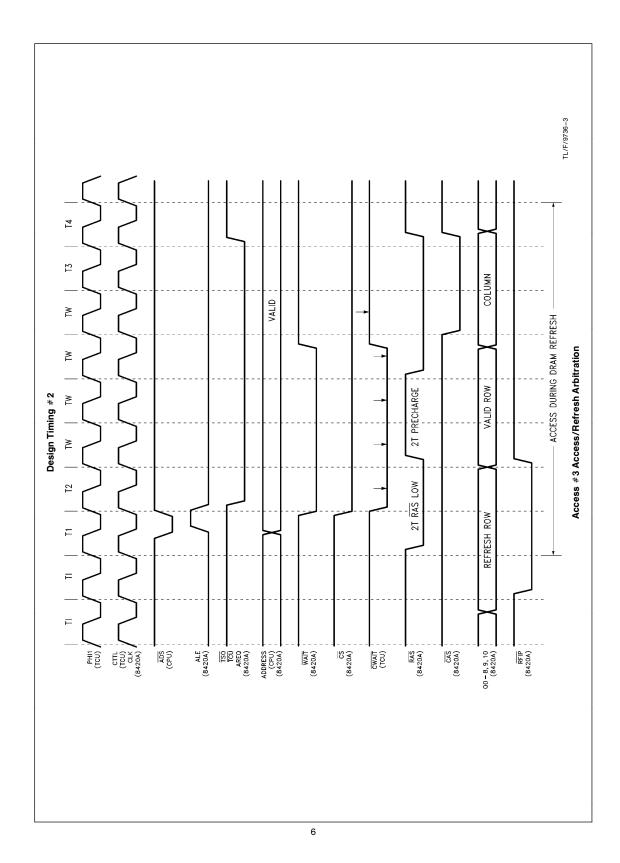

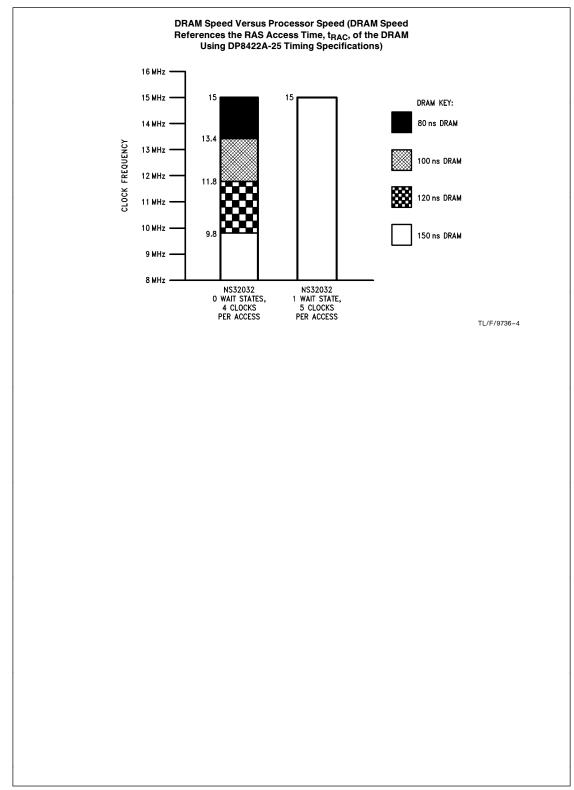

This design is a simple circuit to interface the DP8420A/21A/22A to the NS32C016 and up to 32 Mbytes of DRAM. The DP8420A/21A/22A is operated in mode 0. An access cycle begins when the 32C016 asserts the ADS signal and places a valid address on the bus. The ADS signal places a group of 74AS373 fall-through latches in fallthrough mode and ADS negated latches the address to guarantee the address is valid throughout the entire access. The ADS signal is inverted to produce the signal ALE to the DP8420A/21A/22A. On the next rising clock edge, after the ALE signal is asserted, the DP8420A/21A/22A will assert RAS. After guaranteeing the row address hold time, tRAH, the DP8420A/21A/22A will place the column address on the DRAM address bus, guarantee the column address setup time and assert  $\overline{CAS}$ . The transceivers are enabled by CS and AS. After tCAC, the DRAM will place the data on the bus. The DP8420A/21A/22A will also take care of refresh access arbitration and will hold off the access by asserting the CWAIT signal to the NS32C201 TCU.

Timing parameters are referenced to the numbers shown in the DP8420A/21A/22A data sheet. Times beginning with a "\$" refer to the DP8420A/21A/22A data sheet. Times beginning with a "#" refer to the NS32C016 data sheet. Times beginning with a "!" refer to the NS32C201 data sheet in the 1986 Series 32000® data book. Equations given allow the user the calculation timing based on his frequency and application. The clock to the DELCLK has been chosen to be a multiple of 2MHz. If you do not have a clock, which is a multiple of 2 MHz, the ADS to CAS time must be recalculated.

## DESIGN TIMING PARAMETERS

National Semiconductor Application Note 542 Joe Tate and Rusty Meier May 1989

nterfacing

the DP8420A/21A/22A to the

**JS32008/016/C016/032/132**

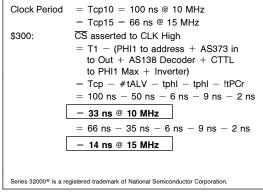

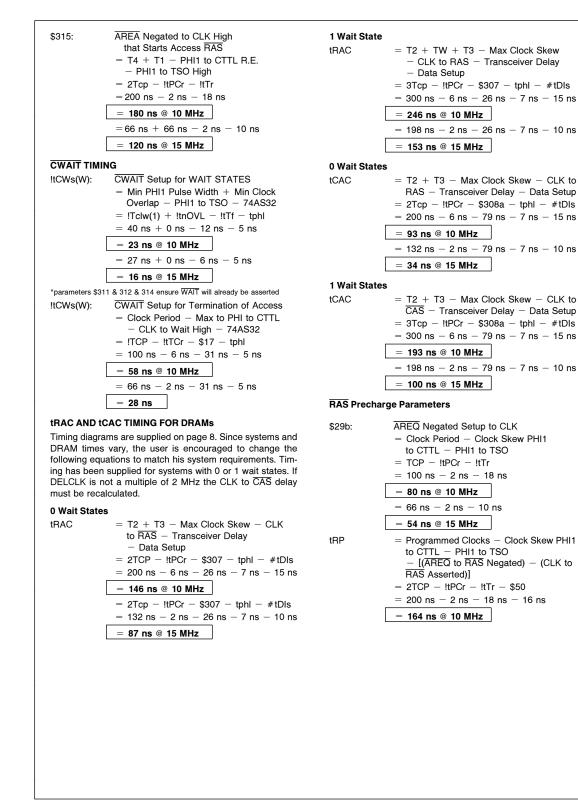

\$301b: ALE Setup to CLK High = T1 - Inverter Max - PHI1 to ADS - CTTL to PHI1 = Tcp - tplh - #tADSa - !tPCr = 100 ns - 5 ns - 35 ns - 2 ns = 55 ns @ 10 MHz = 66 ns - 5 ns - 26 ns - 2 ns = 33 ns @ 15 MHz \$302: ALE Pulse Width T1 - Inverter Max - PHI1 to ADS - CTTL to PHI1 = #tADSw = 30 ns @ 10 MHz = 25 ns @ 15 MHz \$303 & \$304: Address Setup to CLK = T1 - PHI1 to Address + AS373 in to out + CTTL to PHI1 Max) = Tcp - #tADSa - tphI - !tPCr = 100 ns - 50 ns - 6 ns - 2 ns= 42 ns @ 10 MHz = 66 ns - 35 ns - 6 ns - 2 ns = 23 ns @ 15 MHz \$309 ALE Negated Held from CLK High = Min  $\overline{CLK}$  to  $\overline{ADS}$  + Min Inverter CTTL to PHI1 Max = Min CLK to  $\overline{ADS}$  + 1 ns - 2 ns = Min CLK to ADS - 1 ns @ 10 MHz = Min CLK to  $\overline{ADS}$  – 1 ns @ 15 MHz \* no time is specified for CLK to ADS min.\* \$310: WIN Setup to CLK High to Guarantee CAS is Delayed = T1 + T2 - PHI1 to CTTL R.E. - DDIN Signal Valid - 74AS04 = 2Tcp - !tPCr - #tDDINv - tphl = 200 ns - 2 ns - 45 ns - 5 ns <u>= 148</u> @ 10 MHz = 66 ns + 66 ns - 2 ns - 38 ns - 5 ns = 87 ns @ 15 MHz

© 1995 National Semiconductor Corporation TL/F/9736

RRD-B30M115/Printed in U. S. A.

AN-542

|                                                                        | Design Programming Bits                                                       |                        |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------|

| Bits                                                                   | Description                                                                   | Value                  |

| R0, R1                                                                 | $\overline{RAS}$ Low During Refresh = 2T                                      | R0 = 0                 |

|                                                                        | RAS Precharge Time = 2T                                                       | R1 = 1                 |

| R2, R3                                                                 | WAIT Generation Mode during<br>Non-Burst Access                               | R2 = u<br>R3 = u       |

| R4, R5                                                                 | WAIT During Burst                                                             | R4 = 0                 |

| 114,113                                                                | WAIT During Durst                                                             | R5 = 0                 |

| R6                                                                     | ADD Wait States with WAITIN                                                   | R6 = x                 |

| R7                                                                     | WAIT Mode Selected                                                            | R7 = 0                 |

| R8                                                                     | Non-Interleaved Mode                                                          | R8 = 1                 |

| R9                                                                     | Staggered or all RAS Refresh                                                  | R9 = u                 |

| C0, C1, C2                                                             | Divisior for DELCLK                                                           | C0 = *                 |

|                                                                        | *Use a Multiple of 2 MHz External Clock                                       | C1 = *<br>C2 = *       |

| C3                                                                     | + 30 REFRESH                                                                  | C3 = *                 |

| C4, C5, C6                                                             | RAS, CAS Configuration Mode                                                   | C4 = **                |

| 01, 00, 00                                                             | **Choose an all CAS Mode,                                                     | C5 = **                |

|                                                                        | Tie a CAS to Each Nibble                                                      | C6 = **                |

| C7                                                                     | Select 0 ns Column Address Setup                                              | C7 = 1                 |

| C8                                                                     | Select 15 ns Row Address Hold                                                 | C8 = 1                 |

| C9                                                                     | CAS is Delayed During Writes                                                  | C9 = 1                 |

| B0                                                                     | Latches are Fall-Through                                                      | B0 = 1                 |

| B1                                                                     | Access Mode 0                                                                 | B1 = 0                 |

| ECAS0                                                                  | Non-Extend CAS Mode                                                           | $\overline{ECAS}0 = 0$ |

| u = user defined<br>R2 = 0 R3 = 1<br>R2 = 1 R3 = 0<br>R9 = 1<br>R9 = 1 | for 0 WAIT STATES<br>for 1 WAIT STATE<br>all RAS refresh<br>staggered refresh |                        |

|                                                                        | 4                                                                             |                        |

## LIFE SUPPORT POLICY

Lit. # 100542

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.  A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.