Project Navigator User Manual

981-0313-002

September 1994

### 090-0511-002

Data I/O has made every attempt to ensure that the information in this document is accurate and complete. Data I/O assumes no liability for errors, or for any incidental, consequential, indirect or special damages, including, without limitation, loss of use, loss or alteration of data, delays, or lost profits or savings, arising from the use of this document or the product which it accompanies.

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose without written permission from Data I/O.

Data I/O Corporation 10525 Willows Road N.E., P.O. Box 97046 Redmond, Washington 98073-9746 USA (206) 881-6444

Acknowledgments:

Data I/O is a registered trademark and Synario, Project Navigator, Device-Independent Library, and ABEL-HDL are trademarks of Data I/O Corporation.

Data I/O Corporation acknowledges the trademarks of other organizations for their respective products or services mentioned in this document.

© 1993-94 Data I/O Corporation All rights reserved

# **Table of Contents**

# Preface

| Customer Support                         |

|------------------------------------------|

| Technical Assistance                     |

| Sending a Fax                            |

| Using the BBS                            |

| Warranty Information                     |

| End User Registration and Address Change |

| Where to Look for Information ix         |

| Conventions                              |

# 1. Welcome to Synario

| -1 |

|----|

| -1 |

| -1 |

| -2 |

| -3 |

| -3 |

| -3 |

| -4 |

| -4 |

| -5 |

| -5 |

| -5 |

| -6 |

| -7 |

|    |

Synario Project Navigator User Manual

iii

| Synario and Windows               |

|-----------------------------------|

| Flexible Design Entry    1-9      |

| Selecting a Device                |

| Synario File Structure            |

| Learning More About Synario       |

| Exploring Synario's Documentation |

| Exploring Example Designs         |

# 2. Building a Design

| Introduction to Projects and Sources 2-    | 1 |

|--------------------------------------------|---|

| Opening and Saving Projects                | 3 |

| Opening a Project                          | 3 |

| Creating a New Project                     | 3 |

| Saving a Project                           | 4 |

| Naming Sources and Projects                | 4 |

| Creating Schematics and Behavioral Modules | 4 |

| Adding and Removing Source                 | 5 |

| Building a Hierarchical Project            | 5 |

| Understanding Hierarchy 2-                 | 5 |

| Building a Top-level ABEL-HDL Module       | 7 |

| Building a Top-level Schematic             | 7 |

| Building a Top-level VHDL Module           | 7 |

| Test Fixture Sources    2-3                | 8 |

| Building Other Project Sources             | 8 |

|                                            |   |

# 3. Editing Your Design

| Editing Behavioral Modules and Test Stimulus | 3-1 |

|----------------------------------------------|-----|

| Editing Schematics                           | 3-2 |

| Editing Other Sources                        | 3-2 |

| Converting JEDEC Files to ABEL-HDL           | 3-2 |

# 4. Processing Your Design

| <b>Running Processes</b> |  | • | • |  | • | • | • | • | • | • |  |  | • | • | • |  | • | • |  | • | • | • |  |  | • | • |  | • | 4- | -1 |  |

|--------------------------|--|---|---|--|---|---|---|---|---|---|--|--|---|---|---|--|---|---|--|---|---|---|--|--|---|---|--|---|----|----|--|

|--------------------------|--|---|---|--|---|---|---|---|---|---|--|--|---|---|---|--|---|---|--|---|---|---|--|--|---|---|--|---|----|----|--|

Synario Project Navigator User Manual

iv

V

| Vie | ewing Reports and Output Files              | 4-2 |

|-----|---------------------------------------------|-----|

| Pro | ocessing Steps                              | 4-3 |

|     | Displaying Processes                        | 4-3 |

| Wo  | orking with Processes                       | 4-3 |

|     | The Process Window                          | 4-3 |

|     | Changing How a Process Runs with Properties | 4-5 |

| Pro | ocessing Problems                           | 4-5 |

|     | Error Messages                              | 4-5 |

|     | Debugging Problems                          | 4-5 |

|     |                                             |     |

# 5. Designing for Device Independence

| Schematic Design Techniques              | . 5-1 |

|------------------------------------------|-------|

| VCC and GND Symbols                      | . 5-1 |

| Net Names and Symbol Instance Names      | . 5-1 |

| Create Bus and Net Names that are Unique | . 5-2 |

| I/O Pin Guidelines                       | . 5-2 |

| Other Design Considerations              | . 5-2 |

| Naming Restrictions                      | . 5-2 |

| Don't Rely On Case Sensitivity           | . 5-3 |

| Keep Projects Separate                   | . 5-3 |

| Use Text Documents                       | . 5-3 |

| Use a Schematic for the Top-level Source | . 5-3 |

| Test Fixture Include file                | . 5-3 |

| Designing for Device Independence        | . 5-4 |

| Device-independent Designs               | . 5-4 |

| Device-independent ABEL-HDL Modules      | . 5-4 |

| Device-independent Schematics            | . 5-6 |

|                                          |       |

# 6. Working with Devices

| When You Need to Select a Device          | 6-1 |

|-------------------------------------------|-----|

| Selecting a Device                        | 6-1 |

| Automatic Process Updating                | 6-2 |

| What Happens When You Select a Device?    | 6-2 |

| How Processes Change with a Device Change | 6-3 |

| How Properties Change with a Device Change                 | 6-3 |

|------------------------------------------------------------|-----|

| How Schematic Symbols Change with a Device Change $\ldots$ | 6-3 |

| Device Kits                                                | 6-5 |

| What Is a Device Kit?                                      | 6-5 |

| How Do You Use a Device Kit?                               | 6-5 |

| Accessing Device Kit Help Files                            | 6-5 |

# **A. Strategies and Properties**

| Properties                       |

|----------------------------------|

| Advanced Properties              |

| Default Properties               |

| Setting Properties               |

| Strategies                       |

| Creating New Strategies          |

| Changing the Default Strategy    |

| Deleting and Renaming Strategies |

| Saving Strategies                |

| Importing Strategies             |

# **B. Synario Configuration**

| Synario Project Navigator                                | B-1 |

|----------------------------------------------------------|-----|

| Text Editor and Report Viewer                            | B-1 |

| Schematic Editor, Symbol Editor, and Hierarchy Navigator | B-2 |

| Synario Project Navigator Configurable Menu              | B-2 |

# Preface

The Preface includes details about obtaining technical assistance and warranty service. The Preface also explains the Bulletin Board Service, where to find information, and typographic conventions used in the manuals.

### **Customer Support**

For technical assistance and warranty service, contact your local distributor. An updated list of Synario distributors is included in your Synario Design Entry package.

### **Technical Assistance**

You can contact your Synario distributor for technical assistance by calling, sending a fax, or electronic mail (e-mail). You can also access the Data I/O Bulletin Board Service (BBS) for product information.

To help us give you quick and accurate assistance, please provide the following information:

- Product version number

- Product serial number (if available)

- Detailed description of the problem you are experiencing

- Error messages (if any)

- Device manufacturer and part number (if device-related)

When you call, please be at your programmer or computer, have the product manual nearby, and be ready to provide the information listed above.

### Sending a Fax

Fax the information listed above with your name, phone number, and address to your Synario distributor listed on the Synario Distributors sheet.

Synario Project Navigator User Manual

vii

### Using the BBS

To reach Data I/O via the BBS, include your name, phone number, e-mail address, and the information listed above in a message, and send it to the BBS.

From the Data I/O Bulletin Board Service (BBS) you can obtain a wide range of information on Data I/O products, including current product descriptions, new revision information, technical support information, application notes, and other miscellaneous information.

Using the BBS, you can access device support information, request support for a particular device, and leave messages for the BBS system operator or other customers. The BBS also includes many downloadable DOS utilities.

Multiple lines are available, all supporting 1200/2400/9600/19200 baud, with U.S. Robotics Dual/HST V.32*bis*/V.42*bis* modems. The modems are set to 8 data bits, 1 stop bit, and no parity. Online help files provide more information about the BBS and its capabilities.

The BBS numbers in the United States are +1-206-882-1976 and +1-206-861-6959

### Warranty Information

Data I/O Corporation warrants this product against defects in materials and workmanship at the time of delivery and thereafter for a period of ninety (90) days.

The foregoing warranty and the manufacturers' warranties, if any, are in lieu of all other warranties, expressed, implied or arising under law, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

### End User Registration and Address Change

If the end user for this product or your address has changed since you registered the product, please notify your Synario distributer. This ensures that you receive information about product enhancements. Be sure to include the product serial number.

# Where to Look for Information

| If you want to learn about  | Look here                                         |

|-----------------------------|---------------------------------------------------|

| Installation                | Getting Started                                   |

| Menu operation              | Online Help                                       |

| Quick Start                 | Synario Online Tutorial<br>Online Help (F1)       |

| Design tutorials            | Getting Started                                   |

| Device-specific information | Device Kit manual<br>Device Kit Help              |

| ABEL-HDL syntax             | Online Help<br>Synario ABEL-HDL Reference         |

| Schematic commands          | Online Help<br>Synario Schematic Editor Reference |

| Simulation                  | Synario Simulator User Manual                     |

| Complex PLD designs         | PLD Device Kit<br><i>Getting Started</i>          |

| FPGA designs                | FPGA Device Kit<br>Getting Started                |

|                             |                                                   |

Synario Project Navigator User Manual

ix

# Conventions

The conventions used in this manual are described below:

This symbol indicates that the information is available in Synario's online help system.

### **Keys and Key Combinations**

An instruction for pressing two keys at once, such as  $^Z$  (Control and Z), is represented by two keys separated by a plus, such as Ctrl + Z.

A key combination like Esc, Ctrl + T means press and release Esc, then press Ctrl and T at the same time.

### Variable Input

Variable input is italicized and should be replaced with the requested information. For example, "enter copy *filename.hex*" means type "copy" just as you see it and replace *filename.hex* with the name of your file.

Also, some terms are italicized the first time they appear.

### **Optional Input**

Optional items of a command are shown in brackets.

[option1] [option2]...[optionn]

Items separated by a vertical bar (for example, OR | OR | ...) are mutually exclusive; that is, only one of the options listed can be specified.

#### **Displayed Text**

Text displayed on the screen appears in a typewriter-like typeface.

You will see this text displayed on the screen.

### Menu Items, Processes and Properties

Menu items are entered with the menu name, a colon, and the menu selection. For example, File: Exit means to select Exit from the File menu.

Processes and properties are entered as they appear on the screen.

|  |  | IJ |  |

|--|--|----|--|

|  |  |    |  |

|  |  |    |  |

|  |  |    |  |

# Chapter 1 Welcome to Synario

The Synario Universal FPGA Design System brings together several FPGA design tools into a single Windows application. Synario streamlines the device design process, freeing you to concentrate on the details of your design. This chapter explains what Synario is and how you approach device design with it.

If you'd like to start using Synario right away, *Getting Started* gives you information on installing and starting Synario, along with tutorials to get you started designing in Synario.

# What Is Synario?

### **Freedom in Design Entry**

Synario is a design entry system for FPGAs. Synario helps you create designs that are

- Composed of either schematics or HDL modules, so you can use the best features of both design entry methods.

- Hierarchical: you can create designs from the bottom up or top down.

- Device independent, so you can easily retarget your designs using Synario's generic behavioral language and generic schematic symbols.

### **Freedom in Design Processing**

Synario also gives you freedom in processing your design. You can

- Design with or without selecting a device, and change the device at any time. Synario updates the processes for the new device.

- Develop and reuse different strategies for processing designs.

- Simulate both the function and timing of your design.

- Simulate your design before choosing a device, and after implementing in a specific device.

- Run any process, with Synario automatically running prerequisite processing.

Synario Project Navigator User Manual

# **Designing with Synario**

Synario consists of many parts, all of which are accessed through the Synario Project Navigator. The Project Navigator helps you keep track of all of the parts of your design, and keeps track of the processing steps necessary to move the design from the conceptual stage through to implementation in an actual device.

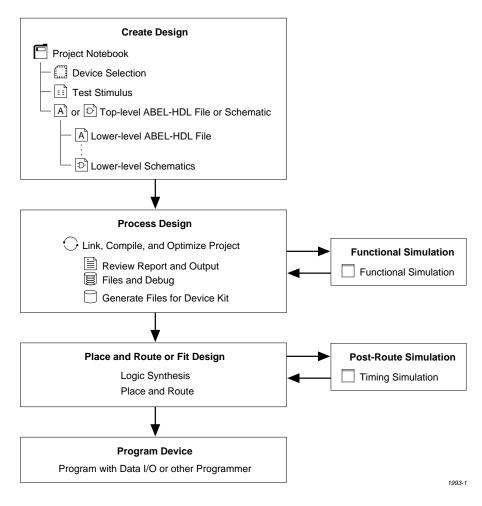

### *Figure 1-1* Synario Design Flow

### **Design Entry**

Synario supports two primary design entry methods: schematic and HDL. You can enter your design using either of these entry methods, or mix schematic and behavior entry in a single design.

In addition to the schematics and HDL portions of your design, Synario allows you to enter and keep track of other files not directly associated with the logic of your design. These files could include things like word processor documents (for your project specification), simulation test fixtures, or graphic state diagrams. These accessory files are kept for you in the Synario Project Notebook. Virtually any type of file can be imported into Synario and kept in the Project Notebook.

### **Functional Simulation**

Functional simulation is a way to verify that your design functions as intended before attempting to fit it into a device. The Synario Simulator is a full-featured simulator that accepts Verilog test stimulus and can display the simulation results in a variety of formats, including waveforms. For designs that include a top-level schematic, Synario also allows you to view simulation results right on the schematic, with actual circuit values displayed for each design input and output. This feature is called cross-probing.

### **Optimization and Device Fitting**

Synario's optional device kits allow you to target your design to a wide range of programmable devices. The devices supported by Synario Device Kits range from simple PAL and PROM devices to complex PLDs and FPGAs.

The optimization and fitting steps that Synario performs for you are determined by the type of device that you choose for implementation. There are two broad categories of devices, however, that can be described in terms of design flows. These categories are FPGAs and PLDs.

### **FPGA Design Flow**

FPGA and PLD device architectures require different design processing. An FPGA-type device differs from a PLD primarily in its need for a place-and-route step. Place-and-route software is typically provided by the FPGA vendors, so the processing steps performed in the Synario environment include the use of tools that may not be integrated directly into the Synario Project Navigator.

Synario Project Navigator User Manual

The FPGA design flow also differs from the PLD design flow in the types of entry formats supported. Because FPGA device fitters (and place-and-route software) operate on netlist format data, you can use both schematics and behavioral (HDL) design entry formats. When you enter a design that consists of a combination of schematics and HDL components, Synario converts all of the input forms to a netlist representation before the design is moved to the device-fitting phase. For most FPGA type devices, the individual project sources (the schematics and HDL files) are combined (merged) during device fitting.

### **PLD Design Flow**

The design flow for PLDs varies depending on the type of PLD chosen. For most types of PLDs, the design flow includes compilation of schematic or HDL sources into the OPEN-ABEL format, and a linking step for designs that are composed of multiple source files. Unlike FPGA design, multiple source files are combined (by linking) prior to the device-fitting process.

The PLD design flow also includes the capability for another form of simulation that is specific to PLDs: test vectors. You can use test vectors to test the function of the design before device-specific synthesis has been performed, and after the JEDEC file has been created. Use the Equation simulator to simulate the design after the equations are compiled and linked. Use the JEDEC simulator to simulate the program-and-test process. JEDEC simulation is supported in Synario for most devices that are programmed using a JEDEC format programmer download file. See your device kit documentation for support information. See the *Equation and JEDEC Simulators User Manual* for more information on the Equation and JEDEC Simulators.

### **Timing Simulation**

After your design is successfully implemented in a programmable device, you can verify the timing performance of the resulting circuit. Timing simulation allows you to verify that your design will operate correctly at the speeds that you will be using in your target system.

To accurately simulate your design with timing, Synario builds a timing model of the programmed device using timing data. Once you have this simulation model, you can use the Synario Simulator to check the operation of the design and timing-related circuit problems.

# What's in Synario

### **Projects and Sources**

Synario organizes a design by collecting all of the files into the Project Notebook. The Project Notebook lists the schematics and behavioral sources that create the logic of your design, testing files, and the device specification. The Project Notebook can also include any other design documents you want to keep with the design, such as design specifications, meeting notes or other supplementary files. Synario calls the notebook, documentation, and design pieces the *sources* of the project.

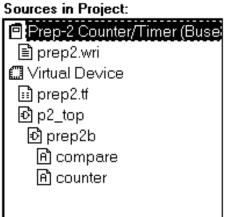

**Figure 1-2** Sources in Project Window

Each project is stored in its own directory to simplify archiving.

### Processes

A Synario project may comprise many pieces, each of which needs to be handled in a different way. You might have schematics that must be drawn with a schematic capture program, tested, and then translated into netlists or other formats. You might also have behavioral modules that need to be compiled, optimized, tested, and translated into another format, and test fixtures that are used without processing. The manner in which each piece of a Synario project is processed is also dependent on the device selected.

All of the steps required to take your design from specification into a device are called *processes* in Synario, and Synario remembers them all for you. When you select a source or change the target device, Synario automatically displays the steps to get the job done, freeing you to concentrate on your design. All you have to do is double-click on a process to run it. Synario's Auto-make capability automatically runs any prerequisite processes before running the process you select.

### *Figure 1-3* Processes for Current Source Window

Processes for Current Source: Navigate Hierarchy Functional Simulation Model Test Fixture Declarations

### **Customizing Processes**

Although Synario processes are usually already optimized for the device and source selected, there may be times when you want to change the way a source is processed. You can do this by changing the options, called *properties*, of a process in the Properties dialog box. You can save multiple sets of processing properties, each into their own *strategy*. For more information on Strategies and Properties, see Appendix A.

#### See Also

Specific processes and properties for each source and device are available in Synario's online help system.

### *Figure 1-4* Properties Dialog Box

| 🛥 Prope                                                                 | rties - (Na | rmal : ABEL] |                  | • |

|-------------------------------------------------------------------------|-------------|--------------|------------------|---|

| Properties:                                                             |             |              | Close            | ר |

| ✓ × None                                                                |             |              |                  |   |

| Generate Listing                                                        | List        | None         | Undo             | ٦ |

| Module Arguments                                                        | Text        |              |                  | ┥ |

| Compile Control Definitions                                             | Text        |              | <u>D</u> efaults |   |

| Adva Adva                                                               | nced        | -            |                  |   |

| Retain Redundant Logic                                                  | T/F         | False        | <u>H</u> elp     |   |

| ABEL Compatibility                                                      | List        | None         |                  | - |

| Double-click the selected item to<br>or use the combo box in the edit r |             |              | 8,               |   |

### **Simulating Your Design**

The Verilog Simulator is an option that provides functional simulation for all designs, and timing simulation for devices that support simulation. Simulation is a process for a test stimulus source.

Designs targeted to most types of PLDs use ABEL-HDL test vectors to simulate the JEDEC programmer load file.

### See Also

If you have the Verilog Simulator, see the *Verilog Simulator User Manual* for information on how to simulate your design.

For simulation support information, see your device kit documentation.

For Equation or JEDEC simulation, see the *Equation and JEDEC Simulators User Manual.*

### Synario Project Navigator User Manual

### **Synario and Windows**

Synario is a Windows program and uses standard Windows operations. If you are familiar with how a Windows application works, you already know a lot about how Synario works. Some of the ways you can use your Windows experience in Synario are described below:

### Drag and Drop from the File Manager

You can drag and drop any file from the Windows' File Manager into a Synario project as a project source. Any source that Synario does not recognize as part of a device design is stored under the Project Notebook as a document. This function is equivalent to choosing Import from the Source menu in the Synario Project Navigator.

### **Double-click Sources to Edit**

The files in a Synario project are shown in the Sources in Project window. The Sources window displays the Notebook name, device selected, and the other sources of the project. Double-click on the device selection to select a new device. Double-click on any source to run the appropriate program with the specified file loaded — the same way you can in the File Manager.

**Note:** Synario sets up a File Manager association for .syn during installation. You may need to set up file extension associations for other files. For instructions, see your Windows documentation.

**Note:** You may also need to enable Use File Associations from the Options: Environment dialog box.

### **Double-click Processes to Run Them**

The steps to process the source highlighted in the Sources window are shown in the Processes for Current Source window. Double-click on a process in the Processes window to run that process. Synario automatically runs any prerequisite processes to complete the process you select.

### **Double-click on Reports to View Them**

The reports generated by Synario processes are also listed in the Process window. You can double-click to view them, or highlight them and click the View button.

Synario Project Navigator User Manual

### Shift+Double-click to Force One Process

If you hold down the shift key while double-clicking on a process, it will force that process to run, even if it is up-to-date.

#### Ctrl+Double-click to Force All Processes

If you hold down the shift key while double-clicking on a process, it will force that process and all prerequisite processes to run, even if they are up-to-date.

#### Double-click in the File Manager to Start Synario

Double-click on a Synario project file (\*.syn) in the File Manager to start Synario with that project loaded.

#### **Press F1 for Help**

Synario comes with an extensive online help system. Press F1 to access context-sensitive help.

# **Flexible Design Entry**

To take advantage of Synario's ability to change devices, enter your design so that it does not require a particular device; this type of design is called device independent. Synario's Schematic Editor and HDL language both have device-independent features:

| Design Type | Device-independent Features                                                                                                                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Schematic   | Use the Synario Device-independent Library to enter your schematics. These symbols are supported by all FPGAs and are mapped to the device-specific symbols before place-and-route. See the <i>SCS Command Reference</i> for more information. |

| HDL         | Use ABEL-HDL's device-independent language features. See the <i>ABEL-HDL Reference</i> for more information.                                                                                                                                   |

|             | See the <i>VHDL User Manual</i> for more information on VHDL.                                                                                                                                                                                  |

Synario Project Navigator User Manual

# *Figure 1-5* Selecting a Device

| Choose Device                                                                                                                                                                |                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Device <u>K</u> it:<br>Generic Device<br>LCA 2000 FPGAs<br>LCA 3000 FPGAs<br>LCA 4000 FPGAs<br>XC 3000 FPGAs (Unified)<br>XC 4000 FPGAs (Unified)<br>XC 4000 FPGAs (Unified) | <u>O</u> K<br><u>C</u> ancel<br><u>H</u> elp |

| Virtual Device<br>Virtual Device                                                                                                                                             |                                              |

### **Selecting a Device**

When you do want to select a device, Synario allows you to become increasingly more specific about the device you want to use. You will need to select (target) a device to do device-specific design processing, such as logic synthesis and place-and-route.

Device-specific functions are provided through device kits. You should have received one or more device kits with your Synario package. Synario device kits are available for FPGAs, such as LCAs and MAX devices. There are also device kits for PLDs and complex PLDs.

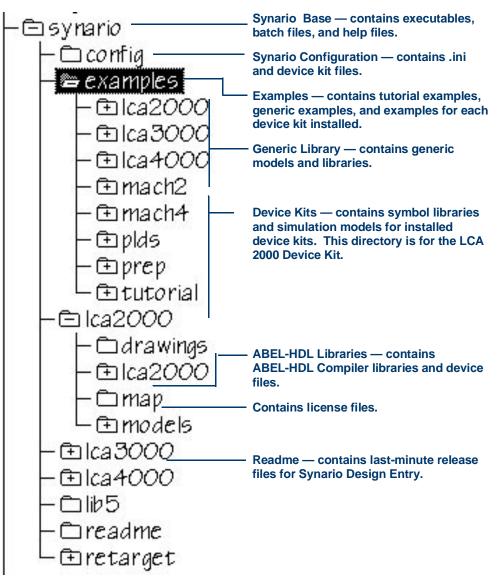

# **Synario File Structure**

The files installed by Synario Design Entry are shown below.

### Figure 1-6

Synario File Structure

Synario Project Navigator User Manual

# Learning More About Synario

### **Exploring Synario's Documentation**

The following table shows where to find things in the Synario documentation. Most information is also available in Synario's online help system.

| To Learn About                           | See                                            |

|------------------------------------------|------------------------------------------------|

| Design Entry Topics:                     |                                                |

| Device-independent                       | Chapter 5, "Designing for Device Independence" |

| designs                                  | ABEL-HDL Reference                             |

|                                          | SCS Reference                                  |

| Device-independent<br>Library            | SCS Reference                                  |

| Design Building Topics:                  |                                                |

| Creating, importing, and editing sources | Chapter 3, "Building Your Design"              |

| <b>Design Processing Topics</b> :        |                                                |

| Selecting a device                       | Chapter 6, "Working with Devices"              |

| Processing your design                   | Chapter 4, "Processing Your Design"            |

| Strategies and properties                | Appendix A, "Strategies and Properties"        |

|                                          |                                                |

### **Exploring Example Designs**

Synario comes with many example designs (called projects) that get you started creating your own designs. When you install a device kit, the installation program adds examples for the supported device.

### To load an example design:

Select Open Example from the Synario Project Navigator File menu.

*OR* Double-click the *filename*.syn file in the Windows File Manager.

This chapter introduces projects and sources, and gives instructions on how to build a design with them. For examples of building designs with Synario projects, see your *Getting Started* guide.

# Introduction to Projects and Sources

In Synario, a design that will be targeted to a device is referred to as a project. A project contains sources that

- Identify the project and list included sources

- Define the design's logic

- Define the target device

- Provide test stimulus to test the design

Projects are built from the following types of sources. The type of source is indicated by the icon to the left of the source name in the Source Window.

| Source                       |           | Icon Example |

|------------------------------|-----------|--------------|

| Project notebook             |           | hiermult.syn |

| Device family                | a         | lca.fdk      |

| ABEL-HDL logic description   | A         | hierabel.abl |

| Structural logic description | ð         | hierschm.sch |

| VHDL logic description       | $\square$ | hiervhdl.vhd |

| Verilog test fixtures        |           | hierstim.tf  |

Synario Project Navigator User Manual

\_

| Source                                                   |           | Icon Example         |

|----------------------------------------------------------|-----------|----------------------|

| VHDL test bench                                          | se l      | hiertb.vhd           |

| ABEL-HDL test vectors                                    | £         | hiertv.abv (or .abl) |

| Waveform stimulus                                        | Ð         | waves.wdl            |

| Undefined or incorrect source reference                  | 2         |                      |

| Schematic source that failed<br>Update Hierarchy process | ð         |                      |

| ABEL-HDL source that failed<br>Update Hierarchy process  | A         |                      |

| VHDL source that needs to be compiled                    | $\square$ |                      |

### See Also

### Projects

"Opening and Saving Projects" "Adding Source" "Adding Non-Synario Project Files"

# **Opening and Saving Projects**

### **Opening a Project**

To open an existing Synario project, select Open from the Synario File menu. Each Synario project is stored in its own directory. Example projects are installed in subdirectories under the Synario EXAMPLES directory.

- *OR* Double-click on a Synario project file, *filename*.syn in the Windows File Manager.

- OR Drag a Synario project file, *filename*.syn into Synario.

- *OR* Click on the Open Project button in the toolbar.

### **Creating a New Project**

### To create a new Synario project:

1. Select New from the File menu.

### OR

Click the New Project button D in the toolbar.

- 2. Select a directory for the project, or select the Create Directory button and enter a name for a new directory. All of the files in your project will be stored in this directory.

- 3. Enter a filename for the project file.

- 4. Double-click on the project notebook icon 🖻 in the Source window, and enter a title for the project. The project title can be as long as you like, but only the first 20 characters will show. The title can contain spaces and any other keyboard character except tabs and returns. The title is stored in the project file and is included in project output and report files created during processing.

**Hint:** To rename the project, double-click the project icon  $\square$  in the Source window.

*Note:* For some device kits, the project directory and project name should be the same.

### Saving a Project

### To save a project:

Select Save or Save As from the File menu. If you select Save As, Synario asks for a filename to save the project to.

*OR* Click on the Save button  $\blacksquare$  in the toolbar.

### What is Saved

Saving a project saves a project file (.syn extension) with the following information:

- The title of the project

- The sources in the project

- The strategy associated with each source (.sty extension)

Synario also tells the schematic and text editors to save when you save a project.

When you select Save As to save a project to another directory, Synario copies all of the project files to that directory.

## **Naming Sources and Projects**

Use the following guidelines when naming source files and projects:

- Avoid using ABEL-HDL, VHDL or Verilog keywords for module and signal names in any of your source files.

- Do not use any device-kit-specific macro functions to name a source.

### **Creating Schematics and Behavioral Modules**

The design description (logic) for a project is contained within the following types of source:

- Schematics

- ABEL-HDL

- VHDL

One source file in a project is the top-level source for the design. The top-level source defines the inputs and outputs that will be mapped into the device, and references the logic descriptions contained in lower-level sources. The referencing of another source is called "instantiation." Lower-level sources can also instantiate sources to build as many levels of logic as necessary to describe your design.

**Note:** If you build a project with a single source, that source is automatically the top-level source.

See Also

"Building a Hierarchical Project" "Selecting a Device"

### Adding and Removing Source

#### To add source to a project:

Select New from the Source menu, or click on the New button underneath the Sources in Project window.

- *OR* Select Import from the Source menu.

- OR Drag and drop a file from the Windows File Manager.

The new source is entered into the Source window in alphabetical order for each level of hierarchy following the project notebook and device entries.

### To remove source from a project:

- 1. Select (highlight) the source in the Source window.

- 2. Select Remove from the Source window.

Note: Removing a source from a project does not delete the underlying file.

### **Building a Hierarchical Project**

### **Understanding Hierarchy**

Hierarchical FPGA and PLD design consists of a top-level source that contains functional blocks linked to create the overall design. The functional blocks referenced in the top-level source are placeholders for lower-level logic descriptions, which may in turn contain functional blocks that reference even lower-level logic descriptions. The referencing of a logic description is called "instantiation."

Both top-level and lower-level source can be either schematics or behavioral modules (in ABEL-HDL).

**Note:** A source can be referenced ("instantiated") more than once. Also, a source can be both a lower-level and top-level source. For example, "compare" in Figure 2-1 could instantiate another file.

Synario Project Navigator User Manual

Figure 2-1 shows what a hierarchical design looks like in the Synario Sources in Project list.

*Note:* You can change to a "flat" hierarchy view (that shows only the top file) by removing the check on View: Hierarchy.

### Figure 2-1

The Sources in Project Window

| Sources in Project:         |

|-----------------------------|

| Prep-2 Counter/Timer (Buse) |

| 🖹 prep2.wri                 |

| 🖾 Virtual Device            |

| 🗈 prep2.tf                  |

| 🖻 p2_top                    |

| ๗ prep2b                    |

| A) compare                  |

| A counter                   |

|                             |

|                             |

| Prep-2 Counter Timer        | The Project Notebook, which keeps track of all of the files that make up your project.                                        |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Virtual Device              | The Device selected for the project (in this case, no device has been selected).                                              |

| prep2.tf                    | A test fixture used to simulate the design implemented into the device.                                                       |

| p2_top                      | The top-level source for the project, which instantiates the lower-level (indented) sources. In this case, it is a schematic. |

| prep2b, compare,<br>counter | Lower-level ABEL-HDL modules and schematic.                                                                                   |

**Note:** You cannot instantiate a top-level source from a source instantiated below that source. For example, you can't instantiate "top" from the "compare" source.

### Building a Top-level ABEL-HDL Module

In a top-level behavioral module in ABEL-HDL, you use the Interface and Functional\_block keywords to instantiate lower-level files. You can also use the Interface keyword in lower-level files to link to upper-level ABEL-HDL modules (not upper-level schematics).

The ABEL-HDL file **pwmdac.abl** demonstrates the use of the Functional\_block and Interface keywords in a top-level file. The file **counter.abl** demonstrates the use of the Interface keyword in a lower-level file.

#### See Also

"Interface (upper-level)," "Interface (lower-level)," and "Functional\_block" in the *ABEL-HDL Reference*

### **Building a Top-level Schematic**

In a top-level schematic (unless your design contains only one logic source), you use symbols to instantiate lower-level files. Select Add: New Symbol from the Schematic Editor menus to create a functional block symbol for a lowerlevel file.

If you are in a lower-level schematic, you can choose "This Block" in the "New Symbol" dialog box to automatically create a functional block symbol for the current schematic.

The Block Name is the name of the lower-level file, which can be another schematic or a behavioral module.

*Note:* Some device-specific tools require that you not use busses in top-level schematics.

#### See Also

SCS Reference

### Building a Top-level VHDL Module

In a top-level VHDL file, you use component declarations to instantiate lower-level files.

The **arith.vhd** project (a tutorial in the *VHDL User Manual*) demonstrates the use of the component declaration.

*Note:* Some device-specific tools require that you not use busses in top-level VHDL source.

See Also

VHDL User Manual

Synario Project Navigator User Manual

### **Test Fixture Sources**

If you create or import a test fixture file, Synario prompts you whether to associate the test fixture with the device source or HDL/Schematic source.

The project shown in Figure 2-1 includes two test fixtures (.tf extension). One associated with the device (time.tf) and one associated with the top-level source (func.tf).

You can double-click on a test fixture to edit it in the Text Editor.

### **Building Other Project Sources**

You might have sources other than schematic and ABEL-HDL modules. These sources might include simulation test fixtures, documentation files, or other files related to Windows applications.

In most cases, you can drag and drop these files into your Synario project as needed. Any sources that are not part of the design logic description or simulation test fixtures are displayed under the Project Notebook.

This chapter briefly explains the editors that come with Synario to help you start editing the sources that make up your logic design. More detailed information is provided in online help and the following manuals:

| To Edit               | Look Here                                                      |

|-----------------------|----------------------------------------------------------------|

| Behavioral Modules    | ABEL-HDL Reference                                             |

| Schematics            | SCS Reference                                                  |

| Verilog Test Stimulus | <i>Verilog Simulator User Manual</i> (if you have this option) |

| VHDL                  | VHDL User Manual (if you have this option)                     |

You can edit any of the sources that make up your project by double-clicking on them (if you have file associations set up in the Windows File Manager and have enabled "Use File Associations" in "Options: Environment").

In the editor for a source, you can press F1 or use the Help menus to access editor-specific help.

### **Editing Behavioral Modules and Test Stimulus**

The Synario Text Editor provides several macros and templates to help you enter and edit test stimulus and behavioral modules written in ABEL-HDL and VHDL. You can edit an ABEL-HDL, VHDL, or test stimulus source by double-clicking on it, or by selecting it in the source list and choosing Source: Open.

You can also use any ASCII editor to edit behavioral modules and test stimulus. You then import them into your Synario project using drag-and-drop from the Windows File Manager or using Source: Import.

### See Also

| ? |   |

|---|---|

| ( | Ì |

"Menus" for information on Synario Text Editor menus and using templates. *ABEL-HDL Language Reference* for information on ABEL-HDL *Verilog Simulator User Manual VHDL User Manual*

# **Editing Schematics**

Use the Synario Schematic Editor to edit schematic source. You can open the Schematic Editor on a schematic by double-clicking on the schematic name in the source list, or by selecting the source and choosing Source: Open.

See Also

The *SCS Reference* for information on creating schematics and on the Generic Library.

Your device kit documentation for device-specific symbol libraries and generic symbol to device symbol mapping charts.

# **Editing Other Sources**

Other sources can be edited by double-clicking if you associate their file extensions with appropriate editing applications in the Windows File Manager. See your application documentation for editing information.

**Note** You can associate text files with the Synario Text Editor by choosing File: Associate from the Windows File Manager. See your Windows documentation for more information on file association in the File Manager.

# **Converting JEDEC Files to ABEL-HDL**

If you have JEDEC files that you want to convert to ABEL-HDL files to use in a Synario project, you can use jed2ahdl in the Synario DOS window. You can bring up the Synario DOS window by pressing Ctrl+Alt+D.

The options for jed2ahdl are listed below:

```

jed2ahdl infile -o outfile -report mapfile

```

# Chapter 4 Processing Your Design

This chapter explains how to process a project, including

- Running Processes

- Viewing Reports and Output Files

- Understanding Processing Steps

- Summary of Processes for Sources and Projects

### See Also

Online help for Processes and Properties Online tutorial

Chapter 2, "Building a Design" Chapter 3, "Working with Sources" Device kit documentation Verilog Simulator User Manual Equation and JEDEC Simulators User Manual

# **Running Processes**

You can run a process with one of the following procedures:

#### **Double-click on a Process:**

- 1. Select the source you want to process. (To process the entire project, highlight the device.)

- 2. Double-click the end process you want. Synario automatically updates any intermediate steps necessary to complete the required process.

*Note: Shift+double-click forces one level to run; Ctrl+double-click forces all processes to run.*

### OR Use the Start or View Buttons:

- 1. Select the source you want to process. (To process the entire project, highlight the device.)

- 2. Select the process you want.

- 3. Click on the Start button to run the process; click on the View button to run the process and view the resulting file (for report and viewable output files).

### OR Use the Process Menu

- 1. Select the source you want to process. (To process the entire project, highlight the device.)

- 2. Select the process you want.

- 3. From the Process Menu (keyboard shortcut is Ctrl+P), select Start to run the process, or View to run the process and view the resulting file (for report and viewable output files). You can also select Force to run a process again that has already completed successfully.

See Also

"What Happens When You Select a Device?" in Chapter 6

### **Viewing Reports and Output Files**

### To view a report or output file:

- 1. Highlight the desired file.

- 2. Click on the View button or choose View from the Process menu.

- 3. When the process completes successfully, the File Viewer displays the file.

### To view the log for the last process:

Click on the Log button or select Log from the Process menu.

# **Processing Steps**

### **Displaying Processes**

Processes are associated with sources, so the processes displayed are only those processes for the highlighted source. Table 4-1 shows which source some common processes are associated with.

### Table 4-1

Source Associations for Processes

| Type of Process  | Source to Highlight |

|------------------|---------------------|

| Compiling        | Behavioral          |

| Simulation       | Test Fixtures       |

| Generate Netlist | Schematic           |

# **Working with Processes**

This section contains the following topics:

- The Process Window

- Changing How Processes Run with Properties

### **The Process Window**

Each step required to process a project and its source is referred to as a Process. The processes available for the project and each type of source are different and vary based on the device selected. When you select (highlight) the project name or one of the sources in the Source Window, the processes available are displayed in the Process Window.

### **Types of Processes**

The types of Processes available are shown below.

| Icon | Process Type                    |  |

|------|---------------------------------|--|

| o.   | Run batch program               |  |

|      | Run Windows program             |  |

|      | Create Report File and View it  |  |

| 8    | Create Viewable Output File     |  |

| 8    | Create Non-viewable Output File |  |

### To see the status of a Process:

Look to the left of the process type icon for the process status icons:

| Icon      | Means process completed                           |

|-----------|---------------------------------------------------|

| (No icon) | (Not started)                                     |

| 1         | Successfully (without errors or warnings)         |

| Å         | With warnings (subsequent processes can continue) |

| x         | With fatal errors (processing halts completely)   |

#### Changing How a Process Runs with Properties

You can change the way a process runs by changing the options (properties) of the process.

#### To change the properties for a process:

- 1. Select (highlight) the process in the Process window.

- 2. Click on the Properties button.

- *OR* Select Properties from the Process menu.

The Property Editor displays the available properties for the selected process.

1. Double-click on a property to edit it. Changes take effect immediately and are saved to the current strategy.

#### To change properties for a different process or source:

Without closing the Property Editor, select the desired source and process. The Property Editor automatically updates the properties.

See Also

Appendix A, "Strategies and Properties"

### **Processing Problems**

#### Error Messages

Explanations for error messages are available from online help by selecting Messages from the Problem Solving category on the help map. Explanations for Device Kit error messages are available in the help file shipped with the device kit.

#### **Debugging Problems**

If you are having problems with Synario programs running under syndos, you can debug them by running a DOS window with the syndos.pif file. To access this window, press Ctrl+Alt+D. This gives you a DOS window with the same environment. Type **exit** to quit.

Synario Project Navigator User Manual

4-5

# Designing for Device Independence

This chapter covers project design techniques and designing for device independence. This information on conventions for designing with Synario will help you produce designs that are

- Easier to debug

- Easy to move to other device families

- Compatible with Synario designs created by other Synario users

### **Schematic Design Techniques**

#### VCC and GND Symbols

The Synario Schematic Editor does not have VCC or GND symbols. Instead, you create connections to ground and VCC by naming the net "VCC" or "GND." Nets with those names are tied to the corresponding global signal. By creating a vertical net with the name "VCC" attached at the top, the VCC bar symbol appears. Likewise, by creating a vertical net with the name "GND" attached at the bottom, the ground symbol appears.

#### Net Names and Symbol Instance Names

During simulation, you may want to probe the design for certain nets or symbols. To improve post-synthesis debugging, you should name all of your intermediate nets with unique names, rather than having Synario provide automatic net names (which can be cryptic and difficult to sort out).

#### Create Bus and Net Names that are Unique

Bus names and net names, if identical, will "short out" in Verilog simulation because of the way Verilog breaks out bus signals. For example:

DATA[7:0]

and

DATA

will cross-connect during simulation and cause unpredictable errors. Avoid using buses and nets names that are identical.

#### I/O Pin Guidelines

- Place I/O Pins on Top-level Only Keep I/O symbols (and pin assignments) in the top level source only. This makes designs much easier to simulate and understand later, as all of the device I/O can be found in one place, the top level source.

- Avoid Using Ordered Buses on I/O pins for a top-level schematic, for example, data[7:0]. Because most fitters flatten buses, using ordered buses causes the Verilog test fixutre created for functional simulation to be unusable for post-route simulation.

- Use Alphanumeric Characters for Signal Names The first character should always be alphabetic.

- Use Global Net Names Vcc and GND only to tie unused inputs high or low.

- Do not end signal names with #\_ (for example 3\_).

### **Other Design Considerations**

#### Naming Restrictions

You cannot assign an ABEL-HDL module name or VHDL entity name that is longer than 8 characters to a sub-module you want to instantiate in a schematic. The matching symbol name is limited by DOS filename restrictions.

#### Don't Rely On Case Sensitivity

Names should not rely on case to provide uniqueness. For example, don't use "FRED" and "fred" in the same design. Some tools in the Synario environment are inherently case sensitive, though many are not case sensitive. Duplicate names with different cases may internally "short" together during some back-end process, resulting in an invalid programming file and/or incorrect simulation results. Some processes also modify the case of signals and names.

#### Keep Projects Separate

Keep projects separate in their own directories to make them easier to archive, easier to move, and easier for other engineers to work on.

#### **Use Text Documents**

Place design notes in separate text files associated with your project rather than documenting directly in the schematics and ABEL-HDL modules to make the logic easier to follow.

#### Use a Schematic for the Top-level Source

Using a schematic for the top-level souce allows you to take advantage of the design navigation and cross-probing features of the Hierarchy Navigator.

#### **Test Fixture Include file**

Use a Verilog `include statement to include the automatically-generated test fixture declarations (.tfi) in your test fixture (.tf) files to minimize re-working the test fixture files.

#### See Also

Verilog Simulator User Manual

### **Designing for Device Independence**

This section describes how to create device-independent designs that can be easily moved to different devices. Designing for device independence has many advantages. Device-independent designs mean you can:

- Take advantage of new devices as they become available with minimal maintenance.

- Learn one behavioral language and one symbol library for all devices, instead of learning a new one for each device you use.

- Try a design in several architectures to determine the ones in which your design fits best or runs fastest.

- Not be committed to the architecture you start your design with.

- Re-use your Synario designs in whole or in part.

- Draw your schematic without committing to a device.

- Perform functional simulation before device-specific features are specified.

You can map a device-independent design into a similar device, or link together several smaller designs targeted for small devices into a larger device.

### **Device-independent Designs**

#### Device-independent ABEL-HDL Modules

Most of the ABEL-HDL language is device independent (for example, equations, truth tables, state machine descriptions, and test vectors). However, the ABEL-HDL compiler needs some information about how signals function in logic descriptions.

| Information needed    | Provided in ABEL-HDL with                                                                           |

|-----------------------|-----------------------------------------------------------------------------------------------------|

| Signal specifications | Istype attributes in the signal declarations and dot extensions on signals in the logic description |

| Special functions     | Property Statements                                                                                 |

Most common signal functions can still be described independent of a device with the pin-to-pin signal declarations. Some special features available in only certain classes of devices require device-specific ("detailed") signal declarations.

#### **Conditional Symbols**

Some devices also have special functions that can be accessed through conditionally-compiled syntax. Each device kit has one or more special compiletime symbols that can be used to create conditionally-compiled designs. The table below shows a sample of the conditional symbols for various device kits. Refer to your device kit for more information on the conditional symbols supported.

| Device Kit | Conditional Symbols   |  |

|------------|-----------------------|--|

| LCA2000    | _LCA2000_, _LCA_      |  |

| LCA3000    | _LCA3000_, _LCA_      |  |

| LCA4000    | _LCA4000_, _LCA_      |  |

| PLDs       | _PLD_                 |  |

| MAX5000    | _MAXPLUS2_, _MAX5000_ |  |

| MAX7000    | _MAXPLUS2_, _MAX7000_ |  |

| MACH2      | _MACH2_, _MACH_       |  |

| MACH4      | _MACH4_, _MACH_       |  |

|            |                       |  |

An example of how to use conditional symbols in your ABEL-HDL source file is shown below:

```

@IFDEF _LCA_

{

<LCA macros>

}

@IFDEF _PLD_

{

<PLD macros>

}

```

#### **Pin-to-pin Signal Specifications**

Using ABEL-HDL's pin-to-pin syntax allows you to create logic descriptions that can be migrated to different devices. Use the pin-to-pin syntax whenever you have a choice to allow the module to be migrated with little or no modification.

#### **Detailed Signal Specifications**

Detailed signal specifications provide you with access to unique features found only in certain device families.

Synario Project Navigator User Manual

5-5

**Note:** You can combine pin-to-pin and detailed signal declarations. In most cases, the ABEL-HDL compiler can reconcile the requirements of both types. In some cases, however, the circuit function may be ambiguous and the compiler displays an error message.

Syntax descriptions indicate whether the syntax is pin-to-pin or detailed.

#### See Also

"Pin-to-pin Vs. Detailed Module Descriptions" in the *Synario ABEL-HDL Language Reference*

Your device kit for device-specific ABEL-HDL property statements and dot extension restrictions

#### **Device-independent Schematics**

#### Synario Device-independent Library

Synario's Device-independent Library gives you device-independent flexibility for your schematics. If you use device-specific symbols in a schematic, you may have to redraw the schematic if you later migrate your design to a different device.

#### **Device Kit Symbol Libraries**

The symbol libraries that come with each device kit are device specific. If you plan to stay in one device family, these libraries are all you need. However, since device kit symbols are tied tightly to the device they describe, migrating a project with a device-specific schematic may require redrawing the schematic using the new target device's symbol library. For this reason, we recommend the Synario Device-independent Library if you plan to use more than one type of device.

#### See Also

"Device-independent ABEL-HDL Modules"

Your device kit for device symbol libraries and Synario Device-independent Library mapping

There are many ways you can make it easier to map an existing design into a different device. These methods are discussed in Chapter 5, "Designing for Device Independence."

### When You Need to Select a Device

With Synario, you do not have to select a device to begin processing a design. You do need to select a device before you place and route your design or perform timing simulation (if you have the Synario Simulator).

You can, of course, specify a device at earlier stages in the design process.

### **Selecting a Device**

To choose any device, you must have a Synario Device Kit and the device support for the device installed.

You select the device for your project in the Choose Device dialog box. To access it, double-click on the Device icon in the Sources window, or select the Device icon and choose Open from the Source menu. The Choose Device dialog box is shown in Figure 6-1.

| Device Kit | Lists the titles of the device kits currently licensed for this<br>Synario installation. When you pick a device kit from this<br>list, the Device box belowis updated with the devices<br>supported by that kit.             |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device     | Lists the supported device names licensed by the device<br>kit. You can pick a device from this list, or enter a device<br>name. If you enter a name, it must match a device in the<br>listing (case doesn't have to match). |

**Note:** If the current project has sources that are not supported by the selected device, you will get a message box. Either select a different device or remove the unsupported sources from the project. (For example, standard PLDs do not support schematics, so selecting a P22V10 for a project that includes a schematic will cause this to happen.)

#### *Figure 6-1* Choose Device Dialog Box

| - Choose Dev                                                                                                                                      | ice                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Device <u>K</u> it:<br>Generic Device<br>LCA 2000 FPGAs<br>LCA 3000 FPGAs<br>LCA 4000 FPGAs<br>XC 3000 FPGAs (Unified)<br>XC 4000 FPGAs (Unified) | <u>O</u> K<br><u>C</u> ancel<br><u>H</u> elp |

| <u>D</u> evice:<br>Virtual Device<br>Virtual Device                                                                                               |                                              |

If your device change involves changing the underlying design environment (which is done automatically), Synario asks you to confirm the change.

#### Automatic Process Updating

You do not have to remember how to process your designs for different devices: when you specify or change the device for your design, Synario re-configures the processing steps automatically to reflect the processes required for the selected device.

### What Happens When You Select a Device?

Synario customizes itself for the currently-selected device. Changing the device to a device in a different device kit directly affects which processes, properties, and symbol libraries are available.

More detailed information about what is changed is given in the following sections.

#### How Processes Change with a Device Change

When you change to a device in a different device kit, the processing for the project changes. These changes are reflected in the following changes:

- The available processes change, especially device-specific process steps and netlists.

- The status of some processes that remain may return to "not processed" (that is, the green checks are removed and the process must be re-run for the new device).

- The properties available for processes.

#### How Properties Change with a Device Change

When you change to a device in a different device kit, the properties available for each Process change in the following ways:

- Properties are preserved for processes that did not change from the previous device kit (like the ABEL-HDL process "Compile Logic").

- Properties for new processes, and new properties for existing processes have default values assigned.

- For processes that are not available with the new device, the properties are no longer used or visible, but the settings are saved (if you switch back to the previous device kit, these properties will be the same).

#### How Schematic Symbols Change with a Device Change

When you change to a device in a different device kit, the schematic symbols that are available change. Each device kit supports the Synario Generic Library and the symbol library for the devices in the kit. This means that after changing kits, Add: Symbol in the schematic editor lists the available symbols for the device kit.

#### CAUTION:

- You need to close and re-open the Schematic Editor and Hierarchy Navigator for the symbol availability changes to take effect.

- Schematics drawn with symbols from only the Synario Generic Library work without modification.

- Schematics drawn with symbols from a device-specific symbol library that is no longer available will be missing those symbols (you will get "Missing Symbol File" messages).

**Note:** If you use the Synario Generic Library to draw all of your schematics, you'll rarely have to redo a schematic when you select a different device.

Synario Project Navigator User Manual

6-3

#### **Replacing Missing Symbols in a Migrated Schematic**

To modify a schematic that is missing symbols after you've changed the device kit being used, do one of the following:

- Edit the schematic and select a different symbol from the new device kit library or the Synario Generic Library.

- *OR* Create a new symbol and possibly an underlying schematic to support the new device kit.

#### For example:

Assume your original schematic was targeted to the MAX/FLEX device kit, and you used a symbol from the MAX/FLEX library. You then switch to the LCA3000 device kit, and this symbol is not supported. You get an error message "Missing symbol file *name*.sym" when you try to edit the schematic.

You can create a local symbol called *name*.sym, then draw a schematic called *name*.sch using symbols from the LCA3000 symbol library or the Synario Generic Library to provide the functionality of the MAX/FLEX symbol.

### **Device Kits**

#### What Is a Device Kit?

A device kit contains all of the tools you need to create designs for that device or family of devices. So if you purchase the LCA device kit, you receive tools and documentation to help you create designs for LCAs. Device kits can contain all or some of the following items, depending on the processing requirements for the devices supported:

- Device Synthesis applications

- Place-and-route applications

- Functional and Timing Simulation models (for simulation with the optional Synario Simulator)

- Device-specific Synario project examples

- Device-specific design help files

- Device-specific symbol libraries

- Device optimization and pin assignment software

#### How Do You Use a Device Kit?

#### To use your device kit:

- 1. Install the device kit software.

- 2. In your Synario project, double-click on the device icon and choose a device supported by the device kit.

The installation process installs device kit files that Synario uses to update the processes available to you.

#### Accessing Device Kit Help Files

#### To access the separate help file installed with your device kit:

Choose the device kit help file from the Synario Project Navigator Help menu. This brings up the help file for the currently-selected device kit.

*OR* In Synario's main help file, click on the Device Kit button and choose the device kit help you want.

## Appendix A Strategies and Properties

Many processes have options, called properties, that tell Synario how you want the process carried out. You can modify these properties in the Properties dialog box.

To use the Properties dialog box, select a process in the Process list that you want to modify. If the process has properties, the Properties... button below the Process list will be active. Click on this button to open the Properties dialog box and edit the properties for the currently selected process.

#### **Figure A-1** Properties Dialog Box

| Value list                            | - Prope                                                                 | rties - (Normal : ABEL)                                      | -                |

|---------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|------------------|

| Property entry box<br>Entry OK/Cancel | Properties:                                                             |                                                              |                  |

|                                       | Generate Listing                                                        | List None                                                    | Undo             |

|                                       | Module Arguments                                                        | Text                                                         |                  |

| Properties —                          | Compile Control Definitions                                             | Text                                                         | <u>D</u> efaults |

|                                       | Adva Adva                                                               | inced                                                        |                  |

|                                       | Retain Redundant Logic                                                  | T/F False                                                    | <u>H</u> elp     |

|                                       | ABEL Compatibility                                                      | List None                                                    |                  |

| Quick Help<br>window                  | Double-click the selected item to<br>or use the combo box in the edit r | cycle through possible choice<br>egion for a list of choices | 8.               |

The title of the Properties dialog box window displays the name of the currently selected Strategy (Normal) and the type of source selected (Design). If you modify the properties shown above, you are modifying the properties in the Normal style, for Standard PLDs, for the currently-selected Design-level process.

Synario Project Navigator User Manual

### **Properties**

There are four basic property types: True/False, Text, Num, and List .

**True/False** True/False properties have "T/F" in the second column of the Properties dialog box. To change the value of a True/False property:

Double-click on the property.

- *OR* Select the property and then press the value-list drop-down button to select True of False.

- OR Press T or F when a True/False property is selected.

You can undo a change by pressing the Undo button.

- **Text** Text properties take text strings defined by that property. To modify text properties

- 1. Select the text property in the property list. The current value of the text property (if any) is displayed in the property entry box (see Figure 1-4).

- 2. In the edit region, type in the text value for the property.

- 3. Click on the check (OK) button next to the edit region to accept the change. Click on the X (Cancel) button to cancel changes.

#### **Num** Numeric properties take integer numbers. To modify numeric properties:

- 1. Select the numeric property in the property list. The current value of the numeric property (if any) is displayed in the property entry box (see Figure 1-4).

- 2. In the edit region, type in an integer value for the property.

- 3. Click on the check (OK) button next to the edit region to accept the change. Click on the X (Cancel) button to cancel changes.

- List List properties allow you to select one value from a list of possible choices. To change the value:

- 1. Select the List property.

- 2. Click on the value-list drop-down button and select one of the values.

- *OR* Double-click on the List property. Each double-click causes the List property to change to the next possible value in the list.

Synario Project Navigator User Manual

#### **Advanced Properties**

Some properties in the Properties dialog box are advanced. Be sure to review the online help for these properties before changing them.

#### **Default Properties**

You can reset properties to the defaults for your device kit by clicking the Defaults button.

### **Setting Properties**

#### To set properties:

- 1. Select a source (for example, select the device to change project properties, or select a logic source (schematic or ABEL-HDL module) to change source properties).

- 2. Select a process from the Process window.

- 3. Click on the Properties button, or choose Properties from the Process menu. The Properties dialog box displays the standard and device-specific properties for that process.

- 4. Click on a property to select it.

- 5. Double-click on an option to toggle between choices. Click once to select an option and type in a new value, then select the green check to accept the change or the red X to undo.

If you change your mind, click on the Undo button.

6. To change the properties for another process, click on the desired source and/or process in the Synario main window. (You may need to move the Properties dialog box.)

The properties for the selected process are immediately displayed in the Properties dialog box window.

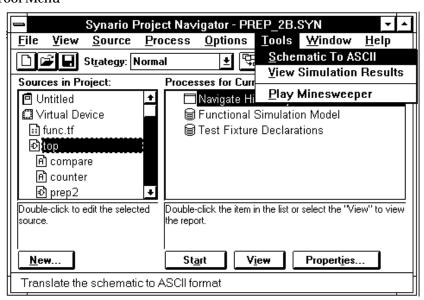

### Strategies

Strategies are advanced features of Synario that allow you to set up different processing options for different parts of a project. For example, you can use strategies to use one set of synthesis options for part of your project, and another set for the rest.

A strategy contains all of the property settings required to process the sources (such as an ABEL-HDL module) in the Sources in Project list, and a strategy can be assigned to one or more of the following types of source in a project:

| £         | Design           |

|-----------|------------------|

| ð         | Schematics       |

| A         | ABEL-HDL modules |

| $\square$ | VHDL sources     |

You can create multiple strategies and associate them with different sources in your design, allowing you to use different property settings for each source in your project.

When you associate a project source with a strategy, the source extracts its property settings from the strategy. For example, if you associate an ABEL-HDL source with a strategy named "Speed," the ABEL-HDL module uses the ABEL-HDL process property settings in the strategy "Speed," and ignores the property settings for the strategy "Normal."