# INTEL 432 SYSTEM SUMMARY: MANAGER'S PERSPECTIVE

Manual Order Number: 171867-001

Copyright © 1981 Intel Corporation Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051 Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

BXP CREDIT i ICE iCS im INSITE Intel Intel Intelevision Intellec iRMX iSBC iSBX Library Manager MCS Megachassis Micromainframe Micromap Multibus Multimodule Plug-A-Bubble PROMPT Promware RMX/80 System 2000 UPI uScope

and the combination of ICE, iCS, iMMX, iRMX, iSBC, iSBX, MCS, or RMX and a numerical suffix.

ii

### PREFACE

The Intel 432 System Summary is a series of booklets that introduces project managers and technical staff to the Intel 432 Micromainframe family. Compared to the 432's reference manuals, this material is both broader in scope and shallower in depth. On the other hand, it is not intended to teach any particular subject but to *introduce* an array of related topics. In general, the System Summary is the first publication anyone interested in the 432 should read.

Although the System Summary is introductory in nature, the presentation does assume a good general background in computer hardware and/or software. Ideally, the reader has previously developed a microcomputer-based product.

Recognizing that readers have different backgrounds and interests, the *System Summary* is published in three volumes:

- Intel 432 System Summary: Manager's Perspective, Order No. 171867;

- Intel 432 System Summary: Software Engineer's Perspective, Order No. 172177;

- Intel 432 System Summary: Hardware Engineer's Perspective, Order No. 172178.

The volumes are to be published in the order given above; consult your Intel sales office for information on the availability of any book in the series.

Each volume begins with an introduction that rapidly surveys the principal members of the product family. The *Manager's Perspective* links the major innovations of the 432 to the application issues that inspired them. This material is valuable to engineers as well as managers. The *Software Engineer's Perspective* begins with a description of a few key technical concepts that are central to the design of both the 432 and applications that are based upon it. It covers the 432 architecture (the compiler writer's view of the processors), Ada\* (the 432's first programming language), and iMAX (the 432's Multifunction

<sup>\*</sup> Ada is a trademark of the U.S. Department of Defense.

Applications Executive). The Hardware Engineer's Perspective is devoted to the components (chips) and to the System 432/600, a collection of board-level building blocks.

The Intel 432 is a comprehensive and evolving set of hardware and software products; the *System Summary* introduces only the cornerstones. For detailed and up-to-date information on the complete product line, consult your local Intel sales office.

# CONTENTS

U

|                                           | 1  |

|-------------------------------------------|----|

| A New Computer Technology                 | 1  |

| System Organization                       | 2  |

| General Data Processor                    | 4  |

| Interface Processor                       | 7  |

| System 432/600                            | 9  |

| Ada Programming Language                  | 11 |

| iMAX Multifunction Applications Executive | 12 |

| Summary                                   | 13 |

| CHALLENGE AND INNOVATION                  | 15 |

| Computer Innovation                       | 15 |

| The Intel 432                             | 17 |

| THE EFFECTIVE PERFORMANCE                 |    |

| CHALLENGE                                 | 19 |

| Performance-directed Instruction Set      | 19 |

| Incremental Computing Power               | 21 |

|                                           |    |

| Future Performance                        |    |

|                                           | 20 |

| THE SOFTWARE MANAGEMENT                   | 07 |

| CHALLENGE                                 | 27 |

| Compiler-oriented Machine                 | 28 |

| Modular Programming Language              | 31 |

| Modular Applications Executive            | 36 |

| Concurrent Programming And Execution      | 37 |

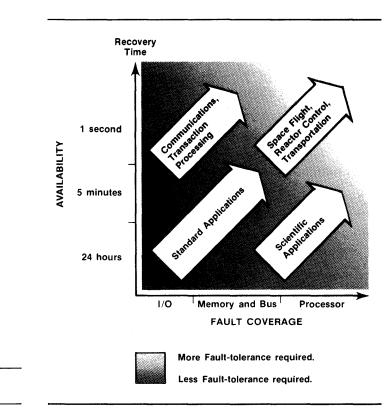

| THE DEPENDABILITY CHALLENGE               | 43 |

| Reliable Floating Point Arithmetic        | 44 |

| Compile-time Checking                     | 45 |

| Module Version Checking                   | 47 |

| Run-time Protection In Hardware           | 47 |

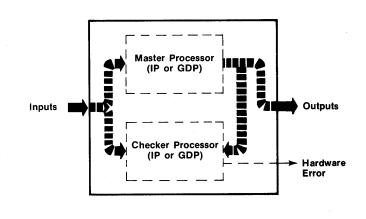

| Self-checking Processors                  | 53 |

| SUMMARY                                   | 57 |

| U.S. AND CANADIAN SALES OFFICES           | 59 |

| INTERNATIONAL SALES OFFICES               | 65 |

|                                           |    |

### TABLES

| 1. | General Data Processor Specification |    |

|----|--------------------------------------|----|

|    | Summary                              | 5  |

| 2. | Interface Processor Specification    |    |

|    | Summary                              | 8  |

| 3. | System 432/600 Specification Summary | 10 |

| 4. | Ada Specification Summary            | 11 |

| 5. | iMAX Specification Summary           | 13 |

| 6. | High Level Language Statements And   |    |

|    | Machine Instructions                 | 30 |

|    |                                      |    |

### **ILLUSTRATIONS**

| 1.  | General 432 System Organization        | 3 |

|-----|----------------------------------------|---|

| 2.  | General Data Processor                 | 5 |

| 3.  | Interface Processor                    | 7 |

| 4.  | System 432/600                         | 9 |

| 5.  | Ada Program Fragment                   | 1 |

| 6.  | iMAX Multifunction Applications        |   |

|     | Executive 12                           | 2 |

| 7.  | Gradual And Quantum Computer           |   |

|     | Innovation 1                           | 5 |

| 8.  | Self-dispatching 22                    | 2 |

| 9.  | Bitwise Instruction Encoding 3         | 1 |

| 10. | Subprogram-based System Organization 3 | 2 |

| 11. | General Form Of A Package 3            | 4 |

| 12. | Package-based System Organization 3    | 5 |

| 13. | iMAX Package-based Organization 3      | 7 |

| 14. | Sequential And Concurrent Execution 3  | 8 |

| 15. | Ada Strong Typing Examples 4           | 6 |

| 16. | Module Version Checking 4              | 8 |

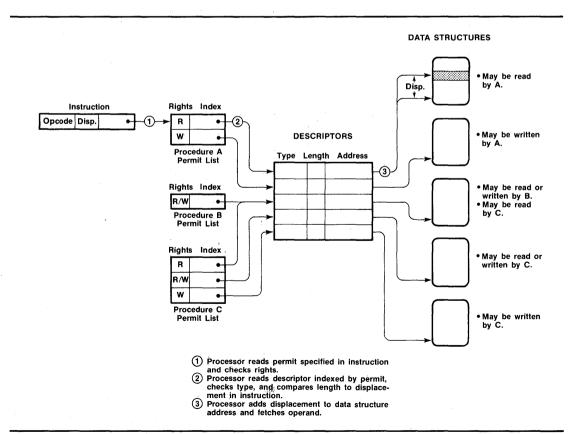

| 17. | 432 Protected Addressing 5             | 0 |

| 18. | Fault-tolerant Systems 5               | 4 |

| 19. | Self-checking Processor Module 5       | 5 |

### INTRODUCTION

#### A NEW COMPUTER TECHNOLOGY

The Intel 432 is a microcomputer family. Original equipment manufacturers (OEMs) will use the 432 as one element of the larger products they build for other parties. These end products may be office automation work stations, factory information systems, large PABXs or telephone office switches, transaction processing systems, families of general-purpose computers and so on. The 432 "engine" at the heart of such a product will often be imperceptible to an end user.

While — as the above list suggests — the 432 can support a diverse array of end products, it is at the same time aimed at a distinctive class of applications. Products wellsuited to the 432 exhibit some or all of the following attributes (as seen by the OEM, not the end user):

- a range of performance (potentially extending up to the level of a midrange mainframe) is required to span a family of related products or to provide headroom for future growth;

- *maximum dependability* (data integrity and uptime) of both hardware and software is critical;

- software dominates development cost and time to market;

- concurrent execution of many independent and cooperative activities characterizes the run-time environment;

- growth and evolution of services over time make software revision as important as initial development.

Compared to "traditional" microcomputer applications, these applications are larger (as measured by consumption of computer as well as staff and financial resources) and are far more complex. These factors place demanding requirements on the computer system selected to support the application.

One requirement of large applications is abundant computer resources; accordingly, the 432 family is based on a 32-bit architecture. Compared to a 16-bit machine, the 432 provides a very large actual address space, an enormous virtual address space, and a rich variety of data types, instructions and addressing modes. While these capabilities are undeniably important, a 32-bit computer is essentially a "bigger hammer." To meet the demands of extremely complex applications, 32-bit resources are at once *necessary* and *insufficient*. That is why, for the 432, its 32-bit architecture is more a *point of departure*, than a goal.

The goal of the 432 is to **significantly reduce the lifecycle costs of complex microcomputer applications**. Toward this end, the 432 introduces a *new computer technology*, an integrated system of hardware, software and methodology. The technology of the 432 preserves the traditional microprocessor virtues of low cost, small physical size and low power consumption. Like a mainframe family, it offers a 32-bit architecture and spans a range of performance. In other important ways, the 432 resembles no computer of the past. Considered as a whole, its new technology constitutes a breakthrough in computer system design. To emphasize that this technology is inadequately described by conventional computer "classifications," the Intel 432 is called the Micromainframe family.

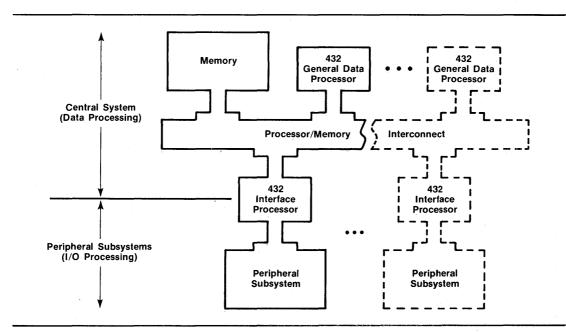

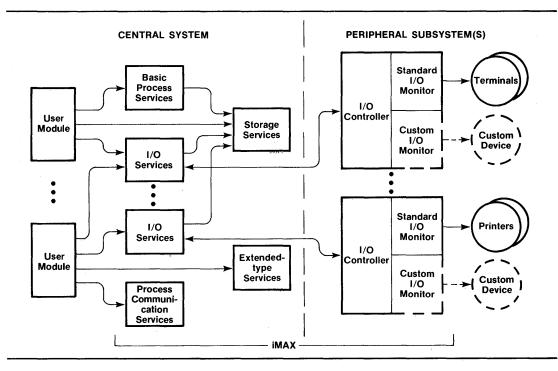

#### SYSTEM ORGANIZATION

All 432-based systems share the overall organization depicted in figure 1. The boundary between the central system and the peripheral subsystems essentially divides responsibility for data processing from input/output processing. It also serves as a protective barrier: all information in central system memory is shielded (by 432 hardware) against unauthorized access; peripheral subsystems may or may not provide any sort of protection. Finally, processing required to satisfy a critical real-time constraint (usually related to an I/O device) is generally performed in a peripheral subsystem, close to the source of the constraint.

The central system is organized as a set of 432 processors that share access to a common pool of memory and to each other. General data processors (GDPs) perform

#### INTRODUCTION

Figure 1. General 432 System Organization computational work, while interface processors (IPs) provide pathways for input/output to and from the central memory. The number and type of processors configured in a given system is a function of performance requirements, and can be varied independently of software. All 432 processors have built-in facilities for communicating with each other, both automatically and under software control. Additional communication facilities permit programs running on the same or different processors to exchange messages through memory.

The central system supports up to 2<sup>24</sup> bytes (16 megabytes) of real memory, and a virtual memory space of 2<sup>40</sup> (over a trillion) bytes. Enforced automatically by the processors, every data structure in the central memory is individually protected. It is important to note here that "data structure" means *any organized collection of information*, including such logical entities as operand stacks and sequences of code, as well as what are ordinarily considered data structures.

#### INTRODUCTION

A multiprocessor design like the 432 permits widely differing systems to be built from a small collection of parts. No bus design could possibly satisfy the cost, size, flexibility and performance requirements of all possible system configurations. Therefore, the 432 defines a standard processor/memory communications protocol rather than a standard bus. Designed to minimize bus occupancy and exploit available bus width, the protocol is based on a variable-length (1 to 16 byte) packet of information. Processors transmit request packets to memory, and receive reply packets in response to read operations. The protocol defines interprocessor communication as well. Each application is free to design an interconnect structure that implements the protocol in conformance with local needs.

Independent decentralized I/O, along the lines of the mainframe channel concept, is inherent in the 432. Input/ output operations — including all device control, interrupt handling and data buffering — are delegated to peripheral subsystems. These are autonomous satellite computers attached to the central system by means of 432 interface processors. The number and configuration of peripheral subsystems is a function of application needs and can evolve over time. Any computer that can communicate over a standard 8- or 16-bit bus, such as Intel's Multibus design (IEEE standard 769), can serve as a peripheral subsystem.

#### GENERAL DATA PROCESSOR

Fabricated in two 64-pin chips (see figure 2 and table 1), the 432 general data processor provides the 432's primary computational base. The GDP combines mainframe computer functionality — data types, addressing modes, basic instruction set — with the form factor, power requirements, and cost characteristics of a microprocessor.

Figure 2. General Data Processor

#### Table 1. General Data Processor Specification Summary

| Addressability                                                                                   | 2 <sup>24</sup> bytes physical, 2 <sup>40</sup> bytes virtual.                                                                                                                                                                                          |  |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Types                                                                                       | character, 16/32 bit signed and unsigned integers, 32/64/80 bit floating point.                                                                                                                                                                         |  |

| Addressing Modes                                                                                 | scalar, stack top, record element, static vector element, dynamic vector element.                                                                                                                                                                       |  |

| Basic Instructions<br>Data Transfer<br>Arithmetic                                                | move, save, zero, one.<br>add, subtract, multiply, divide, remainder, square root,<br>increment, decrement, negate, absolute value.                                                                                                                     |  |

| Logical<br>Comparison                                                                            | AND, OR, XOR, XNOR, complement.<br>equal, not equal, equal zero, not equal zero, greater than,<br>greater than or equal, positive, negative.                                                                                                            |  |

| Conversion<br>Bit Field (1-32 bits)<br>Control Flow                                              | (to any data type).<br>extract, insert, significant bit.<br>branch (conditional and unconditional), call, call with message, return.                                                                                                                    |  |

| High-level Instructions<br>Communication<br>Storage Allocation<br>Mutual Exclusion<br>Protection | <ul> <li>16 instructions (e.g., send, receive, broadcast to processors).</li> <li>4 instructions (e.g., create data segment).</li> <li>6 instructions (e.g., lock object).</li> <li>14 instructions (e.g., restrict rights, inspect access).</li> </ul> |  |

| Automatic Operations                                                                             | Process dispatching and low-level scheduling, message synchronization and queuing.                                                                                                                                                                      |  |

(Table 1 continued on next page)

#### INTRODUCTION

| Protection                   | "Need to know" addressing at data structure level; attempted violations detected and reported by hardware. Automatic detection of processor hardware errors when processors are configured in self-checking pairs. |                         |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| Selected Timing Data         |                                                                                                                                                                                                                    |                         |  |

| (µsec at 8 MHz)              |                                                                                                                                                                                                                    |                         |  |

| Processor Cycle              | 0.125                                                                                                                                                                                                              |                         |  |

| Memory Read/Write            |                                                                                                                                                                                                                    |                         |  |

| (word)                       | 0.75                                                                                                                                                                                                               |                         |  |

| High-level/Automatic         |                                                                                                                                                                                                                    |                         |  |

| Operations*                  | 1                                                                                                                                                                                                                  |                         |  |

| Send Message                 | 86.875                                                                                                                                                                                                             |                         |  |

| Receive Message              | 96.975                                                                                                                                                                                                             |                         |  |

| Create Segment               |                                                                                                                                                                                                                    |                         |  |

| (100,1000,10,000 bytes)      | 94.9, 308.375, 2417.75                                                                                                                                                                                             |                         |  |

| Suspend, Reschedule          |                                                                                                                                                                                                                    |                         |  |

| And Dispatch New             |                                                                                                                                                                                                                    |                         |  |

| Process                      | 401.875                                                                                                                                                                                                            |                         |  |

| Arithmetic*                  | (32-bit integers)                                                                                                                                                                                                  | (80-bit floating point) |  |

| Add/Subtract                 | 0.5                                                                                                                                                                                                                | 19.125                  |  |

| Multiply                     | 6.375                                                                                                                                                                                                              | 27.875                  |  |

| Divide                       | 10.625                                                                                                                                                                                                             | 48.25                   |  |

| Square Root                  | n.a.                                                                                                                                                                                                               | 55.625                  |  |

| Package<br>Power Requirement | (Two) 64-pin quad in-line (QUIP)<br>+5V ±10%, 2.5 Watts                                                                                                                                                            |                         |  |

\*Preliminary figures, subject to change. Data reflect execution time only and do not include instruction fetch, operand fetch/store or pipeline refill, where applicable. Arithmetic figures are thus comparable to register-to-register operations on a register-based machine. High-level and automatic operations do include all memory accesses made during execution; in these cases the memory subsystem is assumed to provide the minimal response time, and no provision is made for delays due to arbitration or error correction.

#### Table 1. General Data Processor Specification Summary (Cont.)

Compared to a conventional processor, the GDP absorbs into hardware many functions that are customarily performed by application and systems software. For example, the GDP provides hardware operations on floating point numbers in its basic instruction set. Clearly, implementing these in hardware improves performance. Less obvious effects are the simplification and improved reliability of software. Without effort, programmers reap the benefits of the very clean, thoroughly-considered algorithms of the proposed IEEE floating point standard.

Extending this concept, the GDP supplements its basic instruction set with additional high-level instructions. These instructions execute time-critical, frequently-used operations that are conventionally performed by operating system software. The operands of these systems programming instructions are not numbers or characters but data structures that resemble conventional OS "control blocks."

Going one step further, the GDP also performs a number of functions automatically, on its own initiative, rather than in response to an instruction. For example, a GDP allocates itself among ready programs with no intervention from an operating system. Since they represent operating system software functions moved into silicon, the highlevel instructions and automatic operations are collectively called the "silicon operating system."

The single-chip 432 interface processor (see figure 3 and table 2) functions at the central system/peripheral subsystem boundary. Acting as an "intelligent adaptor," the interface processor permits peripheral subsystem software to direct data transfers across the system boundary. The interface processor is wired into the memory space of the peripheral subsystem like a memory-mapped peripheral controller and is indistinguishable from a block of local memory. It may be addressed by PS software to execute commands and it may be addressed

Figure 3. Interface Processor

#### INTERFACE PROCESSOR

by any active agent (e.g., DMA controller) to transfer data. The IP's commands correspond to GDP high-level instructions; they permit peripheral subsystem software to operate within the central system environment. An important group of commands enables communication with both programs and processors in the central system.

Data transfers are performed by means of four IP data paths, called *windows*. Each window exposes one "data structure" in central system memory; peripheral subsystem software can switch a window to a different data structure by means of an IP command. To an agent in the peripheral subsystem, a window is just a range of memory addresses; writing into these addresses writes into the exposed data structure, and reading from these addresses obtains data from the data structure. Since all transfers pass through it, the IP is able to insure that a peripheral subsystem does not violate the protection standards of the central system.

| Addressability                                                                                                                               | 2 <sup>24</sup> bytes physical, 2 <sup>40</sup> bytes virtual.                                                                                                                                                     |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Central System Interface                                                                                                                     | Identical to GDP.                                                                                                                                                                                                  |  |

| Peripheral Subsystem Interface                                                                                                               | Appears to peripheral subsystem as memory mapped controller; 8/16<br>bit data bus multiplexed with 16 bit address bus; standard control and<br>interrupt signals; compatible with Multibus architecture.           |  |

| Transfer Units                                                                                                                               | Byte and double-byte.                                                                                                                                                                                              |  |

| Transfer Modes                                                                                                                               | Random: Any single location; block: contiguous set of locations up to 64kb long.                                                                                                                                   |  |

| Data Paths                                                                                                                                   | 3 random mode, 1 switchable block/random mode.                                                                                                                                                                     |  |

| Command Set                                                                                                                                  | Equivalents for large subset of GDP high-level instructions (e.g., send, receive, lock object, etc.)                                                                                                               |  |

| Automatic Operations                                                                                                                         | Message synchronization and queuing.                                                                                                                                                                               |  |

| Protection                                                                                                                                   | "Need to know" addressing at data structure level; attempted violations detected and reported by hardware; automatic detection of processor hardware errors when processors are configured in self-checking pairs. |  |

| Selected Timing Date (at 8 MHz)<br>Maximum Data Rate<br>Block Mode<br>Random Mode<br>High-level Commands*<br>Send Message<br>Receive Message | 5.3 mb/sec.<br>1.1 mb/sec.<br>145.25 μs.<br>141.5 μs.                                                                                                                                                              |  |

| Package                                                                                                                                      | 64-pin quad in-line (QUIP)                                                                                                                                                                                         |  |

| Power Requirements                                                                                                                           | +5V ±10%, 2.5 Watts                                                                                                                                                                                                |  |

\*Preliminary figures, subject to change. System functions are for execution time only and do not include operand fetch or store times, which are highly dependent on memory configuration and bus arbitration.

Table 2. Interface Processor Specification Summary

#### SYSTEM 432/600

The System 432/600 is a set of board-level building blocks (see figure 4 and table 3) from which 432 computer systems can be built quickly with minimal investment and minimal hardware expertise. The 432/600 utilizes the multiprocessing capabilities of the 432 to provide a set of building blocks that can be configured with unusual flexibility.

Figure 4. System 432/600

Computing and I/O power are selected by mixing GDP boards and peripheral subsystems, respectively. By presenting a standard Multibus interface, the 432/600 permits peripheral subsystems to be built from Intel's comprehensive array of iSBC computers, memories and peripheral controllers. A 432/600 configuration may contain a total of six processing elements (GDPs and peripheral subsystems). Storage array boards of 128k-bytes and 256k-bytes permit precise matching of memory to application requirements, up to a total of four megabytes of central system storage.

In addition to these board components, the 432/600 offers diagnostic software, cardcages and backplanes, and a powered and cooled enclosure.

9

#### **INTRODUCTION**

#### Table 3. System 432/600 Specification Summary

| System Organization<br>Functional Elements<br>System Bus<br>Peripheral Subsystem Bus              | 432 general data processor board; 432 interface processor/link board<br>pair; memory controller board; 128/256 kb storage array boards.<br>32-bit multiplexed address/specification/data bus; dedicated status<br>and control signals; round-robin arbitration; 32 mb/sec. instantaneous<br>data rate.<br>Standard Intel Multibus design, separate bus for each peripheral sub-<br>system.                                         |  |

|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Form Factor<br>Power Requirements                                                                 | Intel iSBC (6.75 x 12 in.) +5V ( $\pm$ 10%), 5-7 amps (max.) per board at 5V.                                                                                                                                                                                                                                                                                                                                                      |  |

| Data Processing<br>Functional Element<br>Extensibility<br>Memory Read Cycle<br>Memory Write Cycle | general data processor board.<br>1-5 GDP boards per system.*<br>2.125 μs. (word access).<br>3.375μs. (word access).                                                                                                                                                                                                                                                                                                                |  |

| I/O Processing<br>Functional Element<br>Extensibility<br>Data Rate                                | Independent peripheral subsystem attached to central system via inter-<br>face processor/link board pair.<br>1-5 peripheral subsystems per system.*<br>2.5 mb/sec. per subsystem.                                                                                                                                                                                                                                                  |  |

| Memory<br>Functional Elements<br>Extensibility<br>Type<br>Bandwidth                               | Memory controller board, storage array board of 128 and 256 kb each.<br>128 kb - 4 mb, according to number and type of storage arrays.<br>Dynamic RAM; onboard refresh.<br>7 mb/sec.                                                                                                                                                                                                                                               |  |

| Reliability<br>Memory<br>System Bus<br>Error Reporting<br>Diagnostic Software                     | Error checking and correction standard; all single-bit errors detected<br>and corrected, all double-bit errors detected.<br>Each byte parity-checked.<br>Registers for system, memory and processor errors automatically<br>updated by hardware; accessible to software.<br>Rapid "go/no go" check of entire system; detailed diagnostics provided<br>for each board type; executes on iAPX 86/88-based peripheral sub-<br>system. |  |

| Packaging Accessories<br>Back planes<br>Cardcages<br>Enclosure                                    | 6/12/18 slot units.<br>6/12/18 slot units.<br>Enclosed chassis with power and cooling, 18-slot cardcage, 12-slot<br>system backplane, 6-slot Multibus backplane.                                                                                                                                                                                                                                                                   |  |

\*The maximum number of GDPs and peripheral subsystems combined is 6.

#### ADA PROGRAMMING LANGUAGE

Ada (see figure 5 and table 4) is a modern high level language whose development was sponsored by the United States Department of Defense. In its basic form and "flavor," Ada resembles Pascal, probably the most influential language of the nineteen-seventies. Ada differs from Pascal in *scope*; while Pascal was developed to teach programming, Ada is a production language, explicitly

|                                  | (integer i<br>array_su<br>:<br>idexes:                                                              | ay is array<br>range <>) of flo:<br>im (<br>in real_array;<br>out float;<br>out float;<br>out float; | at; |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|--|

| is                               |                                                                                                     |                                                                                                      |     |  |

| sum_so<br>for i in<br>sum<br>sum | ndexes :=<br>quares :=<br>n a' <b>range</b>  <br>n_x := sun<br>n_indexes<br>n_squares<br><b>op;</b> | 0.0;                                                                                                 |     |  |

Figure 5. Ada Program Fragment

#### Table 4. Ada Specification Summary

| Data Types                                                           | Boolean, character, string, natural, integer, floating point, fixed point, enumeration, array, record, access, plus programmer-defined types.                       |  |  |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operators<br>Logical<br>Relational/Membership<br>Arithmetic<br>Other | and, or, xor.<br>=, /= <, <=, in, not in.<br>+, -, *, /, mod, rem, **, abs.<br>+ (identity), - (negation), not (logical negation), & (catenation).                  |  |  |

| Control Structures                                                   | If-then-else, case, loop, begin-end, go to, return, exit.                                                                                                           |  |  |

| Subprograms                                                          | Procedures and functions.                                                                                                                                           |  |  |

| Module Structures                                                    | Subprograms, packages, tasks.                                                                                                                                       |  |  |

| Concurrent Programming                                               | Complete multitasking facility, including task definition, initiation, termination, prioritization, delayed execution, intertask communication and synchronization. |  |  |

| Input/Output                                                         | General-purpose record-oriented sequential file processing; special text file (line-and-column oriented) processing.                                                |  |  |

| Other Features                                                       | Generic (macro-like) subprograms; exception detection and handling.                                                                                                 |  |  |

oriented toward the construction of software for embedded computer applications. Examples of Ada's additional capabilities include language constructs to support modular development of large systems of programs, concurrent programming (multitasking) and run-time exception handling.

#### iMAX 432 EXECUTIVE

#### Figure 6. iMAX Multifunction Applications Executive

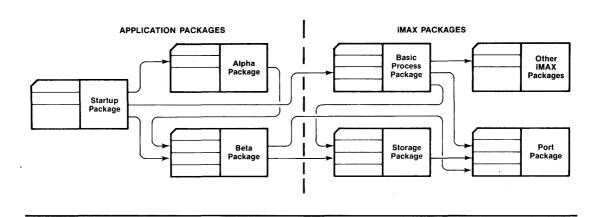

iMAX (Multifunction Applications Executive) is a collection of software "components" (see figure 6 and table 5). Running on both the 432 central system and peripheral subsystems, iMAX provides basic services that are essential to most 432 applications. Carrying the notion of "components" further, users may selectively configure iMAX services into their systems, may replace iMAX modules with their own, and may add new executive services as well.

÷.

#### INTRODUCTION

| System Organization               | Modular "catalog" of Ada packages, each providing a related set of services for central system; peripheral subsystems coordinated by resident I/O controllers.                                  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmer Interface              | Ordinary Ada function and procedure calls; all calls checked at compile-time.                                                                                                                   |

| Storage Services                  | Dynamic segment creation; automatic reclamation and compaction of discarded segments in parallel with normal system operation.                                                                  |

| Basic Process Services            | Dynamic process creation, destruction and control (start, stop,<br>synchronize, etc.); processes and subprocesses may be organized in<br>trees; process scheduling by deadline and/or priority. |

| Process Communication<br>Services | Port (data structure for queuing messages) creation; message transmittal (send, receive, sequence, etc.)                                                                                        |

| Extended-type Services            | Creation, identification and access control for user-defined data struc-<br>ture types.                                                                                                         |

| Input/Output Services             | I/O monitors (device drivers) for terminal-like devices provided;<br>users may write monitors for other devices; programmer interface<br>supports varying degrees of device independence.       |

| Initialization Services           | Loading of initial central system memory image from designated peripheral subsystem; central system startup.                                                                                    |

#### Table 5. iMAX Specification Summary

SUMMARY

The Intel 432 is a comprehensive family of products, embracing chip- and board-level hardware components, a high level programming language and an applications executive. Together, these constitute a system designed to lower the initial cost and the continuing cost of developing complex, highly dependable end products. Such applications are further characterized by the execution of many concurrent activities, a heavy information processing orientation, and the ability to expand performance without changing software.

## CHALLENGE AND INNOVATION

#### COMPUTER INNOVATION

Few fields are more dynamic and innovative than computing. New computers and lines of computers are introduced almost weekly. Yet at the same time, sampling a set of contemporary machines — even across manufacturers and classes (micro, mini or mainframe) — reveals a surprising resemblance in their basic designs.

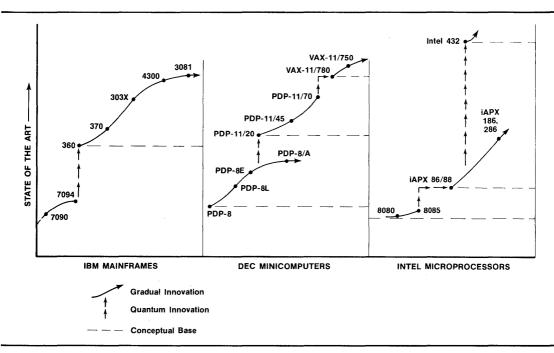

A look at figure 7 helps to explain this phenomenon by examining computer families from IBM<sup>1</sup>, DEC<sup>2</sup> and Intel; the pattern holds for most other manufacturers as well. The state of the art in computing is raised by innovation. As the chart shows, most innovation is gradual or evolutionary. A new computer (or series) usually provides an improvement over its predecessors in terms of address space, instruction set, speed or price, while carrying forward an earlier basic design concept. "Quantum" innovations, which establish new conceptual foundations,

Figure 7. Gradual And Quantum Computer Innovation

<sup>1</sup>International Business Machines Corporation <sup>2</sup>Digital Equipment Corporation

are rare. These few seminal machines instantly elevate the standard for the entire industry, changing the general perception of what a computer is and what it can do. The successful introduction of a quantum machine like the 360 or the PDP-11 inspires a new evolutionary cycle of derivation (and imitation) as the original manufacturer brings out enhanced models, and competitors incorporate the new concepts into their own products.

Of course this pattern is understandable when we consider that a quantum innovation is rarely possible, and then very difficult to realize. Computer innovation is enabled — if not driven — by technology. A sufficient body of technical advances must accumulate to provide the "raw material" for a new design, and technology must make the new machine buildable and economical. Even when the technical basis for a quantum innovation exists, however, market conditions must coincide to open the innovation "window."

History — in the form of past machines — encourages evolutionary development because a quantum innovation usually requires loosening compatibility constraints. Ironically, the very success of a previous innovative machine tends to restrain a company from building another one. To avoid obsoleting large customer investments in training and software, a new market must usually be identified for a quantum machine. Existing lines can then continue to be enhanced in an evolutionary fashion for the benefit of the present customer base, while the new machine builds another base.

The time, expense and risk required to pioneer a quantum computer also pushes most companies toward an evolutionary style of innovation. It is far easier to borrow and enhance proven concepts than to create new ones.

#### THE INTEL 432

The Intel 432 is a quantum innovation in computing. Technically, it combines software engineering and computer science advances of the 1970's with Intel's stateof-the-art MOS technology. The 432 program began in 1975 and the first chips were operational five years later; it represents Intel's largest investment in a single program.

The 432's innovations can be viewed on two levels. First, of course, it delivers 32-bit computer resources in a microcomputer package. This powerful combination opens up a whole new realm of products that can benefit from microcomputer-based design. Yet at the same time, the opportunities afforded by a 32-bit microcomputer system are deeply intertwined with an array of formidable challenges.

These challenges are inherent in the nature of the applications that a 32-bit microcomputer makes feasible for the first time. While these applications will vary enormously in function, they will share a core of common properties. Compared to 8- or 16-bit applications they will be an order of magnitude larger and more complex. Many of them will perform multiple functions concurrently, and most will evolve over many years. Finally, long-term dependable operation will be essential as people and organizations become increasingly reliant on these powerful systems. To grasp the magnitude of these new challenges, one might well consider that the software for many 32-bit microcomputer applications will rival *mainframe operating systems* in size, complexity, and the need for dependable operation.

What have we learned from the development of today's mainframe operating systems (and other ambitious programs)? The record is not encouraging. Many of these systems have never seen the light of day, having been aborted when it became apparent that they could not possibly satisfy their objectives. Those systems that have been placed in operation have uniformly been late, over budget, full of bugs in one release after another, and so fragile that they are almost impossible to modify with confidence. (In fairness, it must also be pointed out that many of these systems do "get the job done" in the

environment for which they have been defined — often a computer room with systems programmers and service personnel located nearby. This is far from the environment of the typical microcomputer-based product, however.)

In short, experience indicates that the traditional technology exemplified in most computers and languages is not up to the challenges of building complex, evolving, highly dependable systems. To build a 32-bit microcomputer that is a miniaturized conventional mainframe or supermini, or a scaled-up 16-bit micro, is to ignore history. The 432's second, and more profound, level of innovation is based on this recognition.

The remainder of this booklet examines the principal challenges facing the developers of complex computerbased products:

- obtaining the right *kind* of performance;

- managing software development and revision;

- insuring *dependable operation* of both hardware and software.

In each area the 432 responds with innovations designed to meet the challenge. Collectively, these innovations constitute a *new computer technology*.

### THE EFFECTIVE PERFORMANCE CHALLENGE

To appreciate what we mean by *effective* performance, consider the following questions:

- How effective is a system that adds integers in a microsecond but requires 1,000 times as long to add real numbers?

- How effective is a system that has eight varieties of string translation instructions, none of which is ever generated by a compiler?

- How effective is a system that spends most of its time executing operating system overhead routines, rather than application code?

- How effective is any system that has a *fixed* level of performance, that cannot be adapted to changing needs?

Effective performance is more than raw instruction speed, it is speed applied to a *variety* of parameters to optimize total end product throughput, even in the face of changing demands.

A single 432 processor has an instruction set that effectively "automates" time-consuming functions normally performed in software. *Multiple* 432 processors work together to deliver a range of performance in both computation and input/output, similar in concept to the range provided by a compatible mainframe or minicomputer family. Finally, the current 432 product line anticipates the ability of technology to support improved performance in the future.

#### PERFORMANCE-DIRECTED INSTRUCTION SET

To improve the performance of any system one must apply optimization efforts selectively to obtain the best return. This is typically done by analyzing the system to see where it spends its time. That is, the system is studied to identify the routines that consume the most total time, either by virtue of lengthy duration, high frequency of execution, or both. This same approach has been applied to the design of the 432's instruction set. Rather than implement a raft of "clever" new instructions, the 432 moves proven highpayoff functions into hardware. These fall into two general categories: numeric computation and operating system "overhead."

Floating point numbers provide a useful approximation of the real number system that people use for most calculations. They can express not only integers but also fractions and irrationals, and are further capable of great range and precision. Because of their versatility, floating point numbers are very attractive for microcomputer applications. Unfortunately, the floating point algorithms are quite complex. When they are implemented in software, floating point operations are so expensive that they must be ruled out for many applications. For example, addition and square root take about 1.600 and 19.600 microseconds respectively when executed in software on a 5MHz iAPX 86. By moving floating point algorithms into hardware, the 432 makes the convenience of floating point arithmetic a practical alternative for most applications (add and square root execution times are about 13 and 56 microseconds respectively). Note that this same argument is the rationale for the Intel 8087 Numeric Data Processor, which brings hardware floating point to 16-bit applications.

Three important functions, which are normally executed by operating system subroutines, have been absorbed into the hardware of the 432. First, as amplified in the following section, general data processors assume responsibility for program dispatching — switching themselves among multiple programs — with no intervention from software. Second, the 432 maintains pools of free memory; storage can be allocated from a pool with a single GDP instruction. Third, both GDPs and IPs support a general-purpose system of program-to-program communication. A message, consisting of any data structure in memory, may be sent or received in a single instruction; messages are queued automatically by the hardware so that send and receive operations may be executed independently of one another.

#### THE EFFECTIVE PERFORMANCE CHALLENGE

#### INCREMENTAL COMPUTING POWER

Since the introduction of the IBM System/360, typical mainframe and minicomputer product lines have been organized as compatible families. Each model of the family offers a different level of performance (and price). While the capability of an individual model is limited, the family as a whole spans a wide range of performance. To obtain a performance increment, the customer must change hardware (i.e., substitute one model for another), but — importantly — existing software is preserved intact.

This kind of flexible performance, taken for granted by mainframe and minicomputer users, is not so welldeveloped in microcomputers. A given microcomputer provides a single level of performance. Over time, new versions that run at higher clock rates are typically introduced; over more time, a new "generation" usually emerges with a different, but upward-compatible architecture. Thus, given the passage of time, an application can usually "trade up" to a faster processor. Often the substitution requires substantial hardware redesign.

This approach is satisfactory in applications that are fairly well-defined with relatively bounded execution-time behavior, as microcomputer-based systems have tended to be. As applications become more complex and more dynamic, however, it becomes increasingly difficult to predict how much processing power a system will need to meet its performance goals. This uncertainty is a serious source of risk since an application must usually commit itself to a processor two years before any software has been written. Even when the "right" decision is made initially, design changes and extensions that crop up during development and after introduction can threaten a system's viability. A second limitation of the "new model" approach is that it effectively prohibits designing a family of end product models that use the same hardware and software components to provide different performance levels. In response to these challenges, the 432 has been designed with incremental performance as an inherent feature of the architecture.

#### THE EFFECTIVE PERFORMANCE CHALLENGE

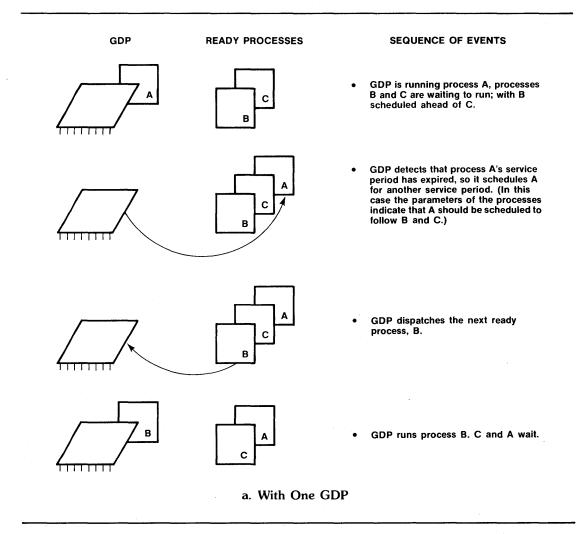

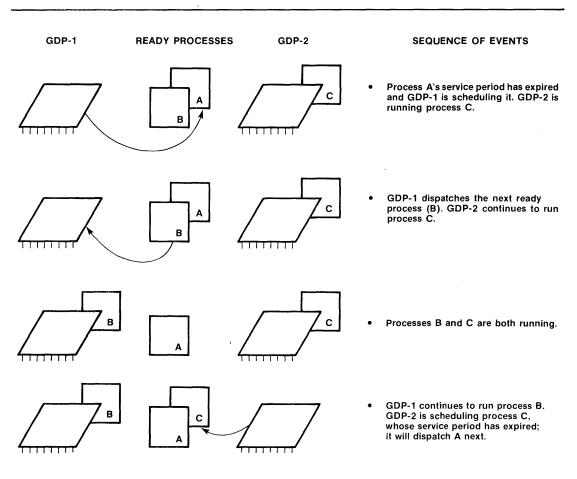

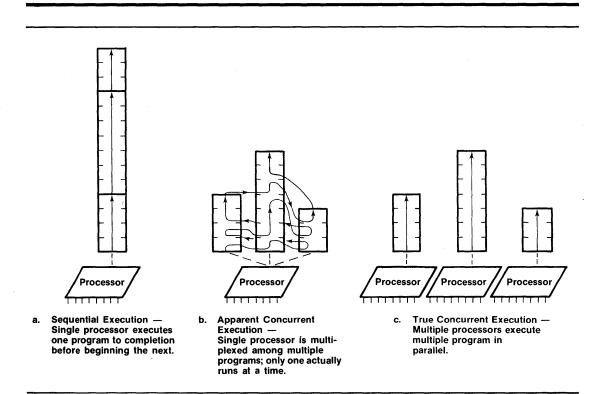

Overall computational throughput in a 432-based design can be adjusted by changing the number of general data processors in the system. These processors are *selfdispatching*; the normal cycle of running a program unit (a process) until it waits for an event (blocks) or times out, rescheduling it for subsequent execution, and then switching to the next ready process is performed automatically by the GDPs (see figure 8). Software, including the operating system, can be completely unaware of how many

Figure 8. Self-dispatching

THE EFFECTIVE PERFORMANCE CHALLENGE

#### b. With Two GDPs

Figure 8. Self-dispatching (cont'd) processors are present in the system. In everyday terms, the effect is somewhat like the single service line used at many banks. The line of customers waiting to be served will move faster if additional tellers open their windows. Since the number of processors is invisible to software, this important facility of the 432 is called *transparent multiprocessing*.

While transparent multiprocessing is most attractive for its ability to add computing power to a system, it is also 1

important to recognize the significance of being able to reduce the number of processors in a system without altering software. If, in a multiple-GDP system, a processor fails, its circuit board can simply be removed from the system. The system can be restarted and it will then provide the same services but at a slower rate. In this way transparent multiprocessing permits a system to remain useful after a processor failure.

Of course, there are limitations to the performance improvement that can be realized by adding processors, and these break down into two general areas. First, in order to utilize the processing potential of multiple GDPs, there must be work for them to do. Most large applications naturally break down into a collection of parallel activities (processes or tasks) regardless of the computer they are destined to run on. (Transparent multiprocessing is, in fact, based on the recognition and exploitation of this natural tendency.) So in practice, most 432 applications lend themselves to effective utilization of transparent multiprocessing as a matter of course. Furthermore, when programmers know that multiple processors are available, they can often design algorithms that consciously exploit the parallel processing capabilities of the system.

The second limitation is the ability of the application's hardware configuration to keep the processors running at full speed. The throughput increment obtained by adding a processor can be constrained by memory bandwidth and latency. Accordingly the 432 permits wide latitude in the design of the memory system as well as the processor/ memory interconnect.

#### DISTRIBUTED INPUT/OUTPUT

In much the same way that 432 computing power is adjustable by varying the number of GDPs in the system, 432 I/O power is a function of the number of peripheral subsystems attached to the central system. Since each peripheral subsystem is an independent computer, I/O capacity is variable along another dimension according to the character (i.e., hardware configuration) of each peripheral subsystem. Additional terminals could be added to a system, for example, either by attaching them to existing subsystems with excess capacity, or by incorporating them in a new peripheral subsystem.

The central system (via an interface processor) presents a very general physical and logical interface to a peripheral subsystem. This encourages the design of different specialized peripheral subsystems that perform critical operations optimally. It also permits many existing systems to be attached to the 432 with a minimum of modification to hardware and software. Finally, the general interface simplifies the modification of a peripheral subsystem — to take advantage of improved technology, for example — and helps to insure that the changes are localized within the subsystem.

The 432 relies on the intelligence of peripheral subsystems to absorb the great majority of processing required to support I/O transfers. Distributing responsibility in this way allows multiple I/O operations to proceed in parallel with each other, and with computation and data processing operations running in the central system. A system's aggregate I/O capacity is subject to the normal limitations imposed by memory latency and bandwidth.

#### FUTURE PERFORMANCE

The 432 has been explicitly designed to provide improved performance in the future while maintaining the overall system framework described in this book. The classic precipitator of a new generation is the "running out of memory" syndrome that has been repeated again and again in microcomputers, minicomputers and mainframes alike. With 16 megabytes of real memory space and a trillion of virtual, the 432 moves this traditional barrier far into the future.

To further extend its useful lifetime, the 432 anticipates continuing semiconductor technology advances by carefully distinguishing between *architecture* and *implementation*. On-chip registers, caches, stack pointers and so on have been made invisible because they are implementation features designed to provide speed, rather than function. Any or all of them can be redesigned to obtain better performance without affecting the machine as seen by a compiler — its architecture.

The 432 is also designed to permit new processors to be neatly integrated into the present family. The GDP and the IP are distinct functionally specialized processor extensions to the 432 *common base* architecture. As experience with the product line grows and new market needs develop, additional compatible processor types can be built to extend the common base architecture in other directions.

### THE SOFTWARE MANAGEMENT CHALLENGE

Experience with mainframe-based programs has shown repeatedly that large software systems are among the most difficult engineering projects that men and women undertake. The large system that is delivered on schedule, within budget, and with performance as promised, is a rarity. Systems that involve real-time or concurrent processing — the norm in microcomputer applications are even more challenging. Finally, successfully modifying or extending large systems has proven so difficult that many organizations spend well over half their budgets for software "maintenance."

Microprocessor users were originally spared the problems of large-scale programming because the earlier machines simply could not support large systems. The introduction of 16-bit machines, however, brought multi-person projects producing upwards of 100,000 lines of source code. To develop a system that exploits the power of a 32-bit microcomputer system in a timely manner will require multiple *teams* of programmers working in parallel. They will develop software that is orders of magnitude larger and more complex than anything ever written for an 8-bit machine. In this new era, managing software size and complexity becomes as critical to project success as discovering and expressing the algorithms that direct the operation of the end product.

The essence of the problem is that complexity increases exponentially with size: it is far easier to write 50 programs of 1,000 lines each than to write a single system of 50,000 lines. While limited address spaces and processing power made early microcomputer-based systems small by definition, machines like the 432 make it possible to build very large systems indeed. To learn from the mainframe experience, rather than repeat it, new tools are needed to reduce complexity where possible, and to otherwise actively manage it.

Addressing the challenge of reducing and managing software complexity, the 432 provides innovations at four levels: first, a machine that is an efficient target for high level language compilers; second, a language explicitly designed for building large systems of programs; third, an executive that provides a "catalog" of widely-applicable core functions that can be selected, extended and modified according to local requirements. Finally, the 432 has been designed from the ground up to support concurrent programming and concurrent execution.

A given program can be written, tested and modified faster in a high level programming language than in an assembly language. The basic concept at work here is simplification: a high level language removes the attributes (and idiosyncracies) of the computer from the programmer's "problem set." The language replaces memory locations. registers, addressing modes and so on, with high level constructs: data structures (such as arrays, records and lists) and control structures (like loops and selection statements) that have been designed to promote the natural and correct expression of problem solutions.

High level languages have been accepted somewhat slowly in microcomputer-based systems primarily because the tradeoff between programming costs and manufacturing costs has often favored assembly language. Memory still dominates the cost of microcomputer system hardware; a compiler for a typical microcomputer will generally produce a larger program than will a skilled assembly language programmer. A larger program generally means slower execution, so to achieve comparable performance, a system programmed in a high level language will require faster (and more expensive) hardware. For applications that are comparatively small and that are produced in high volumes (e.g., those based on single-chip microcomputers), assembly language will continue to make sense. For very large applications, such as those made possible by a 32-bit microcomputer system, high level programming is a practical necessity, since every effort must be made to reduce the complexity of the programming task. For applications in the middle ground, the costs must be weighed case by case. Of course as labor and hardware costs continue their opposing trends, the balance will increasingly tip in favor of high level languages.

#### COMPILER-ORIENTED MACHINE

To make high level programming economically sensible for all 432-based products, the 432 general data processor has been designed to favor code generation by *compilers* rather than assembly language programmers. The machine itself makes it possible for straightforward, non-optimizing compilers to generate code that approaches assembly language programming in size and speed. The strength of this commitment to high level languages, and the success of the design, is indicated by the fact that Intel does not supply an assembler for the GDP, nor is one used inhouse. The portion of the iMAX executive that runs on GDPs, for example, is written entirely in Ada.

There are no visible registers in the GDP; all instruction operands are memory-based. A good assembly language programmer regards registers as high-speed local storage which can be exploited by considering the run-time behavior of the program being written. A compiler, on the other hand, has no knowledge of the run-time behavior of the program it is translating; to it, registers present not so much an opportunity for optimization as a scarce resource which must be managed. Registers *are* used internally in the GDP to improve performance. By keeping registers "behind the scenes," rather than as visible features of the architecture, the GDP reduces compiler complexity. Moreover, new registers can be added to future GDPs to enhance performance without impacting existing software.

The GDP promotes the generation of fast, compact code by requiring fewer machine instructions per high level statement. A compiler for a typical computer must generate several machine instructions to implement each high level language statement. In contrast, the 432's instruction set (in conjunction with its data types and addressing modes) matches typical high level statements on a one-for-one basis (see table 6). A compiler for the 432 simply generates the "obvious" machine instruction(s).

In addition to requiring fewer machine instructions, 432 programs are also made more compact by the instruction encoding technique. As in many modern computers, the instructions that occur most often are shorter in length

#### THE SOFTWARE MANAGEMENT CHALLENGE

|                    | Ada Statement and Interpretation (1)                                                                                                                                         | 432<br>Machine<br>Instructions | Conventional<br>Machine<br>Instructions <sup>(2)</sup> |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------|

| E := F;            | assign simple variable (scalar) F to simple variable E.                                                                                                                      | 1 (MOVE)                       | 2                                                      |

| A(I) := X.B;       | - – assign element B of record X to I'th element of vector $-$ –A.                                                                                                           | 1 (MOVE)                       | 3                                                      |

| A(I) := A(I) + C;  | increment I'th element of vector A by value of simplevariable C.                                                                                                             | 1 (ADD)                        | 4                                                      |

| X.B := C/D(I);     | <ul> <li>- divide simple variable C by I'th element of vector</li> <li>-D, and assign result to element B of record A.</li> </ul>                                            | 1 (DIVIDE)                     | 4                                                      |

| A(I) := X.B-(E*F); | <ul> <li>-multiply simple variables E and F, subtract the result</li> <li>-from element B of record X, and assign the result to<br/>the I'th element of vector A.</li> </ul> |                                | 7                                                      |

#### NOTES:

<sup>1</sup>Assume A..F are variables of the same type (e.g., all integers or all reals) and that the value of l is in the range 0..65,535.

<sup>(2)</sup>Assume a typical register-oriented computer. For example, the instructions required to implement A(I) := A(I) + C might be:

| reg1, I       |

|---------------|

| reg2, A(reg1) |

| reg2, C       |

| A(reg1), reg2 |

|               |

#### Table 6. High Level Language Statements And Machine Instructions

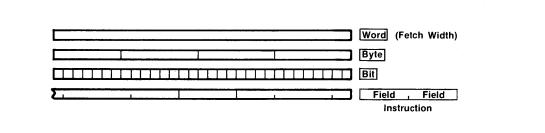

than those used less frequently (e.g., MOVE is shorter than SQUARE ROOT). Instruction references to top-ofstack operands are encoded implicitly; no bits are needed to specify the location of these operands. When a data item is used twice in the same instruction (e.g., A(I) := A(I) \* B), only a single reference is encoded in the instruction. Finally, instructions are encoded bitwise (see figure 9): each instruction consists of a variable number of variablelength bit fields. The shortest instructions are six bits long, while the longest are over 300 bits. Successive instructions are located immediately adjacent to one another in memory, irrespective of word or byte boundaries. (The processor fetches instructions in 32-bit words and extracts the bit fields internally.) There are no unused bits in the instruction stream, either within one instruction or between two instructions.

The GDP's register-free architecture, high level instructions, data types and addressing modes, and very dense instruction encoding substantially narrow the "efficiency gap" between compiler-generated and hand-coded

Figure 9. Bitwise Instruction Encoding programs. Straightforward, non-optimizing compilers will routinely produce code that approaches assembly language in efficiency. This in turn makes the benefits of high level programming economically practical for even high-volume 432 applications.

### MODULAR PROGRAMMING LANGUAGE

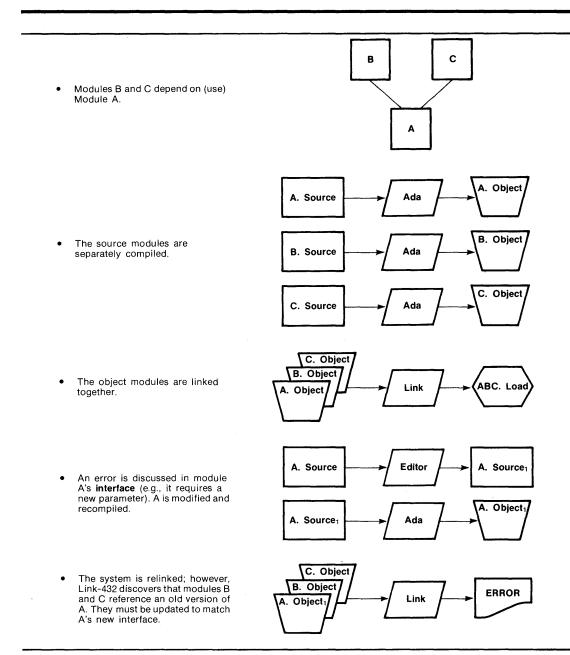

Large software systems are inherently complex; no one can fully understand a system of 100,000 lines. Nor is there time for one person to develop a large system. As a result, large systems are classically developed according to a "divide and conquer" strategy. The large problem is divided into smaller independent subproblems that can be parceled out to teams and individuals. The subsolutions are developed in parallel and are integrated into a single solution that solves the whole problem. In a similar vein, large software systems are usually modified (corrected or extended) by identifying the part(s) of the system to be altered or added, making the changes and additions, and then reintegrating the old, new, and modified parts to produce a new version of the whole system.

The parts into which a system is decomposed, both for initial development and later modification, are called modules. A module may be compiled independently of other modules, and provides a service that other modules can call upon. Modular programming has been practiced in various forms for many years; its goal is to make the

#### THE SOFTWARE MANAGEMENT CHALLENGE

inherent complexity of a large system *manageable* by dividing the system into units that can be considered *independently*, that is, in isolation from the rest of the system. In theory, a programmer can then develop or modify a module without affecting — or even understanding — the rest of the system. Thus, in a modular system, it should be possible to:

- develop modules separately and in parallel with the assurance that they will fit together;

- quickly identify the module that is the source of a bug;

- introduce a new module into the system without jeopardizing what already exists;

- change one module without changing any others.

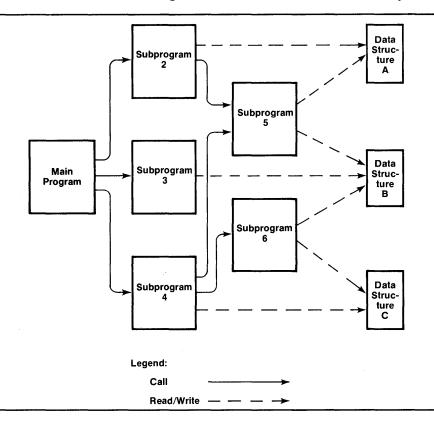

Subprogram-based System Organization

Figure 10.

In practice, these goals have been discouragingly elusive. Figure 10 illustrates a conventional decomposition in which

a module is a subprogram (e.g., a procedure) that performs a well-defined function. This "decomposition by function" is encouraged by most languages whose only support for modular programming is the ability to compile subprograms independently. With this approach, data is considered of secondary importance to algorithms; the data is typically defined "as needed" to make the algorithms work. As a result, systems designed in this manner usually contain a number of global data structures that are accessed by many different modules.

Modules that share access to a data structure violate the basic intent of modular design: they are made *interdependent* by virtue of their mutual dependence on the data structure. What are the consequences of this interdependence? First, programmers writing modules that share a data structure must coordinate the detailed definition of the structure and any changes made to it as the development progresses. Second, damage discovered in a data structure can be attributable to any of the modules that have access to it. Third, a new module that accesses a shared data structure threatens all other modules that use that structure. Fourth, a change in the way one module uses the data structure can necessitate changing some (it can be difficult to tell which) or all of the other modules that use it.

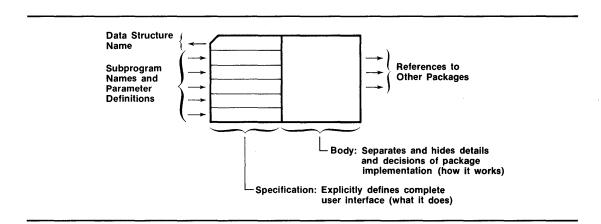

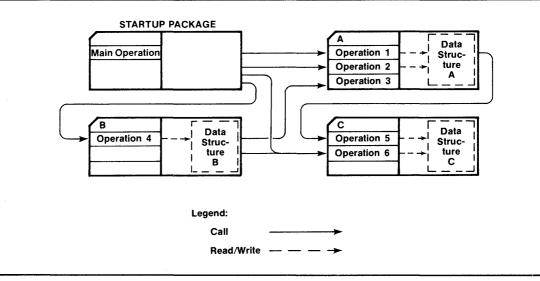

Recognizing the importance of modular programming as well as the shortcomings of past methodologies and tools, Ada defines a new kind of module as an inherent element of the language. This module is called a *package* (see figure 11), and is the basis for an integrated approach to modular programming. (This section concentrates on describing the *effects* of package-based program structure; more information on packages *per se* is provided in the *Software Engineer's Perspective.*)

A package defines both a data structure and a set of operations on that data structure. (Note that a "data structure" can represent an I/O channel, a bank account, or any other type of "thing" managed by the application.) An operation is written as an ordinary procedure or

#### THE SOFTWARE MANAGEMENT CHALLENGE

Figure 11. General Form Of A Package function that can be called to perform a service related to the package's data structure. In a banking application, for example, there might be a package that manages a data structure representing a bank account; this package might provide operations such as open new account, close existing account, debit account, credit account, report account balance, and so on. A file-handling package might provide read, write, and close operations. The (static) organization of a system's software is a network of packages that call each other's operations, as shown in figure 12.