# intel

# 82720 GRAPHICS DISPLAY CONTROLLER

- Displays Low-to-High Resolution Images

- Draws Characters, Points, Lines, Arcs, and Rectangles

- Supports Monochrome, Gray Scale, or Color Displays

- Zooms, Pans and Windows Through a 4 Mpixel Display Memory

- Extremely Flexible Programmable Screen Display, Blanking, and Sync Formats

- Compatible with Intel's Microprocessor Families

- High-Level Commands Off Load Host Processor from Bit Map Loading and Screen Refresh Tasks

- Supports Graphics, Character, and Mixed Display Modes

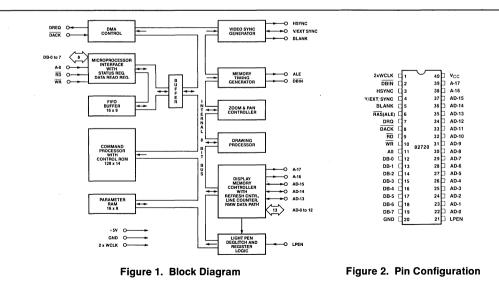

### FUNCTIONAL DESCRIPTION

#### Introduction

The 82720 Graphics Display Controller (GDC) is an intelligent microprocessor peripheral designed to drive highperformance raster-scan computer graphics and character CRT displays. Positioned between the video display memory and Intel microprocessor bus, the GDC performs the tasks needed to generate the raster display and manage the display memory. Processor software overhead is minimized by the GDC's sophisticated instruction set, graphics figure drawing, and DMA transfer capabilities. The display memory directly supported by the GDC can be configured in any number of formats and sizes up to 256K 16-bit words. The display can be zoomed and partitioned screen areas can be independently scrolled and panned. With its light pen input and multiple controller capability, the GDC is ideal for most computer graphics applications. Systems implemented with the GDC can be designed to be compatible with standards such as VDI, NAPLPS, GKS, Core, or custom implementations.

Intel Corporation Assumed No Responsibility for the Use of Any Circuitry Other Than Circuitry Embodied in an Intel Product. No Other Circuit Patent Licenses are Implied. Information contained herein supersedes previously published specifications on these devices from Intel.

| Table | 1. | Pin | Description |

|-------|----|-----|-------------|

|                                                                                                                                                                                                                                                                |                                                                                  | <b></b> |                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                                                                                                                                                                                                                                         | Pin No.                                                                          | Туре    | Name and Description                                                                                                                                                                                               |

| 2XWCLK                                                                                                                                                                                                                                                         | 1                                                                                | 1       | Clock Input                                                                                                                                                                                                        |

| DBIN                                                                                                                                                                                                                                                           | 2                                                                                | 0       | Display Bus Input: Read strobe output used to read display memory data into the GDC.                                                                                                                               |

| HSYNC                                                                                                                                                                                                                                                          | 3                                                                                | 0       | Horizontal Sync: Output used to initiate the horizontal retrace of the CRT display.                                                                                                                                |

| V/EXT<br>SYNC                                                                                                                                                                                                                                                  | 4                                                                                | I/O     | Vertical Sync: Output used to initiate the vertical retrace of the CRT display. In slave mode, this pin is an input used to synchronize the GDC with the master raster timing device.                              |

| BLANK                                                                                                                                                                                                                                                          | 5                                                                                | 0       | Blank: Output used to suppress the video signal.                                                                                                                                                                   |

| RAS (ALE)                                                                                                                                                                                                                                                      | 6                                                                                | 0       | Row Address Strobe (Address Latch Enable): Output used to start the control timing chain when used with dynamic RAMs. When used with static RAMs, this signal is used to demultiplex the display address/data bus. |

| DRQ                                                                                                                                                                                                                                                            | 7                                                                                | 0       | <b>DMA Request:</b> Output used to request a DMA transfer from a DMA controller (8237) or I/O processor (8089).                                                                                                    |

| DACK                                                                                                                                                                                                                                                           | 8                                                                                | I       | DMA Acknowledge: Input used to acknowledge a DMA transfer from a DMA controller<br>or I/O processor.                                                                                                               |

| RD                                                                                                                                                                                                                                                             | 9                                                                                | 1       | Read: Input used to strobe GDC Data into the microprocessor.                                                                                                                                                       |

| WR                                                                                                                                                                                                                                                             | 10                                                                               | 1       | Write: Input used to strobe microprocessor data into the GDC.                                                                                                                                                      |

| A0                                                                                                                                                                                                                                                             | 11                                                                               | i       | Register Address: Input used to select between commands and data read or written.                                                                                                                                  |

| DB0                                                                                                                                                                                                                                                            | 12                                                                               | ı/O     | Bidirectional Microprocessor Data Bus Line: Input enabled by WR. Output enabled by RD.                                                                                                                             |

| DB1<br>DB2<br>DB3<br>DB4<br>DB5<br>DB6<br>DB7                                                                                                                                                                                                                  | 13<br>14<br>15<br>16<br>17<br>18<br>19                                           |         |                                                                                                                                                                                                                    |

| GND                                                                                                                                                                                                                                                            | 20                                                                               |         | Ground.                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                | 40                                                                               |         | + 5V Power Supply                                                                                                                                                                                                  |

| V <sub>CC</sub><br>A <sub>17</sub>                                                                                                                                                                                                                             | 39                                                                               | 0       | Graphics Mode: Display Address Bit 17 Output<br>Character Mode: Cursor and Line Counter Bit 4 Output<br>Mixed Mode: Cursor and Image Mode Flag                                                                     |

| A <sub>16</sub>                                                                                                                                                                                                                                                | 38                                                                               | 0       | Graphics Mode: Display Address Bit 16 Output<br>Character Mode: Line Counter Bit 3 Output<br>Mixed Mode: Attribute Blink and Line Counter Reset                                                                    |

| AD <sub>15</sub><br>AD <sub>14</sub><br>AD <sub>13</sub>                                                                                                                                                                                                       | 37<br>36<br>35                                                                   | I/O     | Graphics Mode: Display Address/Data Bits 13–15<br>Character Mode: Line Counter Bits 0–2 Output<br>Mixed Mode: Display Address/Data Bits 13–15                                                                      |

| AD <sub>12</sub><br>AD <sub>11</sub><br>AD <sub>10</sub><br>AD <sub>9</sub><br>AD <sub>8</sub><br>AD <sub>7</sub><br>AD <sub>6</sub><br>AD <sub>5</sub><br>AD <sub>4</sub><br>AD <sub>3</sub><br>AD <sub>2</sub><br>AD <sub>1</sub><br>AD <sub>0</sub><br>LPEN | 34<br>33<br>32<br>31<br>30<br>29<br>28<br>27<br>26<br>25<br>24<br>23<br>22<br>22 | 1/0     | Display Address/Data Bits 0–12                                                                                                                                                                                     |

| LPEN                                                                                                                                                                                                                                                           | 21                                                                               |         | Light Pen Detect Input                                                                                                                                                                                             |

### FUNCTIONAL DESCRIPTION (Continued)

#### **Microprocessor Bus Interface**

Control of the GDC by the system microprocessor is achieved through an 8-bit bidirectional interface. The status register is readable at any time. Access to the FIFO buffer is coordinated through flags in the status register.

### **Command Processor**

The contents of the FIFO are interpreted by the command processor. The command bytes are decoded, and the succeeding parameters are distributed to their proper destinations within the GDC. The bus interface has priority over the command processor when both access the FIFO simultaneously.

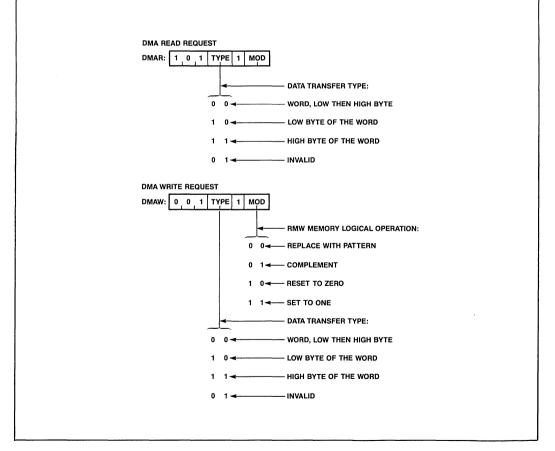

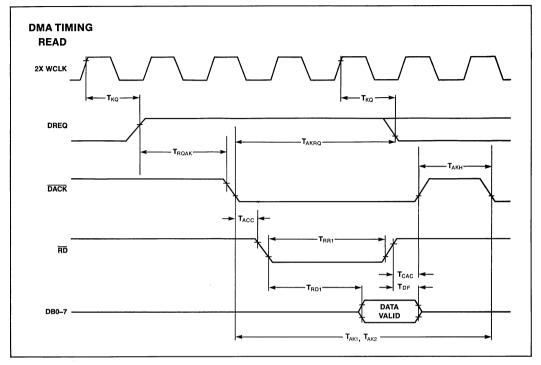

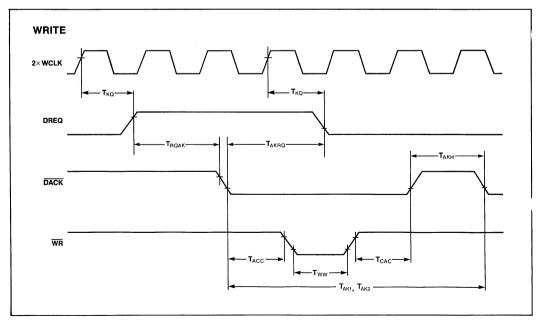

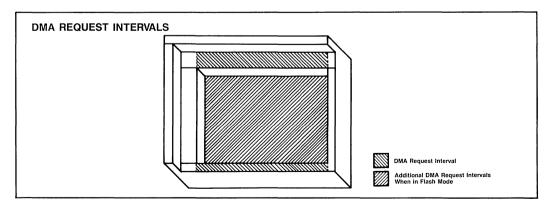

### **DMA** Control

The DMA Control circuitry in the GDC coordinates data transfers when using an external DMA controller. The DMA Request and Acknowledge handshake lines interface with an 8257 or 8237 DMA controller or 8089 I/O processor, so that display data can be moved between the microprocessor memory and the display memory.

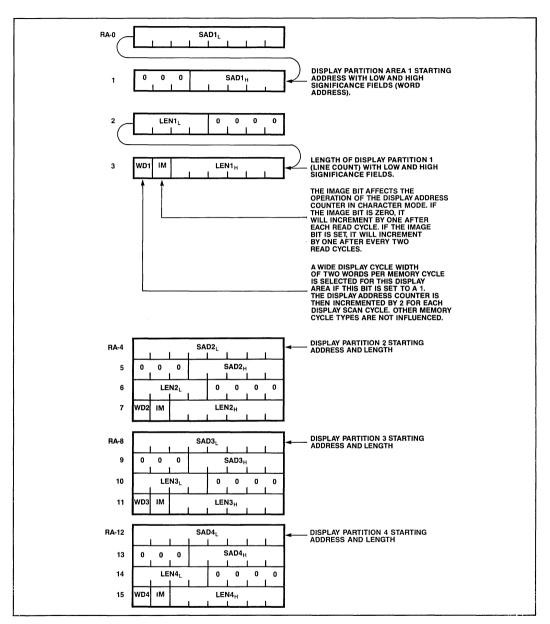

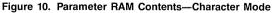

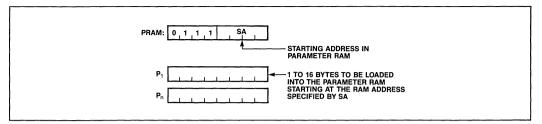

### Parameter RAM

The 16-byte RAM stores parameters that are used repetitively during the display and drawing processes. In character mode, the RAM holds the partitioned display area parameters. In graphics mode, the RAM also holds the drawing pattern and graphics character.

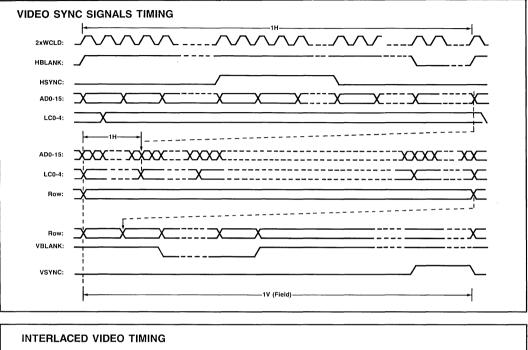

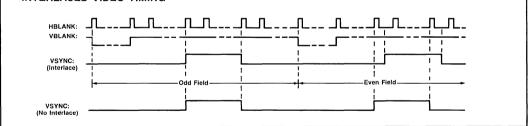

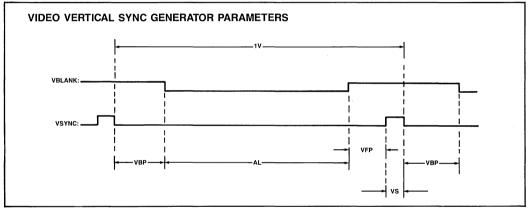

### Video Sync Generator

Based on the clock input, the sync logic generates the raster timing signals for almost any interlaced, non-interlaced, or "repeat field" interlaced video format. The generator is programmed during the idle period following a reset. In video sync slave mode, it coordinates timing between the GDC and another video source.

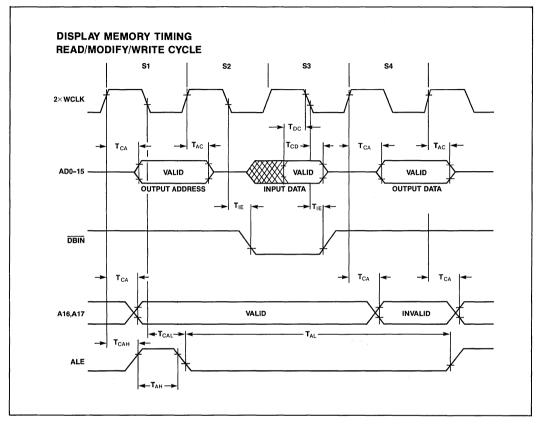

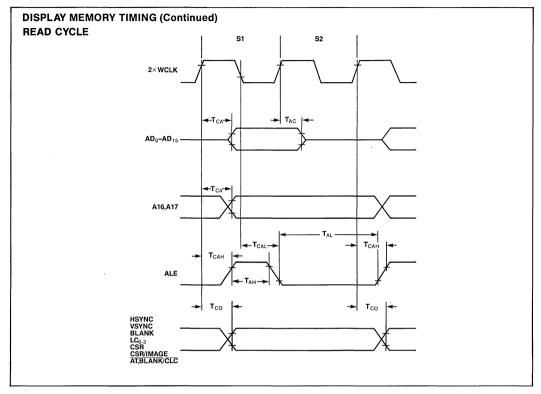

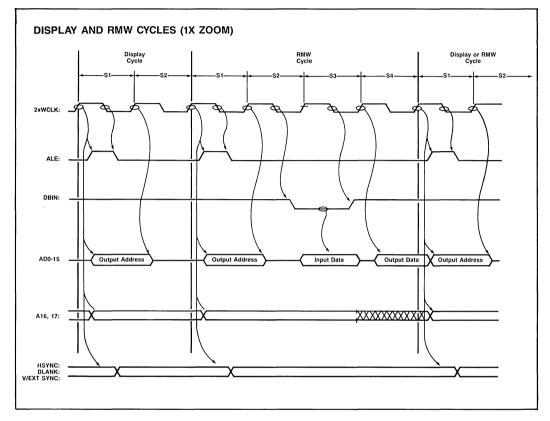

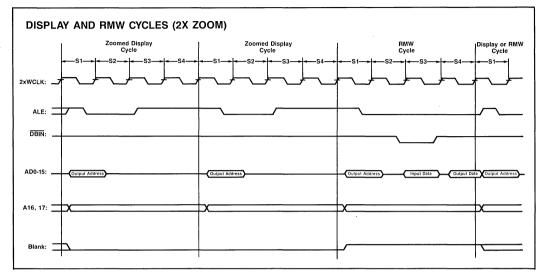

### **Memory Timing Generator**

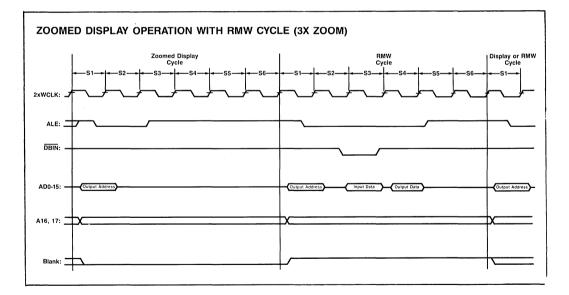

The memory timing circuitry provides two memory cycle types: a two-clock period refresh cycle and the read-modify-write (RMW) cycle which takes four clock periods. The memory control signals needed to drive the display memory devices are easily generated from the GDC's RAS(ALE) and DBIN outputs.

### Zoom and Pan Controller

Based on the programmable zoom display factor and the display area parameters in the parameter RAM, the zoom and pan controller determines when to advance to the next memory address for display refresh and when to go on to the next display area. A horizontal zoom is produced by slowing down the display refresh rate while maintaining the video sync rates. Vertical zoom is accomplished by repeatedly accessing each line a number of times equal to the horizontal repeat. Once the line count for a display area is exhausted, the controller accesses the starting address and line count of the next display area from the parameter RAM. The system microprocessor, by modifying a display area starting address, allows panning in any direction, independent of the other display areas.

### **Drawing Processor**

The drawing processor contains the logic necessary to calculate the addresses and positions of the pixels of the various graphics figures. Given a starting point and the appropriate drawing parameters, the drawing processor needs no further assistance to complete the figure drawing.

### **Display Memory Controller**

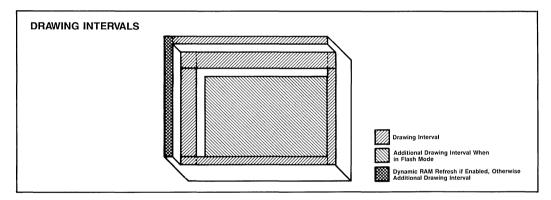

The display memory controller's tasks are numerous. Its primary purpose is to multiplex the address and data information in and out of the display memory. It also contains the 16-bit logic units used to modify the display memory contents during RMW cycles, the character mode line counter, and the refresh counter for dynamic RAMs. The memory controller apportions the video field time between the various types of cycles.

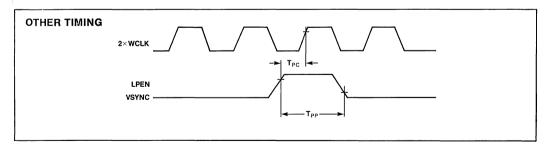

### Light Pen Debouncer

Only if two rising edges on the light pen input occur at the same point during successive video fields are the pulses accepted as a valid light pen detection. A status bit indicates to the system microprocessor that the light pen register contains a valid address.

### System Operation

The GDC is designed to work with Intel microprocessors to implement high-performance computer graphics systems. System efficiency is maximized through partitioning and a pipelined architecture. At the lowest level, the GDC generates the basic video raster timing, including sync and blanking signals. Partitioned areas on the screen and zooming are also accomplished at this level. At the next level, video display memory is modified during the figure drawing operations and data moves. Third, display memory address are calculated pixel by pixel as drawing progresses. Outside the GDC at the next level, preliminary calculations are done to prepare drawing parameters. At the fifth level, the picture must be represented as a list of graphics figures drawable by the GDC. Finally, this representation must be manipulated, stored and communicated. The GDC takes care of the high-speed and repetitive tasks required to implement graphics systems.

### **GENERAL OVERVIEW**

In order to minimize system bus loading, the 82720 uses a private video memory for storage of the video image. Up to 512K bytes of video memory can be directly supported. For example, this is sufficient capacity to store a 2048  $\times$  2048 pixel  $\times$  1 bit image. Images can be generated on the screen by:

- -Drawing Commands

- -Program-Controlled Transfers

- -DMA Transfers from System Memory

The 82720 can be configured to support a wide variety of graphics applications. It can support:

- -High Dot Rates

- -Color Planes

- -Horizontal Split Screen

- -Character-oriented Displays

- -Multiplexed Graphic and Character Display

#### **GRAPHIC DISPLAY CONFIGURATIONS**

The 82720 provides the flexibility to handle a wide variety of graphic applications. This flexibility results from having its own private video memory for storage of the graphics image. The organization of this memory determines the performance, the number of bits/pixel and the size of the display. Several different video memory organizations are examined in the following paragraphs.

In the simplest 82720 system, the memory can store up to a 2048  $\times$  2048  $\times$  1 bit image. It can display a 1024  $\times$  1024  $\times$  1 bit section of the image at a maximum dot rate of 44 MHz, or 88 MHz in wide mode. In this configuration, only 1 bit/pixel is used.

By partitioning the memory into multiple banks, color, gray scale and higher bandwidth displays can be supported. By adding various amounts of external logic, many cost/performance tradeoffs for both display and drawing are realizable.

The video memory can be partitioned into 4 banks, each 1024 x 1024 bits. By selecting all 4 memory banks during display, 4 bits/pixel can be provided by a single 82720. Each bank of video memory contributes 1 bit to each pixel. This configuration can support color monitors, again with a maximum dot shift rate of 44 or 88 MHz.

Higher performance may be achieved by using multiple 82720s. Multiple 82720s can be used to support multiple display windows, increased drawing speed, or increased bits per pixel. For display windows, each 82720 controls one window of the display. For increased drawing speed, multiple 82720s are operated in parallel. For increased bits/pixel, each 82720 contributes a portion of the number of bits necessary for a pixel.

#### **CHARACTER DISPLAY CONFIGURATION**

Although the 82720 is intended primarily for rasterscan graphics, it can be used as a character display controller. The 82720 can support up to 8K by 13 bits of private video memory in this configuration (1 character = 13 bits). This is sufficient memory to store 4 screens of data containing 25 rows by 80 characters. The 82720 can display up to 256 characters per row. Smooth vertical scrolling of each of 4 independent display partitions is also supported.

#### MIXED DISPLAY CONFIGURATION

The GDC can support a mixed display system for both graphic and character information. This capability allows the display screen to be partitioned between graphic and character data. It is possible to switch between one graphic display window and one character display window with raster line resolution. A maximum of 256K bytes of video memory is supported in this mode: half is for graphic data, half is for character data. In graphic mode, a one megapixel image can be stored and displayed. In character mode, 64K, 16-bit characters can be stored.

### **DETAILED OPERATIONAL DESCRIPTION**

The GDC can be used in one of three basic modes —Graphics Mode, Character Mode and Mixed Mode. This section of the data sheet describes the following for each mode:

- 1. Memory organization

- 2. Display timing

- 3. Special Display functions

- 4. Drawing and writing

#### **Graphics Mode Memory Organization**

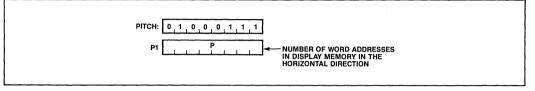

The Display Memory is organized into 16-bit words (32-bit words in wide mode). Since the display memory can be larger than the CRT display itself, two width parameters must be specified: display memory width and display width. The Display width (in words) is selected by a parameter of the Reset command. The Display memory width (in words) is selected by a parameter of the Pitch command. The height of the Display memory can be larger than the display itself. The height of the Display is selected by a parameter of the Reset command. The height of the Display is selected by a parameter of the Reset command. The height of the Display is selected by a parameter of the Reset command. The GDC can directly address up to 4Mbits (0.5Mbytes) of display RAM in graphics mode.

#### **Graphics Mode Display Timing**

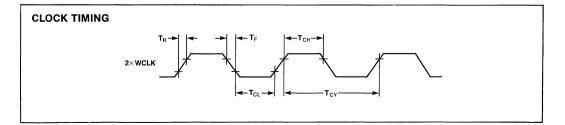

All raster blanking and display timings of the GDC are a function of the input clock frequency. Sixteen or 32 bits of data are read from the RAM and loaded into a shift register in each two clock period display cycle. The Address and Data busses of the GDC are multiplexed. In the first part of the cycle, the address of the word to be read is latched into an external demultiplexer. In the second part of the cycle the data is read from the RAM and loaded into the shift register. Since all 16 (32) bits of data are to be displayed, the dot clock is 8 × (16 ×) the GDC clock or 16 × (32 ×) the Read cycle rate.

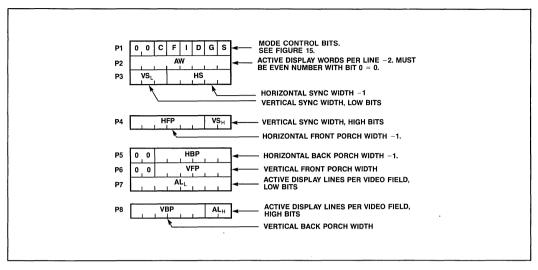

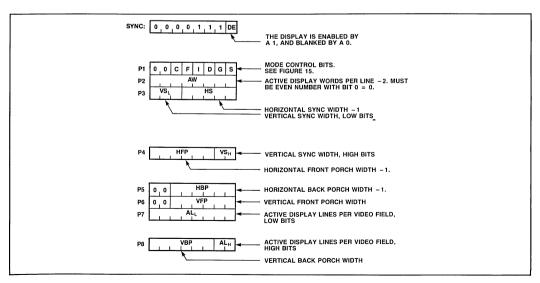

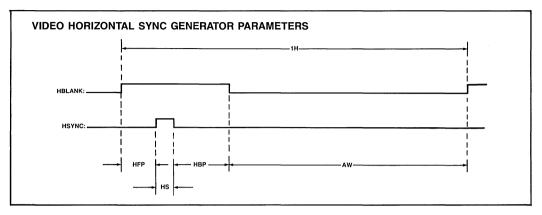

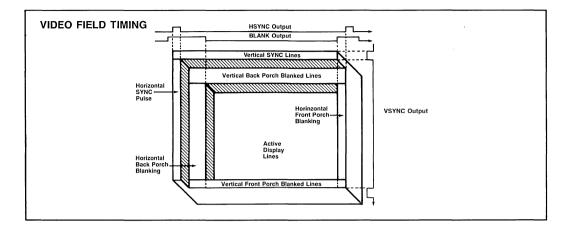

Parameters of the Reset or Sync command determine the horizontal and vertical front porch, sync pulse, and back porch timings. Horizontal parameters are specified as multiples of the display cycle time, and vertical parameters as a multiple of the line time.

Another Reset command parameter selects interlaced or non-interlaced mode. A bit in the parameter RAM can define Wide Display Mode. In this mode, while data is being sent to the screen, the display address counter is incremented by two rather than one. This allows the display memory to be configured to deliver 32 bits from each display read cycle.

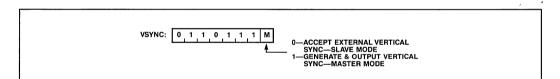

The V Sync command specifies whether the V Sync Pin is an input or an output. If the V Sync Pin is an output, the GDC generates the raster timing for the display and other CRT controllers can be synchronized to it. If the V Sync pin is an input, the GDC can be synchronized to any external vertical Sync signal.

#### **Graphics Mode Special Display Functions:**

#### WINDOWING

The GDC's Graphics Mode Display can be divided into two windows on the screen, upper and lower. The windows are defined by parameters written into the GDC's parameter RAM. Each window is specified by a starting address and a window length in lines. If the second window is not used, the first window parameters should be specified to be the same as the active display length.

#### ZOOMING

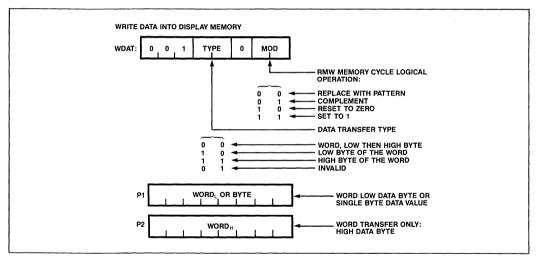

A parameter of the GDC's zoom command allows zooming by effectively increasing the size of the dots on the screen. This is accomplished vertically by repeating the same display line. The number of times it is repeated is determined by the display zoom factor parameter. Horizontally, zoom is accomplished by extending each display word cycle and displaying fewer words per line, according to the zoom factor. It is the responsibility of the microprocessor controlling the GDC to provide the shift register clock circuitry with the zoom factor required to slow down the shift registers to the appropriate speed. The frequency of the 2XWCLK should not be changed. The zoom factor must be set to a known state upon initialization.

#### PANNING

Panning is accomplished by changing the starting address of the display window. In this way, panning is possible in any direction, vertically on a line by line basis and horizontally on a word by word basis.

#### **Graphics Mode Drawing and Writing**

The GDC can draw solid or patterned lines, arcs, circles, rectangles, slanted rectangles, characters, slanted characters, filled rectangles. Direct access to the bit map is also provided via the DMA Commands and the Read or Write data commands.

#### MEMORY MODIFICATION

All drawing and writing functions take place at the location in the display RAM specified by the cursor. The cursor is not displayed in Graphics Mode. The cursor location is modified by the execution of drawing, reading or writing commands. The cursor will move to the bit following the last bit accessed.

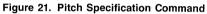

Each bit is drawn by executing a Read-Modify-Write cycle on the display RAM. These R/M/W cycles normally require four 2XWCLK cycles to execute. If the display zoom factor is greater than two, each R/M/W cycle will be extended to the width of a display cycle. Write Data (WDAT), Read Data (RDAT), DMA write (DMAW) and DMA read (DMAR) commands can be used to examine or modify one to 16 bits in each word during each R/M/W cycle. All other graphics drawing commands modify one bit per R/M/W cycle.

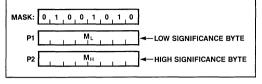

An internal 16-bit Mask register determines which bit(s) in the accessed word are to be modified. A one in the Mask register allows the corresponding bit in the display RAM to be modified by the R/M/W cycle. A zero in the Mask register prevents the GDC from modifying the corresponding bit in the display RAM.

The mask must be set by the Mask Command prior to issuing the WDAT or DMAW command. The Mask register is automatically set by the CURS command and manipulated by the graphics commands.

The display RAM bits can be modified in one of four ways. They can be set to 1, reset to 0, complemented or replaced by a pattern.

When replace by a pattern mode is selected, lines, arcs and rectangles will be drawn using the 16-bit pattern in parameter RAM bytes 8 and 9.

In set, reset, or complement mode, parameter RAM bytes 8 and 9 act as another level of masking for line arc and rectangle drawing. As each 16-bit segment of the line or arc is drawn, it is checked against the pattern in the parameter RAM. If the pattern RAM bit is a one, the display RAM bit will be set, reset, or complemented per the proper modes. If the pattern RAM bit is a zero, the display RAM bit won't be modified.

When replace by pattern mode is selected, the graphics character and fill commands will cause the 8 x 8 pattern in parameter RAM bytes 8 to 15 to be written directly into the display RAM in the appropriate locations.

In set, reset, or complement mode, the 8 x 8 pattern in parameter RAM bytes 8 to 15 act as a mask pattern for graphics character or fill commands. If the appropriate parameter RAM bit is set, the display RAM bit will be modified. If the parameter RAM bit is zero, the display RAM bit will not be modified. These modes are selected by issuing a WDAT command without parameters before issuing graphics commands. The pattern in the parameter RAM has no effect on WDAT, RDAT, DMAW, or DMAR operations.

#### **READING AND DRAWING COMMANDS**

After the modification mode has been set and the parameter RAM has been loaded, the final drawing parameters are loaded via the figure specify (FIGS) command. The first parameter specifies the direction in which drawing will occur and the figure type to be drawn. This parameter is followed by one to five more parameters depending on the type of character to be drawn.

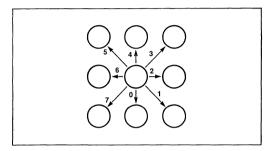

The direction parameter specifies one of eight octants in which the drawing or reading will occur. The effect of drawing direction on the various figure types is shown in Figure 9.

RDAT, WDAT, DMAR, and DMAW Operations move through the Display memory as shown in the "DMA" Column.

The other parameters required to set up figure reading or drawing are shown in Figure 3.

| DRAWING TYPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DC                    | D                          | D2                                             | D1            | DM      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------|------------------------------------------------|---------------|---------|

| INITIAL VALUE*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                     | 8                          | 8                                              | - 1           | - 1     |

| LINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $ \Delta \mathbf{I} $ | $2 \Delta D  -  \Delta I $ | $2( \Delta \mathbf{D}  -  \Delta \mathbf{I} )$ | $2 \Delta D $ | -       |

| ARC**                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | rsin ¢1               | r-1                        | 2(r – 1)                                       | - 1           | rsin θ1 |

| RECTANGLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                     | A-1                        | B – 1                                          | - 1           | A - 1   |

| AREA FILL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | B-1                   | Α                          | A                                              | -             |         |

| GRAPHIC<br>CHARACTER***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B-1                   | A                          | A                                              | -             | -       |

| WRITE DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | W – 1                 | _                          | -                                              | -             | -       |

| DMAW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D – 1                 | C-1                        | -                                              | -             | -       |

| DMAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D – 1                 | C-2                        | (C – 2)/2†                                     | -             | -       |

| READ DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | w                     | -                          | -                                              | -             | -       |

| <ul> <li>AREA FILLING IN WHICH B AND A ≤6. IF A = 8 THERE IS NO<br/>NEED TO LOAD D AND D2.</li> <li>WHERE:         <ul> <li>-1 = ALL ONES VALUE.</li> </ul> </li> <li>ALL ONES VALUE.</li> <li>ALL ONES VALUE.</li> </ul> <li>ALL NORS VALUE.</li> <li>ALL ONES VALUE.</li> <li>ALL ONES VALUE.</li> <li>- = NO PARAMETER BYTES SENT TO GDC FOR THIS PARAMETER.</li> <li>- = NO PARAMETER BYTES SENT TO GDC FOR THIS PARAMETER.</li> <li>- = NO PARAMETER BYTES SENT TO GDC FOR THIS PARAMETER.</li> <li>- = NO PARAMETER BYTES SENT TO GDC FOR THIS PARAMETER.</li> <li>- = NO UBS OF CURVATURE. IN PIXELS.</li> <li>Φ = ANGLE FROM MAJOR AXIS TO END OF THE ARC. Φ ≤45°.</li> <li>+ ROUND DY TO THE NEXT HIGHER INTEGER.</li> <li>A NUMBER OF PIXELS IN THE INITIALLY SPECIFIED DIRECTION.</li> <li>B = NUMBER OF PIXELS IN THE INITIALLY SPECIFIED DIRECTION.</li> <li>C = NUMBER OF FORDS TO BE ACCESSED.</li> <li>C = NUMBER OF WORDS TO BE ACCESSED.</li> <li>C = NUMBER OF WORDS TO BE ACCESSED.</li> <li>C = NUMBER OF THE IS SLECTED.</li> <li>D = NUMBER OF THE IS SLECTED.</li> <li>D = NUMBER OF THE ISSEL ST AN THE DIRECTION.</li> <li>TRANSFER MODE IS SELECTED.</li> <li>D = NUMBER OF THE INST TO BE TARASFERRED IN THE INITIALLY SPECIFIED DIRECTION.</li> <li>C = NUMBER OF THE INST TO BE ACCESSED.</li> <li>C = NUMBER OF THE INST TO BE ACCESSED.</li> <li>D = NUMBER OF THE INST TO BE ACCESSED.</li> <li>D = NUMBER OF THE INST THE INITIALLY SPECIFIED DIRECTION.</li> <li>D = NUMBER OF THE INST THE INITIALLY SPECIFIED DIRECTION.</li> <li>D = NUMBER OF NORDS TO BE ACCESSED.</li> <li>D = NUMBER OF THE INTERLY SPECIFIED DIRECTION.</li> |                       |                            |                                                |               |         |

Figure 3. Drawing Parameter Details

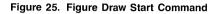

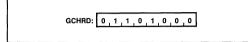

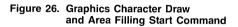

After the parameters have been set, line, arc, circle, rectangle or slanted rectangle drawing operations are initiated by the Figure Draw (FIGD) command. Character, slanted character, area fill and slanted area fill drawing operations are initiated by the Graphics Character Draw (GCHRD) command. DMA transfers are initiated by the DMA Read or Write (DMAR or DMAW) commands. Data Read Operations are initiated by the Read Data (RDAT) Command. Data Write Operations are initiated by writing a parameter after the WDAT command.

The area fill operation steps and repeats the  $8 \times 8$  graphics character pattern draw operation to fill a rectangular area. If the size of the rectangle is not an integral number of  $8 \times 8$  pixels, the GDC will automatically truncate the pattern at the edges furthest from the starting point.

The Graphics Character Drawing capability can be modified by the Graphics Character Write Zoom Factor (GCHR) parameter of the zoom command. The zoom write factor may be set from 1 to 16 (by using from 0 to 15 in the parameter). Each dot will be repeated in memory horizontally and vertically (adjusted for drawing direction) the number of times specified by the zoom factor.

The WDAT command can be used to rapidly fill large areas in memory with the same value. The mask is set to all 1's, and the least significant bit of the WDAT parameter replaces all bits of each word written.

### **Character Mode Memory Organization**

In character mode, the Display memory is organized into up to 8K characters of up to 13 bits each. Wide mode is also available for characters of up to 26 bits.

The display memory can be larger than the display itself. The display width (in characters) is a parameter of the reset command. The display memory width (in characters) is a parameter of the Pitch Command. The height of the display (in lines) is a parameter of the Reset Command. The display memory height is determined by dividing the number of display memory words by the pitch.

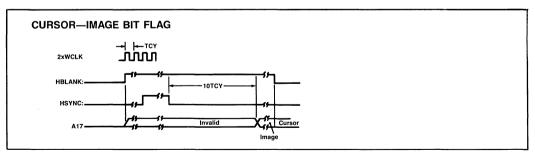

In character mode, the display works almost exactly as it does in graphics mode. The differences lie in the fact that data read from the display RAM is used to drive a character generator as well as attribute logic if desired. In Character mode, address bits 13–16 become line counter outputs used to select the proper line of the character generator, and the address 17 output becomes the cursor and line counter MSB output.

### **Character Mode Display Timing**

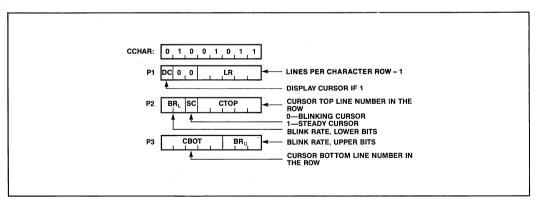

In character mode, the display timing works as it does in graphics mode. In addition, the Address 17 output becomes cursor output. The characteristics of the cursor are defined by parameters of the cursor and Character Characteristics (CCHAR) command. One bit allows the cursor output to be enabled or disabled. The height of the cursor is programmable by selecting the top and bottom line between which the cursor will appear. The blink rate is also programmable. The parameter selects the number of frame times that the cursor will be inactive and active, resulting in a 50% duty cycle cursor blinking at 2 × the period specified by the parameter.

The cursor output pin also provides the line counter bit 4 signal, which is valid 10 clocks after the trailing edge of HSYNC.

### Character Mode Special Display Functions

#### WINDOWING

The GDC's Character Mode display can be partitioned into one to four windows on the screen. The windows are defined by parameters written into the GDC's Parameter RAM. Each window is specified by a starting address and a window length in lines.

If windowing is not required, the first window length should be specified to be the same as the active display length.

#### ZOOMING AND PANNING

In character mode, zooming and pan handling commands function the same way as in Graphics Mode.

#### **Character Mode Drawing and Writing**

The GDC can read or write characters of up to 13 bits into or out of the Display RAM.

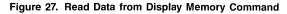

All reading and writing functions take place at the display RAM location specified by the cursor. The cursor location can be read by issuing the CURD command. The cursor can be moved anywhere within the display memory by the CURS command. The cursor location is also modified by the execution of character read or write commands.

Each character is written or read via a Read/Modify/Write cycle. The mask register contents determine which bit(s) in the character are modified. The mask register can be used to change character codes without modifying attribute bits or vice-versa. The Replace with pattern, Set, Reset and Complement modes work exactly as they do in graphics mode, with the exception that the parameter RAM Pattern is not used. The pattern used is a parameter of the WDAT command.

The Figure Specify (FIGS) command must be set to Character Display mode, as well as specify the direction the cursor will be moved by read or write data commands.

In character mode, the FIGD and GCHRD commands are not used.

### **Mixed Mode Memory Organization**

In mixed mode, the display memory is organized into two banks of up to 64K words of 16 bits each (32 bits in wide mode).

The display height and width are programmable by the same Reset or Sync command parameters as in the graphics and character modes. The display memory width (in words) is a parameter of the Pitch Command and the height of the display memory is determined by dividing the number of display memory words by the pitch.

An image mode signal is used to switch the external circuitry between graphics and character modes in two display windows.

In a graphics window, the GDC works as it does in pure graphics mode, but on a smaller total memory space (64K words vs 512K words).

In a character window, the GDC works as it does in pure character mode, but the line counter must be implemented externally. The counter is clocked by the horizontal sync pulse and reset by a signal supplied by the GDC.

In mixed mode, the GDC provides both a cursor and an attribute blink timing signal.

### **Mixed Mode Display Timing**

In mixed mode, each word in a graphic area is accessed twice in succession. The AW parameter of the Reset or Sync command should be set to twice its normal value, and the video shift register load signal must be suppressed during the extra access cycle.

In addition, A16 becomes a Multiplexed Attribute and Clear Line Counter signal and A17 becomes a multiplexed cursor and image mode signal. A16 provides an active high line counter reset signal which is valid 10 clocks after the trailing edge of HSYNC. During the active display line time, A16 provides blink timing for external attribute circuitry. This signal blinks at 1/2 the blink rate of the cursor with a 75% on, 25% off duty cycle. A17 provides a signal which selects between graphics or character display, which is also valid 10 clocks after the trailing edge of HSYNC. During the active display time, A17 provides the cursor signal. The cursor timing and characteristics are defined in exactly the same way as in pure character mode.

### **Mixed Mode Special Display Functions**

#### WINDOWING

The GDC supports two display windows in mixed mode. They can independently be programmed into either graphics or character mode determined by the state of two bits in the parameter RAM. The window location in display memory and size are also determined by parameters in the parameter RAM.

#### ZOOMING AND PANNING

In mixed mode, zooming and panning commands function the same as in graphics and character mode.

#### Mixed Mode Drawing and Writing

In mixed mode, the GDC can write or draw in exactly the same ways as in both graphics and character modes. In addition, the FIGS command has a parameter GD (Graphics Drawing Flag) which sets the image mode signal to select the proper RAM bank.

#### **DEVICE PROGRAMMING**

The GDC occupies two addresses on the system microprocessor bus through which the GDC's status register and FIFO are accessed. Commands and parameters are written into the GDC FIFO and are differentiated by address bit A0. The status register or the FIFO can be read as selected by the address line.

| A0 | READ            | WRITE               |

|----|-----------------|---------------------|

|    | STATUS REGISTER | PARAMETER INTO FIFO |

| •  |                 |                     |

|    | FIFO READ       | COMMAND INTO FIFO   |

| 1  |                 |                     |

Figure 4. GDC Microprocessor Bus Interface Registers

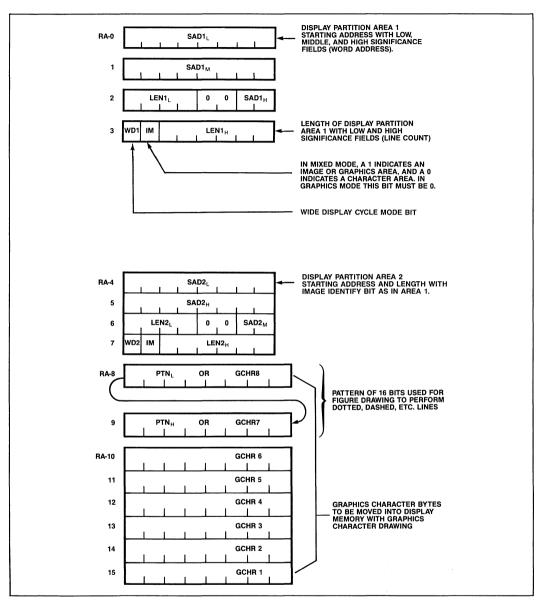

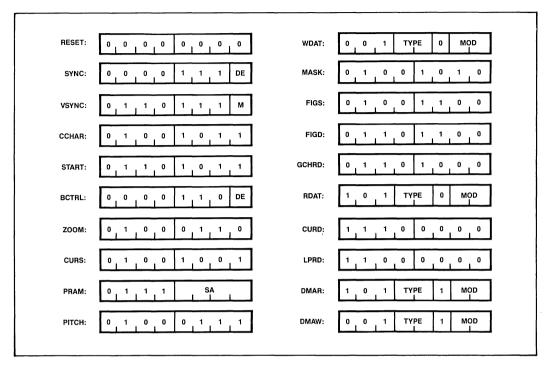

Commands to the GDC take the form of a command byte followed by a series of parameter bytes as needed for specifying the details of the command. The command processor decodes the commands, unpacks the parameters, loads them into the appropriate registers within the GDC and initiates the required operations.

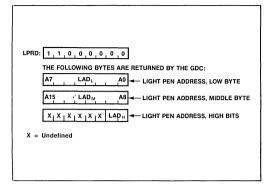

The commands available in the GDC can be organized into five categories as described in figure 5.

|                                                            | OL COMMANDS                                                                                                |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1. RESET                                                   | RESETS THE GDC TO ITS IDLE STATE.                                                                          |

| 2. SYNC:                                                   | SPECIFIES THE VIDEO DISPLAY FORMAT.                                                                        |

| 3. VSYNC                                                   | SELECTS MASTER OR SLAVE VIDEO                                                                              |

|                                                            | SYNCHRONIZATION MODE                                                                                       |

| 4. CCHAR                                                   | : SPECIFIES THE CURSOR AND CHARACTER ROW                                                                   |

|                                                            | HEIGHTS.                                                                                                   |

| DISPLAY CON                                                | TROL COMMANDS                                                                                              |

| 1. START:                                                  |                                                                                                            |

| 2. BCTRL                                                   |                                                                                                            |

| L. DOTTL                                                   | THE DISPLAY.                                                                                               |

| 3. ZOOM:                                                   |                                                                                                            |

| J. 200m.                                                   | GRAPHICS CHARACTERS WRITING.                                                                               |

| 4. CURS:                                                   |                                                                                                            |

| 4. 00110.                                                  | MEMORY.                                                                                                    |

| 5. PRAM:                                                   |                                                                                                            |

| 0. 1 104.00.                                               | THE DISPLAY AREAS AND SPECIFIES THE EIGHT                                                                  |

|                                                            | BYTES FOR THE GRAPHICS CHARACTER.                                                                          |

| 6. PITCH:                                                  |                                                                                                            |

| 0. 111011.                                                 | DISPLAY MEMORY.                                                                                            |

| DRAWING CO                                                 | NTROL COMMANDS                                                                                             |

| 1. WDAT:                                                   |                                                                                                            |

| I. WDAT:                                                   | MEMORY.                                                                                                    |

| 2. MASK:                                                   |                                                                                                            |

| 3. FIGS:                                                   |                                                                                                            |

| 3. FIGS:                                                   | PROCESSOR.                                                                                                 |

| 4. FIGD:                                                   |                                                                                                            |

| 5. GCHRD                                                   |                                                                                                            |

| 5. GUNKL                                                   | . DRAWS THE GRAPHICS CHARACTER INTO DISPLAT                                                                |

|                                                            |                                                                                                            |

|                                                            | A READ COMMANDS                                                                                            |

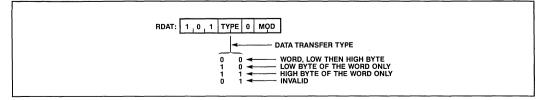

| 1. RDAT:                                                   | READS DATA WORDS OR BYTES FROM DISPLAY                                                                     |

|                                                            | MEMORY.                                                                                                    |

|                                                            |                                                                                                            |

|                                                            |                                                                                                            |

|                                                            |                                                                                                            |

|                                                            |                                                                                                            |

| 2. DMAW:                                                   | REQUESTS A DMA WRITE TRANSFER.                                                                             |

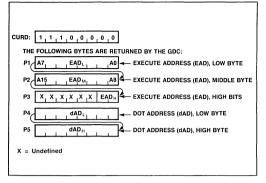

| 2. CURD:<br>3. LPRD:<br>DMA CONTRO<br>1. DMAR:<br>2. DMAW: | READS THE CURSOR POSITION.<br>READS THE LIGHT PEN ADDRESS.<br>IL COMMANDS<br>REQUESTS A DMA READ TRANSFER. |

Figure 5. GDC Command Summary

Figure 6. Status Register (SR)

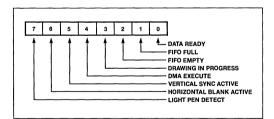

### **Status Register Flags**

SR-7: Light Pen Detect: When this bit is set to 1, the light pen address (LAD) register contains a deglitched value that the system microprocessor may read. This flag is reset after the 3-byte LAD is moved into the FIFO in response to the light pen read command. **SR-6: Horizontal Blanking Active:** A 1 value for this flag signifies that horizontal retrace blanking is currently underway.

**SR-5: Vertical Sync:** Vertical retrace sync occurs while this flag is a 1. The vertical sync flag coordinates display format modifying commands to the blanked interval surrounding vertical sync. This eliminates display disturbances.

**SR-4: DMA Execute:** This bit is a 1 during DMA data transfers.

**SR-3: Drawing in Progress:** While the GDC is drawing a graphics figure, this status bit is a 1.

**SR-2: FIFO Empty:** This bit and the FIFO Full flag coordinate system microprocessor accesses with the GDC FIFO. When it is 1, the Empty flag ensures that all the commands and parameters previously sent to the GDC have been processed.

**SR-1: FIFO Full:** A 1 at this flag indicates a full FIFO in the GDC. A 0 ensures that there is room for at least one byte. This flag needs to be checked before each write into the GDC.

**SR-0: Data Ready:** When this flag is a 1, it indicates that a byte is available to be read by the system microprocessor. This bit must be tested before each read operation. It drops to a 0 while the data is transferred from the FIFO into the microprocessor interface data register.

### **FIFO Operation & Command Protocol**

The first-in, first-out buffer (FIFO) in the GDC handles the command dialogue with the system microprocessor. This flow of information uses a half-duplex technique, in which the single 16-location FIFO is used for both directions of data movement, one direction at a time. The FIFO's direction is controlled by the system microprocessor through the GDC's command set. The microprocessor coordinates these transfers by checking the appropriate status register bits.

The command protocol used by the GDC requires the differentiation of the first byte of a command sequence from the succeeding bytes. This first byte contains the operation code and the remaining bytes carry parameters. Writing into the GDC causes the FIFO to store a flag value alongside the data byte to signify whether the byte was written into the command or the parameter address. The command processor in the GDC tests this bit as it interprets the entries in the FIFO. The receipt of a command byte by the command processor marks the end of any previous operation. The number of parameter bytes supplied with a command is cut short by the receipt of the next command byte. A read operation from the GDC to the microprocessor can be terminated at any time by the next command.

The FIFO changes direction under the control of the system microprocessor. Commands written into the GDC always put the FIFO into write mode if it wasn't in it already. If it was in read mode, any read data in the FIFO at the time of the turnaround is lost. Commands which require a GDC response, such as RDAT, CURD and LPRD, put the FIFO into read mode after the command is interpreted by the GDC's command processor. Any commands and parameters behind the read-evoking command are discarded when the FIFO direction is reversed.

### **Read-Modify-Write Cycle**

Data transfers between the GDC and the display memory are accomplished using a read-modify-write (RMW) memory cycle. The four clock period timing of the RMW cycle is used to: 1) output the address, 2) read data from the memory, 3) modify the data, and 4) write the modified data back into the initially selected memory address. This type of memory cycle is used for all interactions with display memory including DMA transfers, except for the two clock period display and RAM refresh cycles.

The operations performed during the modify portion of the RMW cycle merit additional explanation. The circuitry in the GDC uses three main elements: the Pattern register, the Mask register, and the 16-bit Logic unit. The Pattern register holds the data pattern to be moved into memory. It is loaded by the WDAT command or, during drawing, from the parameter RAM. The Mask register contents determine which bits of the read data will be modified. Based on the contents of these registers, the Logic unit performs the selected operations of REPLACE, COM-PLEMENT, SET, or CLEAR on the data read from display memory.

The Pattern register contents are ANDed with the Mask register contents to enable the actual modification of the memory read data, on a bit-by-bit basis. For graphics drawing, one bit at a time from the Pattern register is combined with the Mask. When ANDed with the bit set to a 1 in the Mask register, the proper single pixel is modified by the Logic Unit. For the next pixel in the figure, the next bit in the Pattern register is selected and the Mask register bit is moved to identify the pixel's location within the word. The Execution word address pointer register, EAD, is also adjusted as required to address the word containing the next pixel.

In character mode, all of the bits in the Pattern register are used in parallel to form the respective bits of the modify data word. Since the bits of the character code word are used in parallel, unlike the one-bit-ata-time graphics drawing process, this facility allows any or all of the bits in a memory word to be modified in one RMW memory cycle. The Mask register must be loaded with 1s in the positions where modification is to be permitted.

The Mask register can be loaded in either of two ways. In graphics mode, the CURS command contains a four-bit dAD field to specify the dot address. The command processor converts this parameter into the one-of-16 format used in the Mask register for figure drawing. A full 16 bits can be loaded into the Mask register using the MASK command. In addition to the character mode use mentioned above, the 16-bit MASK load is convenient in graphics mode when all of the pixels of a word are to be set to the same value.

The Logic unit combines the data read from display memory, the Pattern register, and the Mask register to generate the data to be written back into display memory. Any one of four operations can be selected: REPLACE, COMPLEMENT, CLEAR or SET. In each case, if the respective Mask bit is 0, that particular bit of the read data is returned to memory unmodified. If the Mask bit is 1, the modification is enabled. With the REPLACE operation, the modify data simply takes the place of the read data for modification enabled bits. For the other three operations, a 0 in the modify data allows the read data bit to be returned to memory. A 1 value causes the specified operation to be performed in the bit positions with set Mask bits.

### **Figure Drawing**

The GDC draws graphics figures at the rate of one pixel per read-modify-write (RMW) display memory cycle. These cycles take four clock periods to complete. At a clock frequency of 5 MHz, this is equal to 800 ns. During the RMW cycle the GDC simultaneously calculates the address and position of the next pixel to be drawn.

The graphics figure drawing process depends on the display memory addressing structure. Groups of 16 horizontally adjacent pixels form the 16-bit words

which are handled by the GDC. Display memory is organized as a linearly addressed space of these words. Addressing of individual pixels is handled by the GDC's internal RMW logic.

During the drawing process, the GDC finds the next pixel of the figure which is one of the eight nearest neighbors of the last pixel drawn. The GDC assigns each of these eight directions a number from 0 to 7, starting with straight down and proceeding counterclockwise.

Figure 7. Drawing Directions

Figure drawing requires the proper manipulation of the address and the pixel bit position according to the drawing direction to determine the next pixel of the figure. To move to the word above or below the current one, it is necessary to subtract or add the number of words per line in display memory. This parameter is called the pitch. To move to the word to either side, the Execute word address cursor, EAD, must be incremented or decremented as the dot address pointer bit reaches the LSB or the MSB of the Mask register. To move to a pixel within the same word, it is necessary to rotate the dot address pointer register to the right or left. Figure 8 summarizes these operations for each direction.

Whole word drawing is useful for filling areas in memory with a single value. By setting the Mask register to all 1s with the MASK command, both the LSB and MSB of the dAD will always be 1, so that the EAD value will be incremented or decremented for each cycle regardless of direction. One RMW cycle will be able to affect all 16 bits of the word for any drawing type. One bit in the Pattern register is used per RMW cycle to write all the bits of the word to the same value. The next Pattern bit is used for the word, etc.

| DIR  | ADDRESS OPERATION(S)                                                |