## intel®

## INTEL 440LX AGPSET: 82443LX PCI A.G.P. CONTROLLER (PAC)

- Supports the Pentium<sup>®</sup> II Processor at a Bus Frequency of 66 MHz

- Supports 32-Bit Addressing

- Optimized In-Order and Request Queue

- Full Symmetric Multi-Processor (SMP) Protocol for Up to Two Processors

- Dynamic Deferred Transaction Support

- GTL+ Compliant Host Bus Supports WC Cycles

- Integrated DRAM Controller

- EDO (Extended Data Out), and Synchronous DRAM Support

- Supports a Maximum Memory Size of 512 MB With SDRAM, or 1 GB With EDO

- 64/72-bit Path to Memory

- Configurable DRAM Interface

- Support for Auto Detection of Memory Type: (DIMM Serial Presence Detect)

- 8 RAS Lines Available

- Support for 4-, 16- and 64-Mbit DRAM devices

- Support for Symmetrical and Asymmetrical DRAM Addressing

- Configurable Support for ECC/EC

- ECC With Single Bit Error Correction and Multiple Bit Error Detection

- Read-Around-Write Support for Host and PCI DRAM Read Accesses

- Supports 3.3V DRAMs

- Accelerated Graphics Port (A.G.P.) Interface

- A.G.P. Specification Compliant

- A.G.P. 66/133 MHz 3.3V Devices Supported

- Synchronous Coupling to the Host Bus Frequency

- PCI Bus Interface

- PCI Revision 2.1 Interface Compliant

- Greater Than 100-MBps Data Streaming for PCI-to-DRAM Accesses

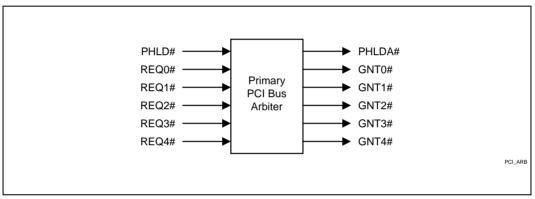

- Integrated Arbiter With Multi-Transaction PCI Arbitration Acceleration Hooks

- Five PCI Bus Masters are Supported in Addition to the Host and PCI-to-ISA I/O Bridge

- Delayed Transaction Support

- PCI Parity Checking and Generation Support

- Data Buffering For Increased Performance

- Extensive CPU-to-DRAM, PCI-to-DRAM, and A.G.P.-to-DRAM Write Data Buffering

- CPU-to-A.G.P., PCI-to-A.G.P., and A.G.P.-to-PCI Data Buffering

- Write Combining Support for CPU-to-PCI Burst Writes

- Supports Concurrent Host, PCI, and A.G.P. Transactions to Main Memory

- System Management Mode (SMM) Compliant

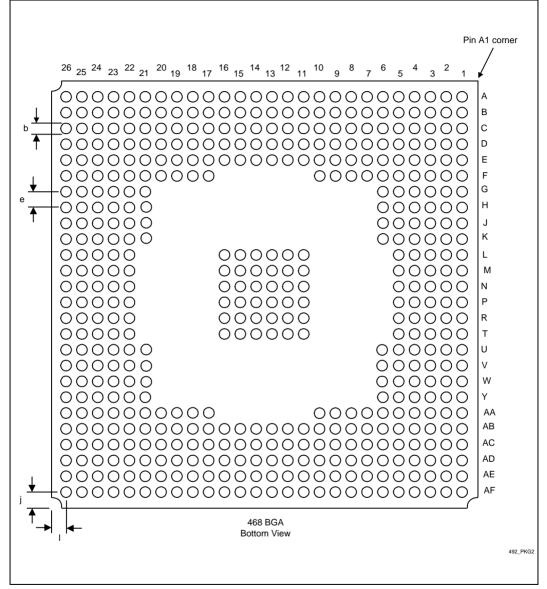

- 492 Pin BGA Package

The 82443LX (PAC) is the first generation of desktop AGPset designed for the Pentium<sup>®</sup> II processor. The 82443LX PCI A.G.P. Controller (PAC) integrates a Host-to-PCI bridge, optimized DRAM controller and data path, and an Accelerated Graphics Port (A.G.P.) interface. A.G.P. is a high performance, component level interconnect, targeted at 3D graphics applications and based on a set of performance enhancements to PCI. The I/O subsystem portion of the PAC platform is based on the PIIX4, a highly integrated version of the Intel's PCI-to-ISA bridge family. PAC is developed as the ultimate Pentium II processor platform and is targeted for emerging 3D graphics and multimedia applications. The 440LX AGPset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

# intel®

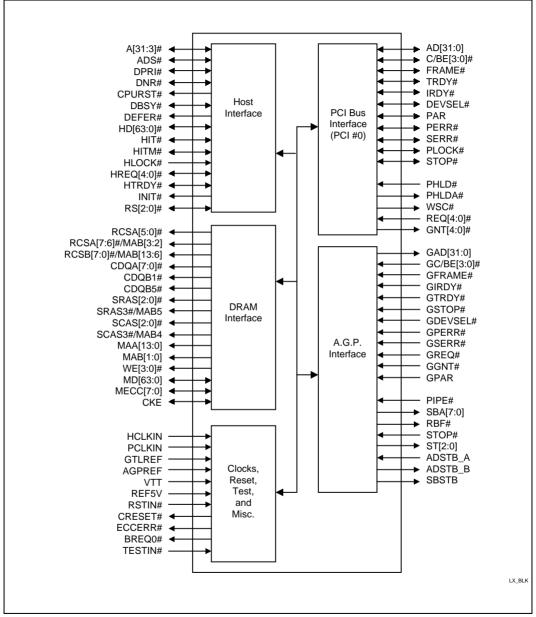

82443LX Block Diagram

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 440LX AGPset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

\*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

Call 1-800-548-4725

or visit the Intel web site at http://www.intel.com

## CONTENTS

#### PAGE

| 1.0. OVERVIEW                                                          | 9  |

|------------------------------------------------------------------------|----|

| 2.0. SIGNAL DESCRIPTION                                                | 13 |

| 2.1. PAC Signals                                                       | 14 |

| 2.1.1. HOST INTERFACE SIGNALS                                          |    |

| 2.1.2. DRAM INTERFACE SIGNALS                                          |    |

| 2.1.3. PCI INTERFACE SIGNALS                                           | 20 |

| 2.1.4. A.G.P. INTERFACE SIGNALS                                        | 22 |

| 2.1.5. CLOCKS, RESET, AND MISCELLANEOUS SIGNALS                        | 25 |

| 2.2. Power-Up/Reset Strapping Options                                  | 26 |

| 2.3. State of PAC Output and Bi-directional Signals During Hard Reset  | 27 |

| 3.0. REGISTER DESCRIPTION                                              | 29 |

| 3.1. Register Access                                                   | 30 |

| 3.1.1. CONFADD—CONFIGURATION ADDRESS REGISTER                          | 30 |

| 3.1.2. CONFDATA—CONFIGURATION DATA REGISTER                            | 31 |

| 3.1.3. CONFIGURATION SPACE MECHANISM                                   | 31 |

| 3.1.3.1. Routing the Configuration Accesses to PCI or A.G.P.           | 31 |

| 3.1.3.2. PCI Bus Configuration Mechanism                               | 31 |

| 3.1.3.3. Mapping of Configuration Cycles on A.G.P.                     | 32 |

| 3.2. PCI Configuration Space (Device 0 and Device 1)                   | 32 |

| 3.3. Register Set—Device 0 (Host-to-PCI Bridge)                        |    |

| 3.3.1. VID—VENDOR IDENTIFICATION REGISTER (DEVICE 0)                   | 35 |

| 3.3.2. DID—DEVICE IDENTIFICATION REGISTER (DEVICE 0)                   | 35 |

| 3.3.3. PCICMD—PCI COMMAND REGISTER (DEVICE 0)                          |    |

| 3.3.4. PCISTS—PCI STATUS REGISTER (DEVICE 0)                           | 37 |

| 3.3.5. RID-REVISION IDENTIFICATION REGISTER (DEVICE 0)                 | 38 |

| 3.3.6. SUBC—SUB-CLASS CODE REGISTER (DEVICE 0)                         | 38 |

| 3.3.7. BCC—BASE CLASS CODE REGISTER (DEVICE 0)                         | 38 |

| 3.3.8. MLT—MASTER LATENCY TIMER REGISTER (DEVICE 0)                    | 39 |

| 3.3.9. HDR—HEADER TYPE REGISTER (DEVICE 0)                             | 39 |

| 3.3.10. APBASE—APERTURE BASE CONFIGURATION REGISTER (DEVICE 0)         | 39 |

| 3.3.11. CAPPTR—CAPABILITIES POINTER (DEVICE 0)                         | 40 |

| 3.3.12. PACCFG—PAC CONFIGURATION REGISTER (DEVICE 0)                   | 41 |

| 3.3.13. DBC—DATA BUFFER CONTROL REGISTER (DEVICE 0)                    | 42 |

| 3.3.14. DRT—DRAM ROW TYPE REGISTER (DEVICE 0)                          | 43 |

| 3.3.15. DRAMC—DRAM CONTROL REGISTER (DEVICE 0)                         | 44 |

| 3.3.16. DRAMT—DRAM TIMING REGISTER (DEVICE 0)                          | 44 |

| 3.3.17. PAM—PROGRAMMABLE ATTRIBUTE MAP REGISTERS (PAM[6:0]) (DEVICE 0) | 46 |

| 3.3.18. DRB-DRAM ROW BOUNDARY REGISTERS (DEVICE 0)                     | 48 |

## intel®

| 3.3.19. FDHC—FIXED DRAM HOLE CONTROL REGISTER (DEVICE 0)                  | 50 |

|---------------------------------------------------------------------------|----|

| 3.3.20. DRAMXC—DRAM EXTENDED CONTROL REGISTER (DEVICE 0)                  | 51 |

| 3.3.21. MBSC-MEMORY BUFFER STRENGTH CONTROL REGISTER (DEVICE 0)           | 52 |

| 3.3.22. MTT-MULTI-TRANSACTION TIMER REGISTER (DEVICE 0)                   | 54 |

| 3.3.23. SMRAM—SYSTEM MANAGEMENT RAM CONTROL REGISTER (DEVICE 0)           | 55 |

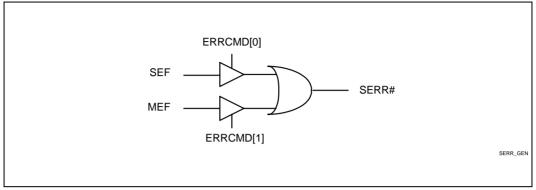

| 3.3.24. ERRCMD—ERROR COMMAND REGISTER (DEVICE 0)                          | 56 |

| 3.3.25. ERRSTS0—ERROR STATUS REGISTER 0 (DEVICE 0)                        | 57 |

| 3.3.26. ERRSTS1—ERROR STATUS REGISTER 1 (DEVICE 0)                        | 59 |

| 3.3.27. RSTCTRL—RESET CONTROL REGISTER (DEVICE 0)                         | 60 |

| 3.3.28. ACAPID—A.G.P. CAPABILITY IDENTIFIER REGISTER (DEVICE 0)           | 61 |

| 3.3.29. AGPSTAT—A.G.P. STATUS REGISTER (DEVICE 0)                         | 62 |

| 3.3.30. AGPCMD—A.G.P. COMMAND REGISTER (DEVICE 0)                         | 62 |

| 3.3.31. AGPCTRL—A.G.P. CONTROL REGISTER (DEVICE 0)                        | 63 |

| 3.3.32. APSIZE—APERTURE SIZE (DEVICE 0)                                   | 64 |

| 3.3.33. ATTBASE—APERTURE TRANSLATION TABLE BASE REGISTER (DEVICE 0)       | 65 |

| 3.3.34. AMTT—A.G.P. INTERFACE MULTI-TRANSACTION TIMER REGISTER (DEVICE 0) | 65 |

| 3.3.35. LPTT-LOW PRIORITY TRANSACTION TIMER REGISTER (DEVICE 0)           | 65 |

| 3.4. A.G.P. Configuration Registers-(Device 1)                            | 66 |

| 3.4.1. VID1—VENDOR IDENTIFICATION REGISTER (DEVICE 1)                     | 66 |

| 3.4.2. DID1—DEVICE IDENTIFICATION REGISTER (DEVICE 1)                     | 66 |

| 3.4.3. PCICMD1—PCI-PCI COMMAND REGISTER (DEVICE 1)                        | 66 |

| 3.4.4. PCISTS1—PCI-PCI STATUS REGISTER (DEVICE 1)                         | 67 |

| 3.4.5. RID1—REVISION IDENTIFICATION REGISTER (DEVICE 1)                   | 67 |

| 3.4.6. SUBC1—SUB-CLASS CODE REGISTER (DEVICE 1)                           | 67 |

| 3.4.7. BCC1—BASE CLASS CODE REGISTER (DEVICE 1)                           | 68 |

| 3.4.8. HDR1—HEADER TYPE REGISTER (DEVICE 1)                               | 68 |

| 3.4.9. PBUSN—PRIMARY BUS NUMBER REGISTER—DEVICE #1                        | 68 |

| 3.4.10. SBUSN—SECONDARY BUS NUMBER REGISTER (DEVICE 1)                    | 69 |

| 3.4.11. SUBUSN—SUBORDINATE BUS NUMBER REGISTER (DEVICE 1)                 | 69 |

| 3.4.12. SMLT—SECONDARY MASTER LATENCY TIMER REGISTER (DEVICE 1)           | 69 |

| 3.4.13. IOBASE—I/O BASE ADDRESS REGISTER (DEVICE 1)                       | 70 |

| 3.4.14. IOLIMIT—I/O LIMIT ADDRESS REGISTER (DEVICE 1)                     | 70 |

| 3.4.15. SSTS—SECONDARY PCI-PCI STATUS REGISTER (DEVICE 1)                 | 71 |

| 3.4.16. MBASE—MEMORY BASE ADDRESS REGISTER (DEVICE 1)                     | 72 |

| 3.4.17. MLIMIT—MEMORY LIMIT ADDRESS REGISTER (DEVICE 1)                   | 72 |

| 3.4.18. PMBASE—PREFETCHABLE MEMORY BASE ADDRESS REGISTER (DEVICE 1)       | 73 |

| 3.4.19. PMLIMIT—PREFETCHABLE MEMORY LIMIT ADDRESS REGISTER (DEVICE 1)     | 73 |

| 3.4.20. BCTRL—PCI-PCI BRIDGE CONTROL REGISTER (DEVICE 1)                  | 74 |

|                                                                           |    |

## intel®

| 4.0. FUNCTIONAL DESCRIPTION                                    | 76  |

|----------------------------------------------------------------|-----|

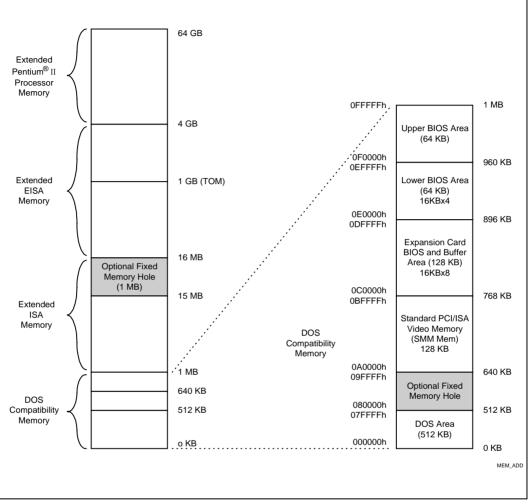

| 4.1. System Address Map                                        | 76  |

| 4.1.1. MEMORY ADDRESS RANGES                                   | 76  |

| 4.1.1.1. Compatibility Area                                    | 76  |

| Extended Memory Area                                           | 78  |

| 4.1.1.2. A.G.P. Memory Address Ranges                          | 79  |

| 4.1.1.3. A.G.P. Graphics Aperture                              | 79  |

| 4.1.1.4. Address Mapping of PCI Devices on A.G.P.              |     |

| 4.1.2. SYSTEM MANAGEMENT MODE (SMM) MEMORY RANGE               | 80  |

| 4.1.3. MEMORY SHADOWING                                        | 80  |

| 4.1.4. I/O ADDRESS SPACE                                       |     |

| 4.1.5. PAC DECODE RULES AND CROSS-BRIDGE ADDRESS MAPPING       | 81  |

| 4.1.5.1. PCI Interface Decode Rules                            |     |

| 4.1.5.2. A.G.P. Interface Decode Rules                         |     |

| 4.1.5.3. Legacy VGA and MDA Ranges                             |     |

| 4.2. Host Interface                                            |     |

| 4.3. DRAM Interface                                            |     |

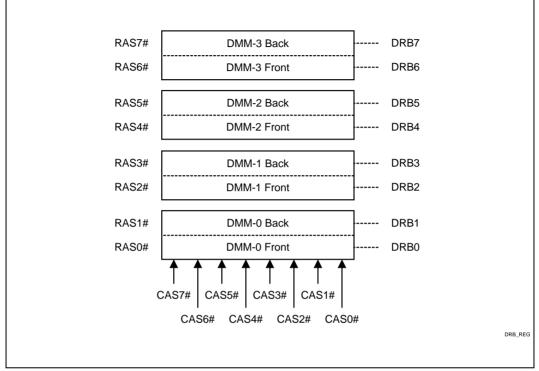

| 4.3.1. DRAM ORGANIZATION AND CONFIGURATION                     |     |

| 4.3.1.1. Configuration Mechanism for DIMMs                     | 91  |

| 4.3.2. DRAM ADDRESS TRANSLATION AND DECODING                   |     |

| 4.3.3. REFRESH CYCLES (CAS# BEFORE RAS#)                       |     |

| 4.3.4. DRAM SUBSYSTEM POWER MANAGEMENT                         |     |

| 4.3.5. SERIAL PRESENCE DETECT (SPD) FOR SDRAM                  |     |

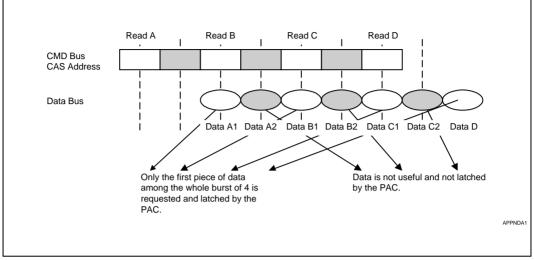

| 4.3.6. SINGLE CLOCK COMMAND MODE FOR SDRAM                     |     |

| 4.3.6.1. Enabling Single Clock Command Mode                    |     |

| 4.3.6.2. Restrictions For Supporting Single Clock Command Mode |     |

| 4.3.6.3. Conclusion For Single Clock Command Mode Support      |     |

| 4.3.7. SUPPORT FOR 2 AND 4 BANKS SDRAM                         |     |

| 4.4. Data Integrity Support                                    |     |

| 4.4.1. ECC GENERATION                                          |     |

| 4.4.1.1. Error Detection and Correction                        |     |

| 4.4.1.2. ECC Test Diagnostic Mode of Operation                 |     |

| 4.5. PCI Interface                                             | 101 |

| 4.6. A.G.P. Interface                                          | -   |

| 4.7. Arbitration and Concurrency                               |     |

| 4.8. System Clocking and Reset                                 |     |

| 4.8.1. HOST FREQUENCY SUPPORT                                  |     |

| 4.8.2. CLOCK GENERATION AND DISTRIBUTION                       |     |

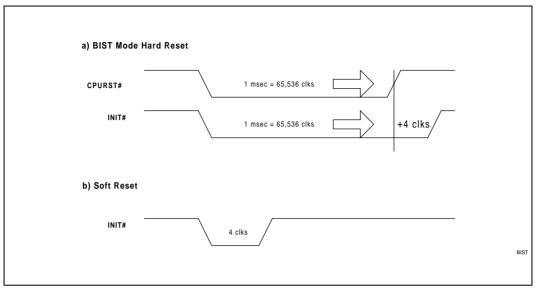

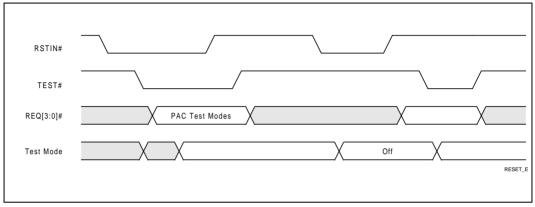

| 4.8.3. SYSTEM RESET                                            |     |

| 4.8.4. PAC RESET STRUCTURE                                     |     |

| 4.8.5. HARD RESET                                              |     |

| 4.8.6. SOFT RESET                                              |     |

| 4.8.7. CPU BIST                                                | 108 |

## int<sub>el</sub>.

## INTEL 82443LX (PAC)

| 5.0. ELECTRICAL CHARACTERISTICS                       |     |

|-------------------------------------------------------|-----|

| 5.1. Absolute Maximum Ratings                         |     |

| 5.2. Power Characteristics                            |     |

| 5.3. Signal Groupings                                 |     |

| 5.4. D.C. Characteristics                             |     |

| 5.5. AC Characteristics                               |     |

| 5.6. 82443LX Timing Diagrams                          |     |

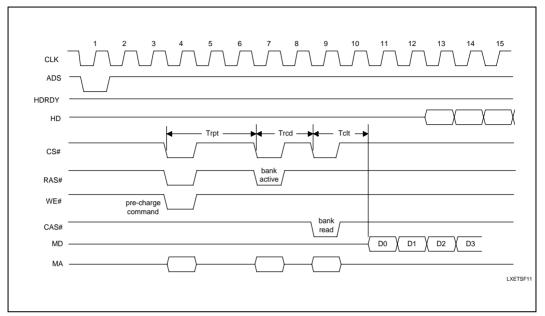

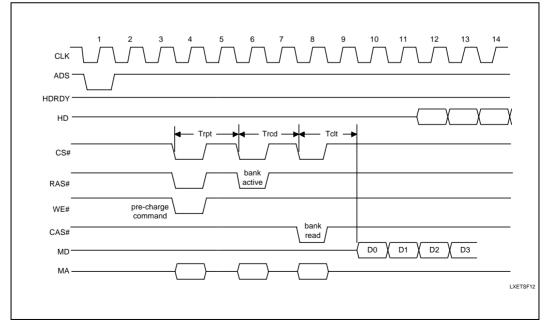

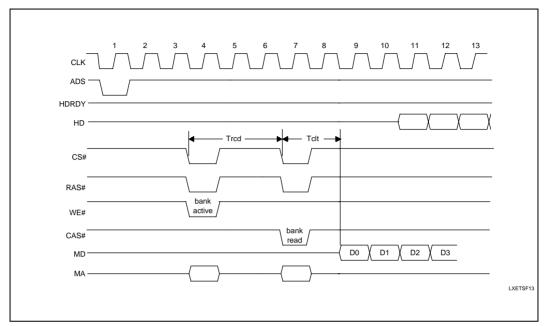

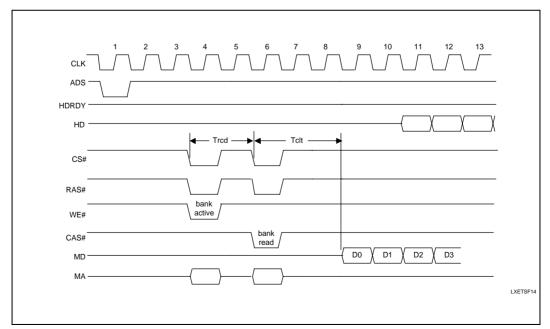

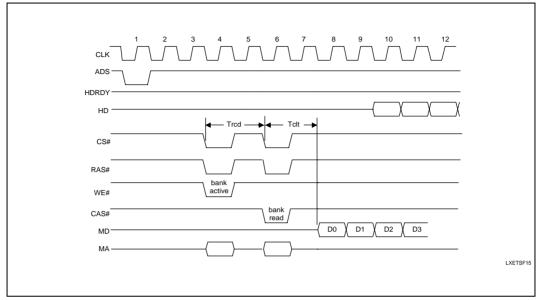

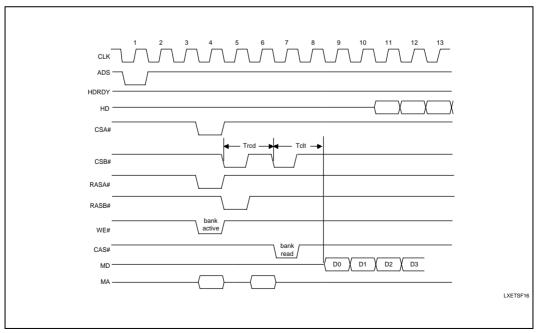

| 5.7. DRAM TIMING RELATIONSHIPS WITH REGISTER SETTINGS |     |

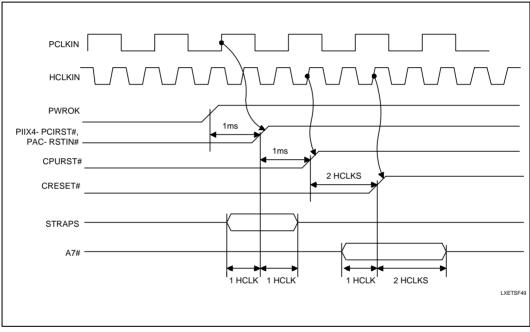

| 5.8. AC TIMING REQUIREMENT FOR STRAPPING OPTIONS      | 131 |

| 6.0. PIN ASSIGNMENT                                   | 131 |

| 7.0. PACKAGE SPECIFICATIONS                           | 139 |

| 8.0. TESTABILITY                                      |     |

| 8.1. 82443LX (PAC) Test Modes                         |     |

| 8.1.1. NAND CHAIN TEST MODE                           | 143 |

## intel®

## **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                                                                                                                                                                                                          |  |

|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| July, 1997       | -001    | This is the first release of the 82443LX data sheet.                                                                                                                                                                                                                                 |  |

| January, 1998    | -002    | <ol> <li>The following sections have been added to the data sheet:         <ul> <li>Section 4.3.5, Serial Presence Detect (SPD) for SDRAM</li> <li>Section 4.3.6, Single Clock Command Mode for SDRAM</li> <li>Section 4.3.7, Support for 2 and 4 Banks SDRAM</li> </ul> </li> </ol> |  |

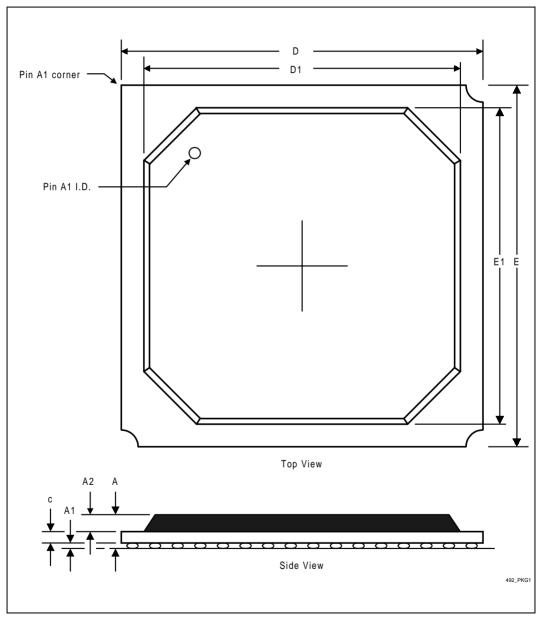

|                  |         | 2. The pinout diagrams (Figures 32 and 33) are top views.                                                                                                                                                                                                                            |  |

|                  |         | <ol> <li>The package dimension diagram (Figure 35) has been updated to<br/>show the correct ball placement. In the previous revision of the data<br/>sheet, some ball placements were missing.</li> </ol>                                                                            |  |

|                  |         | <ol> <li>Electrical Characteristics Chapter has been added. This chapter<br/>contains absolute maximum ratings, thermal characteristics, DC<br/>characteristics, AC characteristics, and timing waveforms.</li> </ol>                                                                |  |

|                  |         | <ol><li>Minor text changes have been made throughout this document for<br/>clarification.</li></ol>                                                                                                                                                                                  |  |

## intel

### 1.0. OVERVIEW

PAC integrates a Host-to-PCI bridge, optimized DRAM controller and data path, and an Accelerated Graphics Port (A.G.P.) interface. The A.G.P. is a high performance, component level interconnect, targeted at 3D graphics applications and based on a set of performance enhancements to PCI. The I/O subsystem portion of the PAC platform is based on the PIIX4, a highly integrated version of the Intel's PCI-to-ISA bridge family. The PAC is developed as the ultimate Pentium II processor platform and is targeted for emerging 3D graphics and multimedia applications. The PAC component includes the following functions and capabilities:

- Support for single and dual Pentium II processor configurations

- 64-bit GTL+ based Host Interface

- 32-bit Host address Support

- 64/72-bit Main Memory Interface with optimized support for SDRAM

- 32-bit PCI Bus Interface with integrated PCI arbiter

- A.G.P. Interface with up to 133-MHz data transfer capability

- Extensive Data Buffering between all interfaces for high throughput and concurrent operations

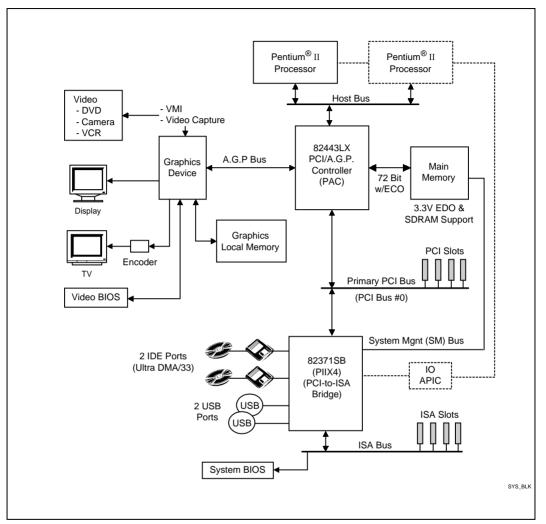

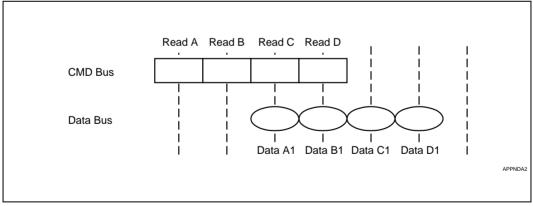

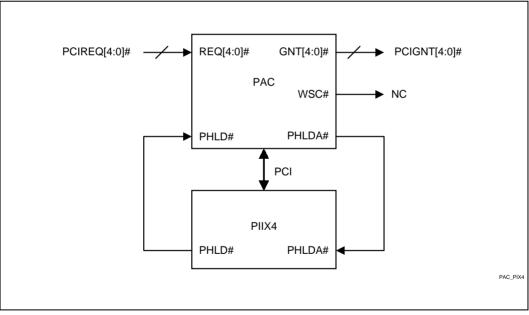

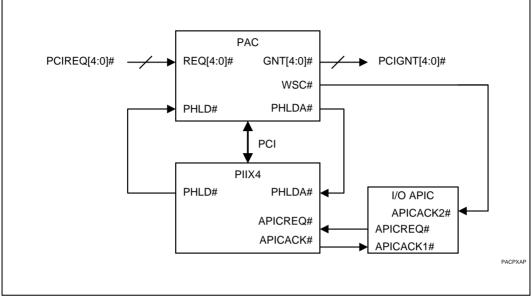

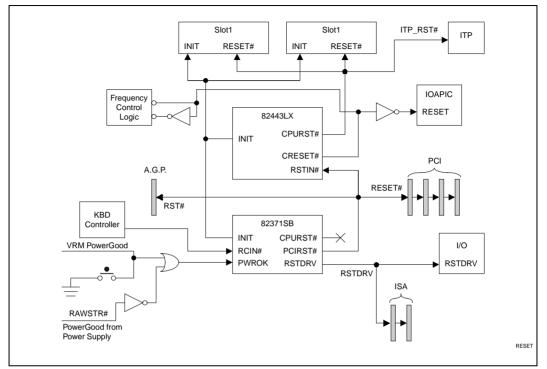

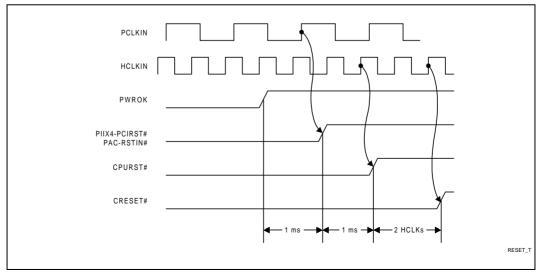

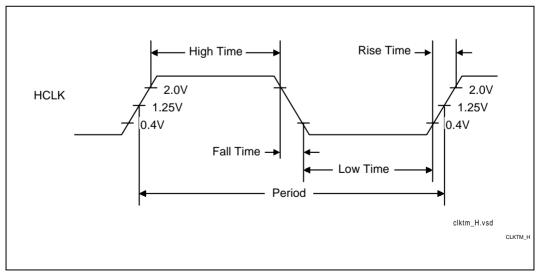

Figure 1 shows a block diagram of a typical platform based on the 440LX AGPset. The PAC host bus interface supports up to two Pentium II processors at 66 MHz. The physical interface design is based on the GTL+ specification. The PAC provides an optimized 72-bit DRAM interface (64-bit Data plus ECC). This interface supports 3.3V DRAM technologies. The PAC provides the interface to a PCI bus operating at 33 MHz. This interface implementation is compliant with PCI Rev 2.1 Specification. The PAC is the first Intel product that introduces the Accelerated Graphics Port interface. The PAC A.G.P. interface implementation is based on the A.G.P. Specification Rev 1.0. It can support up to 133-MHz data transfer rates.

PAC is designed to support the PIIX4 I/O bridge. PIIX4 is a highly integrated multi-functional component that supports the following functions and capabilities:

- PCI Rev 2.1 compliant PCI-to-ISA Bridge with support for 33-MHz PCI operations

- Deep Green Desktop Power Management Support

- Enhanced DMA controller

- 8259 Compatible Programmable Interrupt Controller

- System Timer functions

- Integrated IDE controller with Ultra DMA/33 support

- USB host interface with support for two USB ports

- System Management Bus (SMB) with support for DIMM Serial Presence Detect

- Support for an external I/O APIC component

Figure 1. 440LX System Block Diagram

#### **Host Interface**

The Pentium II processor supports a second level cache size of 256K or 512K. All cache control logic is provided in the Pentium II processor. PAC supports a maximum of 32-bit address or 4-GB memory address space from the processor perspective. PAC provides bus control signals and address paths for transfers between the processor's host bus, PCI bus, Accelerated Graphics Port and main memory. The PAC supports a 4-deep in-order queue (i.e., it provides support for pipelining of up to four outstanding transaction requests on the host bus). Due to the system concurrency requirements, along with support for pipelining of address requests from the host bus, the PAC supports general request queuing for all three interfaces (Host, A.G.P. and PCI).

In Host-to-PCI transfers, depending on the PCI address space being accessed, the address will be either translated or directly forwarded on the PCI bus. If the access is to a PCI configuration space, the processor I/O cycle is mapped to a configuration cycle. If the access is to a PCI I/O or memory space, the processor address is passed without modification to the PCI bus, unless it hits a certain PCI memory address range (later referred in a document as the A.G.P. Aperture or Graphics Aperture) dedicated for graphics memory address space. If this space, or a portion of it, is mapped to main memory, then the address will be translated via the A.G.P. address remapping mechanism. The request will also be forwarded to the DRAM subsystem. Host cycles forwarded to A.G.P. are defined by the A.G.P. address map.

PAC also receives requests from PCI bus and A.G.P. bus initiators for access to main memory. If a target address is within the graphics aperture, then the request is translated into the appropriate memory address. A.G.P. accesses destined to the graphics aperture are not snooped on the host bus because coherency of aperture data is maintained by software. All accesses to the aperture, from the Host, PCI or A.G.P., are translated using the A.G.P. address remapping mechanism.

#### **DRAM Interface**

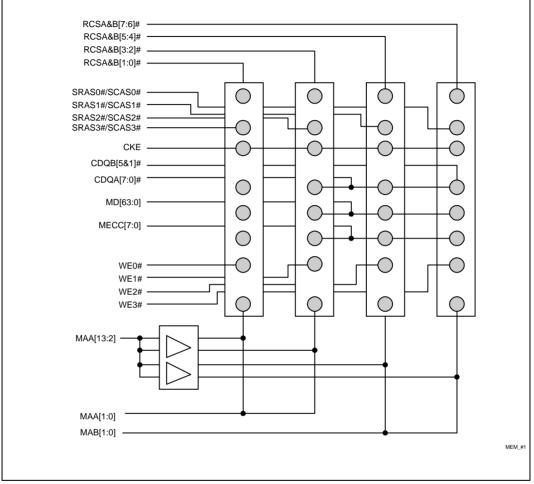

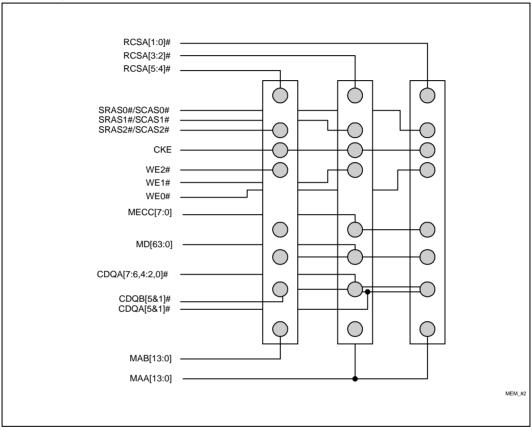

The PAC integrates a main memory controller that supports a 64/72-bit DRAM interface. The DRAM controller supports the following features:

- DRAM type. Extended Data Out (EDO) and Synchronous (SDRAM) DRAM controller optimized for dualbank SDRAM organization

- Memory Size.

- SDRAM: 8 MB to 512 MB with eight memory rows

- EDO: 8 MB to 1 GB with eight memory rows

- Addressing Type. Symmetrical and Asymmetrical addressing

- Memory Modules: Single and double density DIMMs

- Configurable DRAM Interface.

- Configuration #1: Large Memory Array

- Support for single-sided DIMMs based on x4 DRAMs

- Support for single and double-sided x8 and x16 DIMMs

- External buffering is required on MAA[13:2] signals (Do not buffer MAA[1:0] or MAB[1:0])

- 8 Row, 4 DS DIMM socket configuration

- Configuration #2: Small Memory Array

- Support for single and double-sided x8 and x16 DIMMs only

- Two copies of MA[13:2] signals supplied by the PAC (no external buffers required on MA signals)

- 6 Row, 3 DS DIMM socket configuration

- DRAM device technology. 4 Mbit, 16 Mbit and 64 Mbit

- DRAM Speeds. 50 ns and 60 ns for asynchronous EDO DRAM and equivalent SDRAM 66-MHz parameters for synchronous memory.

The 440LX AGPset also provides a DIMM plug-and-play support via Serial Presence Detect (SPD) mechanism. This is supported via the PIIX4 SMB interface. The PAC provides optional data integrity features including EC or ECC in the memory array. Error Checking (EC) mode provides single and multiple bit error detection. In ECC mode, the PAC provides error checking and correction of the data during reads from the DRAM. The PAC supports multiple-bit error detection and single-bit error correction when ECC mode is enabled and single/multi-bit error detection when correction is disabled. During writes to the DRAM, PAC generates ECC for the data.

#### Accelerated Graphics Port (A.G.P.) Interface

The 440LX is the first AGPset product designed to support the A.G.P. interface. The PAC A.G.P. implementation is compatible with the Accelerated Graphics Port Specification 1.0. PAC supports only a synchronous A.G.P. interface, coupling to the host bus frequency. The A.G.P. interface can reach a theoretical ~532 Mbytes/sec transfer rate. The actual bandwidth will be limited by the capability of the PAC memory subsystem.

#### **PCI Interface**

The PAC PCI interface is 33-MHz Revision 2.1 compliant and supports up to five external PCI bus masters in addition to the I/O bridge (PIIX4). PAC supports only synchronous PCI coupling to the host bus frequency.

#### **Read/Write Buffers**

PAC defines a sophisticated data buffering scheme to support the required level of concurrent operations and provide adequate sustained bandwidth between DRAM subsystem and all other system interfaces (CPU, A.G.P. and PCI).

#### System Clocking

PAC operates the host interface at 66 MHz, PCI at 33 MHz and A.G.P. at 66/133 MHz. Coupling between all interfaces and internal logic is done in a synchronous manner. PAC is not designed to support host bus frequencies lower than 66 MHz. The PAC clocking scheme uses an external clock synthesizer (which produces reference clocks for the host, A.G.P. and PCI interfaces).

#### I/O APIC

The I/O APIC is used to support dual processors. In configurations that use PIIX4 with a stand-alone I/O APIC component, PAC supports an external status output signal that can be used to control synchronization of interrupts.

## intel®

### 2.0. SIGNAL DESCRIPTION

This section provides a detailed description of each signal for the PAC. The signals are arranged in functional groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms "assertion" and "negation" are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert** or **assertion**, indicates that the signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The following notations are used to describe the signal type:

- I Input pin

- O Output pin

- **OD** Open Drain Output pin. This pin requires a pull-up to an appropriate voltage

- **I/O** Bi-directional input/output pin

The signal description also includes the type of buffer used for the particular signal:

- GTL+ Open Drain GTL+ interface signal. Refer to the GTL+ I/O Specification for complete details

- PCI PCI bus interface signals. These signals are compliant with the PCI 5.0V Signaling Environment DC and AC Specifications

- **A.G.P.** A.G.P. interface signals. These signals are compatible with A.G.P. Signaling Environment DC and AC Specifications

- LVTTL Low Voltage TTL compatible signals. These are also 3.3V inputs and outputs.

Note that the Pentium II processor address and data bus signals are logically inverted signals. In other words, the actual values are inverted of what appears on the Pentium II processor bus. All control signals follow normal convention. A 0 (low voltage) indicates an active level if the signal is followed by # symbol, and a 1 (high voltage) indicates an active level if the signal has no # suffix.

## 2.1. PAC Signals

#### 2.1.1. HOST INTERFACE SIGNALS

#### Table 1. Host Interface Signals

| Name       | Туре     | Description                                                                                                                                                                                                                                                                                                               |  |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A[31:3]#   | I/O GTL+ | Address Bus: A[31:3]# connect to the processor address bus. During host cycles, the A[31:3]# are inputs. PAC drives A[31:3]# during snoop cycles on behalf of PCI and A.G.P. initiators. Note that the address signals are inverted on the CPU bus.                                                                       |  |

| ADS#       | I/O GTL+ | Address Strobe: The CPU bus owner asserts ADS# to indicate the first of two cycles of a request phase.                                                                                                                                                                                                                    |  |

| BPRI#      | O GTL+   | <b>Priority Agent Bus Request:</b> PAC is the only Priority Agent on the CPU bus.<br>This signal is used to obtain the ownership of the address bus. Unless the<br>HLOCK# signal was asserted, BPRI# has priority over symmetric bus requests<br>and causes the current symmetric owner to stop issuing new transactions. |  |

| BNR#       | I/O GTL+ | <b>Block Next Request:</b> Used to block the current request bus owner from issuing a new request. This signal is used to dynamically control the CPU bus pipeline depth.                                                                                                                                                 |  |

| CPURST#    | O GTL+   | <b>CPU Reset.</b> The CPURST# pin is an output from PAC. PAC generates this signal based on the RSTIN# input signal (from PIIX4). The CPURST# allow t CPU(s) to begin execution in a known state.                                                                                                                         |  |

| DBSY#      | I/O GTL+ | <b>Data Bus Busy:</b> Used by the data bus owner to hold the data bus for transfers requiring more than one cycle.                                                                                                                                                                                                        |  |

| DEFER#     | O GTL+   | <b>Defer: PAC</b> will generate a deferred response. PAC will also use the DEFER# signal to indicate a retry response on the CPU bus.                                                                                                                                                                                     |  |

| DRDY#      | I/O GTL+ | Data Ready: Asserted for each cycle that data is transferred.                                                                                                                                                                                                                                                             |  |

| HD[63:0]#  | I/O GTL+ | <b>Host Data:</b> These signals are connected to the CPU data bus. Note that the data signals are inverted on the CPU bus.                                                                                                                                                                                                |  |

| HIT#       | I/O GTL+ | <b>Hit:</b> Indicates that a caching agent holds an unmodified version of the requested line. Also, the target may extend the snoop window by driving HIT# in conjunction with HITM#.                                                                                                                                     |  |

| HITM#      | I/O GTL+ | <b>Hit Modified:</b> Indicates that a caching agent holds a modified version of the requested line and that this agent assumes responsibility for providing the line. It is also driven in conjunction with HIT# to extend the snoop window.                                                                              |  |

| HLOCK#     | I GTL+   | Host Lock: HLOCK# provides a mechanism to insure that cycles on the Host bus are atomic. All cycles initiated while HLOCK# is asserted are guaranteed atomic. (i.e., no PCI or A.G.Psnoopable access to DRAM is allowed when HLOCK# signal is asserted by the CPU.)                                                       |  |

| HREQ[4:0]# | I/O GTL+ | <b>Request Command:</b> Asserted during both clocks of request phase. In the first clock, the signals define the transaction type to a level of detail that is sufficient to begin a snoop request. In the second clock, the signals carry additional information to define the complete transaction type.                |  |

| Name     | Туре                 | Description                                                          |                                                                                                                                                                             |            |                                            |

|----------|----------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------|

| HTRDY#   | I/O GTL+             |                                                                      | Host Target Ready: Indicates that the target of the CPU bus transaction is able to enter the data transfer phase.                                                           |            |                                            |

| INIT#    | O LVTTL              | shutdown I                                                           | Initialization. This is the output signal generated by the PAC after a CPU shutdown bus cycle, or after a soft reset is initiated by writing to the reset control register. |            |                                            |

| RS[2:0]# | I/O GTL+             | Response                                                             | Response Signals: Indicates type of response according to the following table:                                                                                              |            |                                            |

|          |                      | RS[2:0]                                                              | Response type                                                                                                                                                               | RS[2:0]    | Response type                              |

|          |                      | 000<br>001                                                           | Idle state<br>Retry response                                                                                                                                                | 100<br>101 | Hard Failure<br>No data response           |

|          |                      | 010<br>011                                                           | Deferred response<br>Reserved                                                                                                                                               | 110<br>111 | Implicit Writeback<br>Normal data response |

| HCLKIN   | l<br>LVTTL<br>(2.5V) | Host Clock In: See Clocks, Reset, and Miscellaneous Signals Section. |                                                                                                                                                                             |            |                                            |

#### NOTES:

All of the signals in the host interface are described in the Pentium II Processor data book. The preceding table highlights PAC specific uses of these signals.

#### 2.1.2. DRAM INTERFACE SIGNALS

The PAC DRAM Controller supports two different memory configurations, which are selected during Reset via a strapping on the CKE pin. Configuration #1 is the large memory array. Configuration #2 is the small memory array.

| Signal     | Туре       | Description                                                                                                                                                                                                                       |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCSA[5:0]# | O<br>LVTTL | <b>Row Address Strobe 5-0 (EDO):</b> These signals are used to latch the row address into the memory array. Each signal is used to select one DRAM row. These signals drive the DRAM array directly without any external buffers. |

|            |            | <b>Chip Select 5-0 (SDRAM):</b> For the memory row configured with SDRAM, these pins perform the function of selecting the particular SDRAM components during the active state.                                                   |

|            |            | Same function for Configuration #1 and Configuration #2.                                                                                                                                                                          |

|            |            | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                      |

| Table 2. | DRAM | Interface  | Signals |

|----------|------|------------|---------|

| 10010 11 |      | millionado | eignaio |

Signal

RCSA[7:6]# /

MAB[3:2]

RCSB[7:0]# /

MAB[13:6]

| X (PAC) | ILG ®                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Table 2. DRAM Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0       | Configuration #1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LVTTL   | <b>Row Address Strobe 7-6 (EDO):</b> These signals are used to latch the row address into the memory array. Each signal is used to select one DRAM row. These signals drive the DRAM array directly without any external buffers.                                                                                                                                                                                                                                                           |

|         | <b>Chip Select 7-6 (SDRAM):</b> For the memory row configured with SDRAM, these pins perform the function of selecting the particular SDRAM components during the active state.                                                                                                                                                                                                                                                                                                             |

|         | Configuration #2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | <b>Extra Copy of Memory Address 3-2 (EDO/SDRAM):</b> MAB[3:2] are extra copies of Memory Address [3:2] and should be routed to the closest DIMM socket to the PAC(socket #0). MAB[3:2] will change value if the current or next access is directed to a memory address range mapped to DIMM socket #0. During accesses directed to DIMM socket #1 or #2, these signals will preserve the previously driven state. These signals behave logically and electrically the same way as MAA[3:2]. |

|         | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                                                                                                                                                                                                |

| O       | Configuration #1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LVTTL   | <b>Extra copy of Row Address Strobe 7-0 (EDO):</b> These signals are used to latch the row address into the memory array. Each signal is used to select one DRAM row. These signals drive the DRAM array directly without any external buffers.                                                                                                                                                                                                                                             |

|         | <b>Extra Copy of Chip Select 7-0 (SDRAM):</b> For the memory row configured with SDRAM, these pins perform the function of selecting the particular SDRAM components during the active state.                                                                                                                                                                                                                                                                                               |

int I

#### Configuration #2:

Extra Copy of Memory Address 13-6 (EDO/SDRAM): MAB[13:6] are extra copies of Memory Address [13:6] and should be routed to the closest DIMM socket to the PAC(socket #0). MAB[13:6] will change value if the current or next access is directed to a memory address range mapped to DIMM socket #0. During accesses directed to DIMM socket #1 or #2, these signals will preserve the previously driven state. These signals behave logically and electrically the same way as MAA[13:6]. These signals have programmable buffer strengths for optimization under different signal loading conditions.

| Signal     | Туре       | Description                                                                                                                                                                                                                                                                                                                                       |  |  |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CDQA[7:0]# | O<br>LVTTL | <b>Column Address Strobe (EDO):</b> For EDOs, these signals are used to latch the column address into the memory array (CAS signals). They drive the DRAM array directly without external buffering.                                                                                                                                              |  |  |

|            |            | Input/Output Data Mask (SDRAM): These pins act as synchronized output<br>enables during read cycles and as byte enables during write cycles. In the case of<br>write cycles, byte masking functions are performed during the same clock that<br>write data is driven (i.e., 0 clock latency).                                                     |  |  |

|            |            | Same function for Configuration #1 and Configuration #2.                                                                                                                                                                                                                                                                                          |  |  |

|            |            | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                                                      |  |  |

| CDQB1#     | O<br>LVTTL | Extra Copy of Column Address Strobe 1 (EDO) / Input/Output Data Mask 1 (SDRAM): This is a copy of CAS1#/DQM1 signal. It is used to balance the loading for CAS1#/DQM1 in the ECC memory configurations where this signal is double-loaded.                                                                                                        |  |  |

|            |            | Same function for Configuration #1 and Configuration #2.                                                                                                                                                                                                                                                                                          |  |  |

|            |            | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                                                      |  |  |

| CDQB5#     | O<br>LVTTL | Extra Copy of Column Address Strobe 5 (EDO) / Input/Output Data Mask 5 (SDRAM): This is a copy of CAS5#/DQM5 signal. It is used to balance the loading for CAS5#/DQM5 in the ECC memory configurations where this signal is double-loaded.                                                                                                        |  |  |

|            |            | Same function for Configuration #1 and Configuration #2.                                                                                                                                                                                                                                                                                          |  |  |

|            |            | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                                                      |  |  |

| SRAS[2:0]# | O<br>LVTTL | <b>SDRAM Row Address Strobe (SDRAM):</b> The SRAS[2:0]# signals are multiple copies (for loading purposes) of the same logical SRASx signal used to generate SDRAM command. These commands are encoded on SRASx/SCASx/WE signals. When SRASx is sampled active at the rising edge of the SDRAM clock, the row address is latched into the SDRAMs. |  |  |

|            |            | Same function for Configuration #1 and Configuration #2.                                                                                                                                                                                                                                                                                          |  |  |

|            |            | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                                                      |  |  |

Signal SRAS3# / MAB5

SCAS[2:0]#

SCAS3# / MAB4

|            | Table 2. DRAM Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| O          | Configuration #1:                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LVTTL      | <b>SDRAM Row Address Strobe 3 (SDRAM):</b> The SRAS3# signal is a copy (for loading purposes) of the same logical SRASx signal. It generates SDRAM commands encoded on SRASx/SCASx/WE signals. When SRASx is sampled active at the rising edge of the SDRAM clock, the row address is latched into the SDRAMs.                                                                                                                                                             |

|            | Configuration #2:                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            | <b>Extra Copy of Memory Address 5 (EDO/SDRAM):</b> MAB[5] is an extra copy of Memory Address 5 and should be routed to the closest DIMM socket to the PAC(socket #0). MAB5 will change value if the current or next access is directed to a memory address range mapped to DIMM socket #0. During accesses directed to DIMM socket #1 or #2, these signals will preserve the previously driven state. This signal behaves logically and electrically the same way as MAA5. |

|            | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                                                                                                                                                                               |

| O<br>LVTTL | <b>SDRAM Column Address Strobe (SDRAM):</b> The SCAS[2:0]# signals are multiple copies (for loading purposes) of the same logical SCASx signal used to generate SDRAM commands. These commands are encoded on SRASx/SCASx/WE signals. When SCASx is sampled active at the rising edge of the SDRAM clock, the column address is latched into the SDRAMs.                                                                                                                   |

|            | Same function for Configuration #1 and Configuration #2.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                                                                                                                                                                               |

| 0          | Configuration #1:                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LVTTL      | <b>SDRAM Column Address Strobe 3 (SDRAM):</b> The SCAS3# signal is a physical copy (for loading purposes) of the same logical SCASx signal used to generate SDRAM command encoded on SRASx/SCASx/WE signals. When SCASx is sampled active at the rising edge of the SDRAM clock, the column address is latched into the SDRAMs. These signals drive the SDRAM array directly without any external buffers.                                                                 |

|            | Configuration #2:                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            | Extra Copy of Memory Address 4 (EDO/SDRAM): MAB[4] is an extra copy of                                                                                                                                                                                                                                                                                                                                                                                                     |

int\_l

Configuration #2:Extra Copy of Memory Address 4 (EDO/SDRAM): MAB[4] is an extra copy of<br/>Memory Address 4 and should be routed to the closest DIMM socket to the<br/>PAC(socket #0). MAB4 will change value if the current or next access is directed<br/>to a memory address range mapped to DIMM socket #0. During accesses<br/>directed to DIMM socket #1 or #2, these signals will preserve the previously<br/>driven state. This signal behaves logically and electrically the same way as<br/>MAA4.These signals have programmable buffer strengths for optimization under different<br/>signal loading conditions.

| Signal    | Туре         | Description                                                                                                                                                                                                                                                                                                                |  |  |

|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAA[13:0] | O<br>LVTTL   | <b>Memory Address A (EDO/SDRAM):</b> MAA[13:0] is used to provide the multiplexed row and column address to DRAM. In configuration #1, the MA[13:2] lines are externally buffered to drive the address of the DRAM. External buffering is not required for these signals in Configuration #2.                              |  |  |

|           |              | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                               |  |  |

| MAB[1:0]  | O<br>LVTTL   | <b>Lower Memory Address Copy (EDO/SDRAM):</b> MAB[1:0] are the lower two bits of the memory address used to complete the row and column address to DRAM. These two bits are toggled during the burst phase for EDO cycles.                                                                                                 |  |  |

|           |              | MAB[1:0] will change value if the current or next access is directed to a memory address range mapped to DIMM socket #0 (the closest DIMM to the PAC). During accesses directed to DIMM socket #1 or #2, these signals will preserve the previously driven state.                                                          |  |  |

|           |              | Same function for Configuration #1 and Configuration #2.                                                                                                                                                                                                                                                                   |  |  |

|           |              | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                               |  |  |

| WE[3:0]#  | O<br>LVTTL   | Write Enable Signal (EDO/SDRAM): The WE[3:0]# signals are multiple copies (for loading purposes) of the same logical WEx# signal used to generate write strobe for EDO or SDRAM command. These commands are encoded on SRASx/SCASx/WEx# signals. These signals drive the DRAM array directly without any external buffers. |  |  |

|           |              | Same function for Configuration #1 and Configuration #2.                                                                                                                                                                                                                                                                   |  |  |

|           |              | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                               |  |  |

| MD[63:0]  | I/O<br>LVTTL | <b>Memory Data (EDO/SDRAM):</b> These signals are used to interface to the DRAM data bus.                                                                                                                                                                                                                                  |  |  |

|           |              | These signals are internally connected to 20 $k\Omega$ pull-down resistors.                                                                                                                                                                                                                                                |  |  |

|           |              | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                               |  |  |

| MECC[7:0] | I/O<br>LVTTL | Memory ECC Data (EDO/SDRAM): These signals carry Memory ECC data during DRAM access.                                                                                                                                                                                                                                       |  |  |

|           |              | These signals are internally connected to 20 k $\Omega$ pull-down resistors. These signals are outputs when PAC is writing to the DRAM; otherwise, they will be inputs.                                                                                                                                                    |  |  |

|           |              | These signals have programmable buffer strengths for optimization under different signal loading conditions.                                                                                                                                                                                                               |  |  |

#### Table 2. DRAM Interface Signals

| Signal | Туре         | Description                                                                                                                                                                                                                                                                                                                                 |  |

|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CKE    | I/O<br>LVTTL | <b>Clock Enable (SDRAM):</b> This signal is used to enable/disable the SDRAM clock (internally within the SDRAM component). When "high," it enables normal SDRAM operation. When "low," it deactivates the SDRAM clock and the SDRAM components enter Power Down Mode. Note that all SDRAM banks must be pre-charged before CKE is negated. |  |

|        |              | The SDRAM Power Down Mode is used only for the PAC DRAM array power management.                                                                                                                                                                                                                                                             |  |

|        |              | The CKE signal must be externally buffered, using a CMOS buffer, if SDRAM power management capability is utilized.                                                                                                                                                                                                                          |  |

|        |              | Note that starting with the assertion of RSTIN#, and until 4 clocks of the CPURST# signal negation, this signal will be controlled as an input to allow sampling of the strap attached to this pin. CKE is connected to a 20 k $\Omega$ internal pull-down resistor.                                                                        |  |

#### 2.1.3. PCI INTERFACE SIGNALS

#### Table 3. PCI Interface Signals

| Name     | Туре                 | Description                                                                                                                                                                      |  |  |  |

|----------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | Standard PCI Signals |                                                                                                                                                                                  |  |  |  |

| AD[31:0] | I/O PCI              | <b>PCI Address/Data:</b> These signals are connected to the PCI address/data bus.<br>Address is driven with FRAME# assertion and data is driven or received on following clocks. |  |  |  |

| DEVSEL#  | I/O PCI              | <b>Device Select:</b> Assertion indicates that a PCI target device has decoded its address as the target of the current access. PAC asserts DEVSEL# if the current access is:    |  |  |  |

|          |                      | within Main Memory                                                                                                                                                               |  |  |  |

|          |                      | within the A.G.P. aperture     resides on the A.G.P. interface                                                                                                                   |  |  |  |

|          |                      | a configuration cycle targeting the PAC                                                                                                                                          |  |  |  |

|          |                      | As an input, this signal indicates whether a device on the bus has been selected.                                                                                                |  |  |  |

| FRAME#   | I/O PCI              | <b>Frame:</b> Assertion indicates the address phase of a PCI transfer. Negation indicates that one more data transfer is desired by the cycle initiator.                         |  |  |  |

| IRDY#    | I/O PCI              | Initiator Ready: Asserted when the initiator is ready for a data transfer.                                                                                                       |  |  |  |

| Name       | Туре       | Description                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                      |                          |                                           |

|------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|

| C/BE[3:0]# | I/O PCI    | <b>Command/Byte Enable:</b> The command is driven with FRAME# assertion. Byte enables corresponding to supplied or requested data are driven on following clocks. PCI Bus command encoding and types are listed below.                                                                                                                                               |                                                                                                                                      |                          |                                           |

|            |            | C/BE[3:0]#                                                                                                                                                                                                                                                                                                                                                           | Command Type                                                                                                                         | C/BE[3:0]#               | Command Type                              |

|            |            | 0000                                                                                                                                                                                                                                                                                                                                                                 | Interrupt Acknowledge                                                                                                                | 1000                     | Reserved                                  |

|            |            | 0001                                                                                                                                                                                                                                                                                                                                                                 | Special Cycle                                                                                                                        | 1001                     | Reserved                                  |

|            |            | 0010                                                                                                                                                                                                                                                                                                                                                                 | I/O Read                                                                                                                             | 1010                     | Configuration Read                        |

|            |            | 0011                                                                                                                                                                                                                                                                                                                                                                 | I/O Write                                                                                                                            | 1011                     | Configuration Write                       |

|            |            | 0100                                                                                                                                                                                                                                                                                                                                                                 | Reserved                                                                                                                             | 1100                     | Memory Read Multiple                      |

|            |            | 0101                                                                                                                                                                                                                                                                                                                                                                 | Reserved                                                                                                                             | 1101                     | Reserved (Dual Addr Cyc)                  |

|            |            | 0110                                                                                                                                                                                                                                                                                                                                                                 | Memory Read                                                                                                                          | 1110                     | Memory Read Line                          |

|            |            | 0111                                                                                                                                                                                                                                                                                                                                                                 | Memory Write                                                                                                                         | 1111                     | Memory Write and Invalidate               |

| PAR        | I/O PCI    |                                                                                                                                                                                                                                                                                                                                                                      | <b>Parity:</b> A single parity bit is provided over AD[31:0] and C/BE[3:0]. Even parity is generated across AD[31:0] and C/BE[3:0]#. |                          |                                           |

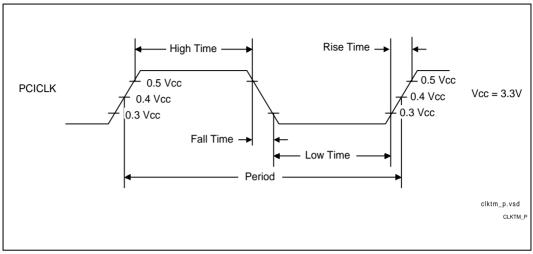

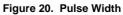

| PERR#      | I/O PCI    | <b>PCI Parity Error:</b> Pulsed by an agent receiving data with bad parity one clock after PAR is asserted. PAC generates PERR# active if it detects a parity error on the PCI bus and the PERR# Enable bit in the PCICMD register is set.                                                                                                                           |                                                                                                                                      |                          |                                           |