ASSP MANUAL

# SCSI-II PROTOCOL CONTROLLER

MB86604A/MB86604L DESIGN MANUAL

MB86604A/MB86604L SCSI-II PROTOCOL CONTROLLER DESIGN MANUAL

- 1. The products described in this manual and the specifications thereof may be changed without prior notice. To obtain up-to-date information and/or specifications, contact your Fujitsu sales representative or Fujitsu authorized dealer.

- 2. Fujitsu will not be liable for infringement of copyright, industrial property right, or other rights of a third party caused by the use of information or drawings described in this manual.

- 3. The contents of this manual may not be transferred or copied without the express permission of Fujitsu.

- 4. The products contained in this document are not internded for use with equipments which require extermely high reliability such as aerospace equipmenta, undersea repeaters, nuclear control systems or medical equipments for life support.

- 5. Some of the products described in this manual may be strategic materials (or special technology) as defined by the Foreign Exchange and Foreign Trade Control Law. In such cases, the products or portions thereof must not be exported without permission as defined under the Law.

<sup>© 1996</sup> FUJITSU LIMITED Printed in Japan

### Contents

| CHAPTER 1 OVERVIEW                                                                           |    |

|----------------------------------------------------------------------------------------------|----|

| 1.1 SCSI PROTOCOL CONTROLLER FEATURES                                                        | 2  |

| 1.2 BLOCK CONFIGURATION                                                                      | 4  |

| 1.3 BLOCK DIAGRAM                                                                            | 6  |

| CHAPTER 2 INPUT/OUTPUT PINS                                                                  | 7  |

| 2.1 MB86604A PIN ASSIGNMENT                                                                  | 8  |

| 2.2 MB86604L PIN ASSIGNMENT                                                                  |    |

| 2.3 EXPLANATION OF PIN FUNCTIONS (SCSI INTERFACE)                                            |    |

| 2.4 EXPLANATION OF PIN FUNCTIONS (MPU INTERFACE)                                             |    |

| 2.5 EXPLANATION OF PIN FUNCTIONS (DMA INTERFACE)                                             | 14 |

| 2.6 EXPLANATION OF PIN FUNCTIONS (CONTROL SIGNAL)                                            |    |

| CHAPTER 3 FUNCTIONS                                                                          |    |

| 3.1 INTERNAL REGISTERS                                                                       |    |

| 3.2 BASIC CONTROL REGISTER                                                                   |    |

| 3.2.1 Output Data Register (Write)                                                           |    |

| 3.2.2 Input Data Register (Read)                                                             |    |

| 3.2.3 Direct Control Register (WRITE)                                                        |    |

| 3.2.4 SPC Status Register (READ)                                                             |    |

| 3.2.5 Nexus Status Register (READ)                                                           |    |

| 3.2.6 SEL/RESEL ID Register (WRITE)                                                          |    |

| 3.2.7 Interrupt Status Register (READ)                                                       |    |

| 3.2.8 Command Register (WRITE)                                                               |    |

| 3.2.9 Command Step Register (READ)                                                           |    |

| 3.2.10 Data Block Register (READ/WRITE)                                                      |    |

| 3.2.11 Data Byte/MC Byte Register (READ/WRITE)<br>3.2.12 DIAGNOSTIC Control Register (WRITE) |    |

| 3.2.12 DIAGNOSTIC Control Register (WRITE)                                                   |    |

| 3.2.13 SCSI Control Signal Status Register (READ)                                            |    |

| 3.2.15 Transfer Period Register (READ/WRITE)                                                 |    |

| 3.2.16 Transfer Offset Register (READ/WRITE)                                                 |    |

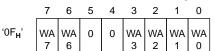

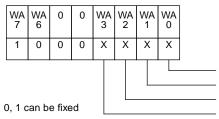

| 3.2.17 Window Address Register (WRITE)                                                       |    |

| 3.2.17 Window Address Register (WRITE)                                                       |    |

| 3.2.19 BASIC Control Register Access                                                         |    |

| 3.3 INITIAL SETTING REGISTER WINDOW                                                          |    |

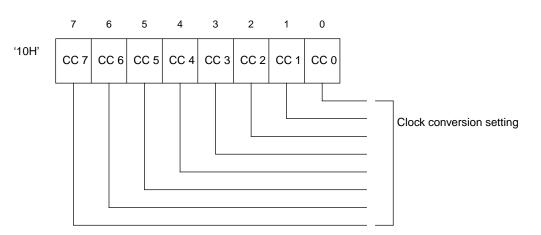

| 3.3.1 Clock Conversion Setting Register (WRITE/READ)                                         |    |

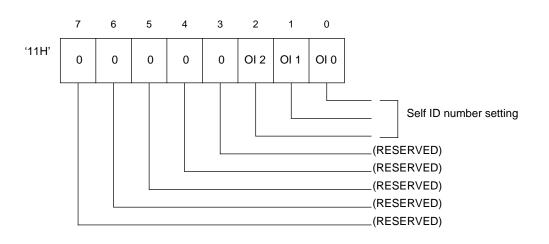

| 3.3.2 Self ID Setting Register (WRITE/READ)                                                  | 50 |

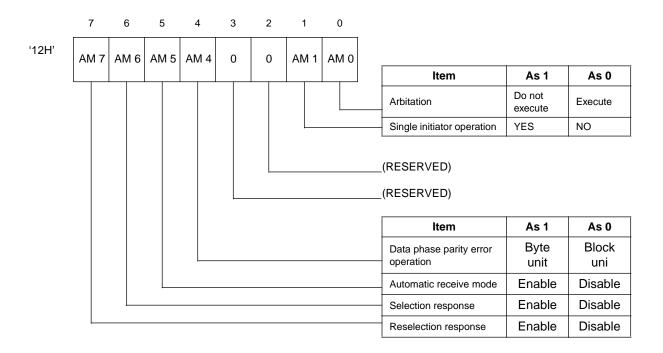

| 3.3.3 Response Mode Setting Register (READ/WRITE)                                            |    |

| 3.3.3.1 BIT 7 (Reselection Response)                                                         |    |

| 3.3.3.2 BIT 6 (Selection Response)                                                           |    |

| 3.3.3.3 BIT 5 (Automatic Receive Mode)                                                       |    |

| 3.3.3.4 BIT 4 (Operation for Data Phase Parity Error)                                        |    |

| 3.3.3.5 BIT 1 (Single Initiator Option)                                                      |    |

| 3.3.3.6 BIT 0 (Arbitration)                                                                  |    |

| 3.3.4 SEL/RESEL Mode Setting Register (WRITE/READ)                                           |    |

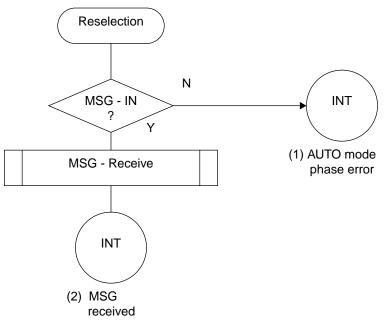

| 3.3.4.1 Initiator Automatic Reselection Response                                             |    |

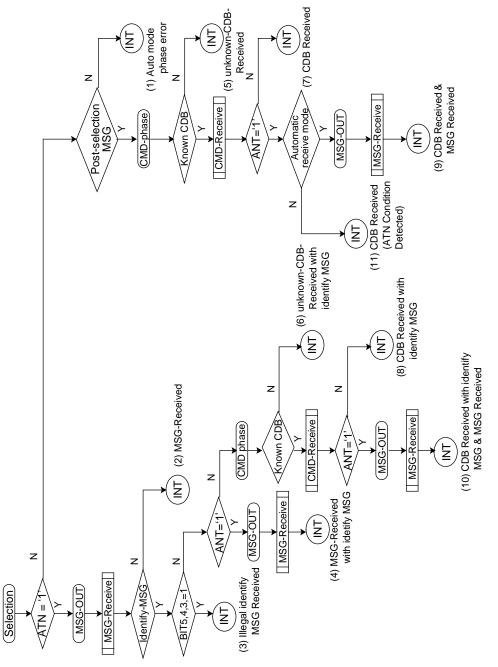

| 3.3.4.2 Target Automatic Selection Response                                                  |    |

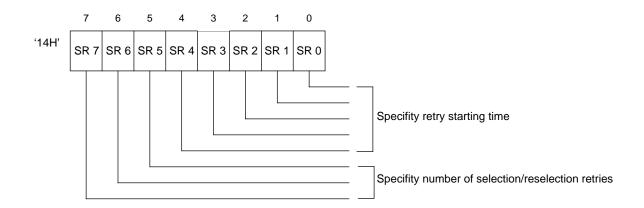

| 3.3.5 SEL/RESEL Retry Setting Register (READ/WRITE)                                          |    |

| 3.3.6 SEL/RESEL Timeout Setting Register (WRITE/READ)                                        |    |

| 3.3.7 REQ/ACK Timeout Setting Register (WRITE/READ)                                          |    |

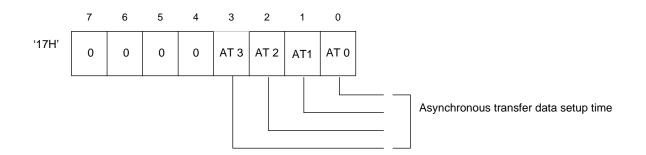

| 3.3.8 Asynchronous Setup Time Setting Register (WRITE/READ)                                  |    |

| 3.3.9 Parity Error Detect Setting Register (WRITE/READ)                                      |    |

| 3.3.10 Interrupt Enable Setting Register (WRITE/READ)                                        |    |

| 3.3.11 Group 6/7 Command Length Setting Register (WRITE/READ)                                |    |

| 3.3.12 DMA System Setting Register (WRITE/READ)                                              |    |

|         | Automatic Operation Mode Setting Register (WRITE/READ)                  |     |

|---------|-------------------------------------------------------------------------|-----|

| 3.3.14  | SPC Timeout Setting Register (WRITE/READ)                               | 86  |

|         | 5 Revision Indication Register (WRITE/READ)                             |     |

|         | S BUFFER WINDOW                                                         |     |

| 3.5 US  | ER PROGRAM MEMORY WINDOW                                                | 90  |

| 3.6 SC  | AM REGISTER WINDOW                                                      | 92  |

| 3.6.1   | SCAM REGISTER93                                                         |     |

| CHAPTE  | R 4 COMMANDS 95                                                         |     |

|         | C COMMANDS                                                              | 96  |

|         | T OF INITIATOR COMMANDS                                                 |     |

|         | List of Initiator Sequential Command Functions                          |     |

|         | List of Initiator Discrete Command Functions                            |     |

|         | T OF TARGET COMMANDS                                                    |     |

| 4.3.1   |                                                                         |     |

|         | List of Target Discrete Command Functions                               | 106 |

|         | T OF COMMON COMMANDS                                                    |     |

| 4.4 LIS | List of Common Command Functions                                        |     |

|         | Common Command Step Codes                                               |     |

|         | OGRAMMABLE COMMANDS                                                     |     |

|         |                                                                         |     |

| 4.5.1   |                                                                         |     |

| 4.5.2   | TEST AND Command                                                        |     |

| 4.5.3   | COMPARE Command                                                         | -   |

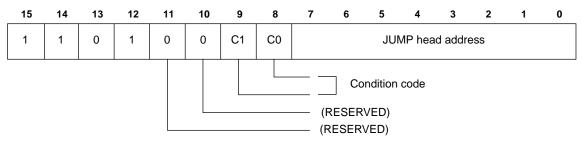

| 4.5.4   | Conditional Branch Command                                              |     |

| 4.5.5   | MOVE Command                                                            |     |

| 4.5.6   | STOP Command                                                            |     |

| 4.5.7   |                                                                         |     |

|         | R 5 OPERATIONS                                                          |     |

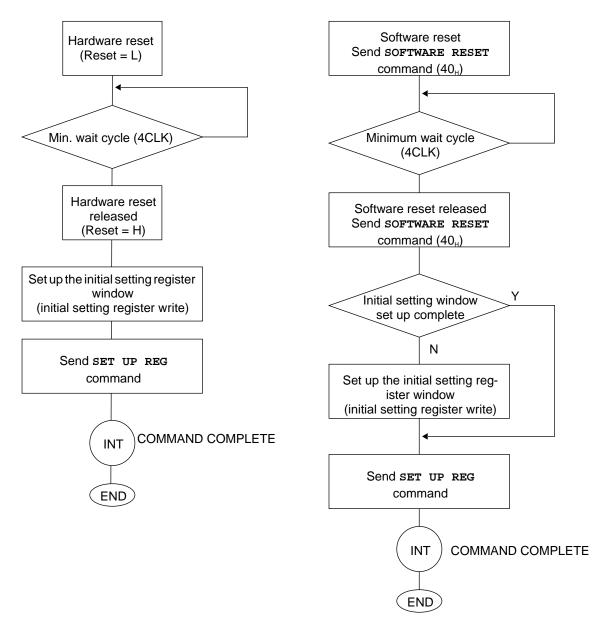

| 5.1 SP  | C INITIALIZATION                                                        | 122 |

| 5.2 INI | TIAL SETTINGS FOR SPC INTERNAL REGISTERS                                | 124 |

| 5.3 SC  | SI BUS PHASE                                                            | 128 |

| 5.3.1   | Message, Command, and Status Phases                                     | 130 |

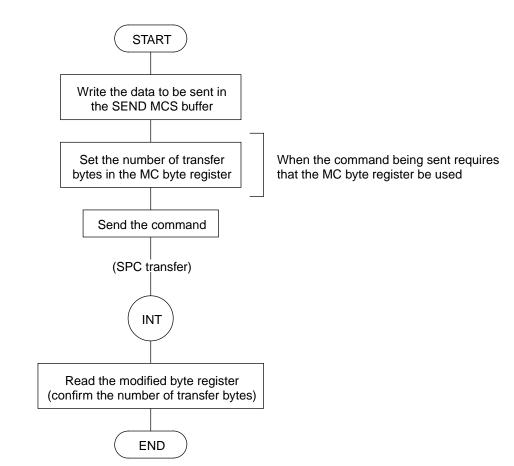

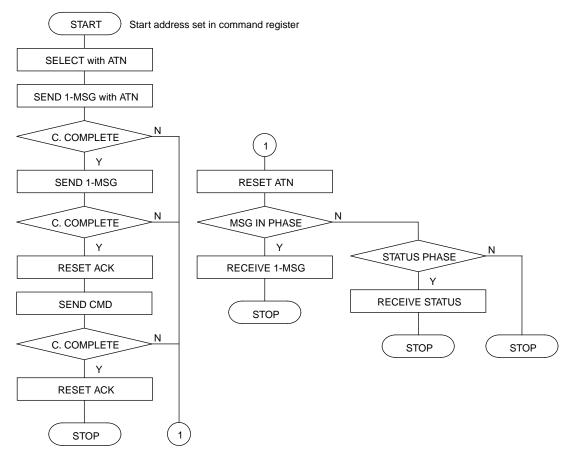

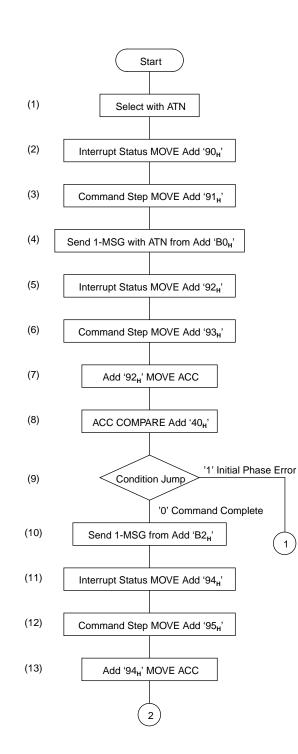

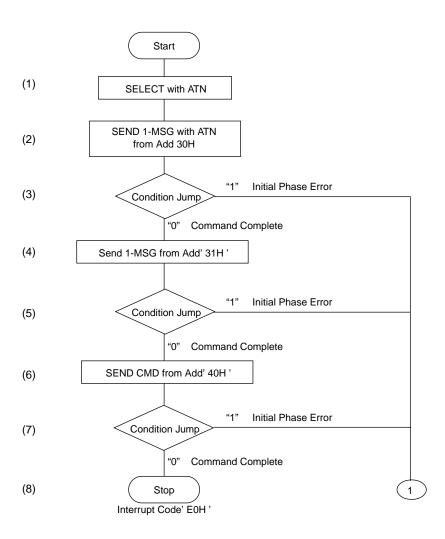

| 5.3     | 1.1 Send Flowchart for Message, Command, Status Phases                  | 131 |

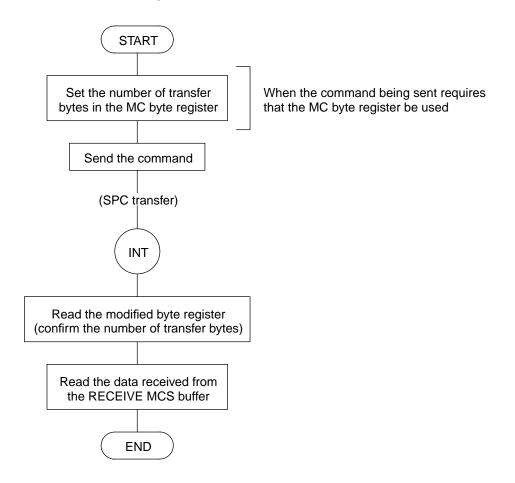

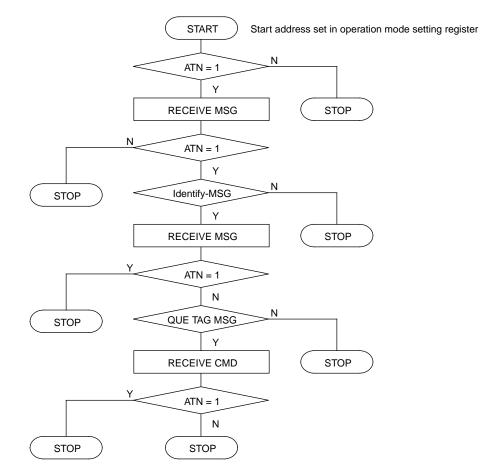

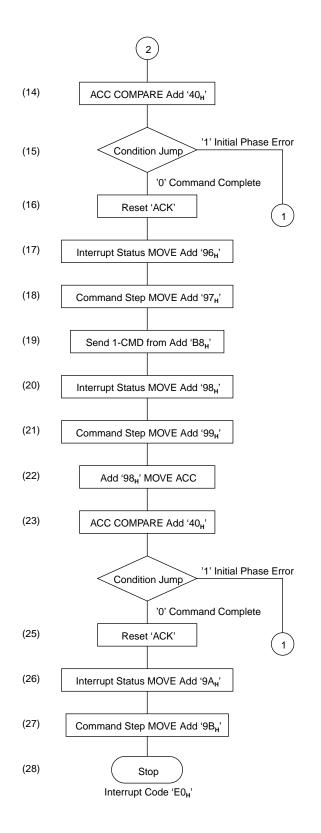

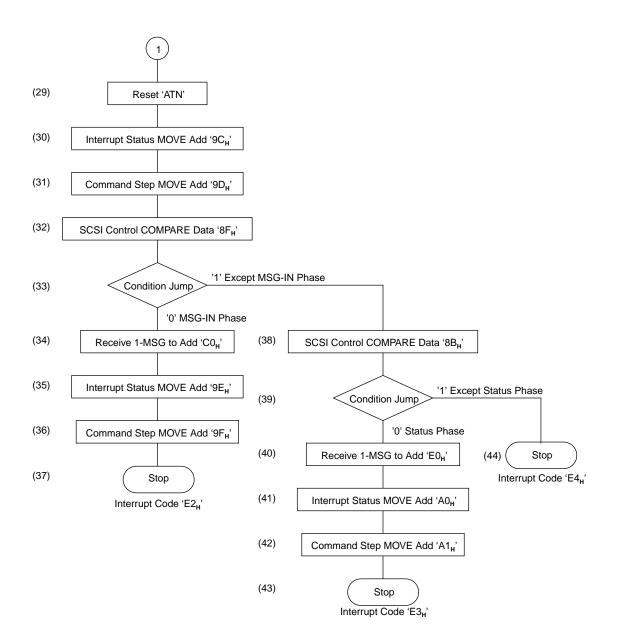

|         | 1.2 Receive Flowchart for Message, Command, Status Phases               |     |

|         | Data Phase                                                              |     |

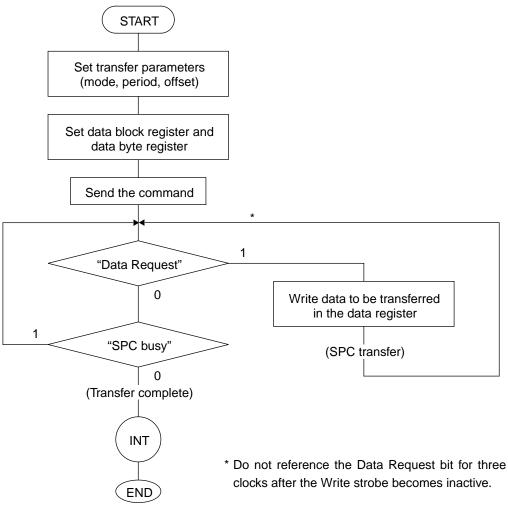

|         | 2.1 Send Flowchart for Program Transfer Mode                            |     |

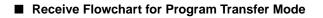

|         | 2.2 Receive Flowchart for Program Transfer Mode                         |     |

|         | ER PROGRAM OPERATION (INITIATOR)                                        |     |

| 5.4.1   |                                                                         |     |

| 5.4.2   |                                                                         |     |

| 5.4.3   |                                                                         |     |

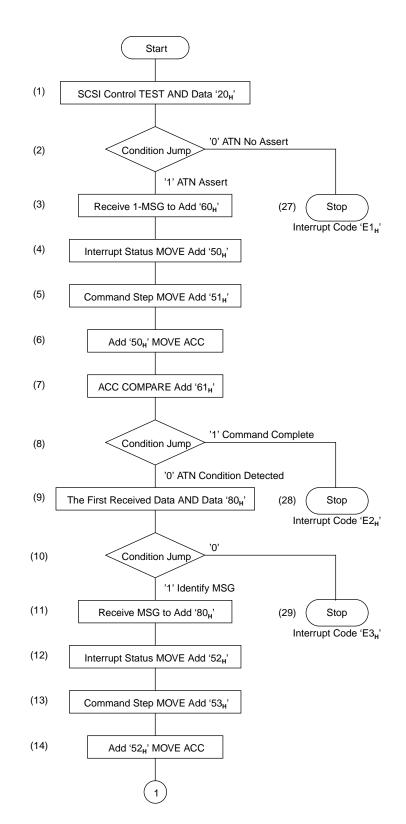

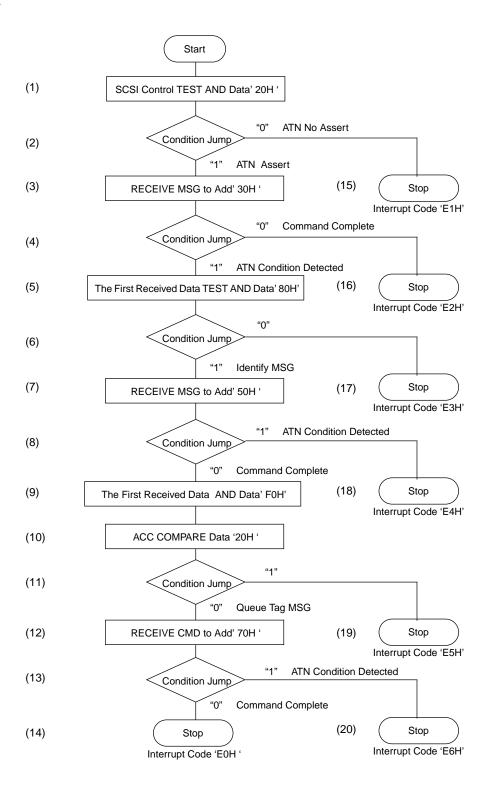

|         | ER PROGRAM OPERATION (TARGET USER PROGRAMMING EXAMPLE)                  |     |

|         |                                                                         |     |

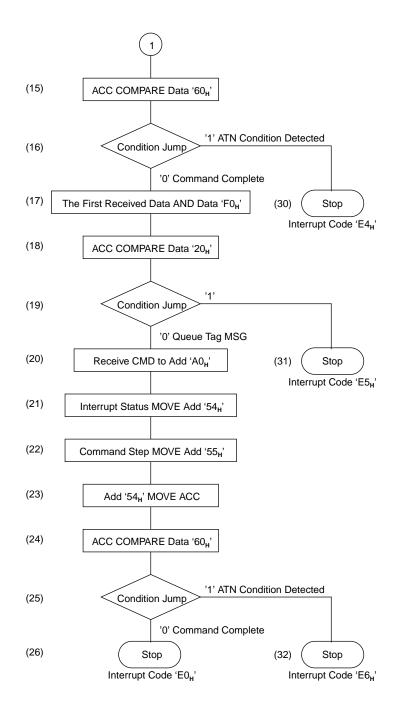

| 5.5.1   | Explanation of Target User Programming Example 1 (Address 00H to 21H)   |     |

|         | a Explanation of Target User Programming Example 1 (Address 22H to 4BH) |     |

|         | Explanation of Target User Programming Example 2 (Address 00H to 8FH)   |     |

|         | Explanation of Target User Programming Example 1 (Address 50H to BFH)   |     |

|         |                                                                         |     |

|         | ERRUPT CODES                                                            |     |

| 5.7.1   | Interrupts Related to SCSI RESET                                        |     |

| 5.7.2   | Interrupts Related to Transfers                                         |     |

| 5.7.3   | Interrupts Related to Phase Transitions                                 |     |

| 5.7.4   | Interrupts Related to REPORT                                            |     |

| 5.7.5   | Interrupts Related to Selection/Reselection                             | 162 |

| 5.7.6   | Interrupts Related to Automatic Selection/Reselection Response          |     |

|         | ERRUPT CODES AND COMMAND STEPS                                          |     |

|         | C OPERATION DURING ERROR DETECTION                                      |     |

| 5.9.1   | When an Offset Error is Detected                                        |     |

| 5.9.2   | When a Short Transfer Period Error is Detected                          |     |

| 5.9.3   | When a SCSI Parity Error is Detected                                    |     |

| 0.9.0   |                                                                         | 174 |

| 5.9.4 When a MPU Parity Error is Detected                         |     |

|-------------------------------------------------------------------|-----|

| 5.9.5 When a DMA Parity Error is Detected                         | 178 |

| 5.9.6 Terminate Procedure                                         |     |

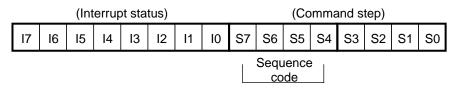

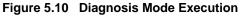

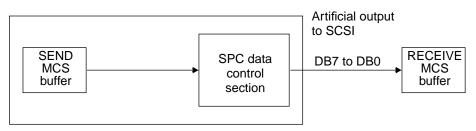

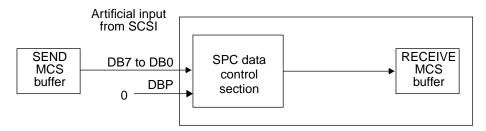

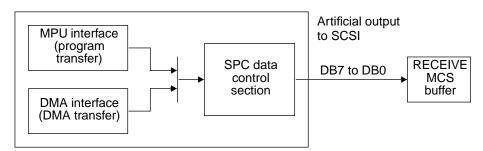

| 5.10 DIAGNOSIS MODE                                               |     |

| 5.10.1 SCSI Control Signals                                       |     |

| 5.10.2 SCSI Data Bus Signal                                       |     |

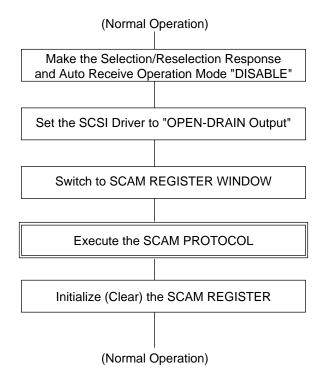

| 5.11 SCAM FUNCTION (only for MB86604L)                            |     |

| CHAPTER 6 SYSTEM CONFIGURATION EXAMPLE                            |     |

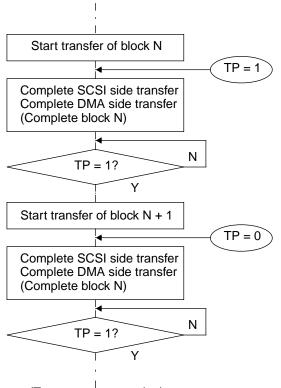

| 6.1 TP SIGNAL CONTROL                                             |     |

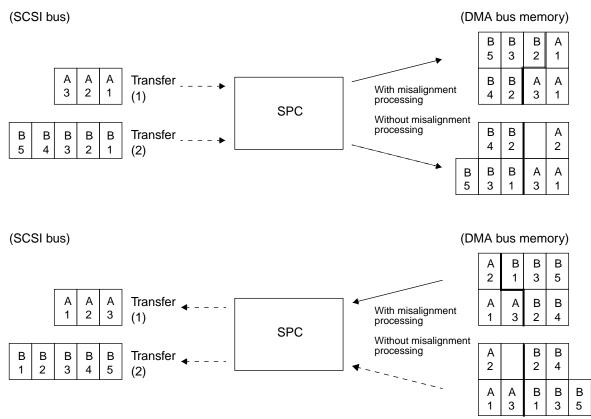

| 6.2 DMA MISALIGNMENT PROCESSING                                   |     |

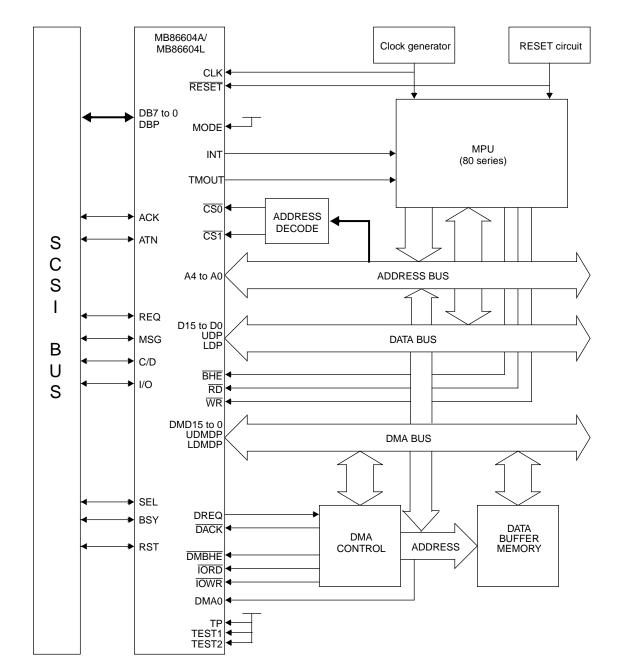

| 6.3 SYSTEM CONFIGURATION EXAMPLE 1 (80 SERIES, SEPARATE BUS TYPE) |     |

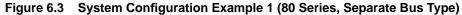

| 6.4 SYSTEM CONFIGURATION EXAMPLE 2 (68 SERIES, SEPARATE BUS TYPE) |     |

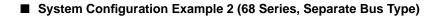

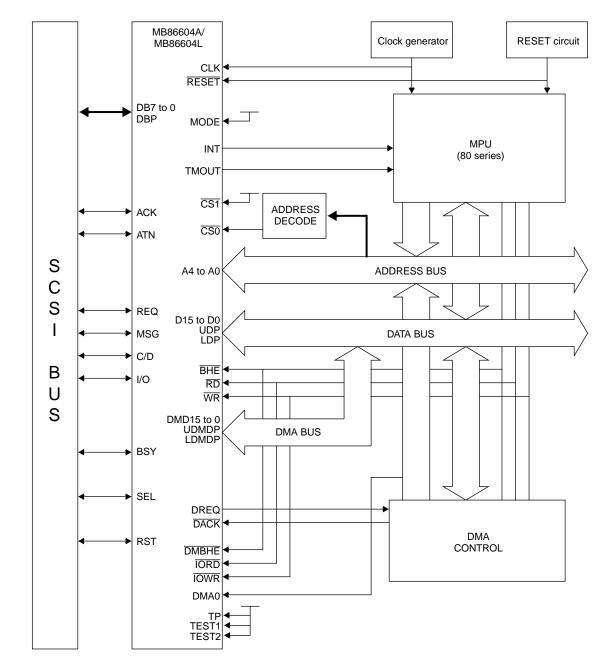

| 6.5 SYSTEM CONFIGURATION EXAMPLE 3 (80 SERIES, COMMON BUS TYPE)   |     |

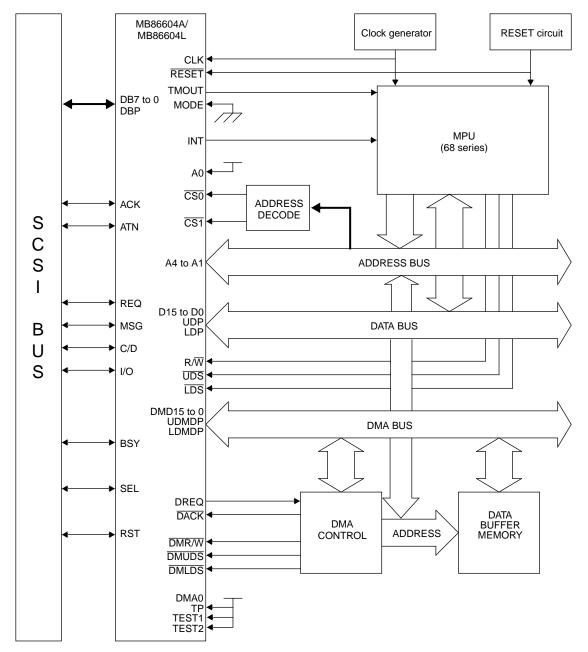

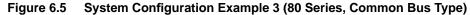

| 6.6 SYSTEM CONFIGURATION EXAMPLE 4 (68 SERIES, COMMON BUS TYPE)   |     |

| APPENDIX                                                          |     |

| APPENDIX A PACKAGE DIMENSIONS                                     |     |

| APPENDIX B PARITY CHECK AND PARITY GENERATE FLOWS                 |     |

| APPENDIX C INITIATOR COMMAND STEP CODES                           |     |

| APPENDIX D TARGET COMMAND STEP CODES                              |     |

| APPENDIX E FLOWCHART FOR INITIATOR USER PROGRAM EXAMPLES          |     |

| APPENDIX F FLOWCHART FOR TARGET USER PROGRAM EXAMPLES             |     |

| APPENDIX G LIST OF INTERRUPT CODES AND COMMANDS                   |     |

| G.1 Initiator Commands                                            |     |

| G.2 Target Commands                                               |     |

| G.3 Common Commands                                               |     |

| G.4 Automatic Selection/Reselection Response                      | 248 |

|                                                                   |     |

### Figures

| Figure 1.1a Package Drawing                                                            | 3    |

|----------------------------------------------------------------------------------------|------|

| Figure 1.1b Package Drawing                                                            | 3    |

| Figure 1.3 Block Diagram                                                               | 6    |

| Figure 2.1 MB86604A Pin Assignment Diagram                                             | 8    |

| Figure 2.2 MB86604L Pin Assignment Diagram                                             | . 10 |

| Figure 3.1 Internal Flow of Information                                                |      |

| Figure 3.2.3 Transfer Flowchart (Direct Control Register: BIT 7)                       |      |

| Figure 3.2.8 Relationship between Command Register (BIT 7 = 1) and User Program Memory |      |

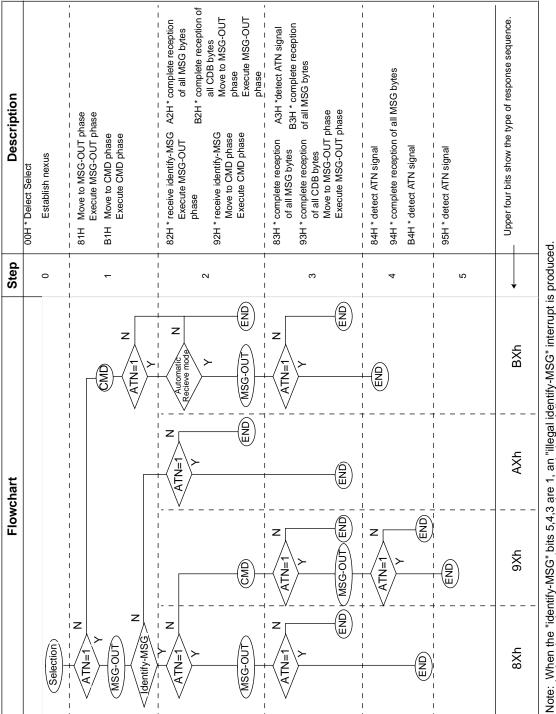

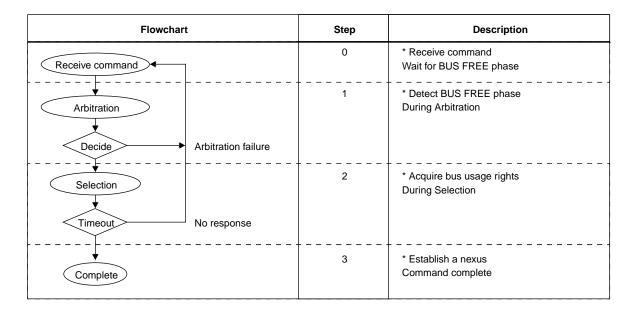

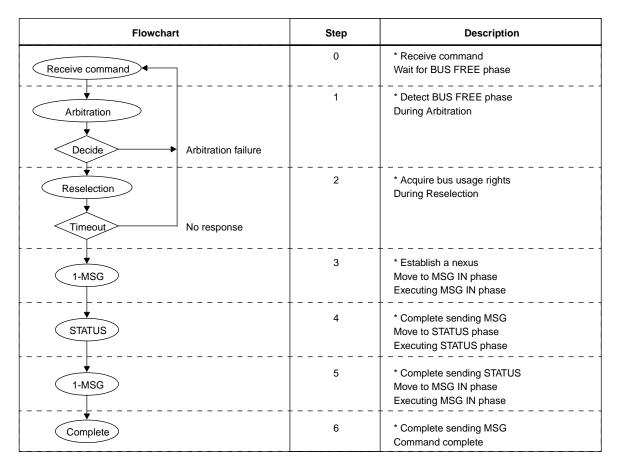

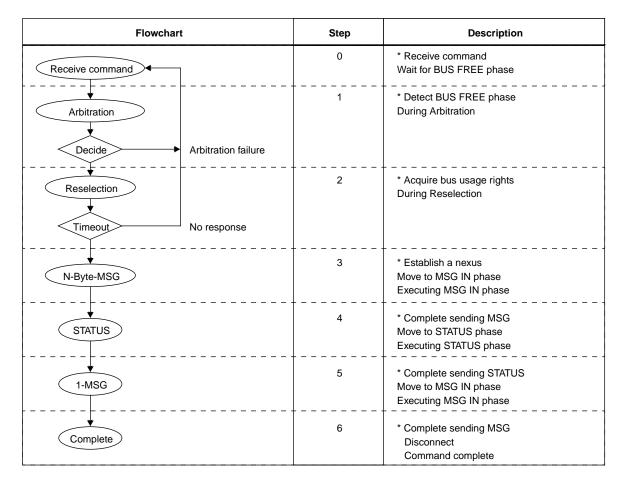

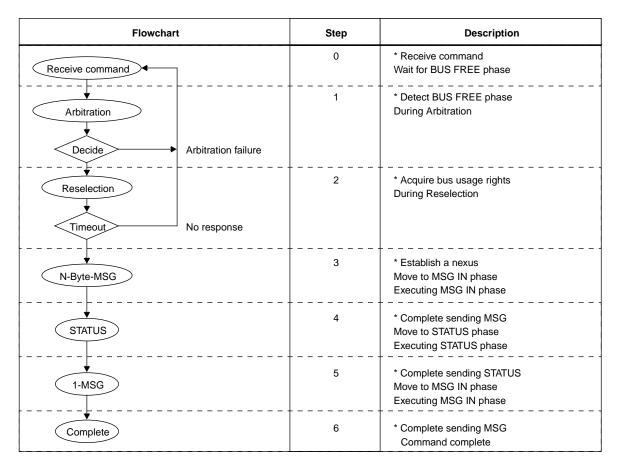

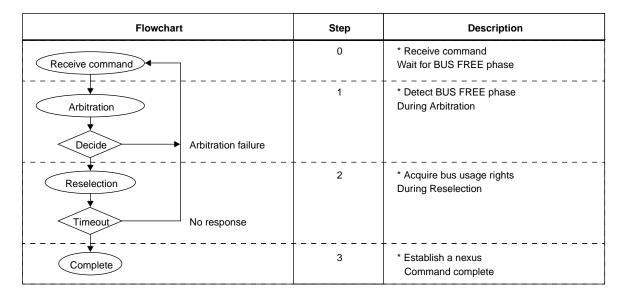

| Figure 3.3.4.1 Initiator Automatic Reselection Response Flowchart                      |      |

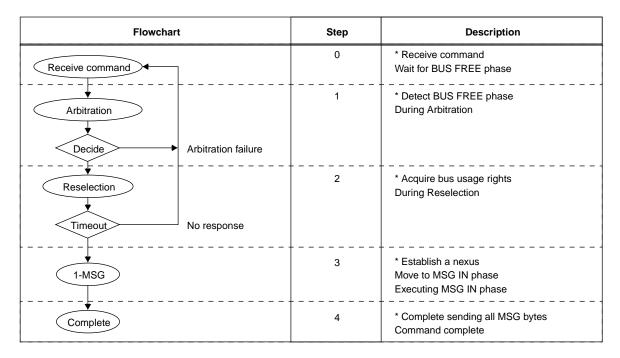

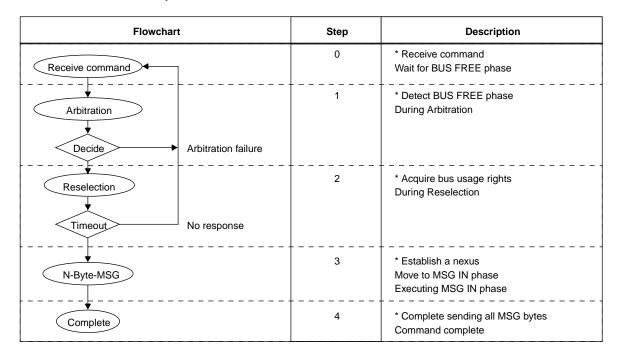

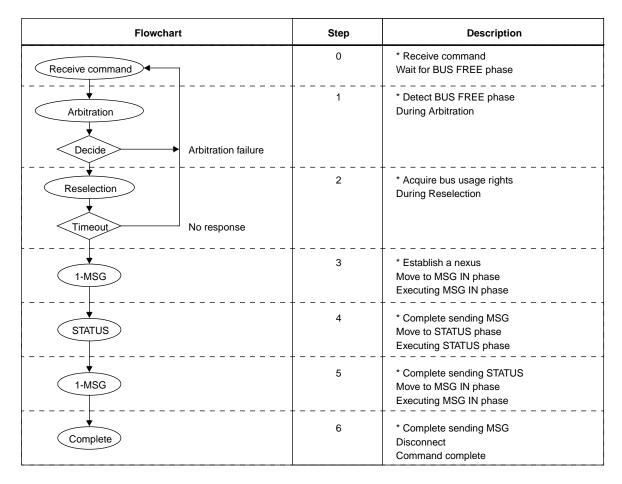

| Figure 3.3.4.2a Target Automatic Selection Response Flowchart                          | . 66 |

| Figure 3.3.4.2b Target Automatic Selection Response Sequence (Step Code Chart)         | . 67 |

| Figure 5.2 Initial Setting Flow After Hardware Reset or Software Reset                 |      |

| Figure 5.3.1.1 Send Flowchart for Message, Command, Status Phases                      |      |

| Figure 5.3.1.2 Receive Flowchart for Message, Command, Status Phases                   |      |

| Figure 5.3.2.1 Send Flowchart for Program Transfer Mode                                |      |

| Figure 5.3.2.2 Receive Flowchart for Program Transfer Mode                             | 135  |

| Figure 5.4 Summary Flowchart of Initiator User Programming Example                     |      |

| Figure 5.5 Summary Flowchart of Target User Programming Example                        |      |

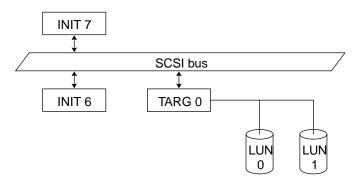

| Figure 5.6a System Configuration (Example of Command Queuing Execution)                | 152  |

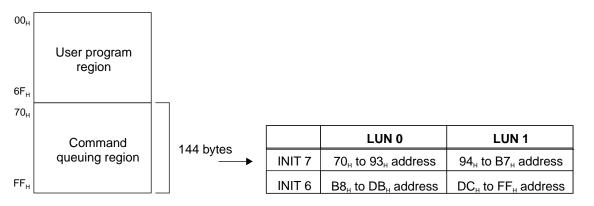

| Figure 5.6b Allocation of Command Queuing Region                                       |      |

| Figure 5.6c Command Queuing Operation Sequence                                         |      |

| Figure 5.10 Diagnosis Mode Execution                                                   |      |

| Figure 5.10.1 Flow of SCSI Control Signals During Diagnosis Mode                       |      |

| Figure 5.10.2a Sending Messages, Commands, and Statuses in Diagnosis Mode              |      |

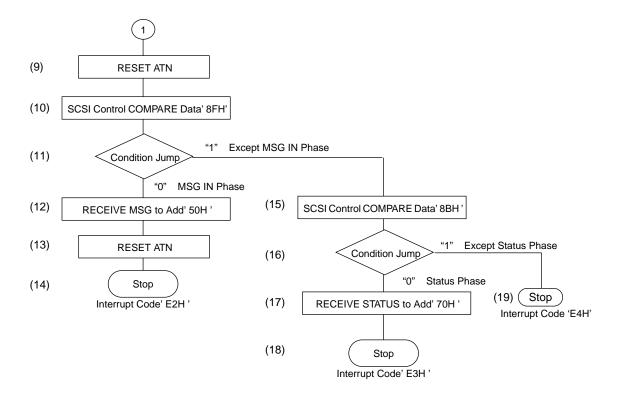

| Figure 5.10.2b Receiving Messages, Commands, and Statuses in Diagnosis Mode            | 184  |

| Figure 5.10.2c Sending Data in Diagnosis Mode                                          |      |

| Figure 5.10.2d Receiving Data in Diagnosis Mode                                        |      |

| Figure 6.1 Flowchart for TP Signal Control Example                                     |      |

| Figure 6.2 DMA Misalignment Processing Example                                         | 189  |

| Figure 6.3 System Configuration Example 1 (80 Series, Separate Bus Type)               | 190  |

| Figure 6.4 System Configuration Example 2 (68 Series, Separate Bus Type)               |      |

| Figure 6.5 System Configuration Example 3 (80 Series, Common Bus Type)                 |      |

| Figure 6.6 System Configuration Example 4 (68 Series, Common Bus Type)                 | 193  |

### lables

| Table 2.1 List of MB86604A Pins                                                                       |     |

|-------------------------------------------------------------------------------------------------------|-----|

| Table 2.2 List of MB86604L Pins                                                                       | 11  |

| Table 2.3 SCSI Interface Pins                                                                         |     |

| Table 2.4 MPU Interface Pins                                                                          | 13  |

| Table 2.5 DMA Interface Pins                                                                          |     |

| Table 2.6 Control Signal Pins                                                                         |     |

| Table 3.1a Internal Register Access (80 Series Mode)                                                  | 18  |

| Table 3.1b Internal Register Access (68 Series Mode)                                                  |     |

| Table 3.1c Relationship between Information Types and Registers                                       | 19  |

| Table 3.2 BASIC Control Register List                                                                 | 20  |

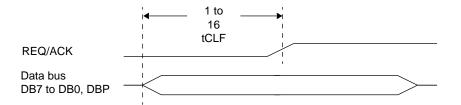

| Table 3.2.15 Relationship between Transfer Period Register and REQ/ACK Signal Minimum                 |     |

| Repetition Time                                                                                       | 43  |

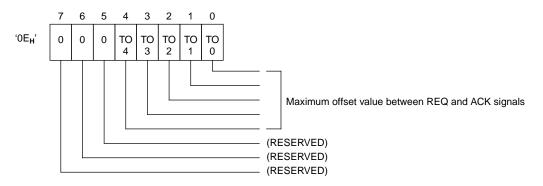

| Table 3.2.16 Relationship between Transfer Offset Register and Maximum Offset Value for               |     |

| REQ/ACK Signals                                                                                       |     |

| Table 3.3 List of Initial Setting Register Window Registers                                           |     |

| Table 3.3.1 Relationship between Clock Conversion Setting Register Bit Setting and input Frequency    |     |

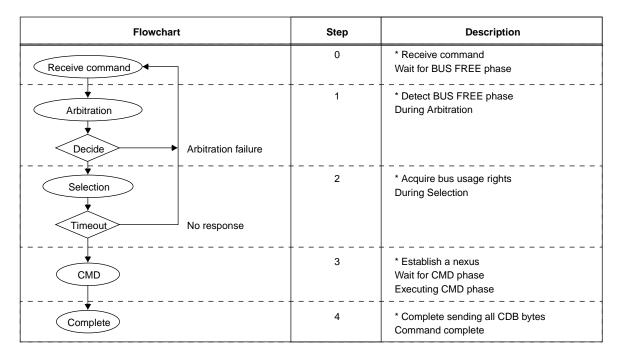

| Table 3.3.4.1 Initiator Automatic Reselection Response Sequence (Step Code Chart)                     |     |

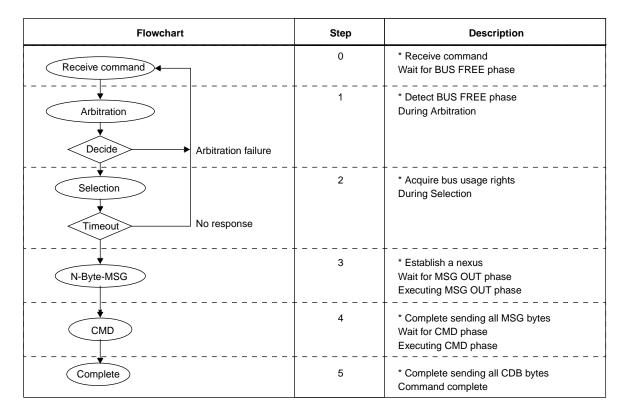

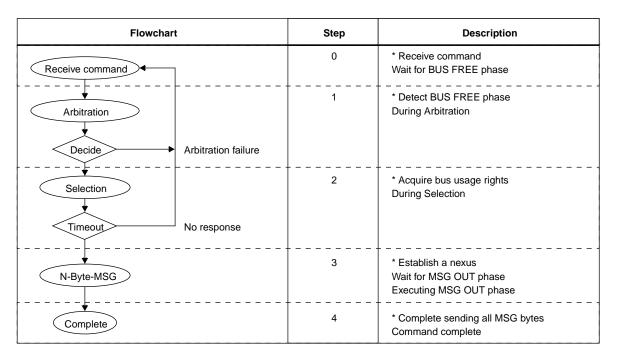

| Table 3.3.4.2 Target Automatic Selection Response Sequence (Step Code Chart)                          |     |

| Table 3.3.5 Relationship between SEL/RESEL Retry Setting Register and Number of Retries               |     |

| Table 3.3.10 Relationship between Interrupt Enable Setting Register and Interrupt Codes               |     |

| Table 3.3.11 List of Bit Setting for Group 6/7 Command Length Setting Register (Group 6)              |     |

| Table 3.3.12 List of Bit Setting for Group 6/7 Command Length Setting Register (Group 7)              | 79  |

| Table 3.4 MCS Buffer Window Buffer List                                                               | 88  |

| Table 3.5 User Program Memory Window Memory Area List                                                 |     |

| Table 4.1 List of Command Types Based on Assignment Method Differences                                | 96  |

| Table 4.2 List of Initiator Commands                                                                  | 97  |

| Table 4.2.1 List of Initiator Sequential Command Functions                                            | 98  |

| Table 4.2.2 List of Initiator Discrete Command Function                                               |     |

| Table 4.3 List of Target Commands                                                                     | 102 |

| Table 4.3.1 List of Target Sequential Command Functions                                               | 104 |

| Table 4.3.2 List of Target Discrete Command Functions                                                 | 106 |

| Table 4.4 List of Common Commands                                                                     | 107 |

| Table 4.4.1 List of Common Command Functions                                                          | 108 |

| Table 4.5 List of Programmable Command Filed Assignments                                              | 112 |

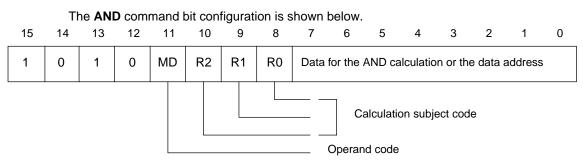

| Table 4.5.1 Relationship between AND Command Bit Settings (BIT 10 to 8)                               |     |

| and the Values Used in the Logical Product Calculation                                                | 114 |

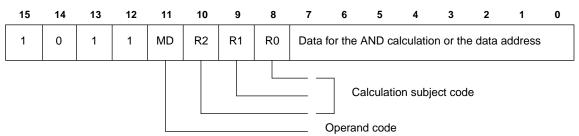

| Table 4.5.2 Relationship between TEST AND Command Bit Settings (BIT 10 to 8)                          |     |

| and the Values Used in the Logical Product Calculation                                                | 115 |

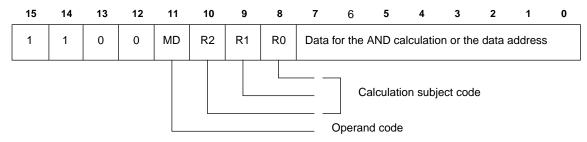

| Table 4.5.3 Relationship between COMPARE Command Bit Settings (BIT 10 to 8) and the Values Used       |     |

| in the Comparison Calculation                                                                         | 116 |

| Table 4.5.5 Relationship between MOVE Command Bit Settings (BIT 10 to 8) and the Values Subject to    |     |

| the MOVE Operation                                                                                    | 118 |

| Table 5.2a Internal Register State After Hardware Reset or Software Reset(BASIC Control Register)     | 124 |

| Table 5.2b Internal Register State After Hardware Reset or Software Reset (Initial Setting Registers) | 125 |

| Table 5.4.1 Explanation of Initiator User Programming Example (Address 00H to 34H)                    |     |

| Table 5.4.2 Explanation of Initiator User Programming Example (Address 40H to E0H)                    |     |

| Table 5.4.3 Explanation of Initiator User Programming Example (Address 00H to 70H)                    |     |

| Table 5.5.1 Explanation of Initiator User Programming Example 1(Address 00H to 21H)                   |     |

| Table 5.5.2a Explanation of Initiator User Programming Example 1 (Address 22H to 4BH)                 |     |

| Table 5.5.2b Explanation of Initiator User Programming Example 2 (Address 00H to 8FH)                 |     |

| Table 5.5.3 Explanation of Target User Programming Example 1 (Address 50H to BFH)                     |     |

| Table 5.7 List of Interrupt Codes                                                                     |     |

| Table 5.7.1 List of Interrupts Related to SCSI RESET                                                  |     |

| Table 5.7.2 List of Interrupts Related to Transfers                                                   |     |

|                                                                                                       |     |

| 1 able 5.7.3 | List of interrupts Related to Phase Transitions                          |     |

|--------------|--------------------------------------------------------------------------|-----|

| Table 5.7.4  | List of Interrupts Related to REPORT                                     |     |

| Table 5.7.5  | List of Interrupts Related to Selection/Reselection                      |     |

| Table 5.7.6  | List of Interrupts Related to Automatic Selection/Reselection Response   |     |

| Table 5.9.1a | SPC Operation When an Offset Error is Detected (Initiator)               | 170 |

| Table 5.9.1b | SPC Operation When an Offset Error is Detected (Target)                  | 170 |

| Table 5.9.2a | SPC Operation When a Short Transfer Period Error is Detected (Initiator) | 172 |

| Table 5.9.2b | SPC Operation When a Short Transfer Period Error is Detected (Target)    | 172 |

| Table 5.9.3a | SPC Operation When a SCSI Parity Error is Detected (Initiator)           | 175 |

| Table 5.9.3b | SPC Operation When a SCSI Parity Error is Detected (Target)              | 175 |

| Table 5.9.4a | SPC Operation When a MPU Parity Error is Detected (Initiator)            | 176 |

| Table 5.9.4b | SPC Operation When a MPU Parity Error is Detected (Target)               |     |

| Table 5.9.5a | SPC Operation When a DMA Parity Error is Detected (Initiator)            |     |

| Table 5.9.5b | SPC Operation When a DMA Parity Error is Detected (Target)               | 178 |

|              |                                                                          |     |

### CHAPIER 1 OVERVIEW

This chapter describes SPC functional features and SPC block configuration.

- 1.1 SCSI PROTOCOL CONTROLLER FEATURES

- 1.2 BLOCK CONFIGURATION4

- 1.3 BLOCK DIAGRAM

# 1.1 SCSI PROTOCOL CONTROLLER FEATURES

The MB86604A/MB86604L are SCSI protocol controllers (below, SPC) based on the ANSI (SCSI-2) standard. By internalizing a sequence control function for the bus phases, the host MPU burden is diminished.

High-speed synchronous transfer is supported. Also, macro-commands which combine multiple commands can be defined in the SPC.

### Features

SPC have the following features.

- (1) SCSI Specifications

- Operation as an initiator or target.

- Transfers two data types.

Synchronous transfer: Maximum 10 MB/second, offset value of 1 to 32 bytes can be set.

Asynchronous transfer: Maximum 5 MB/second.

- Supports programmable commands (internal program memory size: 256 bytes).

- Contains 32-byte FIFO for data phases.

- Transfer block number can be set up to 64 K and transfer block length to 16 MB.

- Contains two 32-byte memory-type data buffers (send, receive) for message, command, and status phases.

- Supports two Automatic information receive modes.

Initiator: Receives information about new target transition phase without issuing command.

Target: Receives information for attention condition produced by initiator without issuing command.

• Supports two Automatic selection/reselection response modes.

Initiator: Operation up to receiving message without issuing command.

Target: Operation up to receiving command without issuing command.

- Specifies transfer parameter by ID (connected device).

- Contains 48 mA single-ended driver/receiver.

Tri-state buffers for the REQ, ACK, DB0 to DB7, DBP, MSG, C/D, I/O, and ATN pins.

- On-chip SCAM registers for SCAM Level-1 protocol (only for MB86604L)

- (2) System Specifications

- a. Supports separate 16-bit MPU bus and DMA bus.

- b. Direct connection with 68 series/80 series MPU.

- c. Supports two types of transfers.

- Program transfers

- DMA transfers (Handshake/burst mode)

Figure 1.1a shows a drawing of the SPC packages. See Appendix A for detailed outer dimensions of SPC packages.

Plastic QFP, 100 pins

MB86604A

### Figure 1.1a Package Drawing

Plastic SQFP, 100 pins MB86604L

Figure 1.1b Package Drawing

# 1.2 BLOCK CONFIGURATION

### The SPC consists of the following nine blocks.

- Internal processor

- Timer

- Receive message, command, status buffer

- Send message, command, status buffer

Command user program memory

- Phase control

- Transfer control

- Data register

Registers

### Block Configuration

The SPC consists of the following nine blocks.

(1) Internal processor

Internal processor for sequence control among the bus phases. The max. operating clock frequency is 20 MHz.

(2) Timer

Manages SCSI time conditions.

Performs other time management as follows.

- Time until REQ/ACK signals are asserted for data in asynchronous transfers.

- Time until selection/reselection are retried.

- Selection/reselection timeout time.

- REQ/ACK timeout time during transfers.

Asynchronous (target):After REQ signal is asserted, time until initiator asserts ACK signal.

Asynchronous (initiator): After ACK signal is asserted, time until target negates REQ signal.

Synchronous (target only):After REQ signal is sent, time until ACK signal which defines offset at 0 is received from initiator.

• SPC Timeout Timer: Indicates that SPC has been in busy for a time longer than time specified.

(3) Phase control

Controls SCSI arbitration, selection/reselection, data in/out, command, status, and message in/ out phases.

(4) Transfer control

Controls SCSI information (data, command, status, message) transfer phases.

There are two types of transfer phase controls.

Asynchronous: Interlock control of REQ signal and ACK signal.

Synchronous: Control by offset value up to 32-byte maximum in data in/out phase.

There are also two data transfer modes.

Program transfer: Data register transfer via MPU interface.

DMA transfer: Transfer using DREQ and DACK signals via DMA interface.

Transfer parameters in synchronous transfers (minimum repeat cycle for sending REQ or ACK from SPC during transfer mode and synchronous transfer, maximum offset value) can be saved by ID and automatically set at the begiinning of data phase.

The number of transfer bytes is defined by the block length and number of blocks.

(5) Registers

The main registers are listed below.

Command register: Commands are defined by 8-bit code. For user program operation, specify the head address of the program allocated to user program memory.

Nexus status register: Show chip operation state, nexus destination ID, and data register state.

SCSI control signal status register: Shows SCSI control signal state.

Interruptstatus register: Describes interrupt state with 8-bit code.

Command step register: Describes command execution state with 8-bit code. Cause of errors can be analyzed by reference to the interrupt status register and this command step register.

Group 6/7 command length define register: Sets the command length for group 6/7 which are undefiend by the SCSI standard. Once this register is set, the command length for group 6/7 can be determined.

(6) Message, command, status receive buffer (Receive MCS buffer)

Receive information buffer. Stores message, command, and status information received by SCSI (32 bytes).

(7) Message, command, status send buffer (Send MCS buffer)

Send information bufffer. Stores message, command, and status information sent by SCSI (32 bytes).

(8) User prgram memory

Program memory for setting programmable commands (256 bytes).

(9) Data register

FIFO data register for storing data phase data (32 bytes).

# 1.3 BLOCK DIAGRAM

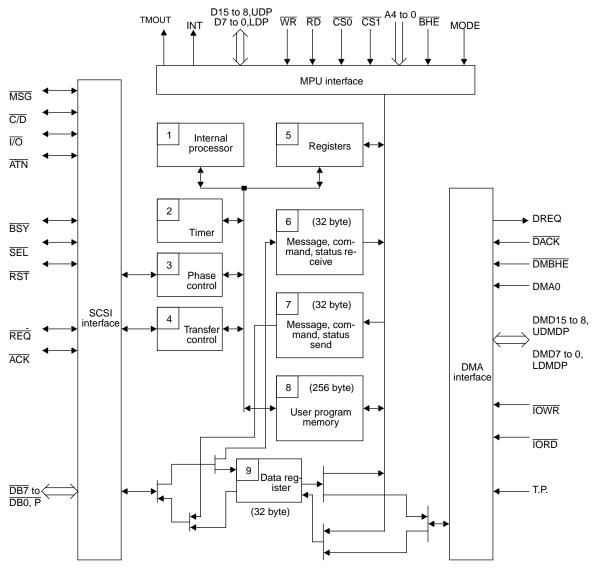

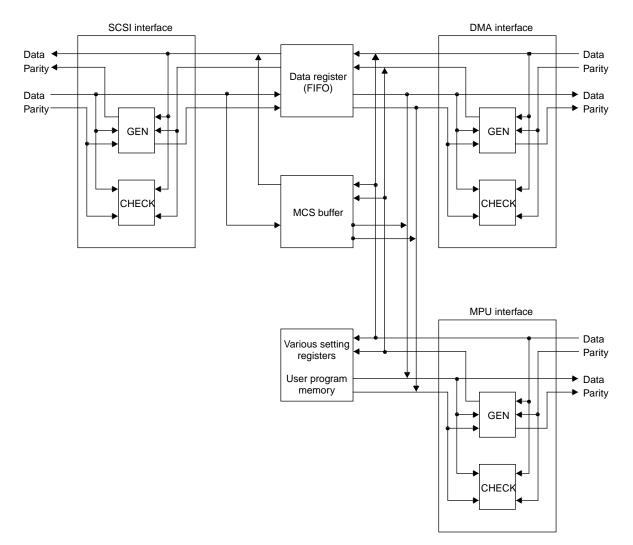

### Block diagram for the MB86604A/MB86604L is shown in Figures 1.3.

### Block Diagram

Figure 1.3 Block Diagram

### CHAPTER 2 INPUT/OUTPUT PINS

This chapter describes the pin assignments for each SPC package and the functions of each pin.

- 2.1 MB86604A PIN ASSIGNMENT

- 2.2 MB86604L PIN ASSIGNMENT

- 2.3 EXPLANATION OF PIN FUNCTIONS (SCSI INTERFACE)

- 2.4 EXPLANATION OF PIN FUNCTIONS (MPU INTERFACE)

- 2.5 EXPLANATION OF PIN FUNCTIONS (DMA INTERFACE)

- 2.6 EXPLANATION OF PIN FUNCTIONS (CONTROL SIGNAL)

## 2.1 MB86604A PIN ASSIGNMENT

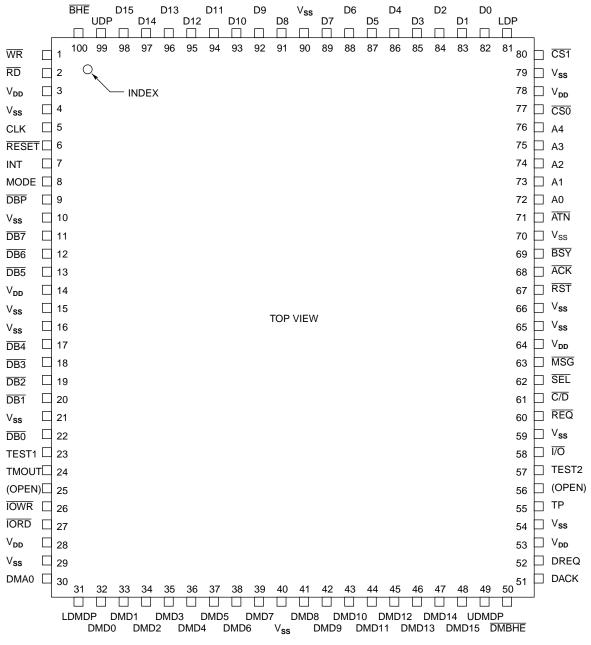

Figure 2.1 shows the MB86604A pin assignment.

Also, Table 2.1 provides a list of MB86604A pins.

### MB86604A Pin Assignment

Figure 2.1 MB86604A Pin Assignment Diagram

| No. | I/O             | Pin<br>name | No. | I/O             | Pin<br>name | No. | I/O             | Pin<br>name | No.     | I/O             | Pin<br>name |

|-----|-----------------|-------------|-----|-----------------|-------------|-----|-----------------|-------------|---------|-----------------|-------------|

| 1   | I               | WR          | 26  | I               | IOWR        | 51  | I               | DACK        | 76      | I               | A4          |

| 2   | I               | RD          | 27  | I               | IORD        | 52  | 0               | DREQ        | 77      | I               | CS0         |

| 3   | Power<br>supply | Vdd         | 28  | Power<br>supply | Vdd         | 53  | Power<br>supply | Vdd         | 78      | Power<br>supply | Vdd         |

| 4   | Ground          | Vss         | 29  | Ground          | Vss         | 54  | Ground          | Vss         | 79      | Ground          | Vss         |

| 5   | I               | CLK         | 30  | I               | DMA0        | 55  | I               | TP          | 80      | I               | CS1         |

| 6   | I               | RESET       | 31  | I/O             | LDMDP       | 56  |                 | (OPEN)      | 81      | I/O             | LDP         |

| 7   | 0               | INT         | 32  | I/O             | DMD0        | 57  |                 | TEST2       | 82      | I/O             | D0          |

| 8   | I               | MODE        | 33  | I/O             | DMD1        | 58  | I/O             | I/O         | 83      | I/O             | D1          |

| 9   | I/O             | DBP         | 34  | I/O             | DMD2        | 59  | Ground          | Vss         | 84      | I/O             | D2          |

| 10  | Ground          | Vss         | 35  | I/O             | DMD3        | 60  | I/O             | REQ         | 85      | I/O             | D3          |

| 11  | I/O             | DB7         | 36  | I/O             | DMD4        | 61  | I/O             | C/D         | 86      | I/O             | D4          |

| 12  | I/O             | DB6         | 37  | I/O             | DMD5        | 62  | I/O             | SEL         | 87      | I/O             | D5          |

| 13  | I/O             | DB5         | 38  | I/O             | DMD6        | 63  | I/O             | MSG         | 88      | I/O             | D6          |

| 14  | Power<br>supply | Vdd         | 39  | I/O             | DMD7        | 64  | Power<br>supply | Vdd         | 89      | I/O             | D7          |

| 15  | Ground          | Vss         | 40  | Groud           | Vss         | 65  | Ground          | Vss         | 90      | Groud           | Vss         |

| 16  | Ground          | Vss         | 41  | I/O             | DMD8        | 66  | Ground          | Vss         | 91      | I/O             | D8          |

| 17  | I/O             | DB4         | 42  | I/O             | DMD9        | 67  | I/O             | RST         | 92      | I/O             | D9          |

| 18  | I/O             | DB3         | 43  | I/O             | DMD10       | 68  | I/O             | ACK         | 93      | I/O             | D10         |

| 19  | I/O             | DB2         | 44  | I/O             | DMD11       | 69  | I/O             | BSY         | 94      | I/O             | D11         |

| 20  | I/O             | DB1         | 45  | I/O             | DMD12       | 70  | Ground          | Vss         | 95      | I/O             | D12         |

| 21  | Power<br>supply | Vss         | 46  | I/O             | DMD13       | 71  | I/O             | ĀTN         | 96      | I/O             | D13         |

| 22  | I/O             | DB0         | 47  | I/O             | DMD14       | 72  | I               | A0          | 97      | I/O             | D14         |

| 23  | I               | TEST1       | 48  | I/O             | DMD15       | 73  | I               | A1          | 98      | I/O             | D15         |

| 24  | 0               | TMOUT       | 49  | I/O             | UDMDP       | 74  | I               | A2          | 99      | I/O             | UDP         |

| 25  |                 | (OPEN)      | 50  | I               | DMBHE       | 75  | I               | A3          | 10<br>0 | I               | BHE         |

Table 2.1 List of MB86604A Pins

# 2.2 MB86604L PIN ASSIGNMENT

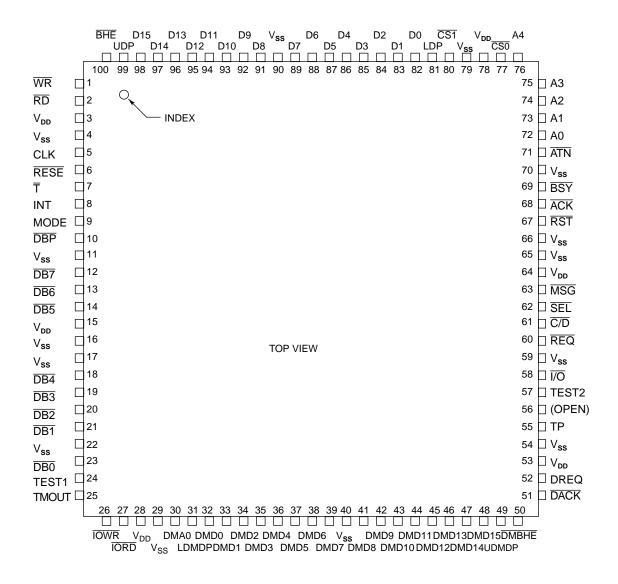

Figure 2.2 shows the MB86604L pin assignment.

Also, Table 2.2 provides a list of MB86604L pins.

### MB86604L Pin Assignment

Figure 2.2 MB86604L Pin Assignment Diagram

| No. | I/O             | Pin<br>name | No. | I/O             | Pin<br>name | No. | I/O             | Pin<br>name | No.     | I/O             | Pin<br>name |

|-----|-----------------|-------------|-----|-----------------|-------------|-----|-----------------|-------------|---------|-----------------|-------------|

| 1   | I               | WR          | 26  | I               | IOWR        | 51  | I               | DACK        | 76      | I               | A4          |

| 2   | I               | RD          | 27  | I               | IORD        | 52  | 0               | DREQ        | 77      | I               | CS0         |

| 3   | Power<br>supply | Vdd         | 28  | Power<br>supply | Vdd         | 53  | Power<br>supply | Vdd         | 78      | Power<br>supply | Vdd         |

| 4   | Power<br>supply | Vss         | 29  | Power<br>supply | Vss         | 54  | Power<br>supply | Vss         | 79      | Power<br>supply | Vss         |

| 5   | Ι               | CLK         | 30  | Ι               | DMA0        | 55  | Ι               | TP          | 80      | Ι               | CS1         |

| 6   | I               | RESET       | 31  | I/O             | LDMDP       | 56  |                 | (OPEN)      | 81      | I/O             | LDP         |

| 7   | 0               | INT         | 32  | I/O             | DMD0        | 57  |                 | TEST2       | 82      | I/O             | D0          |

| 8   | Ι               | MODE        | 33  | I/O             | DMD1        | 58  | I/O             | Ī/O         | 83      | I/O             | D1          |

| 9   | I/O             | DBP         | 34  | I/O             | DMD2        | 59  | Power<br>supply | Vss         | 84      | I/O             | D2          |

| 10  | Power<br>supply | Vss         | 35  | I/O             | DMD3        | 60  | I/O             | REQ         | 85      | I/O             | D3          |

| 11  | I/O             | DB7         | 36  | I/O             | DMD4        | 61  | I/O             | C/D         | 86      | I/O             | D4          |

| 12  | I/O             | DB6         | 37  | I/O             | DMD5        | 62  | I/O             | SEL         | 87      | I/O             | D5          |

| 13  | I/O             | DB5         | 38  | I/O             | DMD6        | 63  | I/O             | MSG         | 88      | I/O             | D6          |

| 14  | Power<br>supply | Vdd         | 39  | I/O             | DMD7        | 64  | Power<br>supply | Vdd         | 89      | I/O             | D7          |

| 15  | Power<br>supply | Vss         | 40  | Power<br>supply | Vss         | 65  | Power<br>supply | Vss         | 90      | Power<br>supply | Vss         |

| 16  | Power<br>supply | Vss         | 41  | I/O             | DMD8        | 66  | Power<br>supply | Vss         | 91      | I/O             | D8          |

| 17  | I/O             | DB4         | 42  | I/O             | DMD9        | 67  | I/O             | RST         | 92      | I/O             | D9          |

| 18  | I/O             | DB3         | 43  | I/O             | DMD10       | 68  | I/O             | ACK         | 93      | I/O             | D10         |

| 19  | I/O             | DB2         | 44  | I/O             | DMD11       | 69  | I/O             | BSY         | 94      | I/O             | D11         |

| 20  | I/O             | DB1         | 45  | I/O             | DMD12       | 70  | Power<br>supply | Vss         | 95      | I/O             | D12         |

| 21  | Power<br>supply | Vss         | 46  | I/O             | DMD13       | 71  | I/O             | ATN         | 96      | I/O             | D13         |

| 22  | I/O             | DB0         | 47  | I/O             | DMD14       | 72  | I               | A0          | 97      | I/O             | D14         |

| 23  | I               | TEST1       | 48  | I/O             | DMD15       | 73  | I               | A1          | 98      | I/O             | D15         |

| 24  | 0               | TMOUT       | 49  | I/O             | UDMDP       | 74  | I               | A2          | 99      | I/O             | UDP         |

| 25  | _               | (OPEN)      | 50  | Ι               | DMBHE       | 75  | I               | A3          | 10<br>0 | Ι               | BHE         |

Table 2.2 List of MB86604L Pins

# 2.3 EXPLANATION OF PIN FUNCTIONS (SCSI INTERFACE)

### Table 2.3 lists the SCSI interface pins and their functions.

### SCSI Interface

Table 2.3 SCSI Interface Pins

| Pin name                                          | I/O | Function                                                                                                                                      |

|---------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

| REQ, ACK, ATN,<br>MSG, C/D, I/O,<br>BSY, SEL, RST | I/O | SCSI control signal input/output<br>Can be directly connected to single-ended SCSI connector.<br>REQ and ACK Pins are the tri-state I/O port. |

| $\overline{DB7}, \overline{DB0}, \overline{DBP}$  | I/O | SCSI data bus input/output<br>Can be directly connected to single-ended SCSI connector.                                                       |

Tri-state SCSI data bus pins:

You can select either tri-state or open-drain port for the  $\overline{DB7}$  to  $\overline{DB0}$ , and  $\overline{DBP}$  pins by a TEST1 pin input level.

Tri-state SCSI control pins:

You can select either tri-state or open-drain port for the  $\overline{MSG}$ ,  $\overline{C/D}$ ,  $\overline{I/O}$ , and  $\overline{ATN}$  pins by a TEST2 pin input level.

# 2.4 EXPLANATION OF PIN FUNCTIONS (MPU INTERFACE)

Table 2.4 lists the MPU interface pins and their functions. Depending on the mode setting, the MPU interface can be connected to the input/ output signals of 80 series or 68 series MPU.

### MPU Interface

| Pin name             | I/O | Function                                                                                                                                                                                            |

|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS0                  | I   | Input signal for MPU to select SPC as I/O device.                                                                                                                                                   |

| CS1                  | I   | Input selection signal (external circuit selection signal) when MPU inputs/outputs DMA bus data via the SPC.                                                                                        |

| D15 to D8, UDP<br>*1 | I/O | Data bus upper byte and parity<br><u>CS0</u> input valid: SPC internal register input/output port<br><u>CS1</u> input valid: DMA bus data input/output port                                         |

| D7 to D0, LDP        | I/O | Data bus lower byte and parity<br><u>CS0</u> input valid: SPC internal register input/output port<br><u>CS1</u> input valid: DMA bus data input/output port                                         |

| A4 to A0             | I   | Input address to select internal register.                                                                                                                                                          |

| RD (R/W)             | I   | <ul> <li>80 series mode: Input IORD signal or RD signal for MPU to read from SPC</li> <li>68 series mode: Input control signal R/W for MPU to read from/write to SPC</li> </ul>                     |

| WR (LDS)             | I   | <ul> <li>80 series mode: Input IOWR signal or WR signal for MPU to read from SPC</li> <li>68 series mode: Input LDS signal output from MPU when data bus lower byte is valid</li> </ul>             |

| BHE (UDS) *2         | I   | <ul> <li>80 series mode: Input BHE signal output from MPU when data bus upper byte is valid</li> <li>68 series mode: Input UDS signal output from MPU when data bus upper byte ils valid</li> </ul> |

| INT                  | 0   | Interrupt request signal output.<br>80 series mode: Hactive<br>68 series mode: L active<br>For this INT signal output, please see the INT signal hold mode in<br>section 3.3.13                     |

| MODE                 | I   | Input signal which specifies MPU (80 series)<br>80 series mode: Input 1<br>68 series mode: Input 0                                                                                                  |

### Table 2.4 MPU Interface Pins

\*1: when 8-bit bus width, pull up the UDP and D15 to D8 pins with approx. 10 k $\Omega$ .

\*2: when 8-bit bus width, fix the BHE pin to "1".

# 2.5 EXPLANATION OF PIN FUNCTIONS (DMA INTERFACE)

### Table 2.5 lists DMA interface pins and their functions.

### DMA Interface

### Table 2.5 DMA Interface Pins

| Pin name                      | I/O | Function                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DREQ                          | 0   | Output DMA transfer request signal for DMAC. Request DMA data transfers between SPC and memory.                                                                                                                                                                 |  |  |  |  |  |

| DACK                          | Ι   | Input DMA transfer permissible signal from DMAC. When DMA transfer permissible signal is active, DMA transfer (read/write) is executed.                                                                                                                         |  |  |  |  |  |

| D15 to D8, UDP<br>*1          | I/O | DMA data bus upper byte and parity<br>CS1 input valid: MPU data bus is connected.                                                                                                                                                                               |  |  |  |  |  |

| DMD7 to D0,<br>LDMDP          | I/O | DMA data bus lower byte and parity<br>CS1 input valid: MPU data bus is connected.                                                                                                                                                                               |  |  |  |  |  |

| IORD (DMR/W)                  | I   | <ul> <li>80 series mode: Input IORD dignal or RD signal to output data from SPC to DMA bus</li> <li>68 series mode: Input control segnal R/W for DMAC to input data to or output data from SPC</li> </ul>                                                       |  |  |  |  |  |

| IOWR (DMLDS)                  | I   | <ul> <li>80 series mode: Input IOWR signal or WR signal to input data on the DMA bus to SPC</li> <li>68 series mode: Input control signal R/W for MPU to read from/write to SPC</li> </ul>                                                                      |  |  |  |  |  |

| DMBHE<br>(DMUDS)              | I   | <ul> <li>80 series mode: Input BHE signal output from DMAC when DMA data bus upper byte is valid</li> <li>68 series mode: Input UDS signal output from DMAC when DMA data bus upper byte ils valid</li> <li>Connect to V<sub>DD</sub> in 8-bit mode.</li> </ul> |  |  |  |  |  |

| DMA0                          | I   | Input address data A0 signal output from DMAC in 80 series mode.<br>68 series mode: Connect power source ( $V_{DD}$ )<br>Connect to $V_{SS}$ or $V_{DD}$ in 8-bit mode.                                                                                         |  |  |  |  |  |

| TP (Transfer<br>Permission)*2 | I   | Input DMA transfer permissible signal.<br>When TP signal is active, SPC performs DMA transfer.<br>If TP signal becomes inactive during a DMA transfer, the transfer is<br>suspended at the block boundary.                                                      |  |  |  |  |  |

\*1: When DMA bus is used in 8-bit, pull up those pins with approx. 10 k $\Omega$ .

\*2: See 6.1 for an explanation of TP signal control

Note: When DMA bus is used in 8-bit mode, use DMD7-0, P or IOWR (DMLDS). DMUDS side cannot be used even in 68 series mode.

# 2.6 EXPLANATION OF PIN FUNCTIONS (CONTROL SIGNAL)

### Table 2.6 lists control signal pins and their functions.

### ■ Control Signals

| Table 2.6 | Control | Signal | Pins |

|-----------|---------|--------|------|

|-----------|---------|--------|------|

| Pin name        | I/O | Function                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RESET           | I   | System reset input. Set at least 4 CLK active.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| CLK             | I   | Clock input. (20, 30, 40 MHz)                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| TEST1           | I   | <ol> <li>Connect to Vss if DBP, DB7 to DB0 are used as open-drain I/O port.</li> <li>Connect to V<sub>DD</sub> if DBP, DB7 to DB0 are used as tri-state I/O port.</li> </ol>                                                                                                                                                                  |  |  |  |  |

| TEST2           | I   | 1) Connect to Vss if $\overline{\text{MSG}}$ , $\overline{\text{C/D}}$ , $\overline{\text{I/O}}$ , and $\overline{\text{ATN}}$ are used as open-drain I/O port.<br>2) Connect to V <sub>DD</sub> if $\overline{\text{MSG}}$ , $\overline{\text{C/D}}$ , $\overline{\text{I/O}}$ , and $\overline{\text{ATN}}$ are used as tri-state I/O port. |  |  |  |  |

| V <sub>DD</sub> | _   | Power supply                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Vss             | _   | Ground                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| тмоит           | 0   | SPC timeout output. When SPC Busy flag=1 for longer time than one specified, this pin outputs "H".                                                                                                                                                                                                                                            |  |  |  |  |

| (OPEN)          | _   | Leave as open pin with no connection.                                                                                                                                                                                                                                                                                                         |  |  |  |  |

### CHAPTER 3 FUNCTIONS

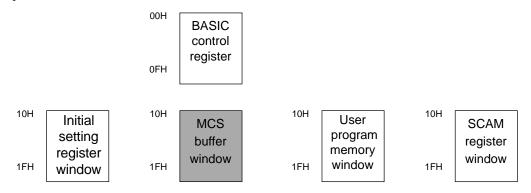

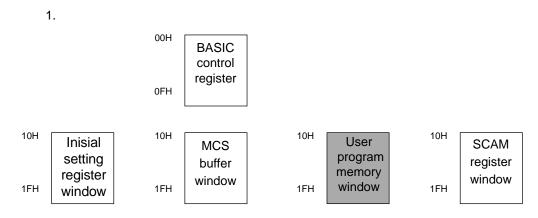

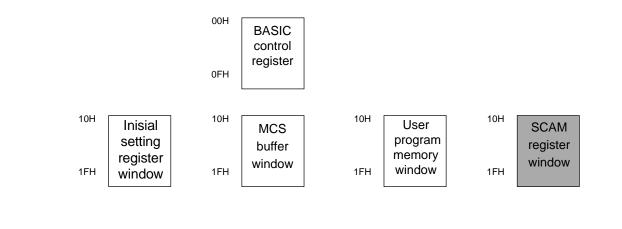

This chapter describes the functions of SPC internal registers, memory, and buffers.

- 3.1 INTERNAL REGISTERS

- 3.2 BASIC CONTROL REGISTER

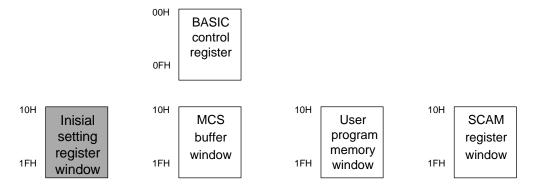

- 3.3 INITIAL SETTING REGISTER WINDOW

- 3.4 MCS BUFFER WINDOW

- 3.5 USER PROGRAM MEMORY WINDOW

- 3.6 SCAM REGISTER WINDOW

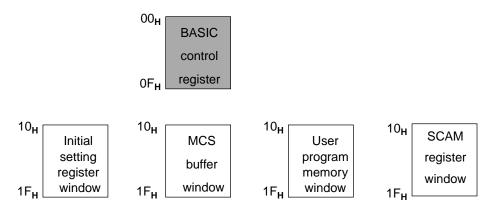

# 3.1 INTERNAL REGISTERS

Indicates the relationship between signal input to access SPC internal registers and accessed registers.

Depending on the type of information, the SPC register where the MPU reads/writes differs (data register or MCS buffer).

### Internal Register Access

Tables 3.1a and 3.1b show the access state to internal registers for 80 series and 68 series modes.

| CS0 | BHE <sup>*1</sup> | A0 | D15 to D8 <sup>*2</sup> | D7 to D0              |

|-----|-------------------|----|-------------------------|-----------------------|

| 1   | _                 | —  | HI-Z                    | HI-Z                  |

| 0   | 0                 | 0  | Odd address register    | Even address register |

| 0   | 0                 | 1  | Odd address register    | HI-Z                  |

| 0   | 1                 | 0  | HI-Z                    | Even address register |

| 0   | 1                 | 1  | HI-Z                    | Odd address register  |

Table 3.1a Internal Register Access (80 Series Mode)

\*1 Set BHE pin to 1 for 8-bit bus operation.

\*2 Connect about 10-k $\Omega$  pull-up resistor to the UDP and D15 to D8 when using 8-bit bus..

| Table 3.1b         Internal Register Access (68 Series Mode) |                   |     |      |                         |                       |

|--------------------------------------------------------------|-------------------|-----|------|-------------------------|-----------------------|

| CS0                                                          | UDS <sup>*2</sup> | LDS | A0*1 | D15 to D8 <sup>*3</sup> | D7 to D0              |

| 1                                                            | —                 | _   | —    | HI-Z                    | HI-Z                  |

| 0                                                            | 0                 | 0   | 1    | Even address register   | Odd address register  |

| 0                                                            | 0                 | 1   | 1    | Even address register   | HI-Z                  |

| 0                                                            | 1                 | 0   | 0    | HI-Z                    | Even address register |

| 0                                                            | 1                 | 0   | 1    | HI-Z                    | Odd address register  |

| 0                                                            | 1                 | 1   | _    | HI-Z                    | HI-Z                  |

\*1 Set A0 pin to 1 for 16-bit bus operation.

\*2 Set  $\overline{\text{UDS}}$  pin to 1 for 8-bit bus operation.

\*3 Connect about 10-k $\Omega$  pull-up resistor to the UDP and D15 to D8 when using 8-bit bus.

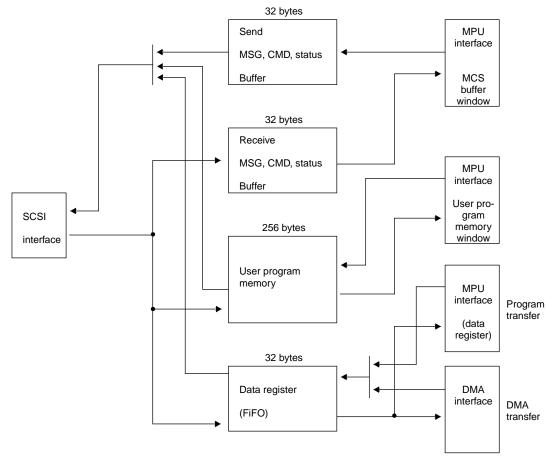

### ■ Data Flow During Transfers

Depending on the type of information, the SPC register where the MPU reads/writes differs (data register or MCS buffer). There are also program transfers and DMA transfers. For DMA transfers, data phases are supported, but messages, commands, and status phases are not.

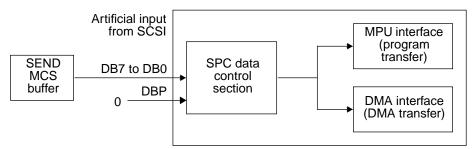

Table 3.1c shows the relationship between information types and registers (program transfer/data transfer). Figure 3.1 outlines the internal flow of information.

Table 3.1c Relationship between Information Types and Registers

| Transfer<br>Information | Program transfer<br>(via MPU bus)    | DMA transfer<br>(via DMA bus) |  |

|-------------------------|--------------------------------------|-------------------------------|--|

| Message phase           |                                      |                               |  |

| Command phase           | MCS buffer<br>(32 byte input/output) | Not possible                  |  |

| Status phase            |                                      |                               |  |

| Data phase              | Data register                        | Data register                 |  |

Figure 3.1 Internal Flow of Information

# 3.2 BASIC CONTROL REGISTER

### This register controls the SPC and confirms SPC states.

### BASIC Control Register

Table 3.2 lists the BASIC control register.

| Na |    | Α  | ddres | S  |    | Write                                     | Read                                |

|----|----|----|-------|----|----|-------------------------------------------|-------------------------------------|

| No | A4 | A3 | A2    | A1 | A0 | write                                     |                                     |

| 00 | 0  | 0  | 0     | 0  | 0  | SCSI output data register (First)         | SCSI input data register (First)    |

| 01 | 0  | 0  | 0     | 0  | 1  | SCSI output data register (Second)        | SCSI input data register (Second)   |

| 02 | 0  | 0  | 0     | 1  | 0  | Direct control register                   | SPC status register                 |

| 03 | 0  | 0  | 0     | 1  | 1  | (RESERVED)                                | Nexus status register               |

| 04 | 0  | 0  | 1     | 0  | 0  | SEL/RESEL-ID register                     | Interrupt status register           |

| 05 | 0  | 0  | 1     | 0  | 1  | Command register                          | Command step register               |

| 06 | 0  | 0  | 1     | 1  | 0  | Data block register (MSB)                 | $\leftarrow$                        |

| 07 | 0  | 0  | 1     | 1  | 1  | Data block register (LSB)                 | $\leftarrow$                        |

| 08 | 0  | 1  | 0     | 0  | 0  | Data byte register (MSB)                  | $\leftarrow$                        |

| 09 | 0  | 1  | 0     | 0  | 1  | Data byte register                        | $\leftarrow$                        |

| 0A | 0  | 1  | 0     | 1  | 0  | Data byte register (LSB)/MC byte register | ←                                   |

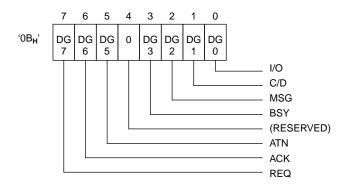

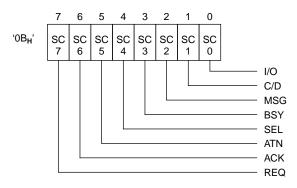

| 0B | 0  | 1  | 0     | 1  | 1  | Diagnostic control signal<br>register     | SCSI control signal status register |

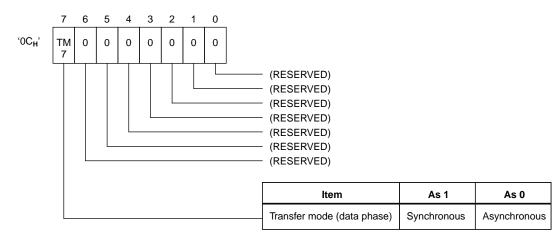

| 0C | 0  | 1  | 1     | 0  | 0  | Transfer mode register                    | $\leftarrow$                        |

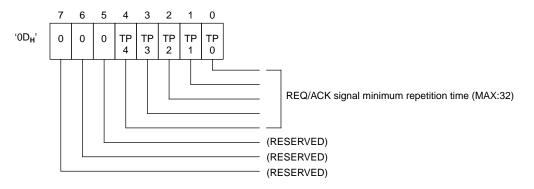

| 0D | 0  | 1  | 1     | 0  | 1  | Transfer period register                  | $\leftarrow$                        |

| 0E | 0  | 1  | 1     | 1  | 0  | Transfer offset register                  | $\leftarrow$                        |

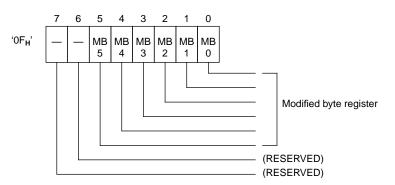

| 0F | 0  | 1  | 1     | 1  | 1  | Window address register                   | Modified byte register              |

### Table 3.2 BASIC Control Register List

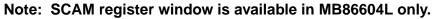

# 3.2.1 Output Data Register (Write)

In the data phase program transfer mode, the output data register outputs data to the SCSI bus.

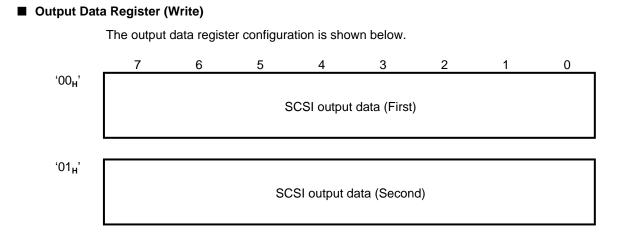

# 3.2.2 Input Data Register (Read)

In the data phase program transfer mode, the input data register inputs data to the SCSI bus.

### ■ Input Data Register (Read)

The input data register configuration is shown below.

# MEMO

# 3.2.3 Direct Control Register (WRITE)

The direct control register (WRITE) provides direct control regardless of whether a command is issued to the SPC.

### Direct Control Register (WRITE)

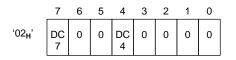

The direct control register bit configuration is shown below.

Next, the functionality of each bit is described.

BIT 7: ATN signal control

Control bit for direct control of ATN signal assert. When the SPC operates as an initiator, the ATN signal is asserted by writing 1 in BIT 7. Effective for interrupting a data phase (produces attention condition).

After writing 1 in BIT 7 and asserting the ATN signal, be sure to write 0 and return to the initial state before issuing the next command. The ATN signal is not negated by writing 0. In order to negate the ATN signal, issue a RESET ATN signal.

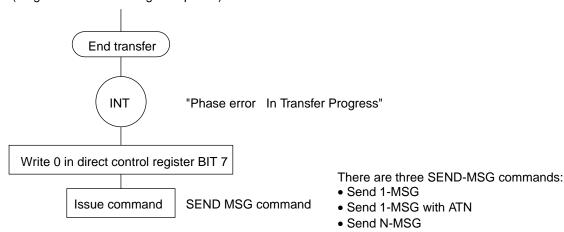

In Figure 3.2.3, the relationship between transfers and BIT 7 is diagrammed in a flowchart.

Start transfer

Write 1 in direct control register BIT 7

(Assert ATN signal) (Target: move to message out phase)

Figure 3.2.3 Transfer Flowchart (Direct Control Register: BIT 7)

### BIT 4: TMOUT signal clear

Control bit to clear the TMOUT pin signal. The TMOUT pin is cleared by writing "1" to this bit while the SPC Busy bit (Bit 6) in the SPC Status Register (02h) = "0". When SPC Busy = "1", the TMOUT pin is not cleared.

3.2 BASIC CONTROL REGISTER

# 3.2.4 SPC Status Register (READ)

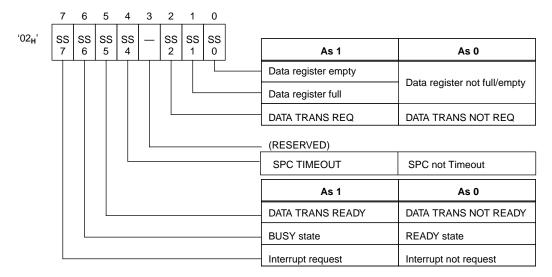

### The SPC status register shows the operating state of the SPC.

### SPC Status Register (READ)

The SPC status register (READ) bit configuration is shown below.

Next, the functionality of each bit is described.

BIT 7: Interrupt request

When there is an interrupt request from the SPC to the host MPU, 1 is indicated. While linked to the INT signal (interrupt request signal) to the host MPU, this bit indicates 1 whenever there is an interrupt request regardless the interrupt is enabled or disabled (interrupt enable register).

BIT 6: BUSY state

Shows that the SPC is operating.

When the SPC receives a command or automatically begins operating (at Automatic selection/reselection response mode), 1 is indicated.

When the operation is successfully completed or ends unsuccessfully because of an error, 0 is displayed.

If a command is issued when BIT 6 is 1, except for SOFTWARE RESET, the command is ignored and a COMMAND REJECTED interrupt reported.

BIT 5: DATA TRANS READY state

Shows that a transfer is possible (during transfer). When the SPC receives a transfer-related command and the SPC internal set-up finishes, 1 is displayed in this bit.

BIT 4: SPC Timeout State

Shows that SPC is operating over the time specified in the SPC timeout Setting register. When the SPC's operation terminated within the time specified, this bit value is "0". This bit can be cleared by writing "1" to the TMOUT pin clear bit (Bit 4) of Direct Control Register while SPC busy=0.

### BIT 2: DATA TRANS REQ

Shows state of data phase transfer request.

During SCSI-INPUT, when two or more bytes can be read from the data register (the data register contains two or more bytes) or when the data register contains the last byte, 1 is indicated.

During SCSI-OUTPUT, when two or more bytes can be written in the data register (the data register contains 30 or less bytes) or the last byte can be written in the data register, 1 is indicated. Refer to this bit when conducting a program transfer. Also, when DMA transfer mode, "1" will be indicated in this bit while the DREQ signal is asserted.

BIT 1: Data Register FULL

When the data register is FULL, 1 is indicated.

BIT 0: Data Register EMPTY

When the data register is EMPTY, 1 is indicated.

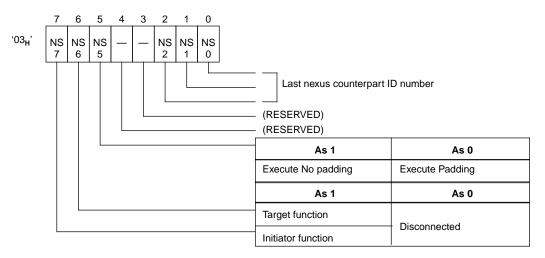

# 3.2.5 Nexus Status Register (READ)

# The nexus status register (READ) shows the SPC internal state and the nexus counterpart ID.

### Nexus Status Register (READ)

The nexus status register (READ) bit configuration is shown below.

Next, the functionality of each bit is described.

BIT 7: Initiator function

When the SPC starts as the initiator, 1 is indicated. At the following points, 1 is indicated.

- Reselection by the target (SEL and I/O signals are true when the self ID bit is true).

- After acquiring bus usage rights as the initiator and asserting the SEL signal, when the ID bit is sent to the data bus during the selection phase or when the ATN signal is asserted simultaneously.

When the SPC is disconnected by the target and I-T nexus is released, 0 is indicated.

BIT 6: Target function

When the SPC starts as the target, 1 is indicated. At the following points, 1 is indicated.

- Selection by the initiator (SEL signal is true and I/O signal is false when the self ID bit is true).

- After acquiring bus usage rights as the target and asserting the SEL signal, when the ID bit is sent to the data bus during the reselection phase or when the I/O signal is asserted simultaneously.

When the SPC is disconnected and I-T nexus is released, 0 is indicated.

#### BIT 5: Padding operation

1 is indicated when the SPC receives a data transfer command with padding and then it did not perform the padding transfer after transferring the specified byte data. When the padding transfer is performed, 0 is indicated. This bit does not change if a data transfer command without padding is performed.

Also, please read out the value for this bit until the disconnect is occurred, since this bit is cleared when the device is newly nexused.

Furthermore, this bit can not be referred by the user program.

#### BIT 2-0: Final nexus counterpart ID

Stores nexus counterpart ID. BIT 2-0 are set at the following points.

- During the initiator function in the selection phase, when a BSY signal is received from the counterpart target.

- During the target function in the reselection phase, when a BSY signal is received from the counterpart initiator.

- During the intiator function, when a BSY signal is asserted in response to a target reselect request.

- During the target function, when a BSY signal is asserted in response to an initiator select request.

Data is stored in those bits even when the SPC is disconnected. This data is rewritten when a new nexus is established.

When the SPC is the target in the Automatic selection response mode, it operates automatically up to the command phase. At which time, the host MPU can reference this register to find out the initiator ID number. Also, when the SPC is the initiator in the Automatic reselection response mode, it operates automatically up to the message in phase. At which time, the host MPU can reference this register to find out the target ID number. (See 3.3.4 for more about the Automatic selection/reselection response mode).

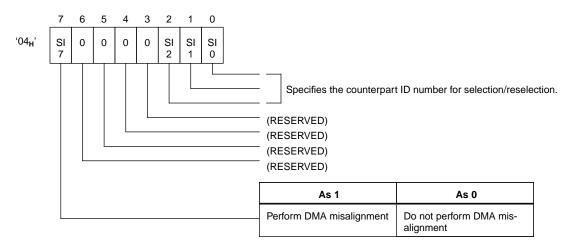

### 3.2.6 SEL/RESEL ID Register (WRITE)

## The SEL/RESEL ID register (WRITE) specifies DMA transfer misalignment processing and the selected counterpart bus device ID.

#### SEL/RESEL ID Register (WRITE)

The SEL/RESEL ID register (WRITE) bit configuration is shown below.

Next, the functionality of each bit is described.

BIT 7: DMA transfer misalignment

Please set when the DMA transfer width is 16 bits, the first MPU/DMA side read/write is done by byte access, and writing to the system memory or reading from the system memory is performed to/from an odd address.

- 1:Writing to the system memory or reading from the system memory can be performed to/from an odd address.

- 0:Writing to the system memory or reading from the system memory can be performed to/from an even address. See 6.2 for more details.

- BIT 2-0: Setting SEL-RESEL ID

Specify the counterpart bus device ID number for selection/reselection with a binary digit.

#### Setting Transfer Mode/Transfer Parameters

When setting the transfer mode/transfer parameters (PERIOD, OFFSET), after specifying the counterpart ID number in the SEL/RESEL ID register, set the following.

- Transfer mode register (address 0C<sub>H</sub>)

- Transfer period register (address 0D<sub>H</sub>)

- Transfer offset register (address 0E<sub>H</sub>)

For a target in the selection phase to which only the target ID bit is sent (single initiator), set the transfer parameters with the initiator ID number as 0.

### 3.2.7 Interrupt Status Register (READ)

## The interrupt status register (READ) displays the reason for the interrupt using an 8-bit code.

#### Interrupt Status Register (READ)

The interrupt status register (READ) bit configuration is shown below.

|                    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------------------|----|----|----|----|----|----|----|----|

| '04 <sub>H</sub> ' | IS |

|                    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

The interrupt status register, an FIFO-type register (8 bytes), stores interrupt codes which occur until the command is completed and can store two or more interrupt codes. Read this register when BIT 7 (interrupt request exists) of the SPC status register (address  $02_H$ ) is 1.

After each host MPU read operation, this register indicates the next interrupt code.

The interrupt status register value occurs at the step indicated by the command step register (address  $05_{\rm H}$ ). Therefore, read this register and the command step register at the same time.

With an 8-bit MPU, read the command step register after reading the interrupt status register (unless this is done, the next interrupt code will not be shown).

See 5.7 for more on interrupt codes.

Notes on Reading Interrupt Status Register

- If Bit 7 of automatic operation mode setting register (address 1Ch) is set to "1", all the interrupt code should be read out from this register. Otherwise, any commands issued later will be ignored.

- 2) Do not access this register until SPC Busy bit (Bit 6 of SPC Status register) becomes "0" after the command was issued. Also, please read out the interrupt codes before issuing new command.

3.2 BASIC CONTROL REGISTER

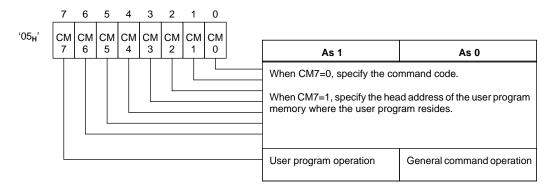

### 3.2.8 Command Register (WRITE)

### The command register (WRITE) issues commands for the SPC.

#### Command Register (WRITE)

The command register (WRITE) bit configuration is shown below.

Next, the functionality of each bit is described.

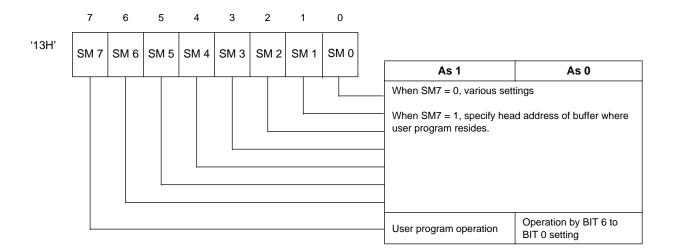

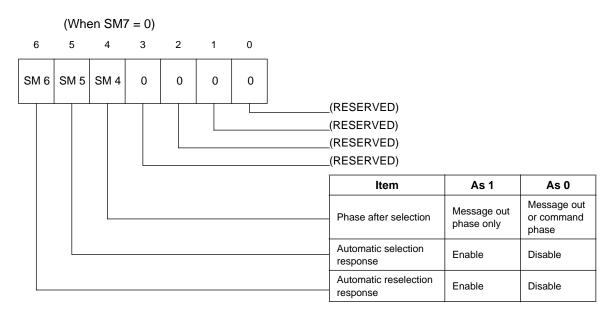

BIT 7: User program operation

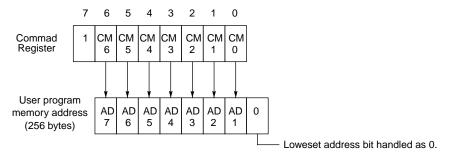

This bit indicates whether the SPC operation will be conducted by the user program or by command. The meaning of BIT 6-0 changes depending on this bit setting.

0:Write the command code in BIT 6-0 (see chapter 4 for more on command codes).

1:Write the head address of the user program in BIT 6-0 (Figure 3.2.8). The SPC starts executing from the command at the address specified in the user program memory written in this bit. The head address of the user program can be specified in 2-byte units (only even address).

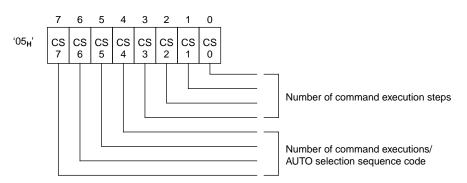

### 3.2.9 Command Step Register (READ)

The command step register (READ) indicates the number of command execution steps and program steps in the user program.

An FIFO-type register (8 bytes), it stores command steps corresponding to the interrupt status register.

### Command Step Register (READ)

The command step register (READ) bit configuration is shown below.

Next, the functionality of each bit is described.

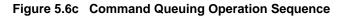

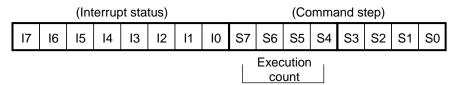

BIT 7-4: Number of user program command executions/Automatic selection response mode sequence code

During user program operation: Ring counter which indicates the number of command executions. Advanced with each command execution start.

Only counts discrete commands. Special commands are not counted (see 4.1 for more on discrete commands and special commands).

During Automatic selection response mode (target only) operation: Indicates the type of response operation sequence (see 3.3.4 for more on the Automatic selection response mode).

BIT 3-0:Number of command execution steps

Indicates the number of command execution steps. Step codes are defined for each command (see chapter 4 for more on command steps). Same when set to the Automatic selection/reselection response mode. In the Automatic receive mode, information is received but this bit is not affected.

(Example) When an "Initial phase error & MSG-receive" interrupt occurs, the execution step at which the phase error occurred is indicated.

#### Notes on Reading Command Step Register

- The contents of interrupt status register (address 04h) are the interrupt codes generated at the step indicated in this command step register. Therefore, it is necessary to read out this register along with the interrupt status register.

When 8-bit MPU is used, be sure always read out this step register after reading out the interrupt status register. If not, the next interrupt status will not be indicated. Also, if this register is read out before reading out the interrupt status register, the correct interrupt status will not be read out.

- 2) Please do not access this step register until Bit 6 (SPC Busy bit) of SPC Status register becomes "0" after issuing the command. If a new command is issued, please read out the existing step codes in advance.

### 3.2.10 Data Block Register (READ/WRITE)

# The data block register (READ/WRITE) specifies the number of blocks for data phase transfers.

#### Data Block Register (READ/WRITE)

The data block register (READ/WRITE) bit configuration is shown below.

|                    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------------------|----|----|----|----|----|----|----|----|

| '06 <sub>H</sub> ' | BL |

|                    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| '07 <sub>H</sub> ' | BL |

|                    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

Specify the number of blocks to be transferred in the data phase in the data block register bits.

Fixed length: Specify the number of transfer blocks.

Variable length: Enter 0001<sub>H</sub>.

This register's read values become valid after the completion report (including abnormal completions),

when the data block register and byte register are both 00 following a normal completion or when the number of untransferred blocks and bytes are reported following an abnormal completion.

#### (Example)

Set values: Blocks at  $000A_H$  and byte length at  $000100_H$ .

Normal: Blocks at  $0000_{H}$  and byte length at  $00000_{H}$ .

Abnormal 1: Blocks at 0004<sub>H</sub> and byte length at 000AC<sub>H</sub>.

In this case, the untransferred data is four blocks and  $AC_H$  bytes. Meanwhile, the transferred data is five blocks and  $54_H$  bytes.

Abnormal 2: Blocks at  $0004_{H}$  and bytes at  $0000_{H}$ .

In this case, the untransferred data is four blocks, and the transferred data is six blocks.

Abnormal 3: Blocks at  $0005_H$  and byte length at  $0100_H$ .

In this case, the untransferred data is six blocks (five blocks and  $100_{\rm H}$  bytes), and the transferred data is four blocks.

#### Data Block Register Access

The data block register becomes valid after the completion report (including abnormal completions). Prior to the completion report, initial values are indicated.

Please specify (set) this register when SPC Busy bit (Bit 6 of SPC status register) = "0".

### MEMO

#### 3.2 BASIC CONTROL REGISTER

### 3.2.11 Data Byte/MC Byte Register (READ/WRITE)

The data byte/MC byte register (READ/WRITE) specifies the number of transfer bytes for data phase transfers and message phase/ command phase transfers.

#### Data Byte/MC Byte Register (READ/WRITE)

The data byte/MC byte register (READ/WRITE) bit configuration is shown below.

|                    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

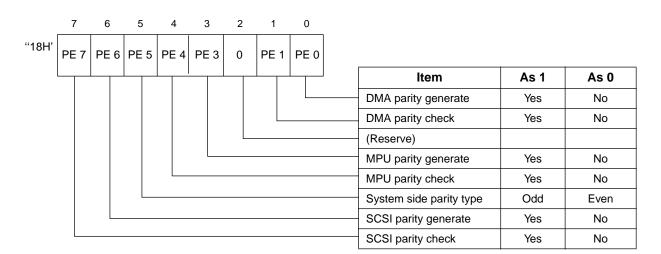

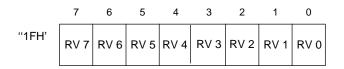

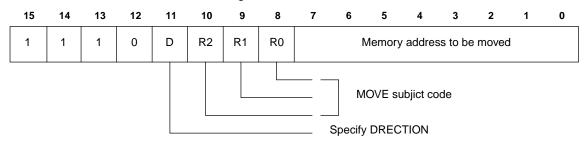

|--------------------|----|----|----|----|----|----|----|----|