# FUĴITSU

VLSI Communication Architectures Lab, Fujitsu Microelectronics Ltd, Vaughan Street, West Gorton Manchester M12 5DU UK Tel : +44 61 230 6262 Fax : +44 62 230 6276

# ENHANCEMENT SUMMARY

Network Termination Controller (NTC)

# MB86683/MB86683A

Edition 1.0, May 1994

| 2.1. Summary       3         2.2. Pin Assignment       4         2.3. JTAG Test Port       5         2.4. System Clock       11         2.5. Cell Stream Interface       12         2.6. Microprocessor Interface       13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1. INTRODUCTION                          | 2  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----|--|

| 1.2. Purpose of Document       2         1.3. Disclosure       2         2. HARDWARE CHANGES       3         2.1. Summary       3         2.2. Pin Assignment       4         2.3. JTAG Test Port       5         2.4. System Clock       11         2.5. Cell Stream Interface       12         2.6. Microprocessor Interface       13         3. FUNCTIONAL CHANGES       14         3.1. Receive / Transmit Framer       14         3.2. Network Statistics Record       15         3.3. Cell Stream Interface       18         3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22 | 1.1. Document Change History             | 2  |  |

| 2. HARDWARE CHANGES       3         2.1. Summary       3         2.2. Pin Assignment       4         2.3. JTAG Test Port       5         2.4. System Clock       11         2.5. Cell Stream Interface       12         2.6. Microprocessor Interface       13         3. FUNCTIONAL CHANGES       14         3.1. Receive / Transmit Framer       14         3.2. Network Statistics Record       15         3.3. Cell Stream Interface       18         3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                          | 1.2. Purpose of Document                 | 2  |  |

| 2.1. Summary       3         2.2. Pin Assignment       4         2.3. JTAG Test Port       5         2.4. System Clock       11         2.5. Cell Stream Interface       12         2.6. Microprocessor Interface       13         3. FUNCTIONAL CHANGES       14         3.1. Receive / Transmit Framer       14         3.2. Network Statistics Record       15         3.3. Cell Stream Interface       18         3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                              | 1.3. Disclosure                          | 2  |  |

| 2.2. Pin Assignment       4         2.3. JTAG Test Port       5         2.4. System Clock       11         2.5. Cell Stream Interface       12         2.6. Microprocessor Interface       13         3. FUNCTIONAL CHANGES       14         3.1. Receive / Transmit Framer       14         3.2. Network Statistics Record       15         3.3. Cell Stream Interface       18         3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                           | 2. HARDWARE CHANGES                      | 3  |  |

| 2.3. JTAG Test Port       5         2.4. System Clock       11         2.5. Cell Stream Interface       12         2.6. Microprocessor Interface       13         3. FUNCTIONAL CHANGES       14         3.1. Receive / Transmit Framer       14         3.2. Network Statistics Record       15         3.3. Cell Stream Interface       18         3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                               | 2.1. Summary                             | 3  |  |

| 2.4. System Clock       11         2.5. Cell Stream Interface       12         2.6. Microprocessor Interface       13         3. FUNCTIONAL CHANGES       14         3.1. Receive / Transmit Framer       14         3.2. Network Statistics Record       15         3.3. Cell Stream Interface       18         3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                                                                   | 2.2. Pin Assignment                      | 4  |  |

| 2.5. Cell Stream Interface122.6. Microprocessor Interface133. FUNCTIONAL CHANGES143.1. Receive / Transmit Framer143.2. Network Statistics Record153.3. Cell Stream Interface183.4. Cell Transmitter / Receiver183.5. OAM controller183.6. Microprocessor / DMA Interface193.7. Switch Statistics Handler.193.8. JTAG Test Circuitry193.9. Control Registers203.10. Status Registers22                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.3. JTAG Test Port                      | 5  |  |

| 2.6. Microprocessor Interface133. FUNCTIONAL CHANGES143.1. Receive / Transmit Framer143.2. Network Statistics Record153.3. Cell Stream Interface183.4. Cell Transmitter / Receiver183.5. OAM controller183.6. Microprocessor / DMA Interface193.7. Switch Statistics Handler.193.8. JTAG Test Circuitry193.9. Control Registers203.10. Status Registers22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.4. System Clock                        | 11 |  |

| 3. FUNCTIONAL CHANGES143.1. Receive / Transmit Framer143.2. Network Statistics Record153.3. Cell Stream Interface183.4. Cell Transmitter / Receiver183.5. OAM controller183.6. Microprocessor / DMA Interface193.7. Switch Statistics Handler193.8. JTAG Test Circuitry193.9. Control Registers203.10. Status Registers22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.5. Cell Stream Interface               | 12 |  |

| 3.1. Receive / Transmit Framer143.2. Network Statistics Record153.3. Cell Stream Interface183.4. Cell Transmitter / Receiver183.5. OAM controller183.6. Microprocessor / DMA Interface193.7. Switch Statistics Handler193.8. JTAG Test Circuitry193.9. Control Registers203.10. Status Registers22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.6. Microprocessor Interface            | 13 |  |

| 3.2. Network Statistics Record       15         3.3. Cell Stream Interface       18         3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3. FUNCTIONAL CHANGES                    | 14 |  |

| 3.3. Cell Stream Interface       18         3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface       19         3.7. Switch Statistics Handler       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.1. Receive / Transmit Framer           | 14 |  |

| 3.4. Cell Transmitter / Receiver       18         3.5. OAM controller       18         3.6. Microprocessor / DMA Interface.       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.2. Network Statistics Record           | 15 |  |

| 3.5. OAM controller       18         3.6. Microprocessor / DMA Interface.       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.3. Cell Stream Interface               | 18 |  |

| 3.6. Microprocessor / DMA Interface.       19         3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.4. Cell Transmitter / Receiver         | 18 |  |

| 3.7. Switch Statistics Handler.       19         3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.5. OAM controller                      | 18 |  |

| 3.8. JTAG Test Circuitry       19         3.9. Control Registers       20         3.10. Status Registers       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.6. Microprocessor / DMA Interface      | 19 |  |

| 3.9. Control Registers203.10. Status Registers22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.7. Switch Statistics Handler           | 19 |  |

| 3.10. Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.8. JTAG Test Circuitry                 | 19 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | 20 |  |

| 3.11. Additional / Modified Register Map 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          | 22 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.11. Additional / Modified Register Map | 24 |  |

-

## **1. INTRODUCTION**

# **1.1. Document Change History**

Issue 0.1, first draft by Steve Dabecki, Jan 10th 1993.

Issue 0.2, added extra functionality and expanded some sections, Mar 1st 1994.

Edition 1.0, modified sections and redefined the UTOPIA interface, May 27th 1994.

# **1.2. Purpose of Document**

This document details both the hardware and functional changes between the engineering sample version of the Network Termination Controller (NTC), and the production version of this device. These two parts have the chip numbers MB86683 and MB86683A respectively.

This document should be read in conjunction with the latest version of the NTC datasheet (Edition 1.0 October 1993).

# 1.3. Disclosure

All Rights Reserved.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical applications. Complete information sufficient for construction purposes is not necessarily given.

This information contained in this document does not convey any license under copyrights, patent rights, software rights or trademarks claimed by Fujitsu.

The information contained in this document has been carefully checked and believed to be reliable. However Fujitsu assumes no responsibility for inaccuracies.

Fujitsu reserves the right to change the product specifications without notice.

No part of this publication may be copied or reproduced in any form without the prior written consent of Fujitsu.

# 2. HARDWARE CHANGES

# 2.1. Summary

The main hardware changes between the two devices has been the addition of 9 signal pins. The purpose of these pins can be summarised in 4 ways :-

| 1. Addition of JTAG test pins :                 | TDO<br>TDI<br>T <b>MS</b><br>TCK | (pin 132)<br>(pin 131)<br>(pin 130)<br>(pin 129) |

|-------------------------------------------------|----------------------------------|--------------------------------------------------|

| 2. Additional system clock pin:                 | DCLK<br>CLKSEL                   | (pin 61)<br>(pin 62)                             |

| 3. Increased functionality of the Cell Stream : | CS/UT                            | (pin 64)                                         |

| 4. Additional microprocessor pins :             | BCLR<br>BERR                     | (pin 173)<br>(pin 124)                           |

Also, one pin name has been changed to improve clarity. Pin DCOUT/DCOUT (pin 169), has been renamed to DCOUT/BGOUT. BGOUT is an abbreviation for Bus Grant Out, and is used in conjunction with the Bus Grant (BG) signal in MOTOROLA mode.

It should be noted that use of internal pull-up resistors on some of these pins ensures that the MB86683A is backwardly compatible.

The following pins have internal pull-up resistors :-

CLKSEL, CS/UT, BCLR, BERR.

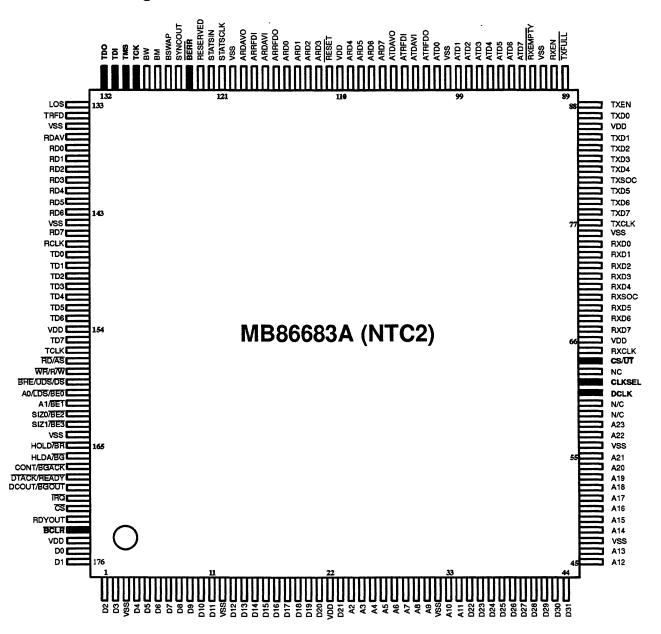

The additional pins are highlighted in bold in the following pin assignment diagram. The pins are also shaded for clarity.

Further explanation of these signals follow the pin assignment diagram.

## 2.2. Pin Assignment

# 2.3. JTAG Test Port

MB86683A now contains Boundary Scan Test Circuitry compliant with IEEE 1149.1 (JTAG). This requires the addition of the 4 pins described earlier. The JTAG circuitry is internally reset at power on, and hence the optional JTAG reset pin (TRST) is not required.

The JTAG circuitry allows easier board level testing by allowing the signal pins on the device to form a serial scan chain around the device. The test modes are controlled by accessing an internal Test Access Port Controller (TAP), which is in turn controlled from the TAP.

The Boundary Scan Register (BSR) consists of 223 registers, which form a serial shift register starting from pin 133 (LOS), moving in a anti-clockwise direction around the chip to finish at pin 128 (BW).

It should be noted that none of the internal D-types which form the BSR are reset, and hence are initially undefined. A valid pattern needs to be shifted into the register prior to any testing. However, while the JTAG TAP controller is reset, the I/O pins are connected through to the system logic.

A detailed explanation of the scan chain is given in the following tables, and uses the following key :-

| <u>Pin Type</u> :      | I = Input, C = Clock input, O = Output, B = Bidirectional,<br>T = Tristate, Iu = Input with pull-up resistor.                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>BSR Cell Type</u> : | <ul> <li>BSI1 allows capture of device input pin and control of logic input pin.</li> <li>BSI3 allows capture of device input pin only.</li> <li>BSO allows capture of logic output pin and control of device output pin ( = BSI1 ).</li> <li>BSOE allows control of tristate-able output pin.</li> <li>BSDI allows control of bidirectional pin ( = BSOE ).</li> <li>BSBI allows capture and control of bidirectional input and output pin ( = BSI1 + BSO ).</li> </ul> |

| Control Group No. :    | Denotes a JTAG BSR cell which controls a (group of) tristate-able output(s) or bidirectional pin(s).                                                                                                                                                                                                                                                                                                                                                                     |

| Controlled Group No.   | : Denotes a JTAG BSR cell which connects to a tristate-able<br>output or bidirectional pin which is controlled by the JTAG BSR<br>cell numbered in the previous column.                                                                                                                                                                                                                                                                                                  |

| BSR<br>Cell<br>No. | BSR<br>Cell<br>Type | Control<br>Group<br>No. | Controlled<br>Group<br>No. | Pin<br>Type | Pin<br>No. | Pin<br>Name    |

|--------------------|---------------------|-------------------------|----------------------------|-------------|------------|----------------|

| 1                  | BSI1                |                         |                            | 1           | 133        | LOS            |

| 2                  | BSI1                |                         |                            | I           | 134        | TRFD           |

| 3                  | BSI1                |                         |                            | 1           | 136        | RDAV           |

| 4                  | BSI1                |                         |                            | 1           | 137        | RD0            |

| 5                  | BSI1                |                         |                            | 1           | 138        | RD1            |

| 6                  | BSI1                |                         |                            | I           | 139        | RD2            |

| 7                  | BSI1                |                         |                            | 1           | 140        | RD3            |

| 8                  | BSI1                |                         |                            | 1           | 141        | RD4            |

| 9                  | BSI1                |                         |                            | 1           | 142        | RD5            |

| 10                 | BSI1                |                         |                            | I           | 143        | RD6            |

| 11                 | BSI1                |                         |                            | 1           | 145        | RD7            |

| 12                 | BSI3                |                         |                            | С           | 146        | RCLK           |

| 13                 | BSO                 |                         |                            | 0           | 147        | TD0            |

| 14                 | BSO                 |                         |                            | 0           | 148        | TD1            |

| 15                 | BSO                 |                         |                            | 0           | 149        | TD2            |

| 16                 | BSO                 |                         |                            | 0           | 150        | TD3            |

| 17                 | BSO                 |                         |                            | 0           | 151        | TD4            |

| 18                 | BSO                 |                         |                            | 0           | 152        | TD5            |

| 19                 | BSO                 |                         |                            | 0           | 153        | TD6            |

| 20                 | BSO                 |                         |                            | 0           | 155        | TD7            |

| 21                 | BSI3                |                         |                            | С           | 156        | TCLK           |

|                    |                     |                         |                            |             |            |                |

| 22                 | BSDI                | 1                       |                            |             |            |                |

| 23 & 24            | BSBI                |                         | 1                          | В           | 157        | RD / AS        |

| 25 & 26            | BSBI                |                         | 1                          | В           | 158        | WR/R/W         |

| 27                 | BSDI                | 2                       |                            |             |            |                |

| 28 & 29            | BSBI                |                         | 2                          | В           | 159        | BHE / UDS / DS |

| 30 & 31            | BSBI                |                         | 1                          | В           | 160        | A0 / LDS / BEO |

| 32 & 33            | BSBI                |                         | 1                          | В           | 161        | A1/BET         |

| 34                 | BSDI                | 3                       |                            |             |            |                |

| 35 & 36            | BSBI                |                         | 3                          | В           | 162        | SIZO / BE2     |

| 37 & 38            | BSBI                |                         | 3                          | В           | 163        | SIZ1 / BE3     |

| 39                 | BSDI                | 4                       |                            |             |            |                |

| 40 & 41            | BSBI                |                         | 4.                         | В           | 165        | HOLD / BR      |

| 42                 | BSI1                |                         |                            | I           | 166        | HLDA / BG      |

| 43                 | BSDI                | 5                       |                            |             |            |                |

| 44 & 45            | BSBI                |                         | 5                          | В           | 167        | CONT / BGACK   |

| 46                 | BSI1                |                         | ſ                          | I           | 168        | DTACK / READY  |

| 47                 | BSOE                | 6                       | T                          |             |            |                |

| 48                 | BSO                 |                         | 6                          | Т           | 169        | DCOUT / BGOUT  |

| 49                 | BSOE                | 7                       |                            |             |            |                |

| 50                 | BSO                 |                         | 7                          | Т           | 170        | IRQ            |

| BSR<br>Cell<br>No.  | BSR<br>Cell<br>Type | Control<br>Group<br>No. | Controlled<br>Group<br>No. | Pin<br>Type | Pin<br>No. | Pin<br>Name |

|---------------------|---------------------|-------------------------|----------------------------|-------------|------------|-------------|

| 51                  | BSI1                |                         |                            | l           | 171        | CS          |

| 52                  | BSO                 |                         |                            | 0           | 172        | RDYOUT      |

| 53                  | BSI1                |                         |                            | I           | 173        | BCLR        |

| 54                  | BSDI                | 8                       |                            |             |            |             |

| 55 & 56             | BSBI                |                         | 8                          | В           | 175        | D0          |

| 57 & 58             | BSBI                |                         | 8                          | В           | 176        | D1          |

| 59 & 60             | BSBI                |                         | 8                          | В           | 1          | D2          |

| 61 & 62             | BSBI                |                         | 8                          | В           | 2          | D3          |

| 63 & 64             | BSBI                |                         | 8                          | В           | 4          | D4          |

| 65 & 66             | BSBI                |                         | 8                          | В           | 5          | D5          |

| 67 & 68             | BSBI                |                         | 8                          | В           | 6          | D6          |

| 69 & 70             | BSBI                |                         | 8                          | В           | 7          | D7          |

| 71 & 72             | BSBI                |                         | 8                          | В           | 8          | D8          |

| 73 & 74             | BSBI                |                         | 8                          | В           | 9          | D9          |

| 75 & 76             | BSBI                |                         | 8                          | В           | 10         | D10         |

| 77 & 78             | BSBI                |                         | 8                          | В           | 11         | D11         |

| 79 & 80             | BSBI                |                         | 8                          | В           | 13         | D12         |

| 81 & 82             | BSBI                |                         | 8                          | В           | 14         | D13         |

| 83 & 84             | BSBI                |                         | 8                          | В           | 15         | D14         |

| 85 & 86             | BSBI                |                         | 8                          | В           | 16         | D15         |

| 87                  | BSDI                | 9                       |                            |             |            |             |

| 88 & 89             | BSBI                |                         | 9                          | В           | 17         | D16         |

| 90 & 91             | BSBI                |                         | 9                          | В           | 18         | D17         |

| 92 & 93             | BSBI                |                         | 9                          | В           | 19         | D18         |

| 94 & 95             | BSBI                |                         | 9                          | В           | 20         | D19         |

| <b>96 &amp; 9</b> 7 | BSBI                |                         | 9                          | В           | 21         | D20         |

| 98 & 99             | BSBI                |                         | 9                          | В           | 23         | D21         |

| 100 & 101           | BSBI                |                         | 1                          | В           | 24         | A2          |

| 102 & 103           | BSBI                |                         | 1                          | В           | 25         | A3          |

| 104 & 105           | BSBI                |                         | 1                          | В           | 26         | A4          |

| 106 & 107           | BSBI                |                         | 1                          | В           | 27         | A5          |

| 108 & 109           | BSBI                |                         | 1                          | В           | 28         | A6          |

| 110                 | BSO                 |                         | 1                          | Т           | 29         | A7          |

| 111                 | BSO                 |                         | 1_                         | Т           | 30         | A8          |

| 112                 | BSO                 |                         | 1                          | Т           | 31         | A9          |

| 113                 | BSO                 |                         | 1                          | Т           | 33         | A10         |

| 114                 | BSO                 |                         | 1                          | Т           | 34         | A11         |

| 115 & 116           | BSBI                |                         | 9                          | В           | 35         | D22         |

| 117 & 118           | BSBI                |                         | 9                          | В           | 36         | D23         |

| 119 & 120           | BSBI                |                         | 9                          | В           | 37         | D24         |

| 121 & 122           | BSBI                |                         | 9                          | В           | 38         | D25         |

| 123 & 124           | BSBI                |                         | 9                          | В           | 39         | D26         |

| BSR<br>Cell<br>No. | BSR<br>Cell<br>Type | Control<br>Group<br>No. | Controlled<br>Group<br>No. | Pin<br>Type | Pin<br>No. | Pin<br>Name |

|--------------------|---------------------|-------------------------|----------------------------|-------------|------------|-------------|

| 125 & 126          | BSBI                |                         | 9                          | В           | 40         | D27         |

| 127 & 128          | BSBI                |                         | 9                          | В           | 41         | D28         |

| 129 & 130          | BSBI                |                         | 9                          | В           | 42         | D29         |

| 131 & 132          | BSBI                |                         | 9                          | В           | 43         | D30         |

| 133 & 134          | BSBI                |                         | 9                          | В           | 44         | D31         |

| 135                | BSO                 |                         | 1                          | Т           | 45         | A12         |

| 136                | BSO                 |                         | 1                          | Т           | 46         | A13         |

| 137                | BSO                 |                         | 1                          | Т           | 48         | A14         |

| 138                | BSO                 |                         | 1                          | Т           | 49         | A15         |

| 139                | BSO                 |                         | 1                          | Т           | 50         | A16         |

| 140                | BSO                 |                         | 1                          | Т           | 51         | A17         |

| 141                | BSO                 |                         | 1                          | т           | 52         | A18         |

| 142                | BSO                 |                         | 1                          | Т           | 53         | A19         |

| 143                | BSO                 |                         | 1                          | Т           | 54         | A20         |

| 144                | BSO                 |                         | 1                          | Т           | 55         | A21         |

| 145                | BSO                 |                         | 1                          | Т           | 57         | A22         |

| 146                | BSO                 |                         | 1                          | Т           | 58         | A23         |

|                    |                     |                         |                            |             |            |             |

| 147                | BSI3                |                         |                            | С           | 61         | DCLK        |

| 148                | BSI1                |                         |                            | lu          | 62         | CLKSEL      |

| 149                | BSI1                |                         |                            | lu          | 64         | CS/UT       |

| 150                | BSI3                |                         |                            | С           | 65         | RXCLK       |

| 151                | BSO                 |                         |                            | 0           | 67         | RXD7        |

| 152                | BSO                 |                         |                            | 0           | 68         | RXD6        |

| 153                | BSO                 |                         |                            | 0           | 69         | RXD5        |

| 154                | BSO                 |                         |                            | 0           | 70         | RXSOC       |

| 155                | BSO                 |                         |                            | 0           | 71         | RXD4        |

| 156                | BSO                 |                         |                            | 0           | 72         | RXD3        |

| 157                | BSO                 |                         |                            | 0           | 73         | RXD2        |

| 158                | BSO                 |                         |                            | 0           | 74         | RXD1        |

| 159                | BSO                 |                         |                            | 0           | 75         | RXD0        |

| 160                | BSI3                |                         |                            | С           | 77         | TXCLK       |

| 161                | BSI1                | 1                       |                            | I           | 78         | TXD7        |

| 162                | BSI1                |                         | -                          | 1           | 79         | TXD6        |

| 163                | BSI1                |                         |                            | 1           | 80         | TXD5        |

| 164                | BSI1                |                         |                            | I           | 81         | TXSOC       |

| 165                | BSI1                |                         | 1                          | I           | 82         | TXD4        |

| 166                | BSI1                |                         |                            | I           | 83         | TXD3        |

| 167                | BSI1                |                         |                            | 1           | 84         | TXD2        |

| 168                | BSI1                |                         |                            | 1           | 85         | TXD1        |

| 169                | BSI1                |                         |                            | 1           | 87         | TXD0        |

| 170                | BSI1                |                         |                            | I           | 88         | TXEN        |

| BSR<br>Cell<br>No. | BSR<br>Cell<br>Type | Control<br>Group<br>No. | Controlled<br>Group<br>No. | Pin<br>Type | Pin<br>No. | Pin<br>Name |

|--------------------|---------------------|-------------------------|----------------------------|-------------|------------|-------------|

| 171                | BSO                 |                         |                            | 0           | 89         | TXFULL      |

| 172                | BSI1                |                         |                            | I           | 90         | RXEN        |

| 173                | BSO                 |                         |                            | 0           | 92         | RXEMPTY     |

| 174                | BSDI                | 10                      |                            |             |            |             |

| 175 & 176          | BSBI                |                         | 10                         | В           | 93         | ATD7        |

| 177 & 178          | BSBI                |                         | 10                         | В           | 94         | ATD6        |

| 179 & 180          | BSBI                |                         | 10                         | В           | 95         | ATD5        |

| 181 & 182          | BSBI                |                         | 10                         | В           | 96         | ATD4        |

| 183 & 184          | BSBI                |                         | 10                         | В           | 97         | ATD3        |

| 185 & 186          | BSBI                |                         | 10                         | В           | 98         | ATD2        |

| 187 & 188          | BSBI                |                         | 10                         | В           | 99         | ATD1        |

| 189 & 190          | BSBI                |                         | 10                         | В           | 101        | ATD0        |

| 191                | BSO                 |                         |                            | 0           | 102        | ATRFDO      |

| 192                | BSI1                |                         |                            | l           | 103        | ATDAVI      |

| 193                | BSI1                |                         |                            | I           | 104        | ATRFDI      |

| 194                | BSO                 |                         |                            | 0           | 105        | ATDAVO      |

| 195                | BSDI                | 11                      |                            |             |            |             |

| 196 & 197          | BSBI                |                         | 11                         | В           | 106        | ARD7        |

| 198 & 199          | BSBI                |                         | 11                         | В           | 107        | ARD6        |

| 200 & 201          | BSBI                |                         | 11                         | В           | 108        | ARD5        |

| 202 & 203          | BSBI                |                         | 11                         | В           | 109        | ARD4        |

| 204                | BSI1                |                         |                            | I           | 111        | RESET       |

| 205 & 206          | BSBI                |                         | 11                         | В           | 112        | ARD3        |

| 207 & 208          | BSBI                |                         | 11                         | В           | 113        | ARD2        |

| 209 & 210          | BSBI                |                         | 11                         | В           | 114        | ARD1        |

| 211 & 212          | BSBI                |                         | 11                         | В           | 115        | ARD0        |

| 213                | BSO                 |                         |                            | 0           | 116        | ARRFDO      |

| 214                | BSI1                |                         |                            | I           | 117        | ARDAVI      |

| 215                | BSI1                |                         |                            | l           | 118        | ARRFDI      |

| 216                | BSO                 |                         |                            | 0           | 119        | ARDAVO      |

| 217                | BSI3                |                         |                            | С           | 121        | STATSCLK    |

| 218                | BSI1                |                         |                            | I           | 122        | STATSIN     |

| 219                | BSI1                |                         |                            | I           | 124        | BERR        |

| 220                | BSO                 | ×                       | -                          | 0           | 125        | SYNCOUT     |

| 221                | BSI1                |                         |                            | I           | 126        | BSWAP       |

| 222                | BSI1                |                         |                            | I           | 127        | BM          |

| 223                | BSI1                |                         |                            | 1           | 128        | BW          |

|                    |                     |                         |                            |             |            |             |

|                    |                     |                         |                            | С           | 129        | ТСК         |

|                    |                     |                         |                            | 1           | 130        | TMS         |

|                    |                     |                         |                            | I           | 131        | TDI         |

|                    |                     |                         |                            | Т           | 132        | TDO         |

| BSR<br>Cell<br>No. | BSR<br>Cell<br>Type | Control<br>Group<br>No. | Controlled<br>Group<br>No. | Pin<br>Type | Pin<br>No. | Pin<br>Name     |

|--------------------|---------------------|-------------------------|----------------------------|-------------|------------|-----------------|

|                    |                     |                         |                            |             | 3          | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 12         | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 32         | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 47         | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 56         | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 76         | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 91         | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 100        | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 120        | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 135        | V <sub>SS</sub> |

|                    |                     |                         |                            |             | 144        | V <sub>SS</sub> |

|                    |                     | 1                       |                            |             | 164        | V <sub>SS</sub> |

|                    |                     |                         |                            |             |            |                 |

|                    |                     |                         |                            |             | 22         | V <sub>DD</sub> |

|                    |                     |                         |                            |             | 66         | V <sub>DD</sub> |

|                    |                     |                         |                            |             | 86         | V <sub>DD</sub> |

|                    |                     |                         |                            |             | 110        | V <sub>DD</sub> |

|                    |                     |                         |                            |             | 154        | V <sub>DD</sub> |

|                    |                     |                         |                            |             | 174        | V <sub>DD</sub> |

|                    |                     |                         |                            |             |            |                 |

|                    |                     |                         |                            |             | 59         | N/C             |

|                    |                     |                         |                            |             | 60         | N/C             |

|                    |                     |                         |                            |             | 63         | N/C             |

|                    |                     |                         |                            |             | 123        | N/C             |

-

.

.

# 2.4. System Clock

In MB86683, the system clock pin is RXCLK. This pin is also used as the Cell Stream Interface (CSI) receive clock. The CSI should typically be clocked at 20MHz to support a maximum data rate of 160Mbps across this interface.

This rate would then support the 155.52Mbps (19.44 MHz byte clock) at the transceiver interface.

There may be cases where it is desirable to use a CSI clock of less than 20MHz, in a case where the transceiver interface data rate is considerably lower than 155Mbps, eg E3 framing mode at 34Mbps.

If the RXCLK frequency was lowered in this case, then this would reduce the internal operating speed of the device, and hence all DMA transfers will be proportionately slower.

In MB86683A, an extra pin has been added which may be used as the system clock instead of RXCLK. This clock is called DCLK, and may be derived directly from the processor clock.

Selection of the system clock is done by tying CLKSEL (clock select) pin either high or low. This pin has an internal pull-up resistor, which selects RXCLK by default, to ensure backward compatibility.

Hence,

- to select DCLK as the system clock : connect CLKSEL pin to VSS.

- to select RXCLK as the system clock : leave CLKSEL unconnected.

# 2.5. Cell Stream Interface

The Cell Stream Interface (CSI) provides access to higher layers in the ATM protocol stack. Data across this interface is byte based, but a cell synchronisation signal is provided to give information on the cell boundary. Furthermore, two extra signals are provided to support flow control between the NTC and any other external device supporting a similar scheme. This device may be a Fujitsu Adaptation Layer Controller (ALC), a FIFO used to increase the buffering at this layer, or any other similar device.

The additional signal CS/UT has been added (at pin 64) to give greater flexibility when connecting the NTC to such devices. This interface may be configured as either a standard Cell Stream interface, or as an interface compatible with that defined in the document :

"Utopia, an ATM-PHY Interface Specification" Level 1, Version 2.01 Version 2.0 March 21, 1994.

The CS/UT pin has an internal pull-up resistor, and may be left unconnected for backward compatibility to the MB86683 (i.e. a logic "1" on this pin specifies the Cell Stream interface : a logic "0" specifies the Utopia interface ).

The differences between the Cell Stream interface specification and the Utopia interface specification are as follows :-

- 1. Output signal changes occur on different clock edges ( Cell Stream on falling edge, Utopia on rising edge ).

- 2. Some flow control signals have different polarities (Cell Stream TXEN & RXEN are active high, Utopia TXEN & RXEN are active low ).

- 3. Backward flow control applies to next transfer in Cell Stream and to next edge in Utopia. This is further modified in Utopia by provision of a four-transfer lookahead only on the transmit side (i.e. TXFULL is asserted when five (5) more transfers after the current cycle will cause buffer overrun and data loss).

- 4. The Cell Stream interface includes the data format in the specification, because it has to define the routing tag applied to the front of cells going to the MB86680 SRE device. Utopia has no current specification of the data format.

The only aspect of Utopia which the NTC does not support is the tri-stating of the RXD & RXSOC outputs under the control of the RXEN input.

## 2.6. Microprocessor Interface

The microprocessor interface has two additional pins, namely BCLR and BERR. Both signals are active low inputs, and have internal pull–up resistors to allow backward compatibility with MB86683.

#### BCLR (Bus Clear) :

This signal may be asserted by the control processor to gain control of the system bus by suspending any NTC DMA transfer.

The NTC will release the bus and any DMA transfer will be internally suspended. The NTC DMA controller will then re-request the bus, and once the bus has been granted, the DMA transfer will resume.

#### BERR (Bus Error) :

This signal may be asserted by the control processor to abort any DMA transfer. This would normally be done if the NTC should hold the bus greater than a set time. This may occur if the DMA descriptors have been incorrectly programmed and the NTC is trying to access invalid memory, and hence a DTACK/READY signal will never be generated. On detecting this active signal, the NTC will release the bus and any DMA transfer will be internally aborted.

An interrupt may also be generated by enabling the BERR interrupt in CR58.

On receiving this interrupt, the processor may then read SR63 which will indicate which DMA channel was active when the DMA aborted.

# **3. FUNCTIONAL CHANGES**

There have been many functional improvements applied to the production version of the NTC (MB86683A). Some of these functionality improvements have been achieved by hardware changes described earlier.

These functionality improvements may be summarised as follows :-

## **3.1. Receive / Transmit Framer**

- 1. STS-1 framing mode (in accordance with proposed addition to ATM Forum UNI specification).

- 2. Support for DS-3 using non PLCP framing.

- 3. Additional support for DS-3 OAM using C-bit parity.

- 4. Microprocessor full-duplex access to 5 C-bits. (Provides AIC, FEAC and DL support).

- 5. SYNCOUT output now provides frame sync indication when in framed modes. Still provides cell sync indication in unframed mode.

- 6. Option to invert any of the transmitted BIP values (B1,B2,B3) for test purposes.

# **3.2. Network Statistics Record**

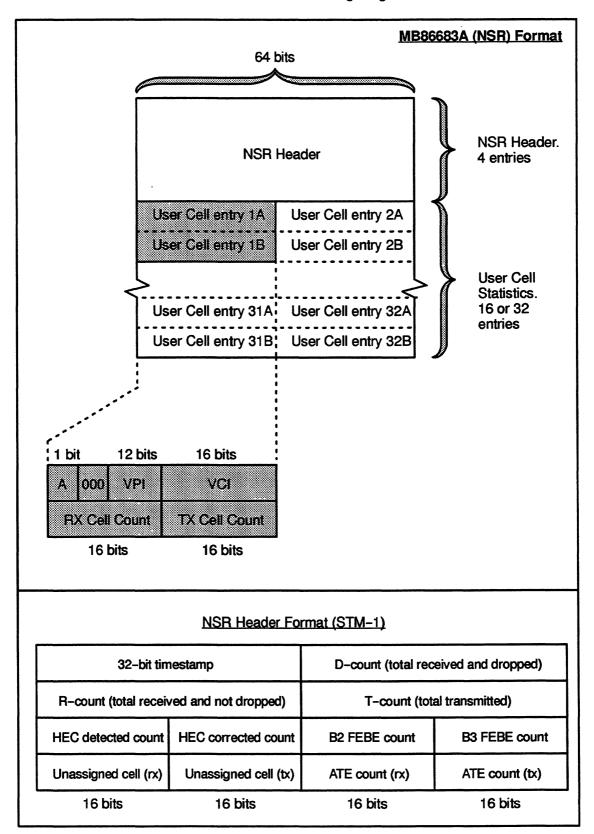

- 1. Improved statistics recording for ATM Forum UNI MIB support.

- 2. NSR now contains 32-bit counts for; total cells received and not dropped (R count), total cells received and dropped (D count), and total cells transmitted (T count).

- 3. NSR table selectable as either header only, header plus 16 user entries, or header plus 32 user entries.

- 4. Optional filtering of user statistics including "0,1 or X" bits over all 28 bits of the VP/VC fields. Allows a range of VP/VCs to monitored.

- 5. Filter may be set to either filter user cells defined by the mask, or not defined by the mask, or it may be disabled completely.

- 6. Optionally disable either of the automatic DMA transfer events, namely counter overflow, or programmable timer.

- 7. Optionally force DMA transfer, independent of automatic events.

- 8. Cell Insert counts in NSR header changed to ATE counts for both RX and TX paths.

- 9. User Cell counts recorded before address translation in RX path, and after address translation in TX path.

- 10. Unassigned Cell counts recorded after address translation in both RX and TX cases.

- 11. TXATE count on a per VP/VC basis has been deleted from the NSR.

- 12. Idle counts deleted (RX and TX), but indirectly available.

#### 3.2.1. Network Statistics – further details

The addition of the three 32-bit counters will allow added support for the UNI MIB specification. The conditions for which these counters are incremented are described as follows :

| R-count : | Total number of assigned ATM layer cells received at the<br>transceiver receive interface that have not been discarded.                   |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

|           |                                                                                                                                           |

| x         | These cells will emerge from the cell stream receive interface,                                                                           |

|           | unless they are discarded due to an address translation error, if<br>the RXATE bit is set to discard. They will not emerge if overwritten |

|           | due to inserted cells having priority.                                                                                                    |

|           | The R-count will still be incremented, even if the cell is discarded due to an address translation error.                                 |

|           | This count will not include cells that have been inserted via the                                                                         |

|           | insert buffer in the receive path.                                                                                                        |

| D-count : | Total number of cells received at the transceiver receive interface that have been discarded.                                             |

|           | The cells may have been discarded due to the following reasons :-                                                                         |

|           | – physical layer cells                                                                                                                    |

|           | - ATM layer cell with uncorrectable HEC error                                                                                             |

|           | <ul> <li>ATM layer cell which has been discarded via the discard mask</li> </ul>                                                          |

| T-count : | Total number of assigned ATM layer cells transmitted at the transceiver transmit interface.                                               |

|           |                                                                                                                                           |

This will include assigned ATM layer cells that have been inserted via the cell transmitter insert buffer.

In order to accommodate the additional cell counts, the NSR table has been rearranged and increased in size. The table now consists of  $36 \times 64$ -bit entities. As the counts are now either 16 or 32-bit wide, they are aligned on 16-bit boundaries to allow greater flexibility for CPU masking. The VPI/VCI values are also aligned on 16-bit boundaries.

As the NSR table is now a different size, the DMA word transfer count (CC) in the descriptor should be set as follows for single burst transfers :-

| Header only              | : CC = 16  |

|--------------------------|------------|

| Header + 16 user entries | : CC = 80  |

| Header + 32 user entries | : CC = 144 |

The format of the NSR is illustrated in the following diagram.

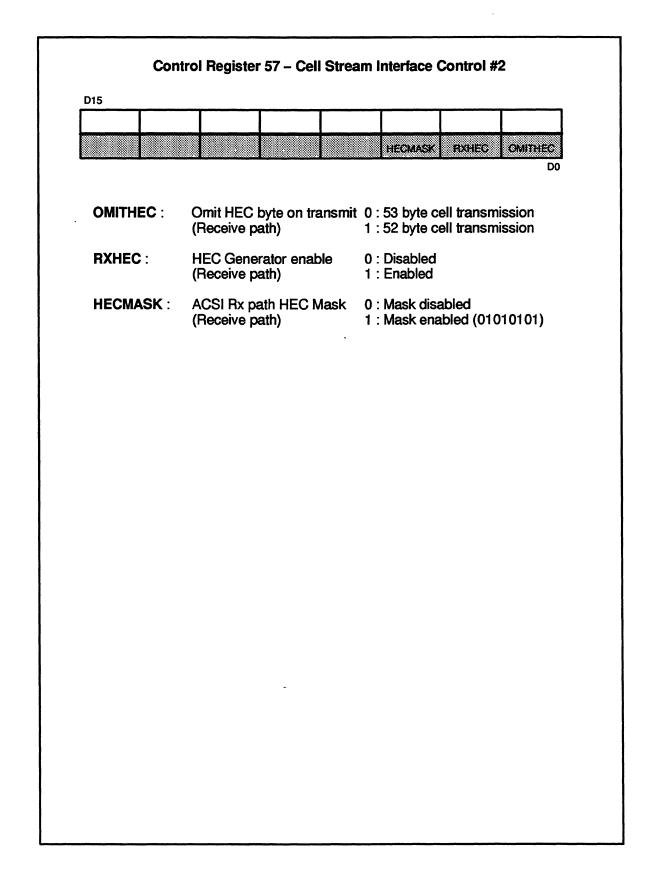

#### 3.3. Cell Stream Interface

- 1. Addition of 1 input pin to configure the cell stream interface for either existing cell stream functionality or UTOPIA. (CS/UT)

- 2. CSI now supports either 52 or 53 byte cells across the interface. In the 52 byte case, the HEC field is omitted. (OMITHEC bit in CR57).

- 3. Internal cell stream receive and transmit internal FIFOs have been reduced from 20 cells to 9.8 cells (512 bytes, excluding the HEC byte in each cell).

# **3.4. Cell Transmitter / Receiver**

- Option to generate either Idle cells or Unassigned cells for cell rate decoupling. (UNASGEN bit in CR26).

Idle cells will always be discarded within the cell receiver.

If unassigned cells are used for cell rate decoupling, then they may be discarded within the cell receiver by setting the UNASS bit in the Cell Receiver Discard register (CR25).

- 2. Option to ignore the GFC field for predefined cell type recognition (GFCIGN bit in CR18/CR26).

- 3. Distributed Sample Scrambler (DSS), which was used in cell-based mode (1 +  $x^{28} + x^{31}$ ), has been deleted.

# 3.5. OAM controller

- 1. Deleted autonomous support for F1/F3 OAM cells.

- 2. Removed LOM interrupt and OAM interrupt indication register used for F1/F3 cell based PLOAM (SR60).

- 3. Rearranged the physical layer alarm status bits in SR59.

#### **3.6.** Microprocessor / DMA Interface.

- 1. Addition of 2 microprocessor input pins to suspend/abort the NTC control of the bus. (BCLR and BERR).

- 2. Addition of 2 interrupts : BERR set on receiving active BERR on pin.

- : ICD set on gaining cell delineation.

- (moving from PRESYNC to SYNC state)

- 3. LOC interrupt now renamed to OCD (Out of Cell Delineation) in accordance with ATM Forum UNI.

- 4. LOM interrupt now deleted.

- 5. Microprocessor register read/write accesses now synchronous to the system clock. Internal read/writes require 7 clocks to complete.

- 6. Byte swapping of the Network Statistics Record and the Switch Statistics no longer performed. Data is always in big endian format to maintain data integrity.

- 7. SLT bit in Channel Control Register (CCR) of Descriptor Location Table no longer required. Direction of data transfer is implied by channel number.

# 3.7. Switch Statistics Handler.

1. Addition of separate register to enable this block independently from the Network Statistics. (CR50)

# **3.8. JTAG Test Circuitry**

1. Addition of JTAG test circuitry in accordance with IEEE 1149.1.

The above changes have required additional control registers. Some existing registers have also had their control bits moved.

Any extra registers or modified register bits with existing registers have been high lighted in the following register table, followed by the additional/modified register map.

# 3.9. Control Registers

| REG | ADDRESS | FUNCTION                                               | ACCESS     |

|-----|---------|--------------------------------------------------------|------------|

|     | AD06    |                                                        |            |

| 0   | 0       | Not Used                                               |            |

| 1   | 2       | General Framer Control                                 | Read/Write |

| 2   | 4       | Transmit Framer Overhead Access Bytes Block 1          | Write      |

| 3   | 6       | Transmit Framer Overhead Access Bytes Block 2          | Write      |

| 4   | 8       | Transmit Framer Overhead Access Bytes Block 3          | Write      |

| 5   | 10      | Transmit Framer Overhead Access Bytes Block 4          | Write      |

| 6   | 12      | Transmit Framer Overhead Access Bytes Block 5          | Write      |

| 7   | 14      | Transmit Framer Overhead Access Bytes Block 6          | Write      |

| 8   | 16      | Transmit Framer Overhead Access Bytes Block 7          | Write      |

| 9   | 18      | Transmit Framer Overhead Access Bytes Block 8          | Write      |

| 10  | 20      | Transmit Framer Overhead Access Bytes Block 9          | Write      |

| 11  | 22      | Transmit Framer Overhead Access Bytes Block 10         | Write      |

| 12  | 24      | Transmit Framer Overhead Access Bytes Block 11         | Write      |

| 13  | 26      | Transmit Framer Overhead Access Bytes Block 12         | Write      |

| 14  | 28      | Transmit Framer Overhead Access Bytes Block 13         | Write      |

| 15  | 30      | Transmit Framer Overhead Access Bytes Block 14         | Write      |

| 16  | 32      | Transmit Framer Overhead Access Bytes Block 15         | Write      |

| 17  | 34      | Transmit Framer Overhead Access Bytes Block 16         | Write      |

| 18  | 36      | Cell Receiver General Control                          | Read/Write |

| 19  | 38      | Cell Receiver HEC / Descrambler Control                | Read/Write |

| 20  | 40      | Cell Receiver User Defined Extract/Discard XMASK #1    | Read/Write |

| 21  | 42      | Cell Receiver User Defined Extract/Discard XMASK #2    | Read/Write |

| 22  | 44      | Cell Receiver User Defined Extract/Discard SMASK #1    | Read/Write |

| 23  | 46      | Cell Receiver User Defined Extract/Discard SMASK #2    | Read/Write |

| 24  | 48      | Cell Receiver Extract Buffer Control                   | Read/Write |

| 25  | 50      | Cell Receiver Discard Control                          | Read/Write |

| 26  | 52      | Cell Transmitter General Control                       | Read/Write |

| 27  | 54      | Cell Transmitter HEC / Scrambler Control               | Read/Write |

| 28  | 56      | Cell Transmitter User Defined Extract/Discard XMASK #1 | Read/Write |

| 29  | 58      | Cell Transmitter User Defined Extract/Discard XMASK #2 | Read/Write |

| 30  | 60      | Cell Transmitter User Defined Extract/Discard SMASK #1 | Read/Write |

| 31  | 62      | Cell Transmitter User Defined Extract/Discard SMASK #2 | Read/Write |

# **Control Registers (continued)**

| REG | ADDRESS | FUNCTION                                  | ACCESS     |

|-----|---------|-------------------------------------------|------------|

|     | AD06    |                                           |            |

| 32  | 64      | Cell Transmitter Extract Buffer Control   | Read/Write |

| 33  | 66      | Cell Transmitter Discard Control          | Read/Write |

| 34  | 68      | OAM Framed Alarm Control                  | Read/Write |

| 35  | 70      | Not Used                                  |            |

| 36  | 72      | Not Used                                  |            |

| 37  | 74      | Not Used                                  |            |

| 38  | 76      | Not Used                                  |            |

| 39  | 78      | Not Used                                  |            |

| 40  | 80      | Not Used                                  |            |

| 41  | 82      | Not Used                                  |            |

| 42  | 84      | Not Used                                  |            |

| 43  | 86      | Not Used                                  |            |

| 44  | 88      | Not Used                                  |            |

| 45  | 90      | Not Used                                  |            |

| 46  | 92      | Not Used                                  |            |

| 47  | 94      | Not Used                                  |            |

| 48  | 96      | Not Used                                  |            |

| 49  | 98      | Not Used                                  |            |

| 50  | 100     | Switch Statistics Handler Control         | Read/Write |

| 51  | 102     | Network Statistics General Control        | Read/Write |

| 52  | 104     | Network Statistics User Cell Mask XMASK#1 | Read/Write |

| 53  | 106     | Network Statistics User Cell Mask XMASK#2 | Read/Write |

| 54  | 108     | Network Statistics User Cell Mask SMASK#1 | Read/Write |

| 55  | 110     | Network Statistics User Cell Mask SMASK#2 | Read/Write |

| 56  | 112     | Cell Stream Interface Control #1          | Read/Write |

| 57  | 114     | Cell Stream Interface Control #2          | Read/Write |

| 58  | 116     | Interrupt Enable                          | Write      |

| 59  | 118     | Interrupt Under Service                   | Write      |

| 60  | 120     | DMA Descriptor Pointer Table Low          | Write      |

| 61  | 122     | DMA Descriptor Pointer Table High         | Write      |

| 62  | 124     | DMA Channel Activity                      | Write      |

| 63  | 126     | DMA Mode                                  | Write      |

# 3.10. Status Registers

| REG | ADDRESS | FUNCTION                                      | ACCESS |

|-----|---------|-----------------------------------------------|--------|

|     | AD06    |                                               |        |

| 0   | 0       |                                               |        |

| 1   | 2       |                                               |        |

| 2   | 4       | Receive Framer Overhead Access Bytes Block 1  | Read   |

| 3   | 6       | Receive Framer Overhead Access Bytes Block 2  | Read   |

| 4   | 8       | Receive Framer Overhead Access Bytes Block 3  | Read   |

| 5   | 10      | Receive Framer Overhead Access Bytes Block 4  | Read   |

| 6   | 12      | Receive Framer Overhead Access Bytes Block 5  | Read   |

| 7   | 14      | Receive Framer Overhead Access Bytes Block 6  | Read   |

| 8   | 16      | Receive Framer Overhead Access Bytes Block 7  | Read   |

| 9   | 18      | Receive Framer Overhead Access Bytes Block 8  | Read   |

| 10  | 20      | Receive Framer Overhead Access Bytes Block 9  | Read   |

| 11  | 22      | Receive Framer Overhead Access Bytes Block 10 | Read   |

| 12  | 24      | Receive Framer Overhead Access Bytes Block 11 | Read   |

| 13  | 26      | Receive Framer Overhead Access Bytes Block 12 | Read   |

| 14  | 28      | Receive Framer Overhead Access Bytes Block 13 | Read   |

| 15  | 30      | Receive Framer Overhead Access Bytes Block 14 | Read   |

| 16  | 32      | Receive Framer Overhead Access Bytes Block 15 | Read   |

| 17  | 34      | Receive Framer Overhead Access Bytes Block 16 | Read   |

| 18  | 36      |                                               |        |

| 19  | 38      |                                               |        |