# **ASTEC SEMICONDUCTOR** DATA BOOK

#### Disclaimer

ASTEC reserves the right to make changes without further notice to any products described herein to improve reliability, function, or design. ASTEC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others. ASTEC products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify ASTEC of any such intended end use whereupon ASTEC will determine availability and suitability of its products for the intended use. **ASTEC** and the ASTEC logo, *(BSR)* PLC.

| Disclaimer                                                  | i    |

|-------------------------------------------------------------|------|

| Table of Contents                                           | ii   |

| Introduction                                                | iv   |

| General Ordering Information                                | V    |

| Package Marking Information                                 | vi   |

| Alternate Source and Product Cross-Reference                | vii  |

| Product Status Definitions                                  | viii |

| Data Sheets - Title Page                                    |      |

| AS431 Precision Adjustable Shunt Reference                  | 1    |

| AS1431 Precision Adjustable Shunt Reference                 | 9    |

| AS2431 (Preliminary) Precision Adjustable Shunt Reference   | 17   |

| AS432 (Proposed) 1.25V Precision Adjustable Shunt Reference | 25   |

| AS1004 Micropower Precision Reference                       | 28   |

| AS2842/3/4/5 Current Mode Controller                        | 35   |

| AS3842/3/4/5 Current Mode Controller                        | 55   |

| AS2214 (Proposed) Current Mode Controller                   | 75   |

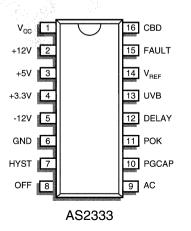

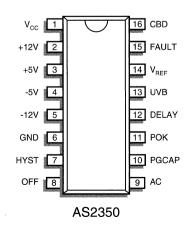

| AS2333/50 (Proposed) Secondary Side Housekeeping Circuit    | 83   |

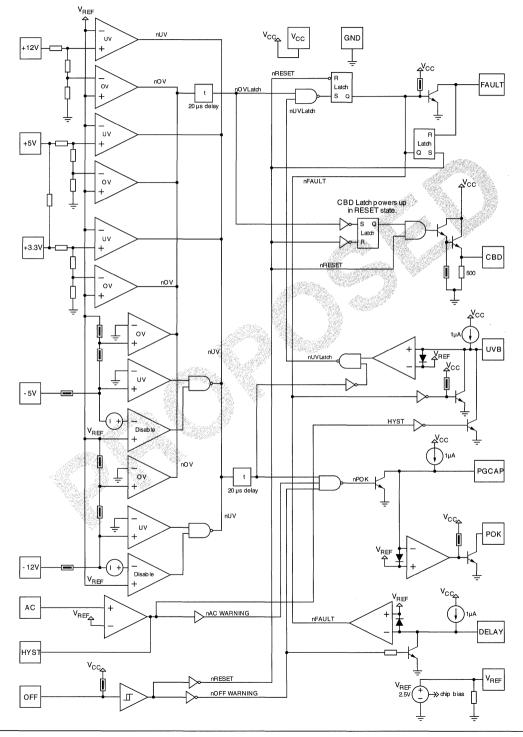

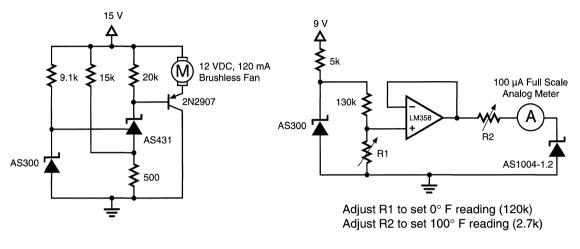

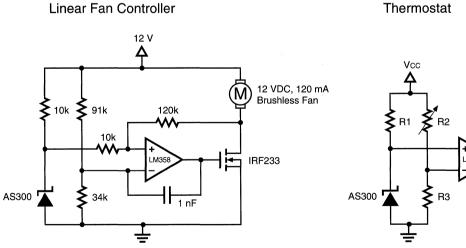

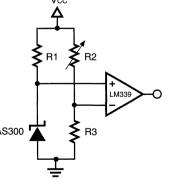

| AS300 Shunt Temperature Sensor                              | 93   |

| AS273 Over-Temperature Detector                             | 99   |

| AS17XX Semi-Custom Bipolar Array                            | 111  |

#### **Application Notes**

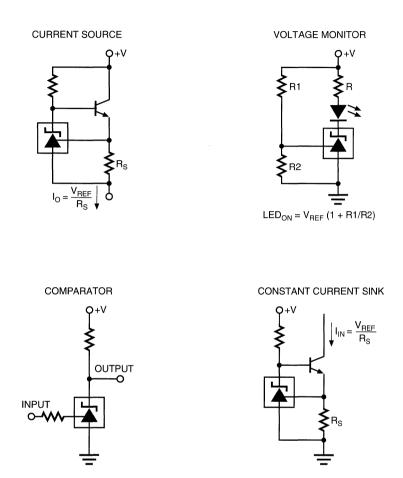

| AN1: AS431 General Application Information               | 133 |

|----------------------------------------------------------|-----|

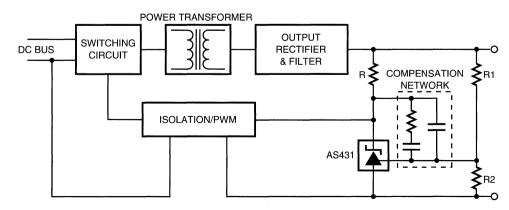

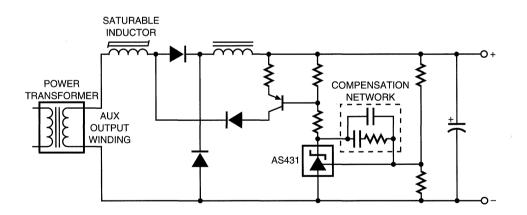

| AN2: Secondary Side Error Amplifier Using the AS431      | 139 |

| AN3: Noise and Stability Considerations Using the AS384X | 143 |

| AN4: AS384X/UC384X Compatibilbity Issues                 | 149 |

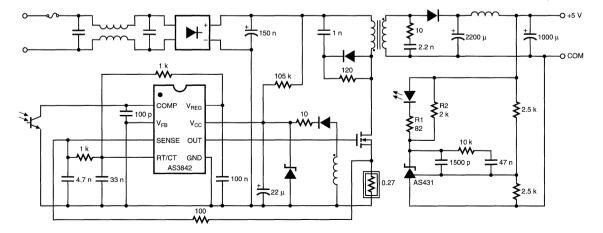

| AN5: Switching Power Supply Control Loop Design (AS3842) | 153 |

|                                                          |     |

#### Appendix

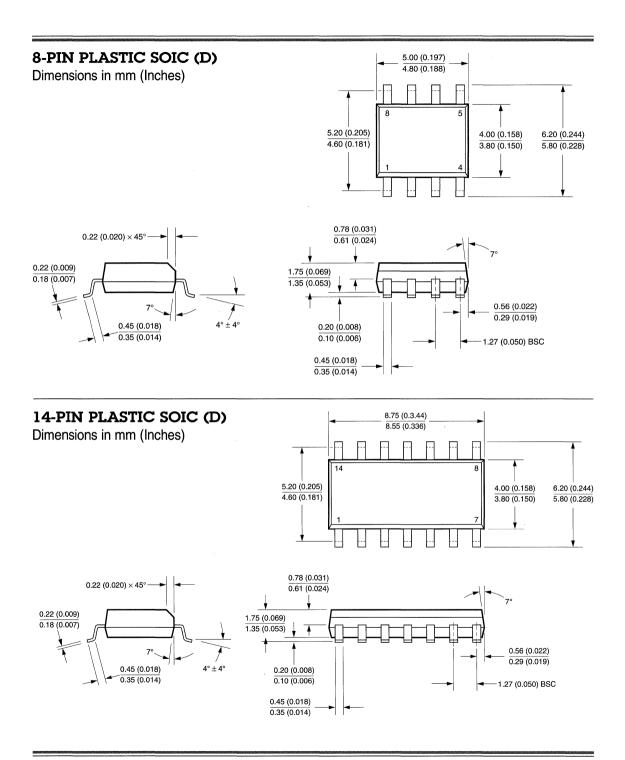

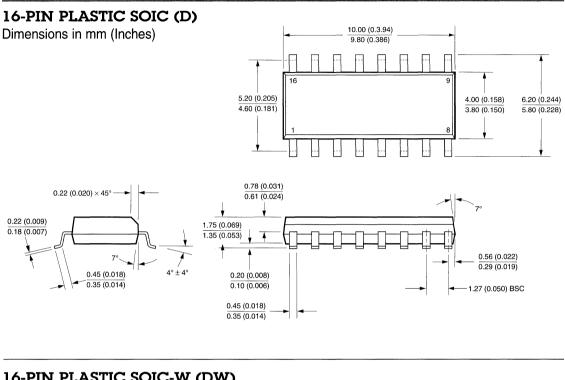

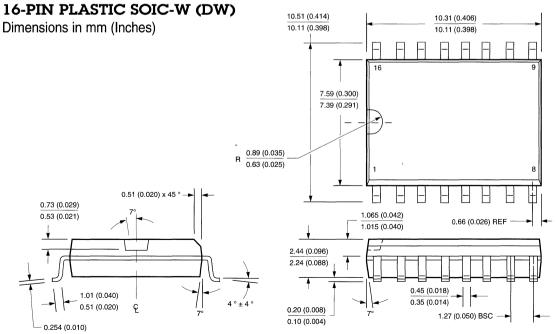

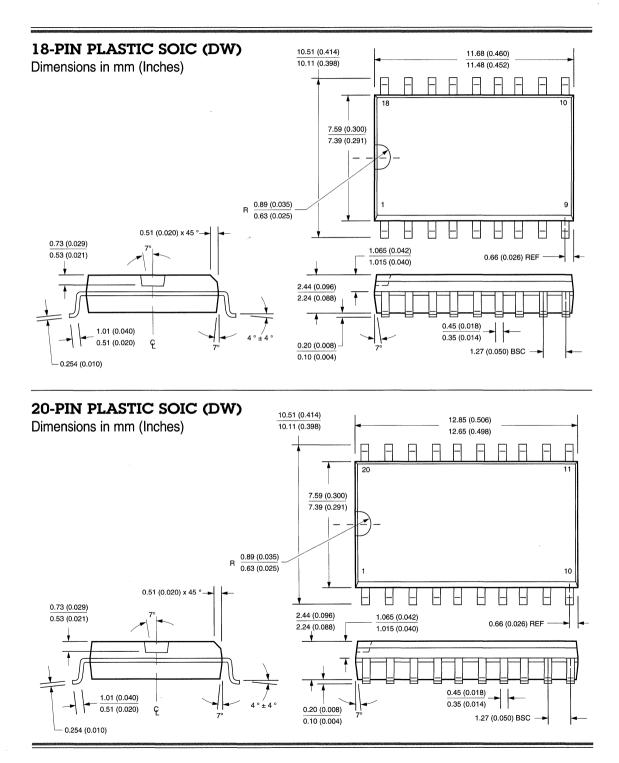

| Package Outline Drawings                  | 165 |

|-------------------------------------------|-----|

| Quality Assurance and Reliability Program | 173 |

Astec Semiconductor Division (ASD) was chartered in 1983 to design and manufacture high quality power management integrated circuits for the Astec family of power supplies.

Extending from this charter, ASD has become power management specialist, developing semiconductor products optimized for the specific need of all customers in power supply, lighting ballast, temperature controllers and consumer electronic applications. Our products are built on modern Bipolar, BiMOS and CMOS technologies. ASD provides their customers products and services built to the highest standards of quality and reliability.

Our goal is to provide quality, technology and predictability in our pursuit of customer satisfaction.

Gene R. Miller President Astec Semiconductor Division

#### **Order Entry**

Products contained within this data book can be ordered from:

Astec Semiconductor 255 Sinclair Frontage Road Milpitas, California 95035 USA Phone: 408-263-8300 Facsimile: 408-263-8340

#### Ordering Information

Minimum engineering order: 50 pieces (product samples available upon request)

Minimum production order: 500 pieces

Each item ordered must appear exactly as listed in the data sheet

F.O.B.: Milpitas, California

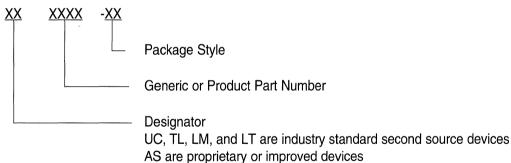

#### Part Number Information

#### Package Suffix Explanation

| Letter Designation | Description                                           |

|--------------------|-------------------------------------------------------|

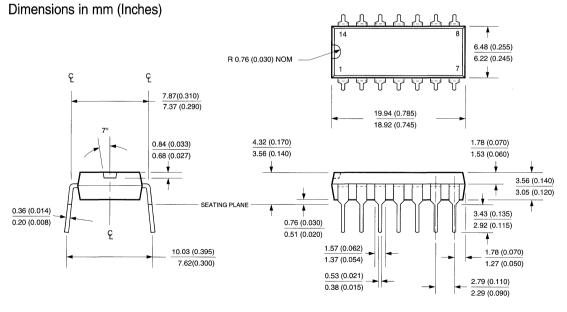

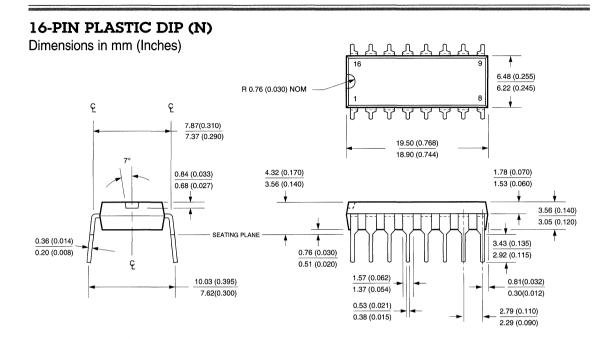

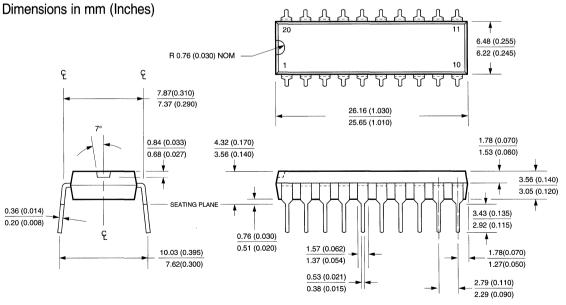

| Ν                  | 8, 14, 16, 18, and 20 Lead Plastic DIP                |

| D                  | 8, 14, and 16 Lead Plastic Narrow Body SOIC           |

| DW                 | 16, 18, and 20 Lead Plastic Wide Body SOIC            |

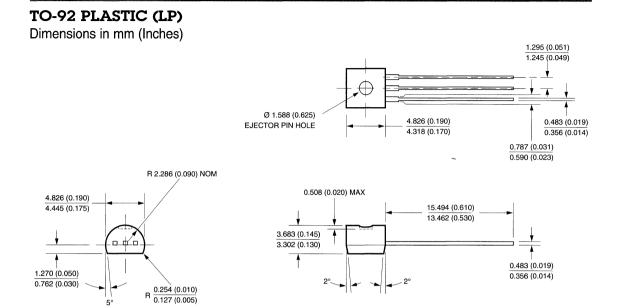

| LP                 | TO-92 Plastic (3 Lead)                                |

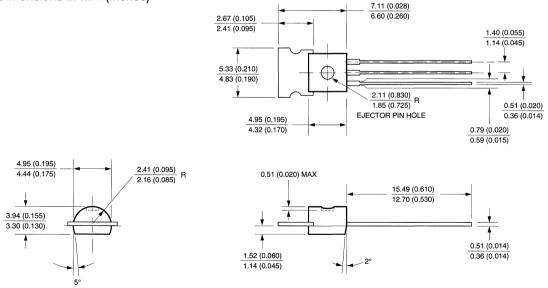

| HP                 | TO-237 Plastic (3 Lead, TO-92 with Top Heat Spreader) |

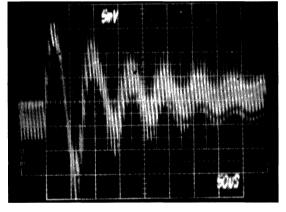

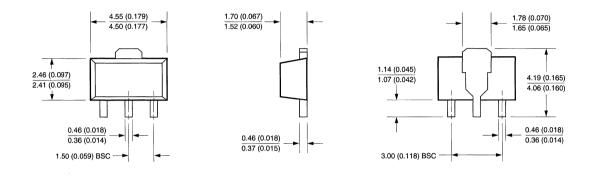

| VS                 | SOT-23 Plastic (3 Lead)                               |

| S                  | SOT-89 Plastic (3 Lead with Heat Spreader)            |

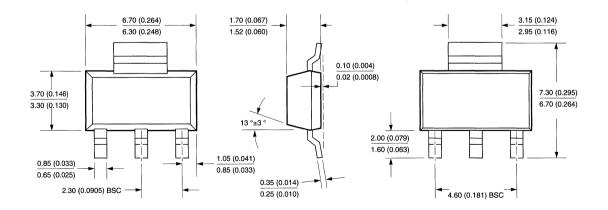

| G                  | SOT-223 Plastic (3 Lead with Heat Spreader)           |

#### Package Marking Explanation

Date Code

Package marking provides a consistent way of identifying product types and managing lot traceability. All Astec products, with the exception of the SOT-23 and SOT-89 packages, are marked with product type, lot number, date code, and country of origin. Each assembly lot in the SOT-23 and SOT-89 packages, receives a unique alpha-numeric code which is recorded in a data base for cross reference to lot number, date code, and country of origin. A complete marking format table is shown below.

|         | 6, 18, and 20                    | TO-92/237 Plastic (3 Lead): |                                   |  |  |

|---------|----------------------------------|-----------------------------|-----------------------------------|--|--|

| Lead P  | astic DIP:                       | Face-                       | Astec Logo                        |  |  |

| Тор-    | Astec Logo                       |                             | Product Name                      |  |  |

|         | Product Name                     |                             | Lot Identificaton Code            |  |  |

|         | Lot Identificaton Code           |                             | Country of Origin                 |  |  |

| Bottom- | Lot Identification Code          |                             | Date Code                         |  |  |

|         | Country of Origin                |                             |                                   |  |  |

|         | Date Code                        | SOT-23                      | Plastic (3 Lead):                 |  |  |

|         |                                  | Тор-                        | Log Book Code                     |  |  |

|         | nd 16 Lead Plastic<br>Body SOIC: |                             |                                   |  |  |

| Тор-    | Product Name                     |                             | Plastic<br>with Heat Spreader):   |  |  |

|         | Lot Identificaton Code           | Top-                        | Product Name                      |  |  |

| Bottom- | Date Code                        | TOP                         | Log Book Code                     |  |  |

|         | Country of Origin                |                             | Log Dook Oode                     |  |  |

|         | and 20 Lead Plastic<br>ody SOIC: |                             | 3 Plastic<br>with Heat Spreader): |  |  |

| Тор-    | Astec Logo                       | 、<br>Тор-                   | Product Name                      |  |  |

|         | Product Name                     |                             | Lot Identificaton Code            |  |  |

|         | Lot Identificaton Code           | Bottom.                     | - Date Code                       |  |  |

| Bottom- | Lot Identification Code          | Donom                       | Country of Origin                 |  |  |

|         | Country of Origin                |                             |                                   |  |  |

### Alternate Source and Product Cross-Reference

| P/N         | ASD Direct<br>Replacement Part | P/N          | ASD Direct<br>Replacement Part        | P/N      | ASD Direct<br>Replacement Part |

|-------------|--------------------------------|--------------|---------------------------------------|----------|--------------------------------|

| Cherry Sem  | niconductor                    | National Ser | miconductor                           | Unitrode |                                |

| CS384XA     | AS384X                         | LM431A       | A431                                  | UC384X   | AS384X                         |

| CS384X      | AS384X                         | LM385-1.2    | AS1004-1.2                            | UC384XA  | AS384X*                        |

|             |                                | LM385-2.5    | AS1004-2.5                            |          |                                |

| Hitachi     |                                |              |                                       |          |                                |

| HA17431     | A431                           | Samsung Se   | emiconductor                          |          |                                |

| HA17384     | AS3842                         | SKA431       | A431                                  |          |                                |

| HA17345     | AS3843                         | KA384X       | AS384X                                |          |                                |

| Linear Tech | ology                          | Texas Instru | iments                                |          |                                |

| LM385-1.2   | AS1004-1.2                     | TL431        | A431                                  |          |                                |

| LM385-2.5   | AS1004-2.5                     | TL431A       | A431                                  |          |                                |

| LT1004-1.2  | AS1004-1.2                     | TL1431       | AS1431                                |          |                                |

| LT1004-2.5  | AS1004-2.5                     | LM385-1.2    | AS1004-1.2                            |          |                                |

| LT1431CZ    | AS1431*                        | LM385-2.5    | AS1004-2.5                            |          |                                |

| LT1242      | AS3842*                        | LT1004-1.2   | AS1004-1.2                            |          |                                |

| LT1243      | AS3843*                        | LT1004-2.5   | AS1004-2.5                            |          |                                |

| LT1244      | AS3844*                        | UC384X       | AS384X                                |          |                                |

| LT1245      | AS3845*                        |              |                                       |          |                                |

| Motorola Se | emiconductor                   |              |                                       |          |                                |

| TL431       | A431                           |              |                                       | -        |                                |

| TL431A      | A431                           |              |                                       |          |                                |

| UC384X      | AS384X                         |              |                                       |          |                                |

| UC384XA     | AS384X                         |              |                                       |          |                                |

|             |                                |              |                                       |          |                                |

|             |                                |              | · · · · · · · · · · · · · · · · · · · |          |                                |

\* Similar Device: Please consult data sheet to determine the suitability of replacement for specific applications

| Data Sheet Identification | Product Status   | Definition                                                                                                                                                                                                                                                        |

|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Proposed                  | In Design        | This data sheet contains the design specifications<br>for product development. These specifications are<br>subject to change. Further information will be pub-<br>lished upon product release.                                                                    |

| Preliminary               | First Production | This data sheet contains preliminary data. Supple-<br>mentary data will be published at a later date. Astec<br>Semiconductor reserves the right to make changes<br>at any time without notice in order to improve<br>design and supply the best product possible. |

| No Identification         | Full Production  | This data sheet contains final specifications and<br>complete typical curves. Astec Semiconductor re-<br>serves the right to make changes at any time without<br>notice in order to improve design and supply the best<br>product possible.                       |

#### **Definition of Terms**

## Data Sheets

#### Notes

#### Features

- Temperature-compensated: 30 ppm/°C

- Trimmed 0.5% bandgap reference

- Internal amplifier with 150 mA capability

- Nominal temperature range extended to 105° C

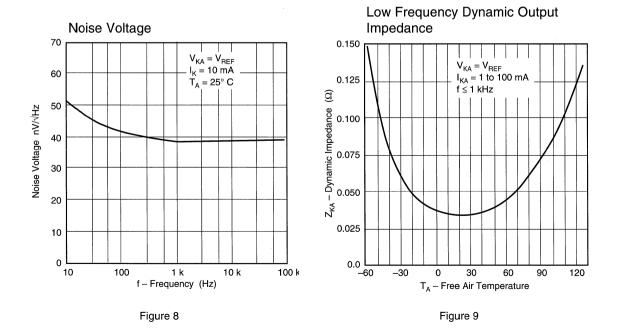

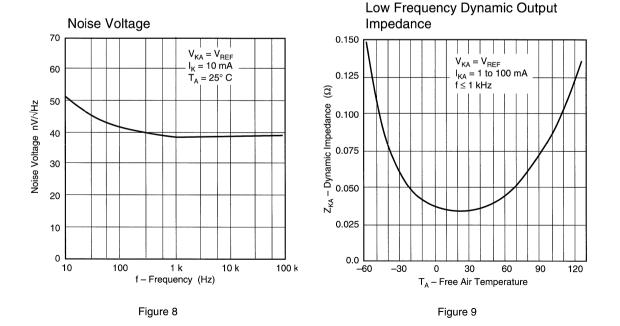

- Low frequency dynamic output impedance: < 150 m

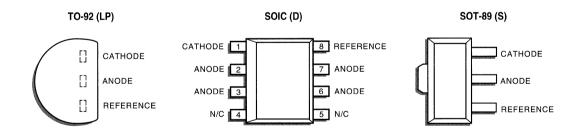

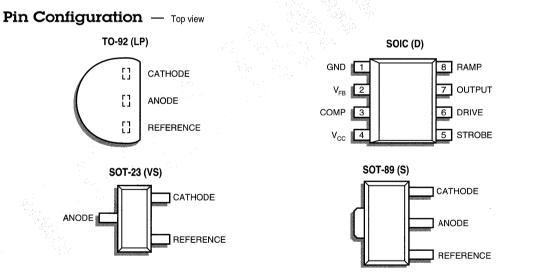

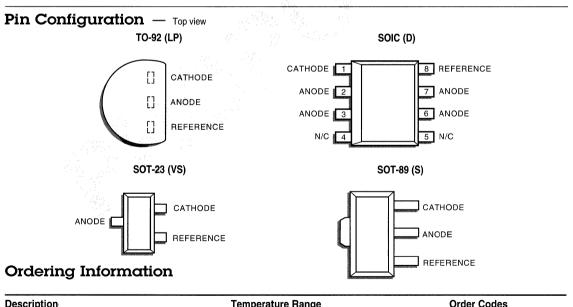

**Pin Configuration** — Top view

- Low output noise

- Robust ESD protection

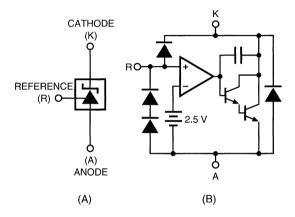

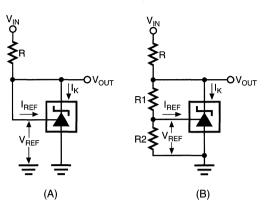

Description

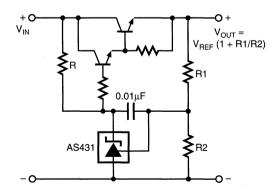

The AS431 is a three-terminal adjustable shunt regulator providing a highly accurate 0.5% bandgap reference. The adjustable shunt regulator is ideal for a wide variety of linear applications that can be implemented using external components to obtain adjustable currents and voltages.

In the standard shunt configuration, the combination of low temperature coefficient (T.C.), sharp turn-on characteristics, low output impedance and programmable output voltage make this precision reference a perfect zener diode replacement.

The A431 regulator is a low-cost solution where a bandgap reference tolerance is not critical. The A431 has a 1% bandgap reference and can be used as a direct replacement for the standard TL431.

#### **Ordering Information**

| Description        | Temperature Range | Order C | odes   |

|--------------------|-------------------|---------|--------|

|                    | -                 | 0.5%    | 1.0%   |

| TO-92              | 0 to 105° C       | AS431LP | A431LP |

| 8-Pin Plastic SOIC | 0 to 105° C       | AS431D  | A431D  |

| SOT-89             | 0 to 105° C       | AS431S  | A431S  |

© ASTEC Semiconductor

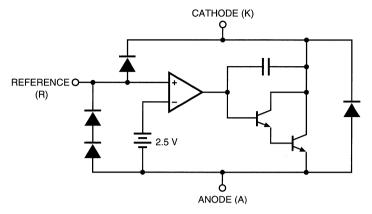

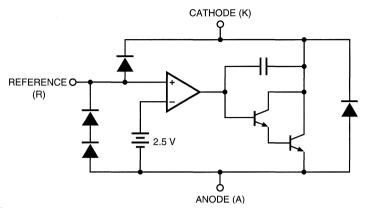

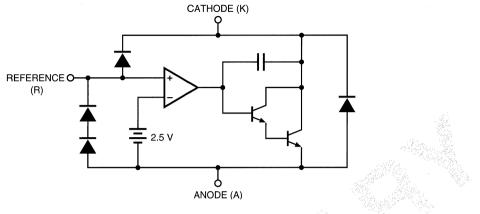

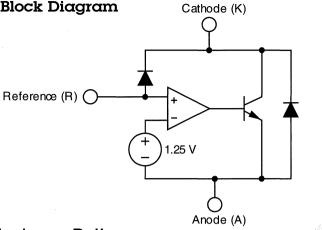

#### Functional Block Diagram

#### **Absolute Maximum Ratings**

| Parameter                              | Symbol           | Rating      | Units |

|----------------------------------------|------------------|-------------|-------|

| Cathode-Anode Reverse Breakdown        | VKA              | 37          | V     |

| Anode-Cathode Forward Current          | I <sub>AK</sub>  | 1           | A     |

| Operating Cathode Current              | IKA              | 250         | mA    |

| Reference Input Current                | I <sub>REF</sub> | 10          | mA    |

| Continuous Power at 25° C              | PD               |             |       |

| TO-92                                  |                  | 775         | mW    |

| 8L SOIC                                |                  | 750         | mW    |

| SOT-89                                 |                  | 1000        | mW    |

| Junction Temperature                   | TJ               | 150         | °C    |

| Storage Temperature                    | T <sub>STG</sub> | – 65 to 150 | °C    |

| Lead Temperature, Soldering 10 Seconds | TL               | 300         | °C    |

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended Conditions**

#### Typical Thermal Resistances

| Parameter       | Symbol | Rating                 | Unit | Package | θја      | θις     | Typical Derating |

|-----------------|--------|------------------------|------|---------|----------|---------|------------------|

| Cathode Voltage | VKA    | $V_{\text{REF}}$ to 20 | V    | TO-92   | 160° C/W | 80° C/W | 6.3 mW/°C        |

| Cathode Current | Iĸ     | 10                     | mA   | SOIC    | 175° C/W | 45° C/W | 5.7 mW/°C        |

|                 |        |                        |      | SOT-89  | 110° C/W | 8° C/W  | 9.1 mW/°C        |

#### **Electrical Characteristics**

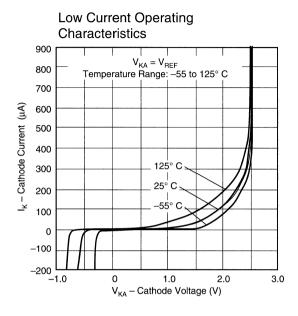

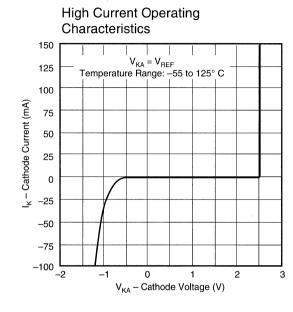

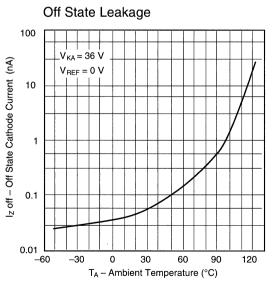

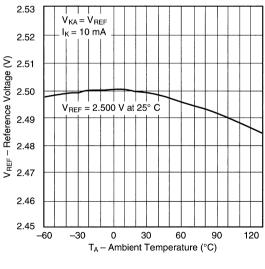

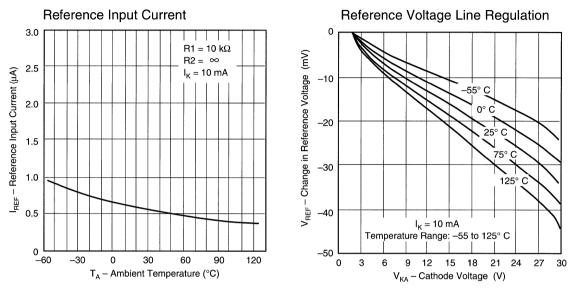

Electrical Characteristics are guaranteed over full junction temperature range (0 to  $105^{\circ}$  C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. The conditions are:  $V_{KA} = V_{REF}$  and  $I_K = 10$  mA unless otherwise stated.

|                                                   |                     | Test                                              | AS431 (0.5%) |       |       | A     | 431 (1.0% | 6)    | Tes     | Test    |

|---------------------------------------------------|---------------------|---------------------------------------------------|--------------|-------|-------|-------|-----------|-------|---------|---------|

| Parameter                                         | Symbol              | Condition                                         | Min          | Тур   | Max   | Min   | Тур       | ́ Мах | Unit    | Circuit |

| Reference Voltage                                 | V <sub>REF</sub>    | $T_A = 25^\circ C$                                | 2.490        | 2.503 | 2.515 | 2.470 | 2.495     | 2.520 | V       | 1       |

|                                                   |                     | Over temp.                                        | 2.469        |       | 2.536 | 2.449 |           | 2.541 | V       | 1       |

| V REF with Temp*                                  | TC                  |                                                   |              | 0.07  | 0.20  |       | 0.07      | 0.20  | mV/ ° C | 1       |

| Ratio of Change in<br>V <sub>BEE</sub> to Cathode | V REF               | V <sub>REF</sub> to 10 V                          | - 2.7        | - 1.0 |       | - 2.7 | -1.0      |       | mV/V    | 2       |

| Voltage                                           | Vĸ                  | 10 V to 36 V                                      | - 2          | - 0.4 | 0.3   | - 2   | - 0.4     | 0.3   |         | 2       |

| Reference Input<br>Current                        | I <sub>REF</sub>    |                                                   |              | 0.7   | 4     |       | 0.7       | 4     | μA      | 2       |

| IREF Temp Deviation                               | I <sub>REF</sub>    | Over temp.                                        |              | 0.4   | 1.2   |       | 0.4       | 1.2   | μA      | 2       |

| Min $I_{K}$ for Regulation                        | I <sub>K(min)</sub> |                                                   |              | 0.4   | 1     |       | 0.4       | 1     | mA      | 1       |

| Off State Leakage                                 | I <sub>K(off)</sub> | V <sub>REF</sub> = 0 V,<br>V <sub>KA</sub> = 36 V |              | 0.04  | 250   |       | 0.04      | 250   | nA      | 3       |

| Dynamic Output<br>Impedance                       | Z <sub>KA</sub>     | f 1 kHz<br>I <sub>K</sub> = 1 to 150 mA           |              | 0.15  | 0.5   |       | 0.15      | 0.5   | Ω       | 1       |

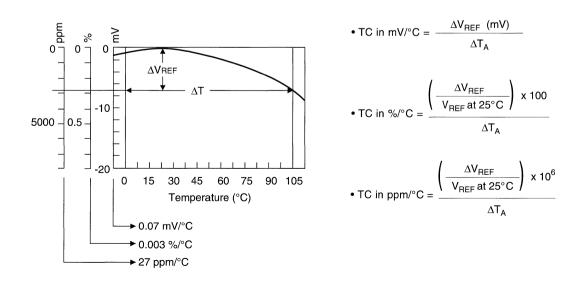

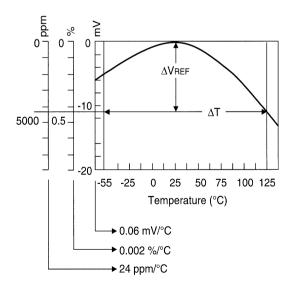

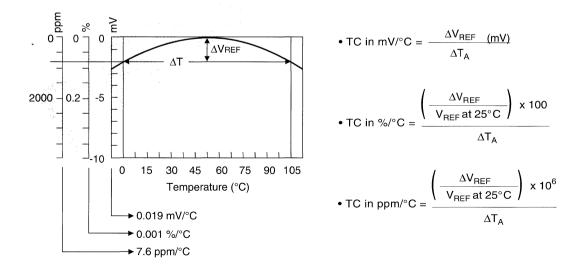

\*Calculating Average Temperature Coefficient (TC)

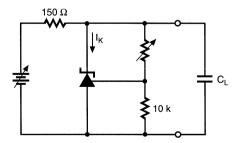

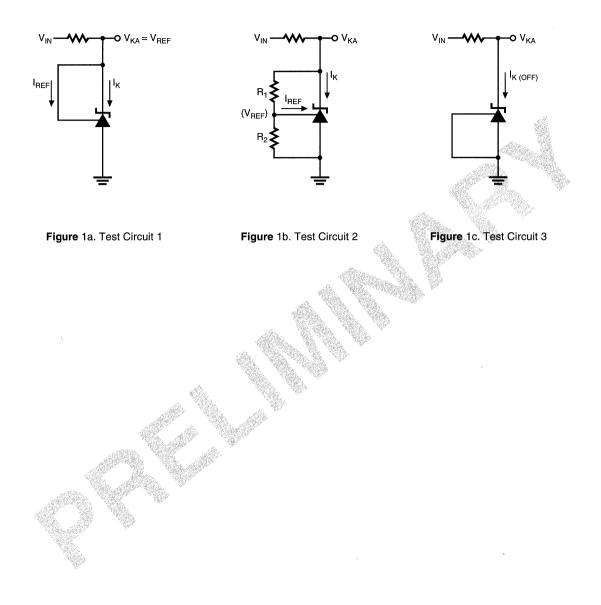

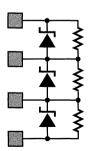

#### **Test Circuits**

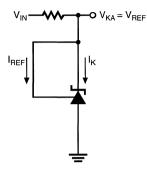

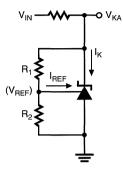

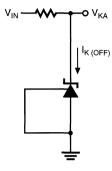

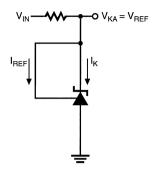

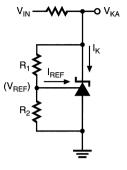

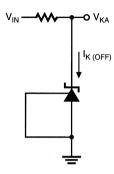

Figure 1a. Test Circuit 1

Figure 1b. Test Circuit 2

Figure 1c. Test Circuit 3

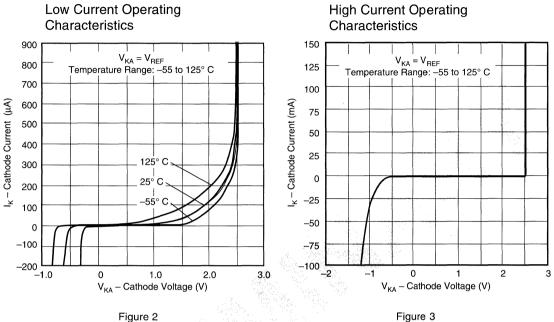

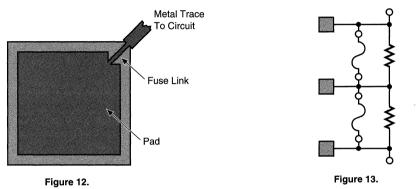

Figure 2

Figure 3

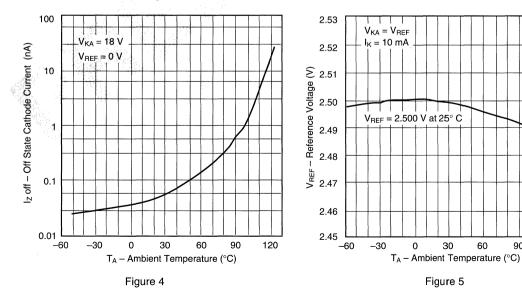

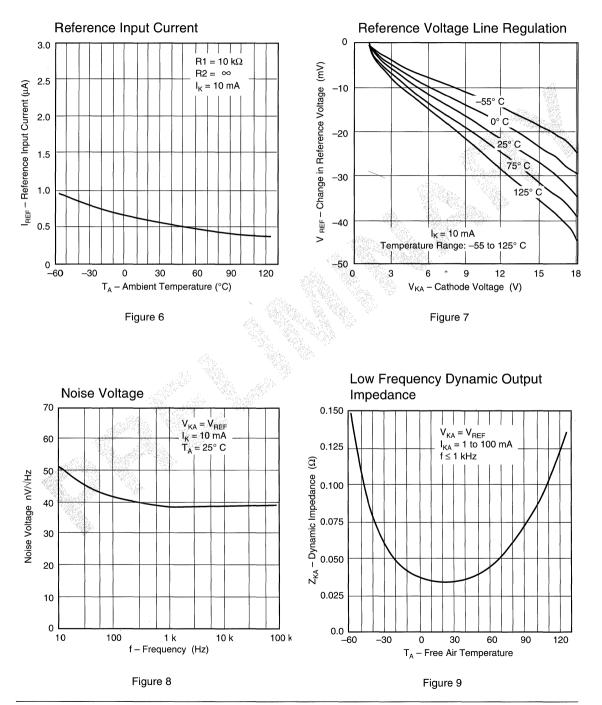

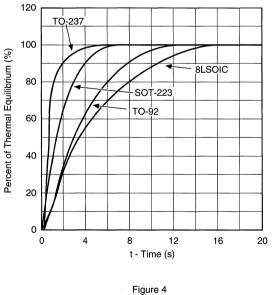

Figure 4

Temperature Coefficient as a Function of Trim Value

Figure 5

Figure 6

ASTEC Semiconductor

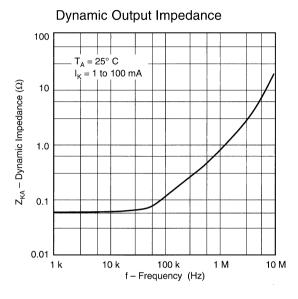

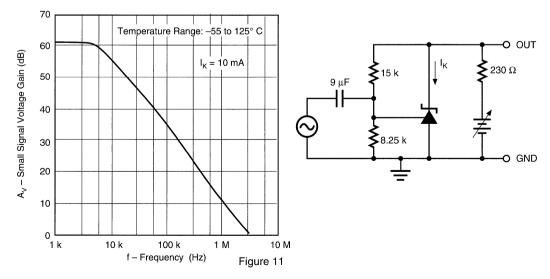

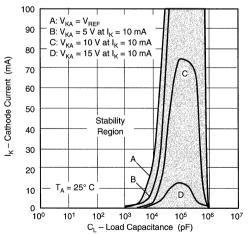

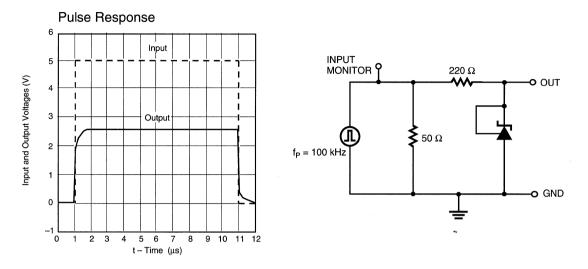

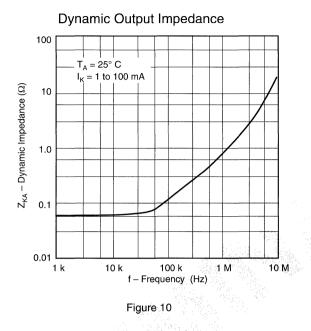

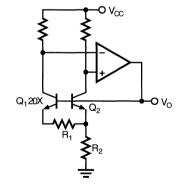

Figure 10

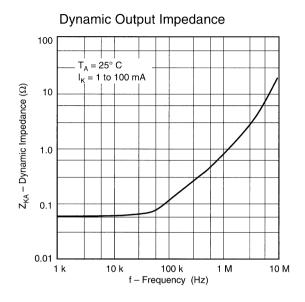

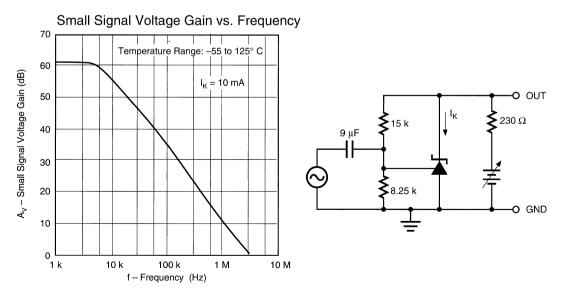

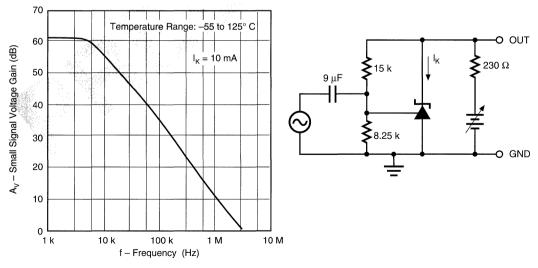

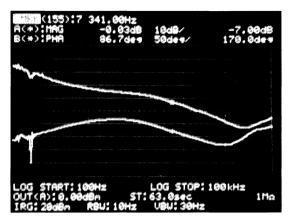

Small Signal Voltage Gain vs. Frequency

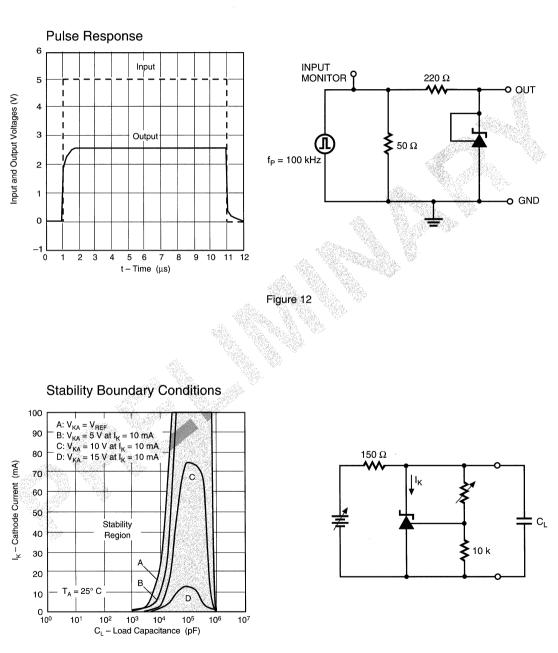

Figure 12

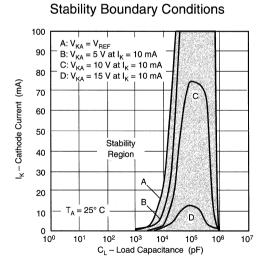

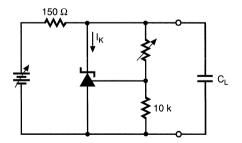

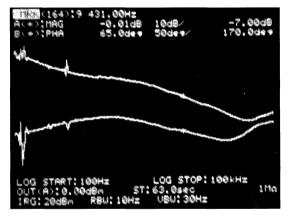

**Stability Boundary Conditions**

Figure 13

#### Features

- Temperature-compensated: 30 ppm/°C

- Trimmed 0.4% bandgap reference

- Internal amplifier with 150 mA capability

- Temperature range: Extended to -55 to125° C

- Low frequency dynamic output impedance: < 150 m

- Low output noise

- Robust ESD protection

#### Description

The AS1431 is a three-terminal adjustable shunt regulator providing a highly accurate 0.4% bandgap reference. The adjustable shunt regulator is ideal for a wide variety of linear applications that can be implemented using external components to obtain adjustable currents and voltages.

In the standard shunt configuration, the combination of low temperature coefficient (T.C.), sharp turn-on characteristics, low output impedance and programmable output voltage make this precision reference a perfect zener diode replacement .

The AS1431 is characterized to operate over the full automotive temperature range of -55 to  $125^{\circ}$  C and is now available in the SOT-89 package.

#### Pin Configuration — Top view

TO-92 (LP) SOIC (D) SOT-89 (S) CATHODE 1 8 REFERENCE CATHODE [] CATHODE ANODE 2 7 ANODE [] ANODE ANODE 6 ANODE ANODE 3 [] REFERENCE N/C 4 5 N/C REFERENCE

#### **Ordering Information**

| Description        | Temperature Range | Order Codes |  |

|--------------------|-------------------|-------------|--|

| TO-92              | -55 to 125° C     | AS1431LP    |  |

| 8-Pin Plastic SOIC | -55 to 125° C     | AS1431D     |  |

| SOT-89             | -55 to 125° C     | AS1431S     |  |

© ASTEC Semiconductor

#### Functional Block Diagram

#### **Absolute Maximum Ratings**

| Parameter                             | Symbol           | Rating      | Units |

|---------------------------------------|------------------|-------------|-------|

| Cathode-Anode Reverse Breakdown       | Vĸa              | 37          | V     |

| Anode-Cathode Forward Current         | I <sub>AK</sub>  | 1           | A     |

| Operating Cathode Current             | IKA              | 250         | mA    |

| Reference Input Current               | I <sub>REF</sub> | 10          | mA    |

| Continuous Power Dissipation at 25° C | PD               |             |       |

| TO-92                                 |                  | 775         | mW    |

| 8L SOIC                               |                  | 750         | mW    |

| SOT-89                                |                  | 1000        | mW    |

| Junction Temperature                  | TJ               | 150         | °C    |

| Storage Temperature                   | T <sub>STG</sub> | – 65 to 150 | °C    |

| Lead Temperature Soldering 10 Seconds | TL               | 300         | °C    |

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended Conditions**

#### **Typical Thermal Resistances**

| Parameter       | Symbol          | Rating                 | Unit | Package | $\theta_{JA}$ | θις     | Typical Derating |

|-----------------|-----------------|------------------------|------|---------|---------------|---------|------------------|

| Cathode Voltage | V <sub>KA</sub> | V <sub>REF</sub> to 20 | ٧    | TO-92   | 160° C/W      | 80° C/W | 6.3 mW/°C        |

| Cathode Current | Ιĸ              | 10                     | mA   | SOIC    | 175° C/W      | 45° C/W | 5.7 mW/°C        |

|                 |                 |                        |      | SOT-89  | 110° C/W      | 8° C/W  | 9.1 mW/°C        |

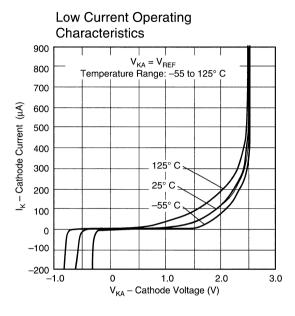

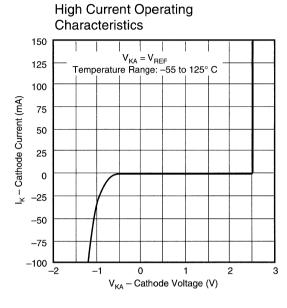

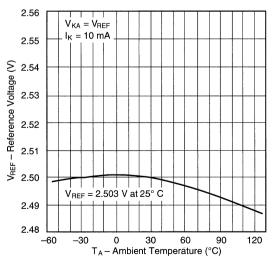

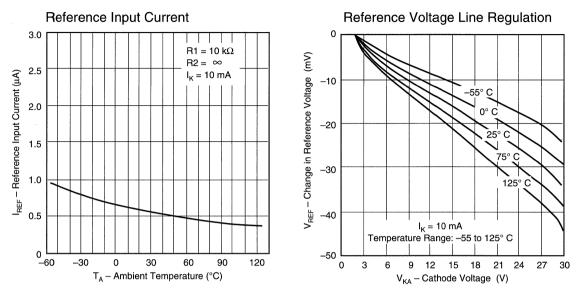

#### **Electrical Characteristics**

Electrical Characteristics are guaranteed over full junction temperature range (-55 to 125° C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. The conditions are: V<sub>KA</sub> = V<sub>REF</sub> and I<sub>K</sub> = 10 mA unless otherwise stated.

| Parameter                                              | Symbol              | Test Condition                                    | Min   | Тур   | Max   | Unit    | Circuit |

|--------------------------------------------------------|---------------------|---------------------------------------------------|-------|-------|-------|---------|---------|

| Reference Voltage                                      | V <sub>REF</sub>    | $T_A = 25^\circ C$                                | 2.490 | 2.500 | 2.510 | V       | 1       |

|                                                        |                     | Over temp.                                        | 2.470 |       | 2.530 | V       | 1       |

| V REF with Temp*                                       | TC                  |                                                   |       | 0.06  | 0.16  | mV/ ° C | 1       |

| Ratio of Change in V <sub>REF</sub> to Cathode Voltage | V <sub>REF</sub>    | V $_{\rm K}$ = 3 V to 36 V                        | -2    | - 1.1 |       | mV/V    | 2       |

| Reference Input Current                                | I <sub>REF</sub>    | $R_1 = 10 \ k$ ; $R_2 =$                          |       | 0.7   | 1.9   | μA      | 2       |

| IREF Temp Deviation                                    | I <sub>REF</sub>    | Over temp.                                        |       | 0.4   | 1.2   | μA      | 2       |

| Min I <sub>K</sub> for Regulation                      | I <sub>K(min)</sub> |                                                   |       | 0.4   | 1     | mA      | 1       |

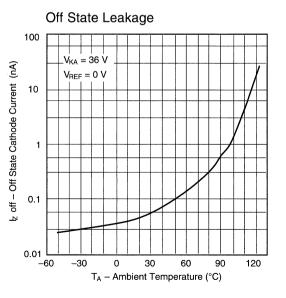

| Off State Leakage                                      | I <sub>K(off)</sub> | V <sub>REF</sub> = 0 V,<br>V <sub>KA</sub> = 36 V |       | 0.04  | 500   | nA      | 3       |

| Dynamic Output Impedance                               | Z <sub>KA</sub>     | f 1 kHz I <sub>K</sub> = 1 to100 mA               |       | 0.15  | 0.2   | Ω       | 1       |

\*Calculating Average Temperature Coefficient (TC)

• TC in mV/°C =

$$\frac{\Delta V_{\text{REF}} \text{ (mV)}}{\Delta T_{\text{A}}}$$

....

• TC in %/°C =

$$\frac{\left(\frac{\Delta T_{HEF}}{V_{REF} \text{ at } 25^{\circ}\text{C}}\right) \times 100}{\Delta T_{A}}$$

• TC in ppm/°C =

$$\frac{\left(\frac{\Delta V_{REF}}{V_{REF} \text{ at } 25^{\circ}\text{C}}\right) \text{ x } 10^{6}}{\Delta T_{A}}$$

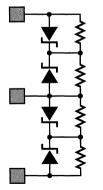

#### **Test Circuits**

Figure 1a. Test Circuit 1

Figure 1b. Test Circuit 2

Figure 1c. Test Circuit 3

Figure 2

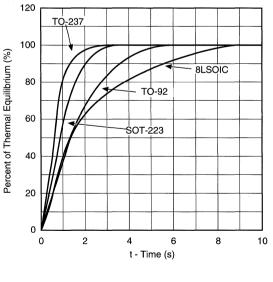

Figure 4

Reference Voltage vs Ambient Temperature

Figure 5

Figure 6

Figure 10

Figure 11

Figure 12

#### AS2431 Precision Adjustable Shunt Reference Preliminary Specification

#### Features

- Temperature-compensated: 15 ppm/°C

- Trimmed 0.5% bandgap reference

- Internal amplifier with 100 mA capability

- Temperature range: Extended to 0 t o 105° C

- Low frequency dynamic output impedance: < 150 m

- Low output noise

#### Description

The AS2431 is a three-terminal adjustable shunt regulator providing a highly accurate 0.5% bandgap reference. The adjustable shunt regulator is ideal for a wide variety of linear applications that can be implemented using external components to obtain adjustable currents and voltages.

In the standard shunt configuration, the combination of low temperature coefficient (T.C.), sharp turn-on characteristics, low output impedance and programmable output voltage make this precision reference an excellent error amplifier.

The AS2431 is a direct replacement for the AS431 in low voltage, low current applications. It is also available in the very small footprint SOT-23.

#### Ordering Information

| Description        | Temperature Range | Order Codes |  |

|--------------------|-------------------|-------------|--|

| TO-92              | 0 to 105° C       | AS2431LP    |  |

| 8-Pin Plastic SOIC | 0 to 105° C       | AS2431D     |  |

| 60T-23 0 to 105° C |                   | AS2431VS    |  |

| SOT-89 (S)         | 0 to 105° C       | AS2431S     |  |

#### Functional Block Diagram

#### Absolute Maximum Ratings

| Parameter                             | Symbol           | Rating     | Units |

|---------------------------------------|------------------|------------|-------|

| Cathode-Anode Reverse Breakdown       | V <sub>KA</sub>  | 18         | V     |

| Anode-Cathode Forward Current         | lak              | 1          | A     |

| Operating Cathode Current             | IKA              | 100        | mA    |

| Reference Input Current               | IREF             | 1          | mA    |

| Continuous Power Dissipation at 25° C | PD               |            |       |

| TO-92                                 |                  | 775        | mW    |

| 8L SOIC                               |                  | 750        | mW    |

| SOT-23                                |                  | 200        | mW    |

| SOT-89                                |                  | 1000       | mW    |

| Junction Temperature                  | TJ               | 150        | °C    |

| Storage Temperature                   | T <sub>STG</sub> | -65 to 150 | °C    |

| Lead Temp, Soldering 10 Seconds       | TL               | 300        | °C    |

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended Conditions**

#### **Typical Thermal Resistances**

| Parameter       | Symbol          | Rating                 | Unit | Package | θja      | θ」c      | Typical Derating |

|-----------------|-----------------|------------------------|------|---------|----------|----------|------------------|

| Cathode Voltage | V <sub>KA</sub> | $V_{\text{REF}}$ to 18 | ۷    | TO-92   | 160° C/W | 80° C/W  | 6.3 mW/°C        |

| Cathode Current | Ιĸ              | 10                     | mA   | SOIC    | 175° C/W | 45° C/W  | 5.7 mW/°C        |

|                 |                 |                        |      | SOT-23  | 575°C/W  | 150° C/W | 1.7 mW/°C        |

|                 |                 |                        |      | SOT-89  | 110° C/W | 8° C/W   | 9.1 mW°C         |

#### **Electrical Characteristics**

Electrical Characteristics are guaranteed over full junction temperature range (0 to  $105^{\circ}$  C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. The conditions are:  $V_{KA} = V_{REF}$  and  $I_K = 10$  mA unless otherwise stated.

| Parameter                                              | Symbol              | Test Condition                                    | Min        | Тур    | Max   | Unit    | Circuit |

|--------------------------------------------------------|---------------------|---------------------------------------------------|------------|--------|-------|---------|---------|

| Reference Voltage                                      | V <sub>REF</sub>    | $T_A = 25^\circ C$                                | 2.490      | 2.500  | 2.510 | V       | 1       |

|                                                        | -                   | Over temp.                                        | 2.480      |        | 2.530 | V       | 1       |

| $\Delta V_{\text{REF}}$ with Temp*                     | тс                  |                                                   |            | 0.02   | 0.06  | mV/ ° C | 1       |

| Ratio of Change in V <sub>REF</sub> to Cathode Voltage | $\Delta V_{REF}$    | V <sub>REF</sub> to 10 V                          | - 2.7      | - 1.01 |       |         |         |

|                                                        | ΔV <sub>K</sub>     | 10V to 18 V                                       | - 2        | - 0.4  | 0.3   | mV/V    | 2       |

| Reference Input Current                                | I <sub>REF</sub>    |                                                   |            | 0.7    | 4     | μΑ      | 2       |

| IREF Temp Deviation                                    | $\Delta I_{REF}$    | Over temp.                                        |            | 0.4    | 1.2   | μA      | 2       |

| Min $I_{K}$ for Regulation                             | I <sub>K(min)</sub> |                                                   |            | 0.4    | 1     | mA      | 1       |

| Off State Leakage                                      | I <sub>K(off)</sub> | V <sub>REF</sub> = 0 V,<br>V <sub>KA</sub> = 18 V |            | 0.04   | 500   | nA      | 3       |

| Dynamic Output Impedance                               | Z <sub>KA</sub>     | $f \le 1 \text{ kHz } I_{K} = 1 \text{ to100 mA}$ | 1997 - BAR | 0.15   | 0.5   | Ω       | 1       |

\*Calculating Average Temperature Coefficient (TC)

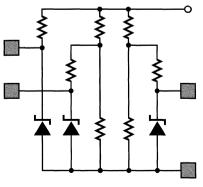

#### **Test Circuits**

#### **Typical Performance**

Off State Leakage

60

90

120

ASTEC Semiconductor

#### Small Signal Voltage Gain vs. Frequency

Figure 11

Figure 13

AS432 1.25 V Precision Adjustable Shunt Reference / Amplifier Proposed Specification

#### Features

- Temperature-compensated: 50 ppm/°C

- Trimmed 0.5% bandgap reference

- Internal amplifier with 150 mA capability

- Nominal temperature range extended to 105° C

- Low frequency dynamic output impedance: < 150 m

- Low output noise

#### Description

The AS432 is a three terminal adjustable shunt regulator utilizing an accurate 1.25V bandgap reference. The AS432 is functionally similar to an AS431 except for its lower reference voltage, making it usable in a wide variety of low voltage applications.

Because of its robust bipolar technology, the AS432 handles a wide range of current, and holds off more than 18V so its use is not limited to low power, low voltage systems. Significant care has been taken to provide adequate AC bandwidth to allow the AS432 as an amplifier in control systems and power electronics.

| Description        | Temperature Range | Order Codes |

|--------------------|-------------------|-------------|

| TO-92              | 0 to 105° C       | AS432LP     |

| 8-Pin Plastic SOIC | 0 to 105° C       | AS432D      |

| SOT - 89           | 0 to 105° C       | AS432S      |

| SOT - 23           | 0 to 105° C       | AS432VS     |

|                    |                   |             |

© ASTEC Semiconductor

# Functional Block Diagram

# Absolute Maximum Ratings

| Parameter                            | Symbol           | Rating      | Units |

|--------------------------------------|------------------|-------------|-------|

| Cathode-Anode Reverse Breakdown      | V <sub>KA</sub>  | 18          | V     |

| Anode-Cathode Forward Current        | I <sub>AK</sub>  | 1           | А     |

| Operating Cathode Current            | lka              | 100         | mA    |

| Reference Input Current              | IREF             | 1           | mA    |

| Continuous Power at 25° C            | PD               |             |       |

| TO-92                                |                  | 775         | mW    |

| 8L SOIC                              |                  | 750         | mW    |

| SOT-89                               | S.               | 1000        | mW    |

| SOT-23                               |                  | 200         | mW    |

| Junction Temperature                 | TJ               | 150         | °C    |

| Storage Temperature                  | T <sub>STG</sub> | – 65 to 150 | °C    |

| Lead Temperature (Soldering 10 sec.) | TL               | 300         | °C    |

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Recommended Conditions**

# **Typical Thermal Resistances**

| Parameter       | Symbol          | Rating                 | Unit | Package | θја      | θυς      | Typical Derating |

|-----------------|-----------------|------------------------|------|---------|----------|----------|------------------|

| Cathode Voltage | V <sub>KA</sub> | $V_{\text{REF}}$ to 18 | V    | TO-92   | 160° C/W | 80° C/W  | 6.3 mW/°C        |

| Cathode Current | ١ĸ              | 10                     | mA   | SOIC    | 175° C/W | 45° C/W  | 5.7 mW/°C        |

|                 |                 |                        |      | SOT-89  | 110° C/W | 8° C/W   | 9.1 mW/°C        |

|                 |                 |                        |      | SOT-23  | 575° C/W | 150° C/W | 1.7 mW/°C        |

# **Electrical Characteristics**

Electrical characteristics are guaranteed over the full junction temperature range (0-105 °C). Ambient temperature must be derated based upon power dissipation and package thermal characteristics. Unless otherwise stated, test conditions are: VKA= VREF and IK=10 mA.

| Parameter                                          | Symbol               | Test Condition                                                          | Min   | Тур   | Max   | Unit |

|----------------------------------------------------|----------------------|-------------------------------------------------------------------------|-------|-------|-------|------|

| Output Voltage                                     | V <sub>REF</sub>     | $I_{\rm K}{=}1~0~mA,~T_{\rm J}{=}25^\circ$ C, $V_{\rm K}{=}V_{\rm REF}$ | 1.244 | 1.250 | 1.256 | v    |

| Line Regulation                                    | V <sub>REF</sub>     | V <sub>KA</sub> = 1.25 to 15 V                                          |       | 10    | 15    | mV   |

| Load Regulation                                    | V <sub>REF</sub>     | I <sub>K</sub> = 1 to 100 mA                                            |       | 3     | 6     | mV   |

| Temperature Deviation                              | V <sub>REF</sub>     | 0 < T <sub>J</sub> < 105° C                                             |       | 2     | 6     | mV   |

| Reference Input Current                            | I <sub>REF</sub>     |                                                                         |       | 3     | 6     | μA   |

| Reference Input Current<br>Temperature Coefficient | I <sub>REF</sub>     | 0 < T <sub>J</sub> < 105 °C                                             |       | 0.3   | 0.6   | μA   |

| Minimum Cathode Current for Regulation             | I <sub>K (MIN)</sub> |                                                                         |       | 0.6   | 1     | mA   |

| Off State Leakage                                  | IK (MIN)             | V <sub>REF</sub> = 0 V, V <sub>KA</sub> = 18 V                          |       | 0.04  | 500   | nA   |

\*Temperature deviation is defined as the maximum deviation of the reference over the given temperature range and does not imply an incremental deviation at any given temperature.

# Typical Performance Curves

# Not Available at Time of Publishing

ASTEC reserves the right to make changes without further notice to any products described herein to improve reliability, function, or design. ASTEC does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others. ASTEC products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify ASTEC of any such intended end use whereupon ASTEC will determine availability and suitability of its products for the intended use. ASTEC and the ASTEC logo are trademarks of ASTEC (BSR) PLC.

# ASTEC SEMICONDUCTOR

255 Sinclair Frontage Road • Milpitas, California 95035 • Tel. (408) 263-8300 • FAX (408) 263-8340

Notes

# Features

- Low voltage reference

- 10 μA turn-on current for AS1004-1.2

- 20 μA turn-on current for AS1004-2.5

- ±4 mV (0.3 %) initial accuracy for AS1004-1.2

- ± 20 mV (0.8 %) initial accuracy for AS1004-2.5

- Guaranteed operation to 20 mA. Over three orders of magnitude of operating current!

- Temperature performance guaranteed

- Very low dynamic impedance

# Description

The AS1004 is a two-terminal precision band-gap voltage reference with a low turn-on current of 10  $\mu A.$

Emulating a 1.235 V zener diode, the AS1004 operates more than three orders of magnitude of output current with minute output impedance and guaranteed stability. With an initial tolerance of  $\pm 4$  mV and guaranteed temperature performance, it is ideal for precision instrumentation, especially in low power applications. Being a low-voltage reference, the AS1004 is also well-suited as a reference for low-voltage power supply applications, especially in power supplies intended for low-voltage logic systems, laptop computers and other portable or battery operated equipment.

The AS1004 is pin-for-pin compatible with the LT1004 and the LM385 and offers improved specifications over both the LM385 and the MP5010. It is also available as a 2.5 V reference with a guaranteed start-up current of 20  $\mu$ A.

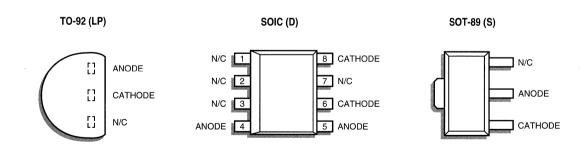

#### **Pin Configuration** — Top view

# **Ordering Information**

| Description        | Temperature Range | Order        | Codes        |

|--------------------|-------------------|--------------|--------------|

| TO-92              | 0 to 70° C        | AS1004-1.2LP | AS1004-2.5LP |

| 8-Pin Plastic SOIC | 0 to 70° C        | AS1004-1.2D  | AS1004-2.5D  |

| SOT-89             | 0 to 70° C        | AS1004-1.2S  | AS1004-2.5S  |

© ASTEC Semiconductor

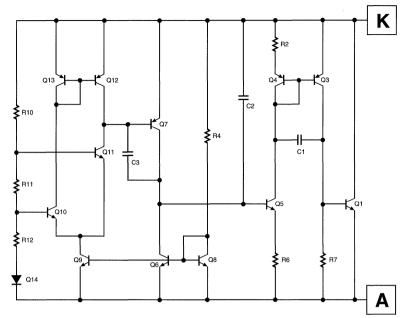

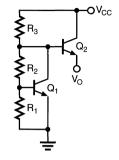

# Simplified Schematic

# **Absolute Maximum Ratings**

| Parameter                              | Symbol           | Rating     | Units |  |

|----------------------------------------|------------------|------------|-------|--|

| Reverse Breakdown Current              | Iz               | 30         | mA    |  |

| Forward Current                        | l <sub>F</sub>   | 30         | mA    |  |

| Continuous Power Dissipation at 25° C  | PD               |            |       |  |

| TO-92                                  |                  | 775        | mW    |  |

| 8LSOIC                                 |                  | 750        | mW    |  |

| SOT-89                                 |                  | 1000       | mW    |  |

| Maximum Junction Temp                  | TJ               | 150        | °C    |  |

| Storage Temperature                    | T <sub>STG</sub> | -65 to 150 | ℃     |  |

| Lead Temperature, Soldering 10 Seconds | TL               | 300        | °C    |  |

# **Recommended Conditions**

# Typical Thermal Resistances

| Parameter       | Symbol | Rating | Unit | Package | θја      | θյς     | Typical Derating |

|-----------------|--------|--------|------|---------|----------|---------|------------------|

| Cathode Current | Iz     | 100    | μA   | TO-92   | 160° C/W | 80° C/W | 6.3 mW/°C        |

|                 |        |        |      | 8L SOIC | 175° C/W | 45° C/W | 5.7 mW/°C        |

|                 |        |        |      | SOT-89  | 110° C/W | 8° C/W  | 9.1 mW/°C        |

# **Electrical Characteristics**

Electrical Characteristics are guaranteed over full junction temperature range (0 to 70° C). Ambient temperature must be derated based on power dissipation and package thermal characteristics.

|                                    |                           | A                                        | S1004-1. | 2     | A     | S1004-2 | .5    |       |        |

|------------------------------------|---------------------------|------------------------------------------|----------|-------|-------|---------|-------|-------|--------|

| Parameter                          | Symbol                    | Test Condition                           | Min      | Тур   | Max   | Min     | Тур   | Мах   | Unit   |

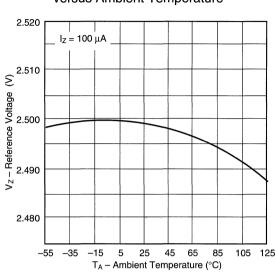

| Reverse Breakdown Voltage          | Vz                        | $I_Z=100~\mu\text{A},~T_J=25^\circ~C$    | 1.231    | 1.235 | 1.239 | 2.480   | 2.500 | 2.520 | V      |

|                                    |                           | $0^\circC \le T_A \le 70^\circC$         | 1.225    | 1.235 | 1.245 | 2.470   | 2.500 | 2.530 | V      |

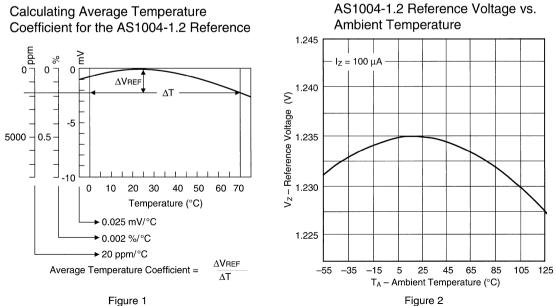

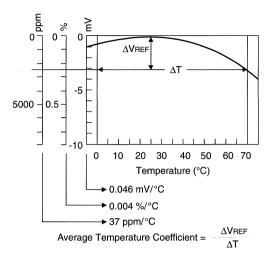

| Average Temperature<br>Coefficient | $\Delta V_Z / \Delta T$   | $I_{min} \le I_Z \le 20 \text{ mA}$      |          | 20    |       |         | 60    |       | ppm/°C |

| Minimum Operating Current          | I <sub>Z (min)</sub>      |                                          |          | 4     | 10    |         | 12    | 20    | μA     |

| Reverse Breakdown Voltage          | $\Delta V_Z / \Delta I_Z$ | $I_{min} \leq I_Z \leq 1 \ mA$           |          | 0.5   | 1     |         | 0.5   | 1     | mV     |

| Change With Current                |                           | Over Temperature                         |          | 0.5   | 1.5   |         | 0.5   | 1.5   | mV     |

|                                    |                           | $1 \text{ mA} \le I_Z \le 20 \text{ mA}$ |          | 6.5   | 10    |         | 6.5   | 10    | mV     |

|                                    |                           | Over Temperature                         |          | 6.5   | 20    |         | 6.5   | 20    | mV     |

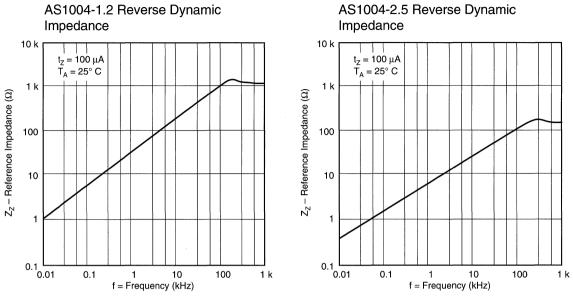

| Reverse Dynamic Impedance          | Zz                        | I <sub>Z</sub> = 100 mA, f = 25 Hz       |          | 0.2   | 0.6   |         | 0.8   | 0.9   | Ω      |

|                                    |                           | Over Temperature                         |          | 1     | 1.5   |         |       | 1.5   | Ω      |

| Wide Band Noise                    | en                        | Iz = 100 μA<br>10 Hz ≤ f ≤ 10 KHz        |          | 60    |       |         | 60    |       | μV     |

| Long Term Stability                | $\Delta V_Z / \Delta T$   |                                          |          | 20    |       |         | 60    |       | ppm/kH |

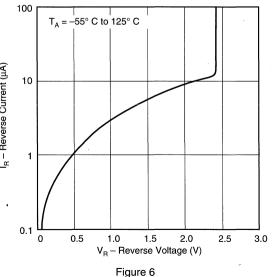

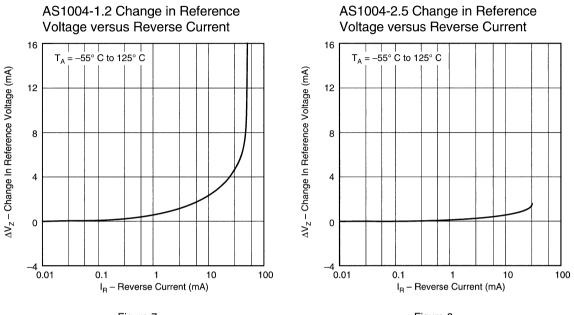

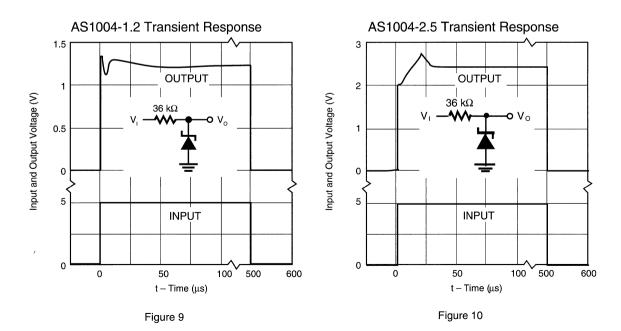

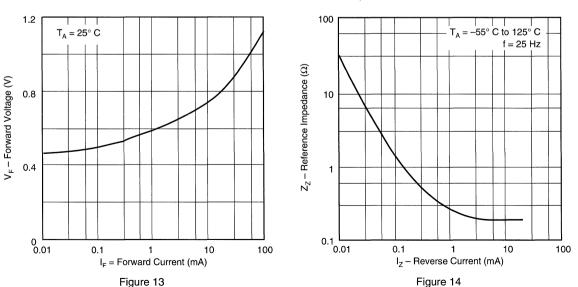

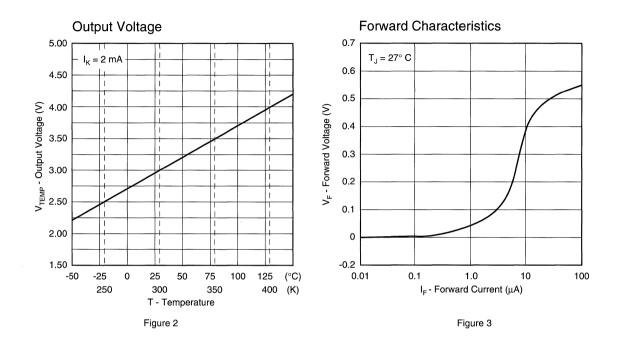

# **Typical Performance Curves**

Calculating Average Temperature

Calculating Average Temperature Coefficient for the AS1004-2.5 Reference

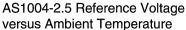

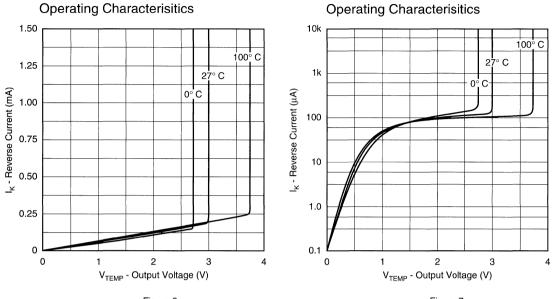

# AS1004-1.2 Reverse Operating Characteristics

Figure 3

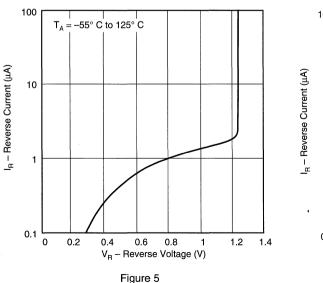

# AS1004-2.5 Reverse Operating Characteristics

Figure 7

Figure 11

Forward Characteristics

Low Frequency Reverse Dynamic Impedance

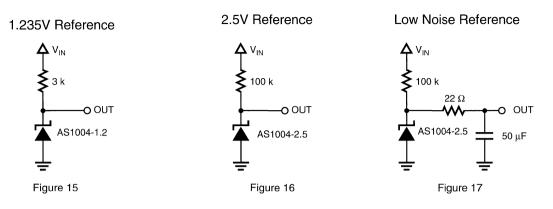

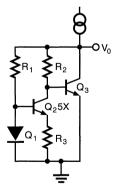

# **Typical Applications**

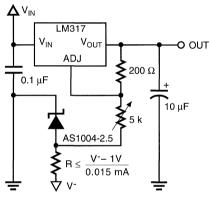

#### Variable Output Regulator

Figure 18

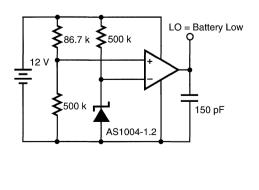

# Lead Acid Low Battery Detector

Figure 20

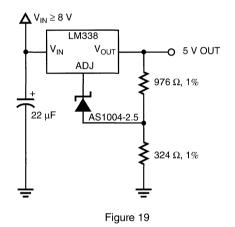

## High Stability 5V Regulator

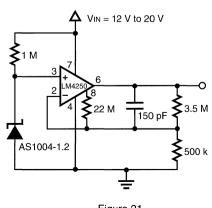

# Micropower 10V Reference

Figure 21

Notes

# AS2842/3/4/5 Current Mode Controller

## Features

- 2.5 V bandgap reference trimmed to 1.0% and temperature-compensated

- Extended temperature range from - 40 to 105° C

- AS2842/3 oscillations trimmed for precision duty cycle clamp

- AS2844/5 have exact 50% max duty cycle clamp

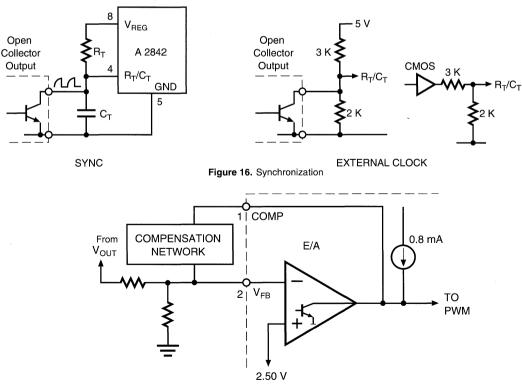

- Advanced oscillator design simplifies synchronization

- Improved specs on UVLO and hysteresis provide more predictable start-up and shutdown

- Improved 5 V regulator provides better AC noise immunity

- Guaranteed performance with current sense pulled below ground

- Over-temperature shutdown

# Description

The AS2842 family of control ICs provide pin-for-pin replacement of the industry standard UC3842 series of devices. The devices are redesigned to provide significantly improved tolerances in power supply manufacturing. The 2.5 V reference has been trimmed to 1.0% tolerance. The oscillator discharge current is trimmed to provide guaranteed duty cycle clamping rather than specified discharge current. The circuit is more completely specified to guarantee all parameters impacting power supply manufacturing tolerances.

In addition, the oscillator and flip-flop sections have been enhanced to provide additional performance. The  $R_T/C_T$  pin now doubles as a synchronization input that can be easily driven from open collector/open drain logic outputs. This sync input is a high impedance input and can easily be used for externally clocked systems. The new flip-flop topology allows the duty cycle on the AS2844/5 to be guaranteed between 49 and 50%. The AS2843/5 requires less than 0.5 mA of start-up current over the full temperature range.

# **Ordering Information**

| Description        | Temperature Range | Order Codes     |

|--------------------|-------------------|-----------------|

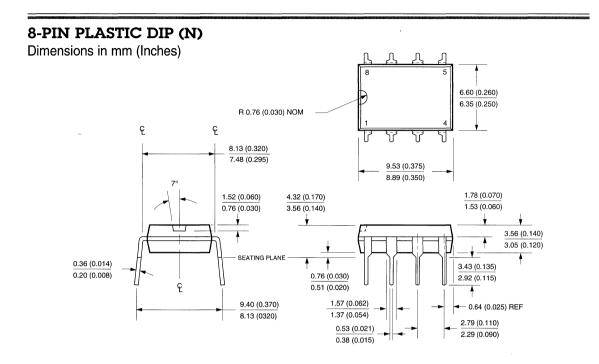

| 8-Pin Plastic DIP  | -40 to 105° C     | AS2842/3/4/5N   |

| 8-Pin Plastic SOIC | -40 to 105° C     | AS2842/3/4/5D-8 |

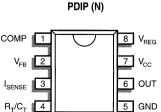

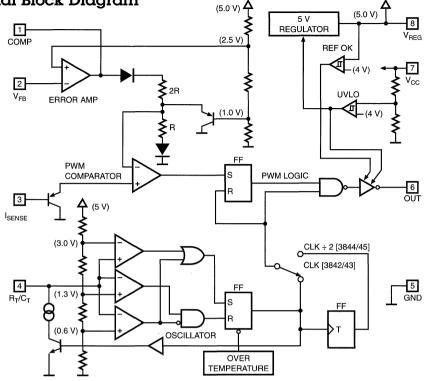

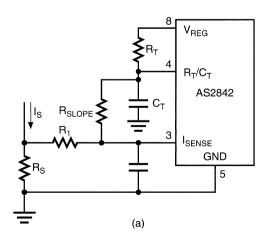

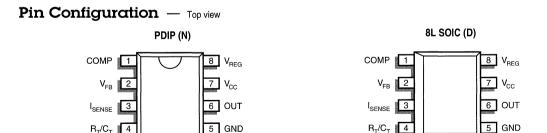

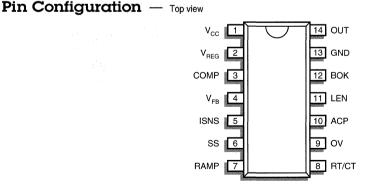

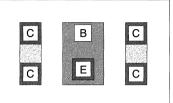

# **Pin Configuration** — Top view

8L SOIC (D)

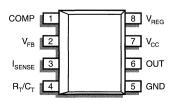

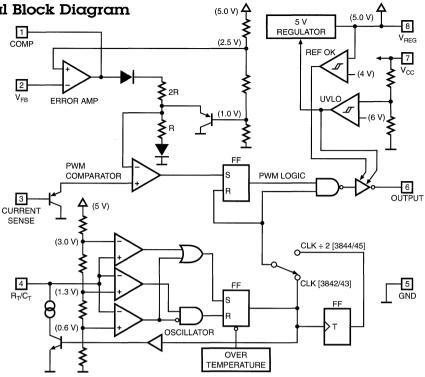

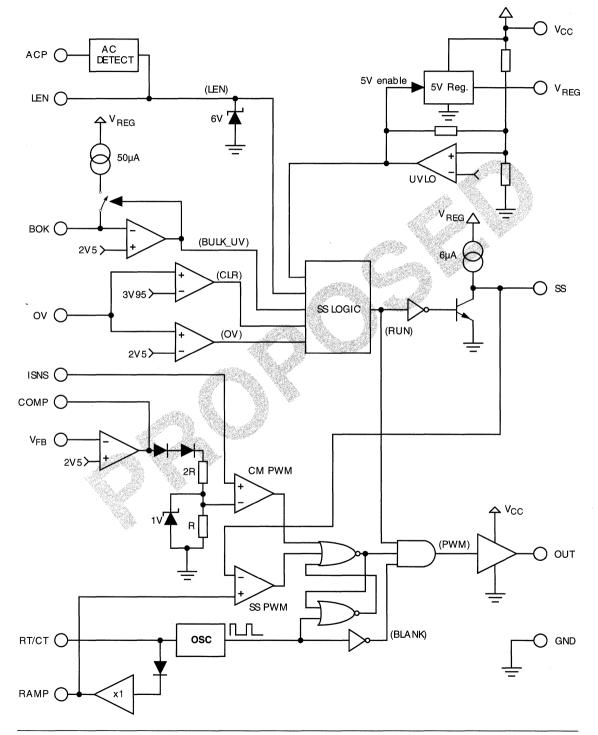

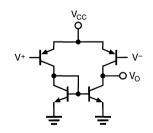

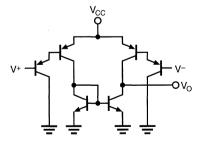

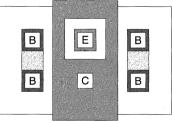

# Functional Block Diagram

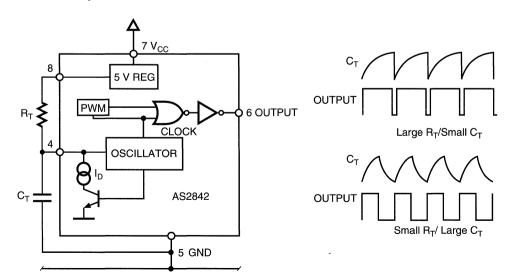

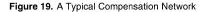

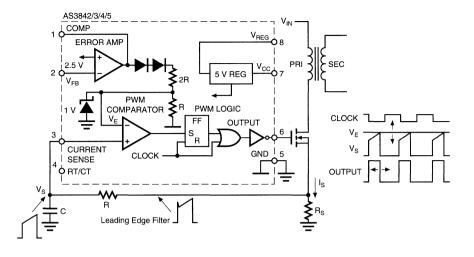

Figure 1. Block Diagram of the AS2842/3/4/5

# **Pin Function Description**

| Pin Number | Function                       | Description                                                                                                                                                                                                                            |

|------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

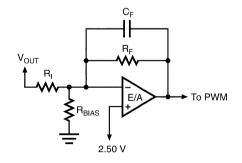

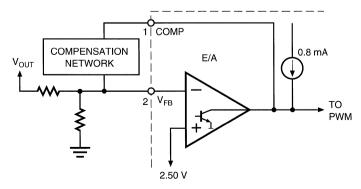

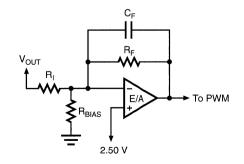

| 1          | COMP                           | This pin is the error amplifier output. Typically used to provide loop compensation to maintain $V_{\text{FB}}$ at 2.5 V.                                                                                                              |

| 2          | V <sub>FB</sub>                | Inverting input of the error amplifier. The non-inverting input is a trimmed 2.5 V bandgap reference.                                                                                                                                  |

| 3          | ISENSE                         | A voltage proportional to inductor current is connected to the input. The PWM uses this information to terminate the gate drive of the output.                                                                                         |

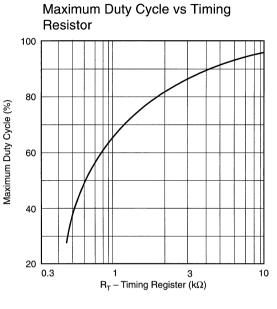

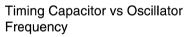

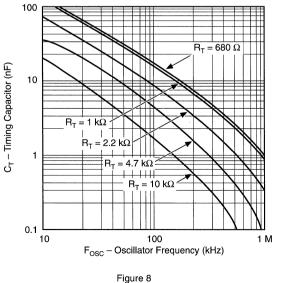

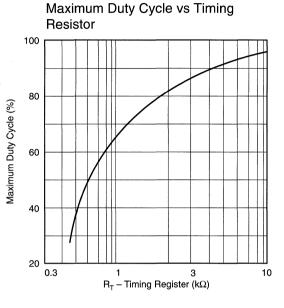

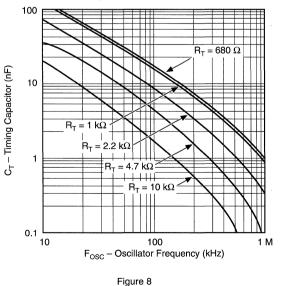

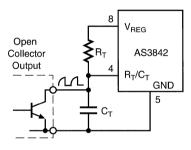

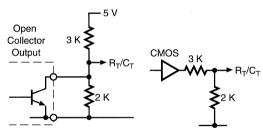

| 4          | R <sub>T</sub> /C <sub>T</sub> | Oscillator frequency and maximum output duty cycle are set by connecting a resistor ( $R_T$ ) to $V_{REG}$ and a capacitor ( $C_T$ ) to ground. Pulling this pin to ground or to $V_{REG}$ will accomplish a synchronization function. |

| 5          | GND                            | Circuit common ground, power ground, and IC substrate.                                                                                                                                                                                 |

| 6          | OUT                            | This output is designed to directly drive a power MOSFET switch. This output can sink or source peak currents up to 1A. The output for the AS2844/5 switches at one-half the oscillator frequency.                                     |

| 7          | Vcc                            | Positive supply voltage for the IC.                                                                                                                                                                                                    |

| 8          | V <sub>REG</sub>               | This 5 V regulated output provides charging current for the capacitor $C_{T}$ through the resistor $R_{T}.$                                                                                                                            |

# **Absolute Maximum Ratings**

| Parameter                                | Symbol           | Rating        | Unit |

|------------------------------------------|------------------|---------------|------|

| Supply Voltage (I <sub>CC</sub> < 30 mA) | V <sub>CC</sub>  | Self-Limiting | V    |

| Supply Voltage (Low Impedance Source)    | Vcc              | 30            | V    |

| Output Current                           | lout             | ±1            | А    |

| Output Energy (Capacitive Load)          |                  | 5             | μJ   |

| Analog Inputs (Pin 2, Pin 3)             |                  | -0.3 to 30    | V    |

| Error Amp Sink Current                   |                  | 10            | mA   |

| Maximum Power Dissipation                | PD               |               |      |

| 8L SOIC                                  |                  | 750           | mW   |

| 8L PDIP                                  |                  | 1000          | mW   |

| Maximum Junction Temperature             | TJ               | 150           | °C   |

| Storage Temperature Range                | T <sub>STG</sub> | -65 to 150    | °C   |

| Lead Temperature, Soldering 10 Seconds   | TL               | 300           | °C   |

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

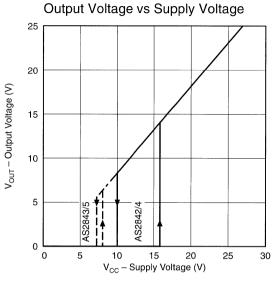

#### **Recommended Conditions**

| Parameter      | Symbol          | Rating                    | Unit |

|----------------|-----------------|---------------------------|------|

| Supply Voltage | V <sub>CC</sub> | an an Without and In Anno |      |

| AS2842,4       |                 | 15                        | V    |

| AS2843,5       |                 | 10                        | V    |

| Oscillator     | fosc            | 50 to 500                 | kHz  |

# **Typical Thermal Resistances**

| Package | θја      | θις     | Typical Derating |

|---------|----------|---------|------------------|

| 8L PDIP | 95° C/W  | 50° C/W | 10.5 mW/°C       |

| 8L SOIC | 175° C/W | 45° C/W | 5.7 mW/°C        |

# **Electrical Characteristics**

Electrical characteristics are guaranteed over full junction temperature range (-40 to  $105^{\circ}$  C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. The conditions are:  $V_{CC} = 15$  V,  $R_T = 10$  k $\Omega$ , and  $C_T = 3.3$  nF, unless otherwise stated. To override UVLO,  $V_{CC}$  should be raised above 17 V prior to test.

| Parameter                           | Symbol             | Test Condition                                                    | Min   | Тур   | Max   | Unit  |

|-------------------------------------|--------------------|-------------------------------------------------------------------|-------|-------|-------|-------|

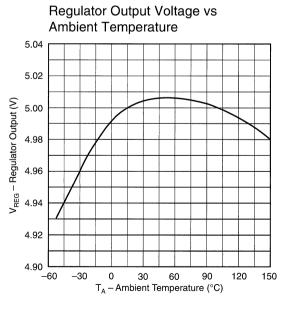

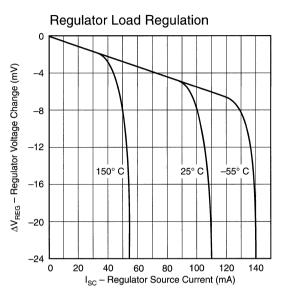

| 5 V Regulator                       |                    |                                                                   | •     |       | •     |       |

| Output Voltage                      | V <sub>REG</sub>   | $T_J = 25^\circ \text{ C}, I_{\text{REG}} = 1 \text{ mA}$         | 4.95  | 5.00  | 5.05  | V     |

| Line Regulation                     | PSRR               | 12 V <sub>CC</sub> 25 V                                           |       | 2     | 10    | mV    |

| Load Regulation                     |                    | 1 I <sub>REG</sub> 20 mA                                          |       | 2     | 10    | mV    |

| Temperature Stability <sup>1</sup>  | TC <sub>REG</sub>  |                                                                   |       | 0.2   | 0.4   | mV/°C |

| Total Output Variation <sup>1</sup> |                    | Line, load, temperature                                           | 4.85  |       | 5.15  | V     |

| Long-term Stability <sup>1</sup>    |                    | Over 1,000 hrs at 25° C                                           |       | 5     | 25    | mV    |

| Output Noise Voltage                | V <sub>NOISE</sub> | 10 Hz f 100 kHz, T ј = 25° С                                      |       | 50    |       | μV    |

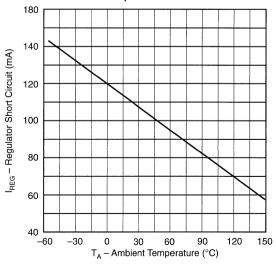

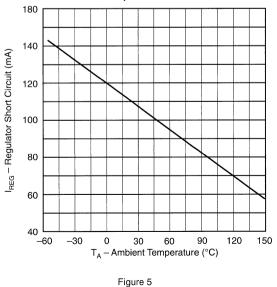

| Short Circuit Current               | Isc                |                                                                   | 30    | 100   | 180   | mA    |

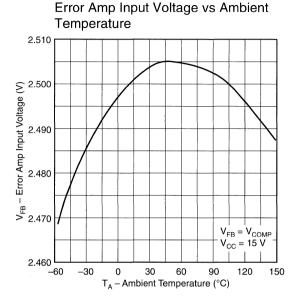

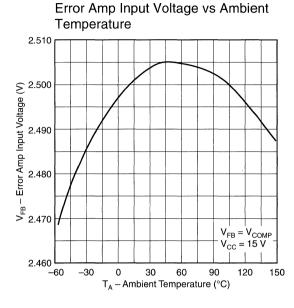

| 2.5 V Internal Reference            |                    |                                                                   |       |       |       |       |

| Nominal Voltage                     | V <sub>FB</sub>    | $T = 25^{\circ} \text{ C}; \text{ I}_{\text{REG}} = 1 \text{ mA}$ | 2.475 | 2.500 | 2.525 | V     |

| Line Regulation                     | PSRR               | 12 V V <sub>CC</sub> 25 V                                         |       | 2     | 5     | mV    |

| Load Regulation                     |                    | 1 I <sub>REG</sub> 20 mA                                          |       | 2     | 5     | mV    |

| Temperature Stability <sup>1</sup>  | TC <sub>VFB</sub>  |                                                                   |       | 0.1   | 0.2   | mV/°C |

| Total Output Variation <sup>1</sup> |                    | Line, load, temperature                                           | 2.450 | 2.500 | 2.550 | V     |

| Long-term Stability <sup>1</sup>    |                    | Over 1,000 hrs at 125° C                                          |       | 2     | 12    | mV    |

| Oscillator                          |                    |                                                                   |       |       |       | -     |

| Initial Accuracy                    | fosc               | T <sub>J</sub> = 25° C                                            | 47    | 52    | 57    | kHz   |

| Voltage Stability                   |                    | 12 V V <sub>CC</sub> 25 V                                         |       | 0.2   | 1     | %     |

| Temperature Stability <sup>1</sup>  | TC <sub>f</sub>    | T <sub>MIN</sub> T <sub>J</sub> T <sub>MAX</sub>                  |       | 5     |       | %     |

| Amplitude                           | fosc               | V <sub>RT/CT</sub> peak-to-peak                                   |       | 1.6   |       | V     |

| Upper Trip Point                    | V <sub>H</sub>     |                                                                   |       | 2.9   |       | V     |

| Lower Trip Point                    | VL                 |                                                                   |       | 1.3   |       | V     |

| Sync Threshold                      | V <sub>SYNC</sub>  |                                                                   | 400   | 600   | 800   | mV    |

| Discharge Current                   | ID                 |                                                                   | 7.5   | 8.7   | 9.5   | mA    |

| Duty Cycle Limit                    |                    | $R_T = 680 \Omega$ , $C_T = 5.3 nF$ , $T_J = 25^{\circ} C$        | 46    | 50    | 52    | %     |

# Electrical Characteristics (cont'd)

Electrical characteristics are guaranteed over full junction temperature range (-40 to 105° C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. The conditions are:  $V_{CC} = 15$  V,  $R_T = 10$  k $\Omega$ , and  $C_T = 3.3$  nF, unless otherwise stated. To override UVLO,  $V_{CC}$  should be raised above 17 V prior to test.

| Parameter                                   | Symbol                | Test Condition                                    | Min   | Тур  | Мах   | Unit  |

|---------------------------------------------|-----------------------|---------------------------------------------------|-------|------|-------|-------|

| Error Amplifier                             | . <b>k</b>            |                                                   |       |      |       |       |

| Input Voltage                               | V <sub>FB</sub>       | $T_J = 25^\circ C$                                | 2.475 | 2.50 | 2.525 | V     |

| Input Bias Current                          | I <sub>BIAS</sub>     |                                                   |       | -0.1 | -1    | μΑ    |

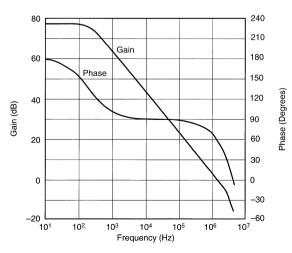

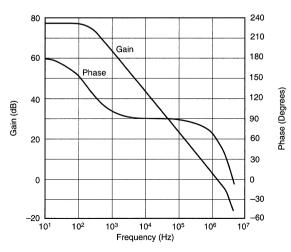

| Voltage Gain                                | A <sub>VOL</sub>      | 2 V <sub>COMP</sub> 4V                            | 65    | 90   |       | dB    |

| Transconductance                            | Gm                    |                                                   |       | 1    |       | mA/mV |

| Unity Gain Bandwidth <sup>1</sup>           | GBW                   |                                                   | 0.8   | 1.2  |       | MHz   |

| Power Supply Rejection Ratio                | PSRR                  | 12 V <sub>CC</sub> 25 V                           | 60    | 70   |       | dB    |

| Output Sink Current                         | ICOMPL                | V <sub>FB</sub> = 2.7 V, V <sub>COMP</sub> = 1.1V | 2     | 6    |       | mA    |

| Output Source Current                       | Ісомрн                | $V_{FB} = 2.3 \text{ V}, V_{COMP} = 5 \text{ V}$  | 0.5   | 0.8  |       | mA    |

| Output Swing High                           | V <sub>COMPH</sub>    | $V_{FB}$ = 2.3 V, $R_L$ = 15 k\Omega to Ground    | 5     | 5.5  |       | V     |

| Output Swing Low                            | VCOMPL                | $V_{FB}$ = 2.7 V, $R_L$ = 15 k $\Omega$ to Pin 8  |       | 0.7  | 1.1   | V     |

| Current Sense Comparator                    |                       |                                                   | ·     | •    |       |       |

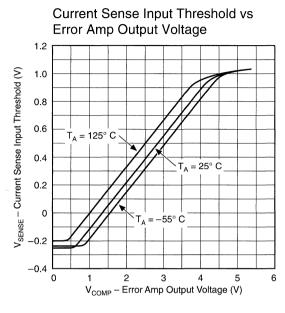

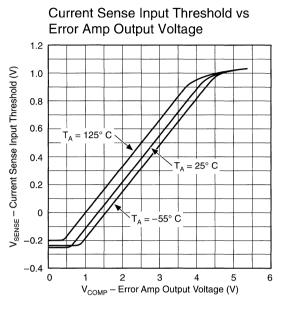

| Transfer Gain <sup>2,3</sup>                | AV <sub>CS</sub>      | -0.2 V <sub>SENSE</sub> 0.8 V                     | 2.85  | 3.0  | 3.15  | V/V   |

| I <sub>SENSE</sub> Level Shift <sup>2</sup> | V <sub>LS</sub>       | V <sub>SENSE</sub> = 0 V                          |       | 1.5  |       | V     |

| Maximum Input Signal <sup>2</sup>           |                       | V <sub>COMP</sub> = 5 V                           | 0.9   | 1    | 1.1   | V     |

| Power Supply Rejection Ratio                | PSRR                  | 12 V <sub>CC</sub> 25 V                           |       | 70   |       | dB    |

| Input Bias Current                          | I <sub>BIAS</sub>     |                                                   |       | -1   | -10   | μΑ    |

| Propagation Delay to Output <sup>1</sup>    | t <sub>PD</sub>       |                                                   |       | 85   | 150   | ns    |

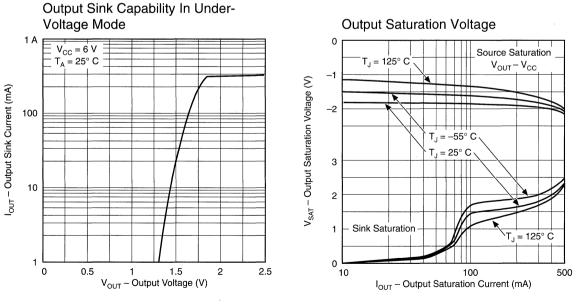

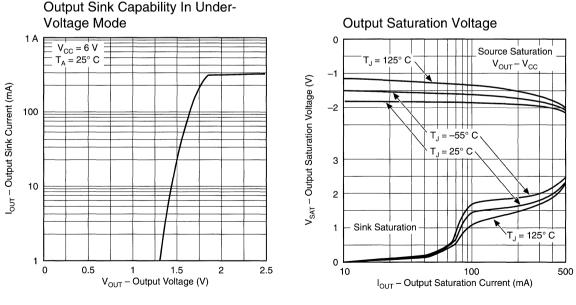

| Output                                      |                       |                                                   |       |      |       |       |

| Output Low Level                            | V <sub>OL</sub>       | I <sub>SINK</sub> = 20 mA                         |       | 0.1  | 0.4   | V     |

|                                             | V <sub>OL</sub>       | I <sub>SINK</sub> = 200 mA                        |       | 1.5  | 2.2   | V     |

| Output High Level                           | V <sub>OH</sub>       | I <sub>SOURCE</sub> = 20mA                        | 13    | 13.5 |       | V     |

|                                             | V <sub>OH</sub>       | I <sub>SOURCE</sub> = 200mA                       | 12    | 13.5 |       | v     |

| Rise Time <sup>1</sup>                      | t <sub>R</sub>        | C <sub>L</sub> = 1 nF                             |       | 50   | 150   | ns    |

| Fall Time <sup>1</sup>                      | tF                    | C <sub>L</sub> = 1 nF                             |       | 50   | 150   | ns    |

| Housekeeping                                |                       |                                                   |       |      |       |       |

| Start-up Threshold                          | V <sub>CC</sub> (on)  | 2842/4                                            | 15    | 16   | 17    | V     |

|                                             |                       | 2843/5                                            | 7.8   | 8.4  | 9.0   | V     |

| Minimum Operating Voltage                   | V <sub>CC</sub> (min) | 2842/4                                            | 9     | 10   | 11    | V     |

| After Turn On                               |                       | 2843/5                                            | 7.0   | 7.6  | 8.2   | V     |

| Output Low Level in UV State                | Vouv '                | $I_{SINK} = 20 \text{ mA}, V_{CC} = 6 \text{ V}$  |       | 1.5  | 2.0   | V     |

| Over-Temperature Shutdown <sup>4</sup>      | T <sub>OT</sub>       |                                                   |       | 125  |       | °C    |

## Electrical Characteristics (cont'd)

Electrical characteristics are guaranteed over full junction temperature range (-40 to 105° C). Ambient temperature must be derated based on power dissipation and package thermal characteristics. The conditions are:  $V_{CC} = 15$  V,  $R_T = 10$  k $\Omega$ , and  $C_T = 3.3$  nF, unless otherwise stated. To override UVLO,  $V_{CC}$  should be raised above 17 V prior to test.

| Parameter                     | Symbol           | Test Condition                                                                                                                                   | Min | Тур        | Max        | Unit     |

|-------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|------------|----------|

| PWM                           |                  |                                                                                                                                                  |     |            |            |          |

| Maximum Duty Cycle            | D <sub>max</sub> | 2842/3                                                                                                                                           | 94  | 97         | 100        | %        |

| Minimum Duty Cycle            | D <sub>min</sub> | 2842/3                                                                                                                                           |     |            | 0          | %        |

| Maximum Duty Cycle            | D <sub>max</sub> | 2844/5                                                                                                                                           | 49  | 49.5       | 50         | %        |

| Minimum Duty Cycle            | D <sub>min</sub> | 2844/5                                                                                                                                           |     |            | 0          | %        |

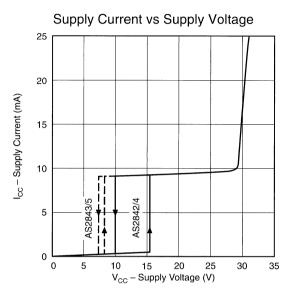

| Supply Current                |                  |                                                                                                                                                  |     |            |            |          |

| Start-up Current              | Icc              | $\begin{array}{l} 2842/4, \ V_{FB} = V_{SENSE} = 0 \ V, \ V_{CC} = 14 \ V \\ 2843/5, \ V_{FB} = V_{SENSE} = 0 \ V, \ V_{CC} = 7 \ V \end{array}$ |     | 0.5<br>0.3 | 1.0<br>0.5 | mA<br>mA |

| Operating Supply Current      | Icc              |                                                                                                                                                  |     | 9          | 17         | mA       |

| V <sub>CC</sub> Zener Voltage | Vz               | I <sub>CC</sub> = 25 mA                                                                                                                          |     | 30         |            | V.       |

|                               |                  |                                                                                                                                                  |     | 1          |            | 1        |

Notes:

1. This parameter is not 100% tested in production.

2. Parameter measured at trip point of PWM latch.

3. Transfer gain is the relationship between current sense input and corresponding error amplifier output at the PWM latch trip point and is mathematically expressed as follows:

$$A = \frac{\Delta I_{COMP}}{\Delta V_{SENSE}}; -0.2 \le V_{SENSE} \le 0.8 V$$

4. At the over-temperature threshold, T<sub>OT</sub>, the oscillator is disabled. The 5 V reference and the PWM stages, including the PWM latch, remain powered.

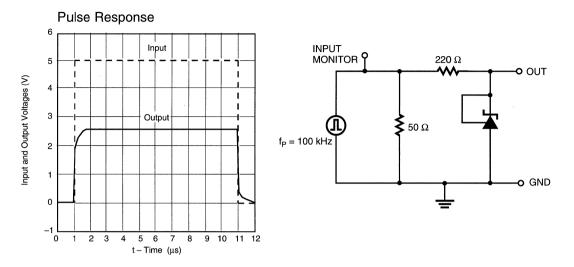

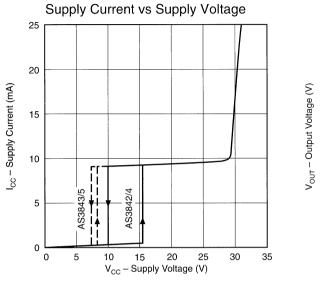

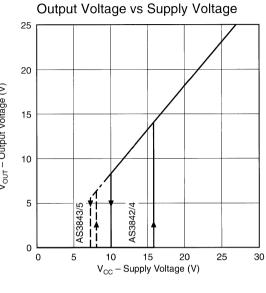

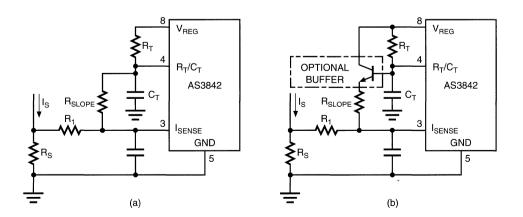

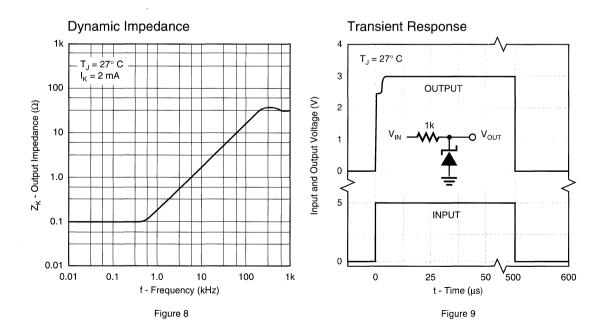

Figure 2

Figure 3

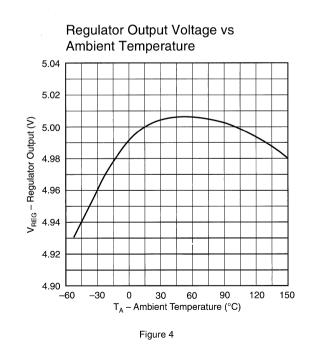

Figure 4

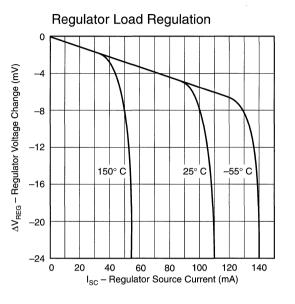

Regulator Short Circuit Current vs Ambient Temperature

Figure 5

Figure 6

Figure 7

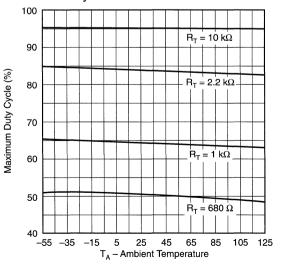

Maximum Duty Cycle Temperature Stability

Figure 9

Figure 10

Figure 11

Figure 12

Figure 13

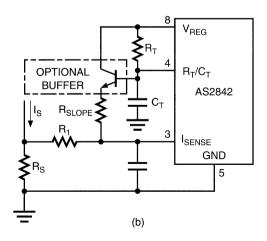

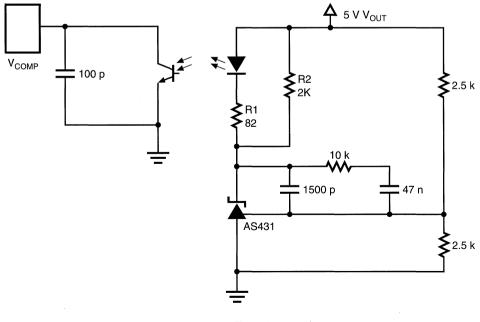

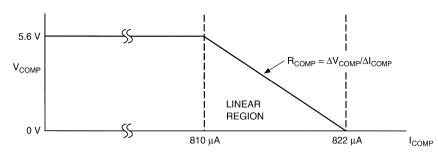

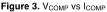

#### **Application Information**

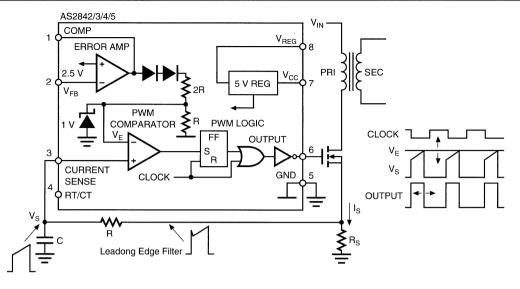

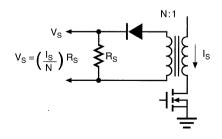

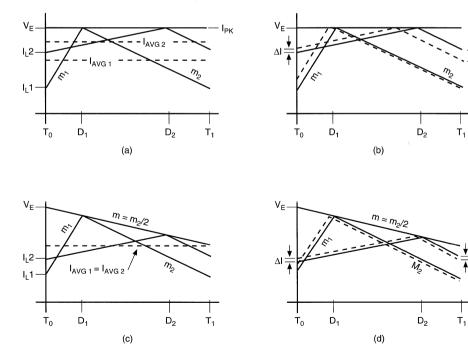

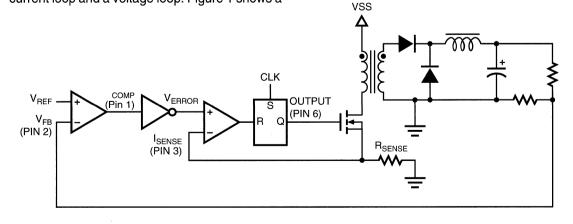

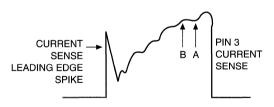

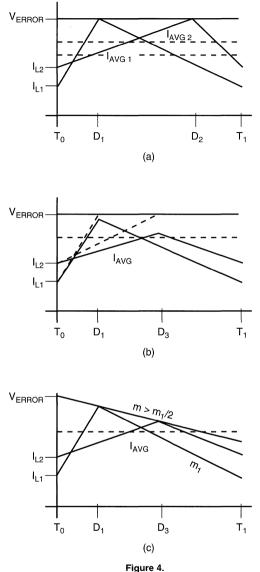

The AS2842/3/4/5 family of current-mode control ICs are low cost, high performance controllers which are pin compatible with the industry standard UC2842 series of devices. Suitable for many switch mode power supply applications, these ICs have been optimized for use in high frequency off-line and DC-DC converters. The AS2842 has been enhanced to provide significantly improved performance, resulting in exceptionally better tolerances in power supply manufacturing. In addition, all electrical characteristics are guaranteed over the full 0 to 105 °C temperature range. Among the many enhancements are: a precision trimmed 2.5 volt reference  $(\pm 0.5\%)$  of nominal at the error amplifier input), a significantly reduced propagation delay from current sense input to the IC output, a trimmed oscillator for precise duty-cycle clamping, a modified flip-flop scheme that gives a true 50% duty ratio clamp on 2844/45 types, and an improved 5 V regulator for better AC noise immunity. Furthermore, the AS2842 provides guaranteed performance with current sense input below ground. The advanced oscillator design greatly simplifies synchronization. The device is more completely specified to guarantee all parameters that impact power supply manufacturing tolerances. V<sub>DC</sub>

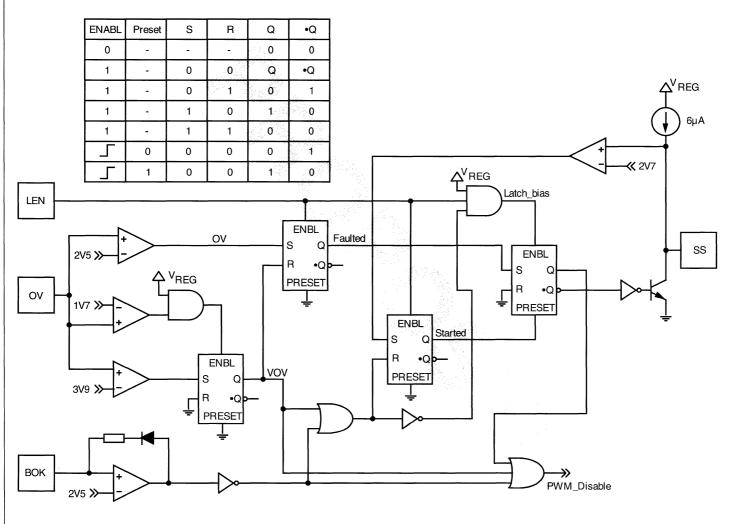

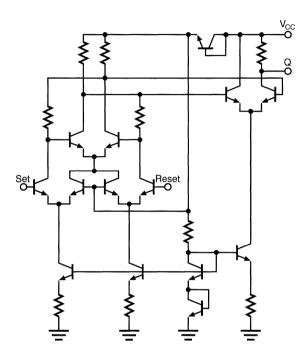

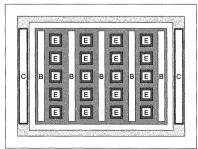

#### Section 1— Theory of Operation

The functional block diagram of the AS2842 is shown in Figure 1. The IC is comprised of the six basic functions necessary to implement current mode control; the under voltage lockout; the reference; the oscillator; the error amplifier; the current sense comparator/PWM latch; and the output. The following paragraphs will describe the theory of operation of each of the functional blocks.

#### 1.1 Undervoltage lockout (UVLO)

The undervoltage lockout function of the AS2842 holds the IC in a low guiescent current (1 mA) "standby" mode until the supply voltage ( $V_{CC}$ ) exceeds the upper UVLO threshold voltage. This guarantees that all of the IC's internal circuitry are properly biased and fully functional before the output stage is enabled. Once the IC turns on, the UVLO threshold shifts to a lower level (hysteresis) to prevent V<sub>CC</sub> oscillations.

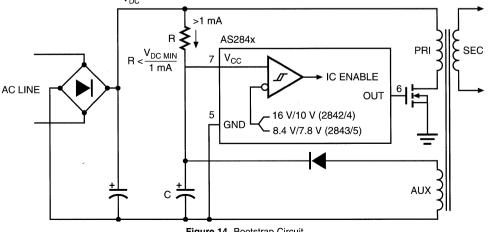

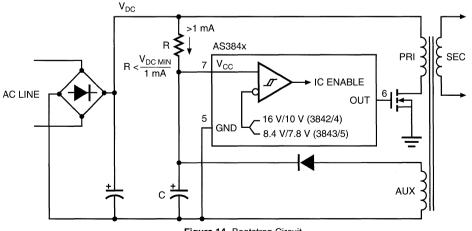

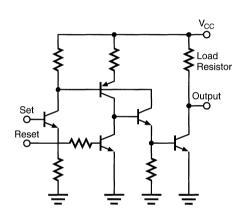

The low quiescent current standby mode of the AS2842 allows "bootstrapping"-a technique used in off-line converters to start the IC from the rectified AC line voltage initially, after which power to the IC is provided by an auxiliary winding off the power supply's main transformer. Figure 14 shows a typical bootstrap circuit where capacitor (C) is

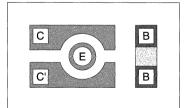

Figure 14. Bootstrap Circuit

charged via resistor (R) from the rectified AC line. When the voltage on the capacitor ( $V_{CC}$ ) reaches the upper UVLO threshold, the IC (and hence, the power supply) turns on and the voltage on C begins to quickly discharge due to the increased operating current. During this time, the auxiliary winding begins to supply the current necessary to run the IC. The capacitor must be sufficiently large to maintain a voltage greater than the lower UVLO threshold during start up. The value of R must be selected to provide greater than 1 mA of current at the minimum DC bus voltage (R < VDCmin/1 mA).

The UVLO feature of the AS2842 has significant advantages over standard 2842 devices. First, the UVLO thresholds are based on a temperature compensated band gap reference rather than conventional zeners. Second, the UVLO disables the output at power down, offering additional protection in cases where V<sub>REG</sub> is heavily decoupled. The UVLO on some 2842 devices shuts down the 5 volt regulator only, which results in eventual power down of the output only after the 5 volt rail collapses. This can lead to unwanted stresses on the switching devices during power down. The AS2842 has two separate comparators which monitor both  $V_{CC}$  and  $V_{REF}$ and hold the output low if either are not within specification.

The AS2842 family offers two different UVLO options. The AS2842/4 has UVLO thresholds of 16 volts (on) and 10 volts (off). The AS2843/5 has UVLO levels of 8.4 volts (on) and 7.6 volts (off).

# 1.2 Reference (V<sub>REG</sub> and V<sub>FB</sub>)

The AS2842 effectively has two precise band gap based temperature compensated voltage references. Most obvious is the  $V_{REG}$  pin (pin 8) which is the output of a series pass regulator. This 5.0 V output is normally used to provide charging current to the oscillator's timing capacitor (Section 1.3). In addition, there is a

trimmed internal 2.5 V reference which is connected to the non-inverting (+) input of the error amplifier. The tolerance of the internal reference is  $\pm 0.5\%$  over the full specified temperature range, and  $\pm 1\%$  for V<sub>REG.</sub>

The reference section of the AS2842 is greatly improved over the standard 2842 in a number of ways. For example, in a closed loop system, the voltage at the error amplifier's inverting input (V<sub>FB</sub>, pin 1) is forced by the loop to match the voltage at the non-inverting input. Thus, VFB is the voltage which sets the accuracy of the entire system. The 2.5 V reference of the AS2842 is tightly trimmed for precision at V<sub>FB</sub>, including errors caused by the op amp, and is specified over temperature. This method of trim provides a precise reference voltage for the error amplifier while maintaining the original 5 V regulator specifications. In addition, force/sense (Kelvin) bonding to the package pin is utilized to further improve the 5 V load regulation. Standard 2842's, on the other hand, specify tight regulation for the 5 V output only and rate it over line, load and temperature. The voltage at VFB, which is of critical importance, is loosely specified and only at 25° C.

The reference section, in addition to providing a precise DC reference voltage, also powers most of the IC's internal circuitry. Switching noise, therefore, can be internally coupled onto the reference. With this in mind, all of the logic within the AS2842 was designed with ECL type circuitry which generates less switching noise because it runs at essentially constant current regardless of logic state. This, together with improved AC noise rejection, results in substantially less switching noise on the 5 V output.

The reference output is short circuit protected and can safely deliver more than 20 mA to power external circuitry.

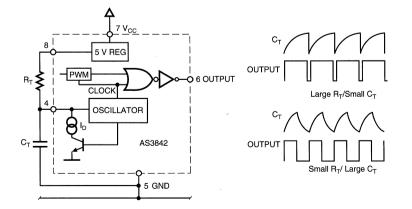

#### 1.3 Oscillator

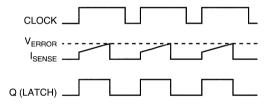

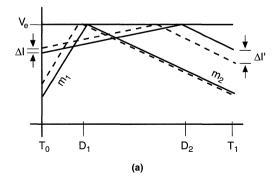

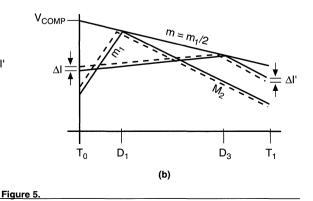

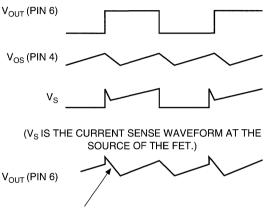

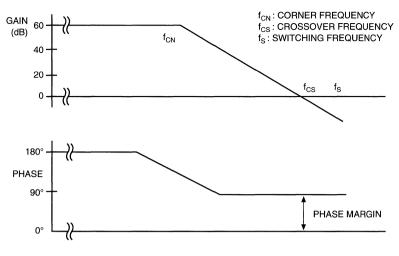

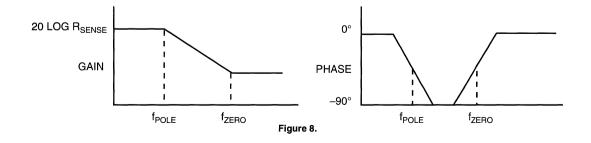

The newly designed oscillator of the AS2842 is enhanced to give significantly improved performance. These enhancements are discussed in the following paragraphs. The basic operation of the oscillator is as follows: