# **Voodoo Banshee<sup>®</sup>**

# UNIVERSAL ACCESS 2D DATABOOK

Revision 1.0 June 11, 1998 Copyright © 1996-1997 3Dfx Interactive, Inc. All Rights Reserved

# 3Dfx Interactive, Inc.

4435 Fortran Drive San Jose, CA 95134 www.3Dfx.com

#### **Copyright Notice:**

[English translations from legalese in brackets]

©1996-1999, 3Dfx Interactive, Inc. All rights reserved

# This document may be reproduced in written, electronic or any other form of expression only in its entirety.

[If you want to give someone a copy, you are hereby bound to give him or her a complete copy.]

#### This document may not be reproduced in any manner whatsoever for profit.

[If you want to copy this document, you must not charge for the copies other than a modest amount sufficient to cover the cost of the copy.]

#### **No Warranty**

THESE SPECIFICATIONS ARE PROVIDED BY 3DFX "AS IS" WITHOUT ANY REPRESENTATION OR WARRANTY, EXPRESS OR IMPLIED, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NONINFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS, OR ARISING FROM THE COURSE OF DEALING BETWEEN THE PARTIES OR USAGE OF TRADE. IN NO EVENT SHALL 3DFX BE LIABLE FOR ANY DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DIRECT OR INDIRECT DAMAGES, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE SPECIFICATIONS, EVEN IF 3DFX HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

[You're getting it for free. We believe the information provided to be accurate. Beyond that, you're on your own.]

|      | COPYRIGHT NOTICE:       .2         No Warranty.       .2 |    |  |  |

|------|----------------------------------------------------------|----|--|--|

| 1.   | INTRODUCTION                                             | 7  |  |  |

| Reso | OLUTIONS                                                 | 8  |  |  |

| 2.   | FUNCTIONAL OVERVIEW                                      | 8  |  |  |

|      | TEM LEVEL DIAGRAM                                        |    |  |  |

|      | iem level diagram<br>hitectural Overview                 |    |  |  |

|      | verall Overview                                          |    |  |  |

|      | D                                                        |    |  |  |

|      | CTIONAL OVERVIEW                                         |    |  |  |

|      | ANSHEE ADDRESS SPACE                                     |    |  |  |

|      |                                                          |    |  |  |

| 4.   | BASIC INIT PROCEDURES                                    | 15 |  |  |

| Prim | /ARY DEVICE                                              | 15 |  |  |

|      | ONDARY DEVICE, OR ON NON-X86 PLATFORMS                   |    |  |  |

| Sett | TING UP VESA DESKTOP MODES                               | 17 |  |  |

| 5.   | 2D                                                       |    |  |  |

| 2D F | REGISTER MAP                                             |    |  |  |

| REG  | ISTER DESCRIPTIONS                                       |    |  |  |

| ste  | atus Register                                            |    |  |  |

|      | CTRL REGISTER                                            |    |  |  |

|      | ommand Register                                          |    |  |  |

|      | ommandExtra Register                                     |    |  |  |

|      | plorBack and colorFore Registers                         |    |  |  |

|      | attern Registers<br>cBaseAddr and dstBaseAddr Registers  |    |  |  |

|      | cSize and dstSize Registers                              |    |  |  |

|      | cXY and dstXY Registers                                  |    |  |  |

|      | cFormat and dstFormat Registers                          |    |  |  |

|      | ipOMin, clipOMax, clip1Min, and clip1Max Registers       |    |  |  |

|      | plorkey Registers                                        |    |  |  |

| ro   | p Register                                               |    |  |  |

|      | neStyle register                                         |    |  |  |

| lir  | neStipple Register                                       | 46 |  |  |

|      | resenhamError registers                                  |    |  |  |

|      | NCH AREA                                                 |    |  |  |

|      | creen-to-screen Blt Mode                                 |    |  |  |

|      | creen-to-screen Stretch Blt Mode                         |    |  |  |

|      | ost-to-screen Blt Mode<br>ost-to-screen Stretch Blt Mode |    |  |  |

|      | ost-to-screen Stretcn Bit Mode<br>ectangle Fill Mode     |    |  |  |

|      | ine Mode                                                 |    |  |  |

|      | olyline Mode                                             |    |  |  |

|      | olygon Fill Mode                                         |    |  |  |

|      | - / 0                                                    |    |  |  |

| MISCELLANEOUS 2D                                                                    | 61 |

|-------------------------------------------------------------------------------------|----|

| Write Sgram Mode Register                                                           | 61 |

| Write Sgram Color Register                                                          | 62 |

| Write Sgram Mask Register                                                           | 62 |

| 6. 3D MEMORY MAPPED REGISTER SET                                                    | 62 |

| NOPCMD REGISTER                                                                     | 62 |

| LFBMODE REGISTER                                                                    | 62 |

| Linear Frame Buffer Writes                                                          | 65 |

| USERINTRCMD REGISTER                                                                | 68 |

| COMMAND DESCRIPTIONS                                                                | 69 |

| NOP Command                                                                         |    |

| USERINTERRUPT Command                                                               |    |

| LINEAR FRAME BUFFER ACCESS                                                          |    |

| Linear frame buffer Writes                                                          | 70 |

| Linear frame buffer Reads                                                           |    |

| PROGRAMMING CAVEATS                                                                 |    |

| Memory Accesses                                                                     |    |

| Determining Banshee Idle Condition                                                  | 71 |

| 7. PLL REGISTERS                                                                    | 72 |

| PLLCTRL REGISTERS                                                                   | 73 |

| 8. DAC REGISTERS                                                                    | 74 |

| DACMODE                                                                             | 74 |

| DACADDR                                                                             |    |

| DACDATA                                                                             | 74 |

| 9. VIDEO REGISTERS(PCI)                                                             | 75 |

| vidMaxRgbDelta                                                                      | 75 |

| vidProcCfg Register                                                                 |    |

| hwCurPatAddr Register                                                               |    |

| hwCurLoc Register                                                                   |    |

| hwCurC0 Register                                                                    |    |

| hwCurC1 Register                                                                    |    |

| vidInFormat                                                                         |    |

| vidInStatus                                                                         |    |

| vidSerialParallelPort Register                                                      |    |

| vidInXDecimDeltas (for VMI downscaling Brensenham Engine)/ vidTvOutBlankHCount (for |    |

| master mode)                                                                        |    |

| vidInDecimInitErrs                                                                  |    |

| vidInYDecimDeltas                                                                   |    |

| vidPixelBufThold                                                                    |    |

| vidChromaKeyMin Register                                                            |    |

| vidChromaKeyMax Register                                                            |    |

| vidCurrentLine Register                                                             |    |

| vidScreenSize                                                                       |    |

| vidOverlayStartCoords                                                               |    |

| vidOverlayEndScreenCoord                                                            |    |

|                                                                                     |    |

| VENDOR_ID REGISTER.97DEVICE_ID REGISTER.97COMMAND REGISTER.97STATUS REGISTER.98REVISION_ID REGISTER.98CLASS_CODE REGISTER.98CACHE_LINE_SIZE REGISTER.98LATENCY_TIMER REGISTER.98LATENCY_TIMER REGISTER.98HEADER_TYPE REGISTER.99BIST REGISTER.99MEMBASEADDR0 REGISTER.99MEMBASEADDR1 REGISTER.99IDBASEADDR1 REGISTER.99SUB VENDORID REGISTER.99SUB VENDORID REGISTER.90OGMBASEADDR REGISTER.00ROMBASEADDR REGISTER.000ROMBASEADDR REGISTER.000ROMBASEADDR REGISTER.000IDO SUBSYSTEMID REGISTER.000IDO RADEALDDR REGISTER.000INTERRUPT_LINE REGISTER.000INTERRUPT_LINE REGISTER.001INTERRUPT_PIN REGISTER.001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | vidOverlayDvdy<br>vidOverlayDvdyOffset<br>vidDesktopStartAddr<br>vidDesktopOverlayStride<br>vidInAddr0 |                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| vidOverlayDvdyOffset       90         vidDesktopStartAddr       90         vidDesktopStartAddr       90         vidInAddr0       91         vidInAddr1       91         vidInAddr2       91         vidInAddr2       91         vidInAddr2       91         vidInAddr2       91         vidInAddr2       91         vidInVaddr2       91         vidInVaddr2       91         vidInVaddr2       91         vidIoutroteriayStartAddr       91         vidIoutroteriayStartAddr       92         Function       92         Signals       92         VIDEO-IN INTERFACE       92         Signals       92         AcqPRoStZE       94         AcqPRoStZE       94         AcqPRostAdDressLice       95         AcqPRostAdDressLice       95         AcqPRostAdDressLice       95         AcqPRostAdDressLice       96         VUVASTRIDE       96         VUVASTRIDE       96         VUVASTRIDE       97         Starus Register       97         Starus Register       97         Starus Register                                                                                                               | vidOverlayDvdyOffset<br>vidDesktopStartAddr<br>vidDesktopOverlayStride<br>vidInAddr0                   | .89                                                        |

| vidDesktopStartAddr     90       vidDesktopOverlayStride     90       vidInAddr0     91       vidInAddr0     91       vidInAddr2     91       vidInAddr2     91       vidInAddr2     91       vidInAddr2     91       vidInStride     91       vidInStride     91       vidCurrOverlayStartAddr     91       vidCurrOverlayStartAddr     91       VIDEO-IN INTERFACE     92       Signals     92       Signals     92       VIDEO LIMITATION     93       IO.AGP/CMD TRANSFER/MISC REGISTERS     94       AGPHOSTADDRESSLOW     94       AGPHOSTADDRESSLOW     94       AGPHOSTADDRESSLOW     94       AGPHOSTADDRESSLOW     94       AGPREQKIZE     95       AGPRAPHICSATRIDE     95       VUVBASEADDRESS     95       VUVBASEADDRESS     96       11     AGP/PCI CONFIGURATION REGISTER SET     96       VUVSTRIDE     96       VUVSTRIDE     98       CALASS_CODE REGISTER     97       COMMAND REGISTER     97       COMMAND REGISTER     98       CLASS_CODE REGISTER     98       CLASS_CODE REGISTER     98       LATENCY_THER                                                                          | vidDesktopStartAddr<br>vidDesktopOverlayStride<br>vidInAddr0                                           |                                                            |

| vidDesktopOverlayStride       90         vidInAddr0       91         vidInAddr1       91         vidInAddr2       91         vidInAddr2       91         vidInAddr2       91         vidInAddr2       91         vidCurrOverlayStartAddr       91         ViDeo-IN INTERFACE       92         Function       92         Signals       92         VIDEO LINITATION       93         10.AGP/CMD TRANSFER/MISC REGISTERS       94         AGPReQSIZE       94         AGPREQSIZE       94         AGPRADRESSLOW       94         AGPRADRESSLOW       94         AGPRAPHICSADDRESS       95         AGPRAPHICSADDRESS       95         AGPRAPHICSTRIDE       95         AGPMOVECMD       95         YUVBASEADDRESS       96         11. AGP/PCI CONFIGURATION REGISTER SET       96         11. AGP/PCI CONFIGURATION REGISTER SET       97         DEVICE_ID REGISTER       97         DEVICE_ID REGISTER       97         Status Register       98         CAASE_CORE REGISTER       98         CAASE_CORE REGISTER       98         CAASE                                                                       | vidDesktopOverlayStride<br>vidInAddr0                                                                  |                                                            |

| vidInAddr0.     91       vidInAddr1     91       vidInAddr2     91       ViDeo-In INTERFACE     92       Function.     92       Signals     92       VIDEO LIMITATION     93       10.AGP/CMD TRANSFER/MISC REGISTERS     94       AGPREQSIZE     94       AGPHOSTADDRESSLOW     94       AGPHOSTADDRESSLOW     94       AGPHOSTADDRESSLOW     94       AGPGRAPHICSADDRESS     95       AGFGRAPHICSADDRESS     95       AGFGRAPHICSADDRESS     95       AGPROVECMD     95       VUVBASEADDRESS     96       YUVSTRIDE     96       11.     AGP/PCI CONFIGURATION REGISTER SET.       96     97       VENDOR_ID REGISTER     97       Command Register     97       Portuce_ID Register     98       Cass_cobe Register     98       Latency_TIMER Register     98       Latency_TIMER REGISTER     99       ID AGP/PCI REGISTER     99       MeMBASEADDR0 Registrer     99 <td>vidInAddr0</td> <td></td>                                                       | vidInAddr0                                                                                             |                                                            |

| vidInAddr1     91       vidInStride     91       vidInStride     91       vidCurrOverlayStartAddr     91       VIDEO-IN INTERFACE     92       Signals     92       Signals     92       VIDEO LIMITATION     93       10.AGP/CMD TRANSFER/MISC REGISTERS     94       AGPROSTAD RESSLOW     94       AGPHOSTADDRESSLOW     94       AGPGRAPHICSADDRESSLOW     94       AGPGRAPHICSADDRESSLOW     94       AGPGRAPHICSADDRESS     95       AOPMOVECND     95       YUVBASEADDRESS     96       YUVSTRIDE     96       11. AGP/PCI CONFIGURATION REGISTER SET     96       VENOR_ID REGISTER     97       DEVICE_ID REGISTER     97       DEVICE_ID REGISTER     97       DEVICE_ID REGISTER     97       PEVISION_ID REGISTER     98       RATER     98       RATERCY_TIMER REGISTER     98       CASS_CODE REGISTER     99       BIST REGISTER     99       MEMBASEADDRO REGISTER     99       ORMAND REGISTER     99       ORMAND REGISTER     99       ORMAND REGISTER     99       Strates Registere     98       CASS_CODE REGISTER     99                                                                |                                                                                                        | .90                                                        |

| vidInAddr2     91       vidInStride     91       vidCurrOverlayStartAddr.     91       VIDEO-IN INTERFACE     92       Function.     92       Signals     92       VIDEO LINTATION     93       10.AGP/CMD TRANSFER/MISC REGISTERS     94       AGPREQSIZE     94       AGPHOSTADDRESSLOW.     94       AGPHOSTADDRESSLOW.     94       AGPGRAPHICS ADDRESS     95       AGPGRAPHICS STRIDE     95       AGPGRAPHICS STRIDE     95       AGPMOVECMD     95       VUVSTRIDE     96       11. AGP/PCI CONFIGURATION REGISTER SET.     96       VENDOR_ID REGISTER     97       PORCI_D DREGISTER     97       Yentown ID REGISTER     97       Status REGISTER     98       CASS_CODE REGISTER     98       CASS_CODE REGISTER     98       CASS_CODE REGISTER     99       BIST REGISTER     99       BIST REGISTER     99       SUBVENDORID REGISTER     99       SUBVADROR REGISTER     99       MEMBASEADDR REGISTER     99       MEMBASEADDR REGISTER     99       MEMBASEADDR REGISTER     99       SUBVENDORID REGISTER     99       NUTHER RECISTER     99 <td>vidInAddr1</td> <td>.91</td>              | vidInAddr1                                                                                             | .91                                                        |

| vidInStride     91       vidCurrOverlayStartAddr     91       VIDEO-IN INTERFACE     92       Function     92       Signals     92       VIDEO LIMITATION     93       10.AGP/CMD TRANSFER/MISC REGISTERS     94       AGPROSIZE     94       AGPHOSTADDRESSLOW     94       AGPHOSTADDRESSLOW     94       AGPGRAPHICSADDRESSLOW     94       AGPGRAPHICSADDRESSLOW     94       AGPGRAPHICSADDRESS     95       AGPMOVECMD     95       VUVBASEADDRESS     96       YUVBASEADDRESS     96       YUVSTRIDE     96       11. AGP/PCI CONFIGURATION REGISTER SET     96       VENDOR_ID REGISTER     97       COMMAND REGISTER     97       COMMAND REGISTER     97       COMMAND REGISTER     98       REVISION_ID REGISTER     98       REVISION_ID REGISTER     98       REVISION_ID REGISTER     98       BIST REGISTER     98       MEMBASEADDROR REGISTER     99       BIST REGISTER     99       BIST REGISTER     99       SUBVENDORID REGISTER     99       SUBVENDORID REGISTER     99       SUBVENDORID REGISTER     99       MEMASEADDR REGISTER     99 </td <td></td> <td>.91</td>                 |                                                                                                        | .91                                                        |

| vidCurrOverlayStartAddr.       91         VIDEO-IN INTERFACE       92         Function.       92         Signals       92         VIDEO LIMITATION       93         10.AGP/CMD TRANSFER/MISC REGISTERS       94         AGPReQSIZE       94         AGPREQSIZE       94         AGPREQSIZE       94         AGPREQSIZE       94         AGPREQSIZE       94         AGPREADERSSLOW       94         AGPREADERSSLOW       94         AGPREADERSSLOW       94         AGPRAPHICSADDRESS       95         AGPGRAPHICSADDRESS       95         AGPGRAPHICSADDRESS       95         AGPRADERSS       96         YUVBASEADDRESS       96         YUVBASEADDRESS       96         YUVSTRIDE       96         11. AGP/PCI CONFIGURATION REGISTER SET       96         VENDOR_ID REGISTER       97         Device_ID REGISTER       97         Command Register       97         Command Register       97         Command Register       98         Revision_ID Register       98         Cache_Line_SizeRegister       98         MeAdaseAddre                                                                        |                                                                                                        |                                                            |

| VIDEO-IN INTERFACE.92Function.92Signals.92VIDEO LIMITATION.9310.AGP/CMD TRANSFER/MISC REGISTERS.94AGPREQSIZE.94AGPHOSTADDRESSLOW.94AGPHOSTADDRESSLOW.94AGPHOSTADDRESSLIGH.94AGPGRAPHICSADDRESS.95AGPGRAPHICSADDRESS.95AGPGRAPHICSTRIDE.95YUVBASEADDRESS.96YUVSTRIDE.96YUVSTRIDE.96YUVSTRIDE.96COMMAND REGISTER.97STATUS REGISTER.97STATUS REGISTER.98CLASS_CODE REGISTER.98LATENCY_TIME REGISTER.98BIST REGISTER.98MEMBASEADDRO REGISTER.99BIST REGISTER.99SUBVENDRI ID REGISTER.99STATUS REGISTER.99STATUS REGISTER.98LATENCY_TIME REGISTER.98LATENCY_TIME REGISTER.99BIST REGISTER.99SUBVENDORID REGISTER.99MEMBASEADDRO REGISTER.99MEMBASEADDRO REGISTER.99SUBVENDORID REGISTER.99SUBVENDORID REGISTER.90MEMBASEADDRO REGISTER.90MEMBASEADDRO REGISTER.90MEMBASEADDRO REGISTER.90MEMBASEADDRO REGISTER.90MEMBASEADDRO REGISTER.90MEMBASEADDRO REGISTER.90MEMBASEADDRO REGISTER.90MEMBASEADDRO REGISTER.90<                                                                                                                                                                                                  |                                                                                                        |                                                            |

| Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                        |                                                            |

| Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                        |                                                            |

| VIDEO LIMITATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                        |                                                            |

| 10.AGP/CMD TRANSFER/MISC REGISTERS       .94         AGPReQSIZE       .94         AGPHOSTADDRESSLOW       .94         AGPHOSTADDRESSLOW       .94         AGPHOSTADDRESSLOW       .94         AGPGRAPHICSADDRESS       .95         AGPGRAPHICSADDRESS       .95         AGPMOVECMD       .95         YUVBASEADDRESS       .96         11. AGP/PCI CONFIGURATION REGISTER SET       .96         11. AGP/PCI CONFIGURATION REGISTER SET       .96         VENDOR_ID REGISTER       .97         Device_ID Register       .97         Octamax Register       .97         Status Register       .98         Revision_ID Register       .98         Cass_code Register       .98         Cass_code Register       .98         Meader_type Register       .98         BIST Recigister       .99         MemBaseAddr0 Register       .99         MemBaseAddr0 Register | 0                                                                                                      |                                                            |

| AGPREQSIZE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VIDEO LIMITATION                                                                                       | .93                                                        |

| AGPHOSTADDRESSLOW94AGPGRAPHICSADDRESS95AGPGRAPHICSATRIDE95AGPMOVECMD95YUVBASEADDRESS96YUVSTRIDE9611. AGP/PCI CONFIGURATION REGISTER SET96VILDASEADDRESS97DEVICE, ID REGISTER97DEVICE, ID REGISTER97COMMAND REGISTER97COMMAND REGISTER97STATUS REGISTER98REVISION_ID REGISTER98CACHE, LINE_SIZE REGISTER98LATENCY_TIMER REGISTER98HEADER_TYPE REGISTER99BIST REGISTER99MEMBASEADDR REGISTER99UBASEADDR REGISTER99UBASEADDR REGISTER99UBASEADDR REGISTER99UBASEADDR REGISTER99UBASEADDR REGISTER99UBASEADDR REGISTER99SUBVENDORID REGISTER99SUBVENDORID REGISTER90IDASEADDR REGISTER90IDASEADDR REGISTER90SUBVENDORID REGISTER90SUBVENDORID REGISTER100ROMASEADDR REGISTER100ROMASEADDR REGISTER100ROMASEADDR REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_LINE REGISTER100<                                                                                                                                                                       | 10.AGP/CMD TRANSFER/MISC REGISTERS                                                                     | .94                                                        |

| AGPHOSTADDRESSHIGH.94AGPGRAPHICSADDRESS.95AGPGRAPHICSSTRIDE.95AGPMOVECMD.95AGPMOVECMD.96YUVBASEADDRESS.96YUVSTRIDE.9611. AGP/PCI CONFIGURATION REGISTER SET.96VENDOR_ID REGISTER.97DEVICE_ID REGISTER.97COMMAND REGISTER.97COMMAND REGISTER.97STATUS REGISTER.98REVISION_ID REGISTER.98CLASS_CODE REGISTER.98LATENCY_TIMER REGISTER.98LATENCY_TIMER REGISTER.99BIST REGISTER.99MEMBASEADDRO REGISTER.99IST REGISTER.99IOBASEADDR REGISTER.90IOM ROMBASEADDR REGISTER.100CAPABILITIES POINTER.100INTERRUPT_LINE REGISTER.101INTERRUPT_IN REGISTER.101INTERRUPT_IN REGISTER.101INTERRUPT_IN REGISTER.101INTERRUPT_IN REGISTER.101INTERRUPT_IN REGISTER.101INTERRUPT_IN REGISTER<                                                                                                                                                                                                               |                                                                                                        |                                                            |

| AGPGRAPHICSADDRESS.95AGPGRAPHICSSTRIDE.95AGPMOVECMD.95YUVBASEADDRESS.96YUVSTRIDE.96YUVSTRIDE.96 <b>11.</b> AGP/PCI CONFIGURATION REGISTER SET.96VENDOR_ID REGISTER.97DEVICE_ID REGISTER.97COMMAND REGISTER.97STATUS REGISTER.97STATUS REGISTER.98CLASS_CODE REGISTER.98CACHE_LINE_SIZE REGISTER.98LATENCY_TIMER REGISTER.98BIST REGISTER.99BIST REGISTER.99MEMBASEADDR REGISTER.99IDBASEADDR REGISTER.99IDBASEADDR REGISTER.99SUBVENDORID REGISTER.99IDBASEADDR REGISTER.99SUBVENDORID REGISTER.90IDASEADDR REGISTER.90IDASEADDR REGISTER.90IDASEADDR REGISTER.90IDASEADDR REGISTER.90IDASEADDR REGISTER.100ROMBASEADDR REGISTER.100IDASEADDR REGISTER.100IDASEADDR REGISTER.100IDASEADDR REGISTER.100IDASEADDR REGISTER.100IDASEADDR REGISTER.100IDASEADDR REGISTER.100IDARSEADDR REGISTER.100IDARSEADDR REGISTER.100IDARSEADDR REGISTER.100IDARSEADDR REGISTER.100IDARSEADDR REGISTER.100IDARSEADDR REGISTER.100IDARSEADDR REGISTER.100<                                                                                                                                                                     |                                                                                                        |                                                            |

| AGPGRAPHICSSTRIDE.95AGPMOVECMD.95YUVBASEADDRESS.96YUVSTRIDE.96YUVSTRIDE.96 <b>11.</b> AGP/PCI CONFIGURATION REGISTER SET.96VENDOR_ID REGISTER.97DEVICE_ID REGISTER.97COMMAND REGISTER.97STATUS REGISTER.98REVISION_ID REGISTER.98RASS_CODE REGISTER.98LATENCY_TIMER REGISTER.98LATENCY_TIMER REGISTER.98BIST REGISTER.99BIST REGISTER.99MEMBASEADDR0 REGISTER.99MEMBASEADDR1 REGISTER.99MEMBASEADDR1 REGISTER.99MEMBASEADDR1 REGISTER.99MEMBASEADDR1 REGISTER.99MORASEADDR REGISTER.100ROBASEADDR REGISTER.100NOBASEADDR REGISTER.100NOBASEADDR REGISTER.100NOBASEADDR REGISTER.100NOBASEADDR REGISTER.100NOBASEADDR REGISTER.100INTERRUPT_LINE REGISTER.101INTERRUPT_LINE REGISTER.101INTERRUPT_LINE REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101                                                                                                                                                                                                       |                                                                                                        |                                                            |

| AGPMOVECMD.95YUVBASEADDRESS.96YUVSTRIDE.9611. AGP/PCI CONFIGURATION REGISTER SET.96VENDOR_ID REGISTER.97Device_ID Register.97COMMAND REGISTER.97COMMAND REGISTER.97STATUS REGISTER.98CLASS_CODE REGISTER.98CACHE_LINE_SIZE REGISTER.98LATENCY_TIMER REGISTER.98HEADER_TYPE REGISTER.99BIST REGISTER.99MEMBASEADDR0 REGISTER.99SUB VENDORID REGISTER.99SUB VENDORID REGISTER.99SUB VENDORID REGISTER.99SUB VENDORID REGISTER.90CAPABILT REGISTER.90CAPABILT REGISTER.100CAPABILTIES POINTER.100INTERRUPT_LINE REGISTER.100INTERRUPT_LINE REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101INTERRUPT_PIN REGISTER.101                                                                                                                                                                                                                                                                                                                                                                                               | AGPGRAPHICSADDRESS                                                                                     | .95                                                        |

| yuvBaseAddress96yuvStride9611. AGP/PCI CONFIGURATION REGISTER SET96Vendor_ID Register97Device_ID Register97Command Register97Command Register97Status Register98Revision_ID Register98Cass_code Register98Cass_code Register98Latency_timer Register98Header_type Register99BIST Register99MemBaseAddr0 Register99ubbaseAddr1 Register99sub VendorID Register99sub VendorID Register99sub VendorID Register99sub VendorID Register90combaseAddr1 Register99sub VendorID Register90sub SystemID Register100sub SystemID Register100CapabiLittes Pointer100Interrupt_line Register100Interrupt_Ine Register101Interrupt_Ine Register101                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                        |                                                            |

| YUVŠTRIDE9611. AGP/PCI CONFIGURATION REGISTER SET96VENDOR_ID REGISTER97DEVICE_ID REGISTER97COMMAND REGISTER97STATUS REGISTER98REVISION_ID REGISTER98CLASS_CODE REGISTER98CACHE_LINE_SIZE REGISTER98LATENCY_TIMER REGISTER98HEADER_TYPE REGISTER99BIST REGISTER99MEMBASEADDRO REGISTER99MEMBASEADDRO REGISTER99IOBASEADDR REGISTER99IOBASEADDR REGISTER99IOBASEADDR REGISTER100SUBVENDORID REGISTER100NOMBASEADDR REGISTER100NOMBASEADDR REGISTER100IOU SUBSYSTEMID REGISTER100IOU ROMBASEADDR REGISTER100IOU ROMBASEADDR REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_IN REGISTER101INTERRUPT_IN REGISTER101INTERRUPT_IN REGISTER101INTERRUPT_IN REGISTER101INTERRUPT_IN REGISTER101INTERRUPT_IN REGISTER101INTERRUPT_IN REGISTER101                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |                                                            |

| 11.AGP/PCI CONFIGURATION REGISTER SET96VENDOR_ID REGISTER97DEVICE_ID REGISTER97COMMAND REGISTER97COMMAND REGISTER98REVISION_ID REGISTER98CLASS_CODE REGISTER98CACHE_LINE_SIZE REGISTER98LATENCY_TIMER REGISTER98LATENCY_TIMER REGISTER99BIST REGISTER99MEMBASEADDRO REGISTER99MEMBASEADDRO REGISTER99IOBASEADDR REGISTER99IOBASEADDR REGISTER99IOBASEADDR REGISTER100ROMBASEADDR REGISTER100NOMBASEADDR REGISTER100NOTERUPT_LINE REGISTER101INTERRUPT_INE REGISTER101INTERRUPT_INE REGISTER101                                                                                                                                                                                                                                                        |                                                                                                        |                                                            |

| VENDOR_ID REGISTER97DEVICE_ID REGISTER97COMMAND REGISTER97STATUS REGISTER98REVISION_ID REGISTER98CLASS_CODE REGISTER98CLASS_CODE REGISTER98CACHE_LINE_SIZE REGISTER98LATENCY_TIMER REGISTER98LATENCY_TIMER REGISTER98HEADER_TYPE REGISTER99BIST REGISTER99MEMBASEADDR0 REGISTER99MEMBASEADDR1 REGISTER99OBASEADDR REGISTER99SUB VENDORID REGISTER99SUB VENDORID REGISTER100ROMBASEADDR REGISTER100ROMBASEADDR REGISTER100ROMBASEADDR REGISTER100NOMBASEADDR REGISTER100INTERRUPT_LINE REGISTER100INTERRUPT_LINE REGISTER101INTERRUPT_PIN REGISTER101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | YUVSTRIDE                                                                                              | .96                                                        |

| DEVICE_ID REGISTER.97COMMAND REGISTER.97STATUS REGISTER.98REVISION_ID REGISTER.98CLASS_CODE REGISTER.98CACHE_LINE_SIZE REGISTER.98LATENCY_TIMER REGISTER.98HEADER_TYPE REGISTER.99BIST REGISTER.99MEMBASEADDR0 REGISTER.99MEMBASEADDR1 REGISTER.99SUB VENDORID REGISTER.99SUB VENDORID REGISTER.99SUB VENDORID REGISTER.90SUB VENDORID REGISTER.00ROMBASEADDR REGISTER.00ION SUBSYSTEMID REGISTER.00ION RASEADDR REGISTER.00INTERRUPT_LINE REGISTER.00INTERRUPT_IN REGISTER.00INTERRUPT_IN REGISTER.00INTERRUPT_IN REGISTER.00INTERRUPT_IN REGISTER.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11. AGP/PCI CONFIGURATION REGISTER SET                                                                 | .96                                                        |

| COMMAND REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VENDOR ID REGISTER                                                                                     | .97                                                        |

| STATUS REGISTER.98REVISION_ID REGISTER.98CLASS_CODE REGISTER.98CACHE_LINE_SIZE REGISTER.98LATENCY_TIMER REGISTER.98HEADER_TYPE REGISTER.99BIST REGISTER.99MEMBASEADDR0 REGISTER.99MEMBASEADDR1 REGISTER.99IOBASEADDR REGISTER.99SUBVENDORID REGISTER.99SUBVENDORID REGISTER.100SUBSYSTEMID REGISTER.100ROMBASEADDR REGISTER.100ROMBASEADDR REGISTER.100INTERRUPT_LINE REGISTER.101INTERRUPT_PIN REGISTER.101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Device ID Register                                                                                     | .97                                                        |

| Revision_ID Register.98CLASS_CODE REGISTER.98CACHE_LINE_SIZE REGISTER.98LATENCY_TIMER REGISTER.98HEADER_TYPE REGISTER.99BIST REGISTER.99MEMBASEADDR0 REGISTER.99MEMBASEADDR1 REGISTER.99IOBASEADDR REGISTER.99SUBVENDORID REGISTER.99SUBVENDORID REGISTER.100SUBSYSTEMID REGISTER.100ROMBASEADDR REGISTER.100ROMBASEADDR REGISTER.100INTERRUPT_LINE REGISTER.101INTERRUPT_PIN REGISTER.101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | COMMAND REGISTER                                                                                       | .97                                                        |

| CLASS_CODE REGISTER98CACHE_LINE_SIZE REGISTER98LATENCY_TIMER REGISTER98HEADER_TYPE REGISTER99BIST REGISTER99MEMBASEADDR0 REGISTER99MEMBASEADDR1 REGISTER99IOBASEADDR REGISTER99SUBVENDORID REGISTER99SUBVENDORID REGISTER100SUBSYSTEMID REGISTER100ROMBASEADDR REGISTER100ROMBASEADDR REGISTER100INTERRUPT_LINE REGISTER101INTERRUPT_PIN REGISTER101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | STATUS REGISTER                                                                                        | .98                                                        |

| CACHE_LINE_SIZE REGISTER.98LATENCY_TIMER REGISTER.98HEADER_TYPE REGISTER.99BIST REGISTER.99MEMBASEADDR0 REGISTER.99MEMBASEADDR1 REGISTER.99IOBASEADDR REGISTER.99SUBVENDORID REGISTER.99SUBVENDORID REGISTER.100SUBSYSTEMID REGISTER.100ROMBASEADDR REGISTER.100INTERRUPT_LINE REGISTER.101INTERRUPT_PIN REGISTER.101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | REVISION_ID REGISTER                                                                                   | .98                                                        |

| LATENCY_TIMER REGISTER98HEADER_TYPE REGISTER99BIST REGISTER99MEMBASEADDR0 REGISTER99MEMBASEADDR1 REGISTER99IOBASEADDR REGISTER99SUBVENDORID REGISTER99SUBVENDORID REGISTER100SUBSYSTEMID REGISTER100ROMBASEADDR REGISTER100CAPABILITIES POINTER100INTERRUPT_LINE REGISTER101INTERRUPT_PIN REGISTER101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CLASS_CODE REGISTER                                                                                    | .98                                                        |

| HEADER_TYPE REGISTER.99BIST REGISTER.99MEMBASEADDR0 REGISTER.99MEMBASEADDR1 REGISTER.99IOBASEADDR REGISTER.99SUBVENDORID REGISTER.99SUBVENDORID REGISTER.100SUBSYSTEMID REGISTER.100CAPABILITIES POINTER.100INTERRUPT_LINE REGISTER.101INTERRUPT_PIN REGISTER.101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CACHE_LINE_SIZE REGISTER                                                                               | .98                                                        |

| BIST Register       .99         MEMBASEADDR0 REGISTER       .99         MEMBASEADDR1 REGISTER       .99         IOBASEADDR REGISTER       .99         SUBVENDORID REGISTER       .100         SUBSYSTEMID REGISTER       .100         ROMBASEADDR REGISTER       .100         ROMBASEADDR REGISTER       .100         ROMBASEADDR REGISTER       .100         ROMBASEADDR REGISTER       .100         INTERRUPT_LINE REGISTER       .101         INTERRUPT_PIN REGISTER       .101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LATENCY_TIMER REGISTER                                                                                 | .98                                                        |

| MEMBASEADDR0 REGISTER       .99         MEMBASEADDR1 REGISTER       .99         IOBASEADDR REGISTER       .99         SUBVENDORID REGISTER       .100         SUBSYSTEMID REGISTER       .100         ROMBASEADDR REGISTER       .100         ROMBASEADDR REGISTER       .100         INTERRUPT_LINE REGISTER       .100         INTERRUPT_PIN REGISTER       .101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | HEADER_TYPE REGISTER                                                                                   | .99                                                        |

| MEMBASEADDR1 REGISTER       .99         IOBASEADDR REGISTER       .99         SUBVENDORID REGISTER       .100         SUBSYSTEMID REGISTER       .100         ROMBASEADDR REGISTER       .100         CAPABILITIES POINTER       .100         INTERRUPT_LINE REGISTER       .101         INTERRUPT_PIN REGISTER       .101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        |                                                            |

| IOBASEADDR REGISTER       .99         SUBVENDORID REGISTER       .100         SUBSYSTEMID REGISTER       .100         ROMBASEADDR REGISTER       .100         CAPABILITIES POINTER       .100         INTERRUPT_LINE REGISTER       .101         INTERRUPT_PIN REGISTER       .101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                        | .99                                                        |

| SUBVENDORID REGISTER       100         SUBSYSTEMID REGISTER       100         ROMBASEADDR REGISTER       100         CAPABILITIES POINTER       100         INTERRUPT_LINE REGISTER       101         INTERRUPT_PIN REGISTER       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MEMBASEADDR0 REGISTER                                                                                  |                                                            |

| SUBSYSTEMID REGISTER       100         ROMBASEADDR REGISTER       100         CAPABILITIES POINTER       100         INTERRUPT_LINE REGISTER       101         INTERRUPT_PIN REGISTER       101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                        | .99                                                        |

| ROMBASEADDR REGISTER       .100         CAPABILITIES POINTER       .100         INTERRUPT_LINE REGISTER       .101         INTERRUPT_PIN REGISTER       .101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | мемBaseAddr1 Register<br>ioBaseAddr Register                                                           | .99                                                        |

| CAPABILITIES POINTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | мемBaseAddr1 Register<br>ioBaseAddr Register                                                           | .99                                                        |

| INTERRUPT_LINE REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MEMBASEADDR1 REGISTER<br>IOBASEADDR REGISTER                                                           | 99<br>100<br>100                                           |

| INTERRUPT_PIN REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MEMBASEADDR1 REGISTER                                                                                  | 99<br>100<br>100<br>100                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MEMBASEADDR1 REGISTER                                                                                  | 99<br>100<br>100<br>100<br>100                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MEMBASEADDR1 REGISTER                                                                                  | 99<br>100<br>100<br>100<br>100<br>100                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MEMBASEADDR1 REGISTER                                                                                  | 99<br>100<br>100<br>100<br>100<br>101<br>101               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MEMBASEADDR1 REGISTER                                                                                  | 99<br>100<br>100<br>100<br>100<br>101<br>101<br>101        |

| FABID REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MEMBASEADDR1 REGISTER                                                                                  | 99<br>100<br>100<br>100<br>100<br>101<br>101<br>101<br>101 |

| CFGSTATUS REGISTER              |     |  |  |

|---------------------------------|-----|--|--|

| CFGSCRATCH REGISTER             |     |  |  |

| NEW CAPABILITIES (AGP AND ACPI) |     |  |  |

| Capability Identifier Register  |     |  |  |

| AGP STATUS                      |     |  |  |

| AGP COMMAND                     |     |  |  |

| ACPI CAP ID                     |     |  |  |

| ACPI CTRL/STATUS                | 104 |  |  |

| 12. INIT REGISTERS              |     |  |  |

| STATUS REGISTER (0x0)           |     |  |  |

| PCIINITO REGISTER (0x4)         |     |  |  |

| LFBMEMORYCONFIG REGISTER (0xC)  |     |  |  |

| MISCINITO REGISTER (0x10)       |     |  |  |

| MISCINIT1 REGISTER (0x14)       |     |  |  |

| DRAMINITO REGISTER (0x18)       |     |  |  |

| DRAMINIT1 REGISTER (0x1C)       |     |  |  |

| AGPINITO REGISTER (0x20)        |     |  |  |

| VGAINITO REGISTER (0x28)        |     |  |  |

| VGAINIT1 REGISTER (0x2C)        |     |  |  |

| 2d_Command_Register (0x30)      |     |  |  |

| 2d_srcBaseAddr Register (0x34)  | 114 |  |  |

| 13. FRAME BUFFER ACCESS         |     |  |  |

| FRAME BUFFER ORGANIZATION       |     |  |  |

| Linear Frame Buffer Access      |     |  |  |

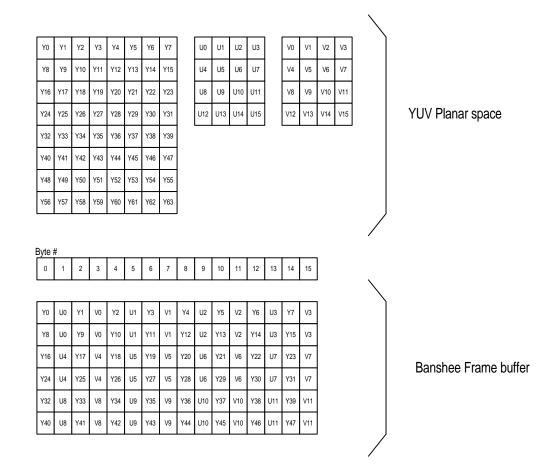

| YUV PLANAR ACCESS               |     |  |  |

| 14. ACCESSING THE ROM           |     |  |  |

| ROM CONFIGURATION               | 116 |  |  |

| ROM READS                       |     |  |  |

| ROM WRITES                      |     |  |  |

|                                 |     |  |  |

| 15. POWER ON STRAPPING PINS     |     |  |  |

| 16. MONITOR SENSE               |     |  |  |

| 17. HARDWARE INITIALIZATION     |     |  |  |

| 18. DATA FORMATS                |     |  |  |

### 1. Introduction

Banshee Graphics Engine is the second generation 3D graphics engine based on the original SST1 architecture. Banshee incorporates all of the original SST1 features such as true-perspective texture mapping with advanced mipmapping and lighting, texture anti-aliasing, sub-pixel correction, gouraud shading, depth-buffering, alpha blending and dithering. In addition to the SST1 features, Banshee will include a VGA core, 2D graphics acceleration, and support for Intel's AGP bus.

#### Features

- SST1 baseline features

- SST1 software compatible

- AGP / PCI bus compliant

- Native VGA core

- 2D acceleration Binary/Ternary operand raster ops Screen to Screen, Screen to Texture space, and Texture space to Screen Blits. Color space conversion YUV to RGB.

1:N monochrome expansion Rendering support of 2048x2048

- Integrated DAC and PLLs.

- Bilinear video scaling

- Video in via feature connector

- Supports SGRAM memories

#### Video-In:

- decimation

- support for interlaced video data

- support VMI, SAA7110 video connectors

- tripple buffers for video-in data

Video-Out:

- Bilinear scaling zoom-in (from 1 to 10x magnification in increments of 0.25x)

- decimation for zoom-out (0.25x, 0.5x, 0.75x)

- chroma-keying for video underlying and overlaying

- support for stereoscopic display

- hardware cursor

- double buffer frame buffers for video refresh

- DDC support for monitor communication

- DPMS mode support

- overlay windows (for 3D and motion video)

#### Resolutions

| VGA    |           |             |                   |              |

|--------|-----------|-------------|-------------------|--------------|

| MODE # | Mode Type | # of Colors | Native Resolution | Alpha Format |

| 0,1    | Alpha     | 16/256K     | 320x200           | 40x25        |

| 0,1    | Alpha     | 16/256K     | 320x350           | 40x25        |

| 0,1    | Alpha     | 16/256K     | 360x400           | 40x25        |

| 2,3    | Alpha     | 16/256K     | 640x200           | 80x25        |

| 2,3    | Alpha     | 16/256K     | 720x400           | 80x25        |

| 2,3    | Alpha     | 16/256K     | 320x200           | 80x25        |

| 4,5    | Graphics  | 4/256K      | 640x200           | 40x25        |

| 6      | Graphics  | 2/256K      | 120x350           | 80x25        |

| 7      | Alpha     | mono        | 320x200           | 80x25        |

| D      | Graphics  | 16/256K     | 640x350           | 40x25        |

| E      | Graphics  | 16/256K     | 640x350           | 40x25        |

| F      | Graphics  | mono        | 640x350           | 80x25        |

| 10     | Graphics  | 16/256K     | 640x350           | 80x25        |

| 11     | Graphics  | 2/256K      | 640x480           | 80x30        |

| 12     | Graphics  | 16/256K     | 640x480           | 80x30        |

| 13     | Graphics  | 256/256K    | 320x200           | 40x25        |

#### VESA

| MODE # | Mode Type | # of Colors | Native Resolution | Alpha Format |

|--------|-----------|-------------|-------------------|--------------|

| 100    | Graphics  | 256/256K    | 640x400           | 80x25        |

| 101    | Graphics  | 256/256K    | 640x480           | 80x30        |

### 2. Functional Overview

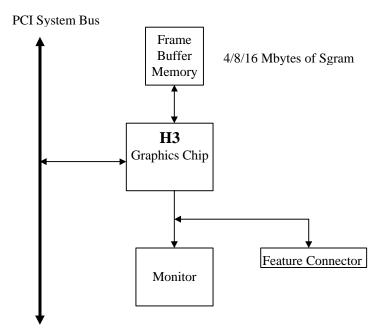

#### System Level Diagram

In its entry configuration, a Banshee graphics solution consists of a single ASIC + RAM. Banshee is a PCI Slave device, that receives commands from the CPU via direct writes or through memory backed fifo writes. Banshee includes an entire VGA core, 2D graphic pipeline, 3D graphics engine, texture raster engine, and video display processor. Banshee supports all VGA modes plus a number of Vesa modes.

#### **Architectural Overview**

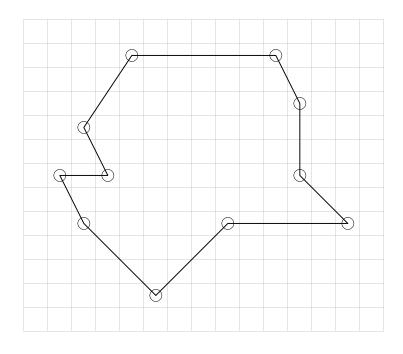

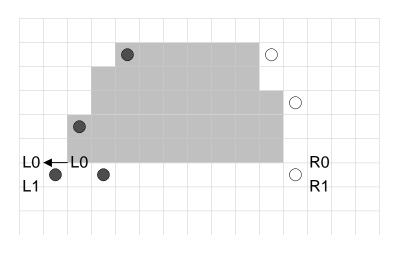

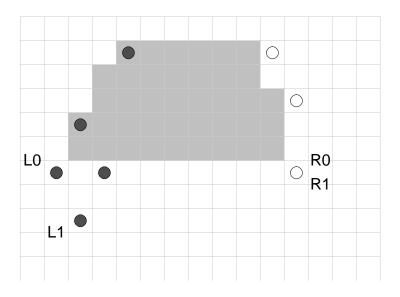

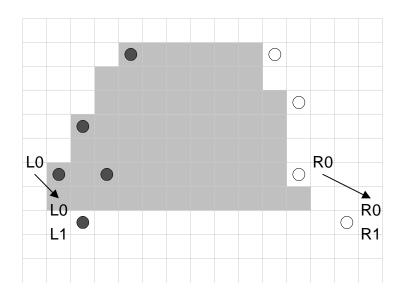

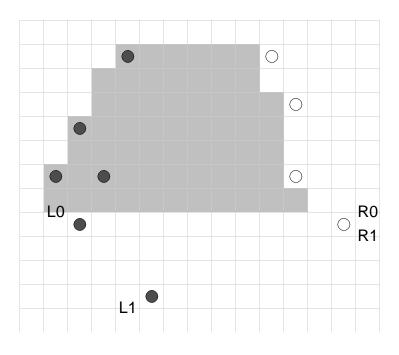

#### **Graphical Overview**

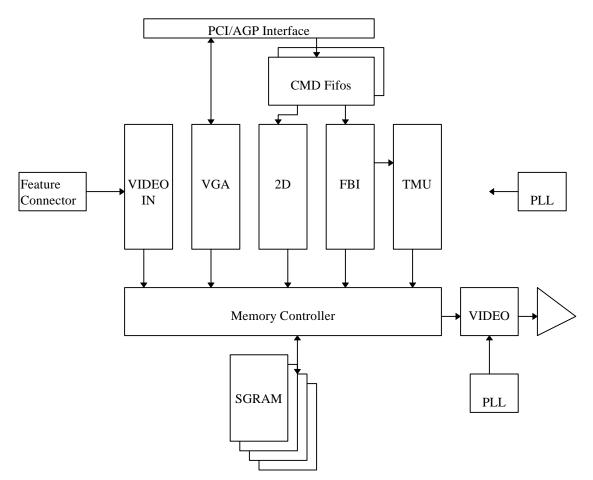

The diagram below illustrates the overall architecture of the Banshee graphics subsystem.

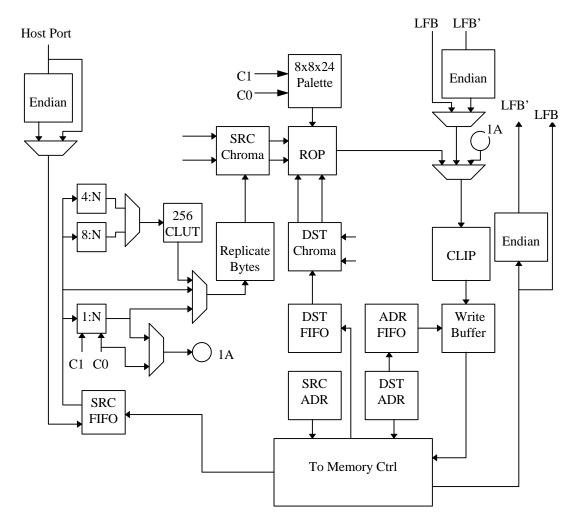

2D

#### **Functional Overview**

<u>Bus Support</u>: Banshee implements both the PCI bus specification 2.1 and AGP specification 1.0 protocols. Banshee is a slave only device on PCI, and a master device on AGP. Banshee supports zero-wait-state transactions and burst transfers.

<u>PCI Bus Write Posting</u>: Banshee uses a synchronous FIFO 32ntries deep which allows sufficient write posting capabilities for high performance. The FIFO is asynchronous to the graphics engine, thus allowing the memory interface to operate at maximum frequency regardless of the frequency of the PCI bus. Zero-wait-state writes are supported for maximum bus bandwidth.

<u>VGA</u>: Banshee includes a 100% IBM PS/2 model 70 compatible VGA core, which is highly optimized for 128 bit memory transfers. The VGA core supports PC '97 requirements for multiple adapter, and vga disable.

<u>Memory Architecture</u>: The frame buffer controller of Banshee has a 128-bit wide datapath with support for up to 100 MHz SGRAMs or SDRAMS. For 2D fills using the standard 2D bitBLT engine, 8 16-bit pixels are written per clock, resulting in a 800 Mpixel/sec peak fill rate. For screen clears using the color expansion capabilities specific to SGRAM, 64 bytes are written per clock, resulting in a 6.4 Gbytes/sec peak fill rate. The minimum amount of memory supported by Banshee is 4 Mbytes, with a maximum of 16 Mbytes supported.

<u>Host Bus Addressing Schemes</u>: Banshee occupies a combined 64 Mbytes of memory mapped address space, using two PCI memory base address pointers. Banshee also occupies 256 bytes of I/O mapped address space for video and initialization registers. The register space of Banshee occupies 6 Mbytes of address space, the linear frame buffer occupies 32 Mbytes of address space.

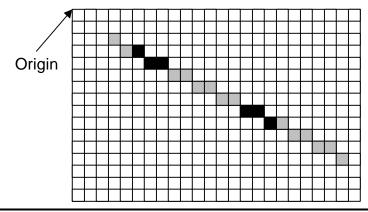

<u>2D Architecture</u>: Banshee implements a full featured 128-bit 2D windows accelerator capable of displaying 8, 16, 24, and 32 bits-per-pixel screen formats. Banshee supports 1, 8, 16, 24, and 32 bits-per-pixel RGB source pixel maps for BitBlts. 4:2:2 and 4:1:1 YUV colorspace are supported as source bitmaps for host to screen BitBlts. Banshee supports screen-to-screen and host-to-screen stretch BitBlts at 100 Mpixels/Sec. Banshee supports source and destination colorkeying, multiple clip windows, and full support of ternary ROP's. Patterned Bresenham line drawing with full ROP support, along with polygon fills are supported in Banshee's 2D core. Fast solid fills, pattern fills, and transparent monochrome bitmap BitBlts in 8 bits-per-pixel, 16 bits-per-pixel, and 32 bits-per-pixel modes.

# **<u>3. Banshee Address Space</u>**

#### MemoryBase0

| Memory Address        |                                            |

|-----------------------|--------------------------------------------|

| 0x0000000 - 0x007FFFF | I/O register remap (See I/O section below) |

| 0x0080000 - 0x00FFFFF | CMD/AGP transfer/Misc registers            |

| 0x0100000 - 0x01FFFFF | 2D registers                               |

| 0x0200000 - 0x07FFFFF | Reserved.                                  |

| 0x0800000 - 0x0BFFFFF | Reserved.                                  |

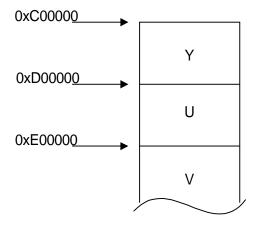

| 0x0C00000 - 0x0FFFFFF | YUV planar space                           |

#### Memory Base1

| Memory Address       |           |

|----------------------|-----------|

| 0x0000000 - 0x1FFFFF | LFB space |

#### I/O Base0

| I/O Address |                                           |

|-------------|-------------------------------------------|

| 0x00 - 0x03 | status Register                           |

|             | Initialization registers                  |

| 0x04 - 0x07 | pciInit0 register                         |

| 0x08 - 0x0b | sipMonitor register                       |

| 0x0c - 0x0f | lfbMemoryConfig register                  |

| 0x10 - 0x13 | miscInit0 register                        |

| 0x14 - 0x17 | miscInit1 register                        |

| 0x18 - 0x1b | dramInit0 register                        |

| 0x1c - 0x1f | dramInit1 register                        |

| 0x20 - 0x23 | agpInit register                          |

| 0x24 - 0x27 | tmuGbeInit register                       |

| 0x28 - 0x2b | vgaInit0 register                         |

| 0x2c - 0x2f | vgaInit1 register                         |

| 0x30 - 0x33 | dramCommand register (see 2D offset 0x70) |

| 0x34 - 0x37 | dramData register (see 2D offset 0x064)   |

| 0x38 - 0x3b | reserved                                  |

|             | PLL and Dac registers                     |

| 0x40 - 0x43 | pllCtrl0                                  |

| 0x44 - 0x47 | pllCtrl1                                  |

| 0x48 - 0x4b | pllCtrl2                                  |

| 0x4c - 0x4f | dacMode register.                         |

| 0x50 - 0x53 | dacAddr register.                         |

| 0x54 - 0x57 | dacData register.                         |

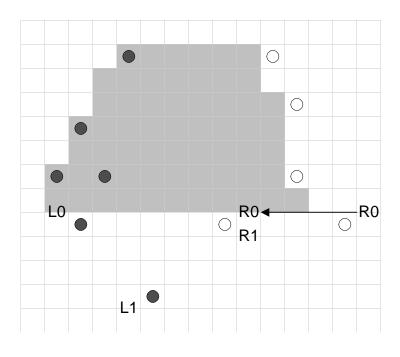

|             | Video Registers part I                    |