|

IMS B419

|

| Engineering Data |

FEATURES |

GENERAL DESCRIPTION |

|

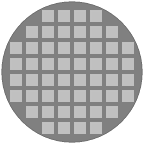

The IMS B419 incorporates the IMS G300B Colour Video Controller (CVC) with the IMS T800 32 bit Floating Point Transputer to form a high performance graphics system. Two Mbytes of four cycle DRAM provides a general purpose store sufficient to run large applications such as windowing environments. Two Mbytes of Video RAM provide arbitary screen resolutions up to a maximum of 1280 x 1024 8 bit/pixel with unrestricted screen formats at resolutions below this. INMOS is a member of the SGS-THOMSON Microelectronics group |

| 42 1482 00 | October 1990 |

The IMS B419 is one of a range of INMOS TRAnsputer Modules (TRAMs). TRAMs are board level transputers with a simple, standardised interface. They integrate processor, memory and peripheral functions allowing powerful, flexible, transputer based systems to be produced with the minimum of design effort1.

The IMS B419 implements a complete high performance graphics subsystem. The frame store consists of 2 Mbytes of dual ported Video RAM which supports displays of arbitrary resolution at 8 bit/pixel. The resolution of the system is programmable and is only limited by the CVC's maximum dot rate and the access time of the serial port on the VRAM. The IMS B419 supports a dot rate up to 100 MHz, the speed of the CVC. The CVC is configured by an IMS T800 which is provided with 2 Mbytes of 200ns cycle DRAM. This store is available for screen manipulation workspace and general program memory. The processor can be used to implement graphic primitives directly or as an intelligent channel, receiving image data from other transputers via its four bidirectional links at data rates of up to 6.8 Mbytes/sec. This makes the IMS B419 useful for applications as diverse as an add-on accelerator for a PC or a Macintosh, as part of an embedded system in industrial control, or as a graphics output for a 3D graphical supercomputer.

Screen sizes are set by writing to a few registers in the G300B CVC, and can be chosen to suit the application. Suppose, for instance, an 8.5 x 11 sheet of paper (in landscape), represented by a screen with 100 pixels per inch. This would need an 1100 x 850 display, a format not normally available from a hardware solution. The G300B gives a line width in multiples of 4 pixels, which makes it simple to produce this screen. As well as producing special screens such as 11 x 8.5, many of the standard screens can also be produced; indeed the user can switch between screen formats, the display clock frequency, and even the source of the input clock, all by simply changing the G300B registers and other registers on the board by software.

Some examples of possible screen sizes are given in Table 30.1. All the screens in the table are for 8 bits per pixel.

Screen Size Pixels Aspect Ratio Interlace

CGA 320 x 240 1.333 no

EGA 640 x 350 1.829 no

VGA 640 x 480 1.333 no

Enh VGA 800 x 600 1.333 no

Ext VGA 1024 x 768 1.333 no

11 x 8.5 1100 x 850 1.294 no

11 x 8.5 1164 x 900 1.293 no

1024 x 1024 1.0 no

1280 x 1024 1.25 no

A5 1216 x 860 1.414 no

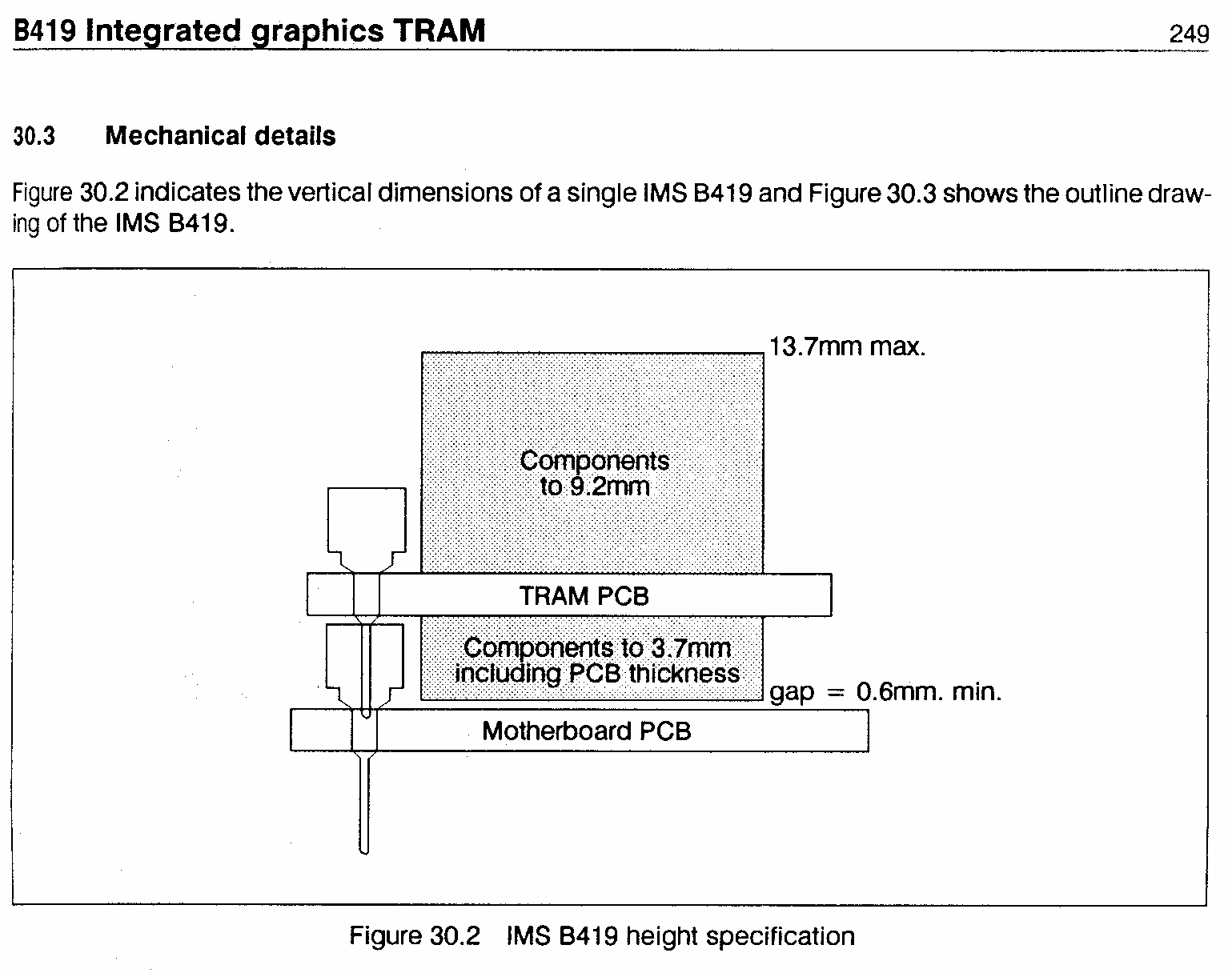

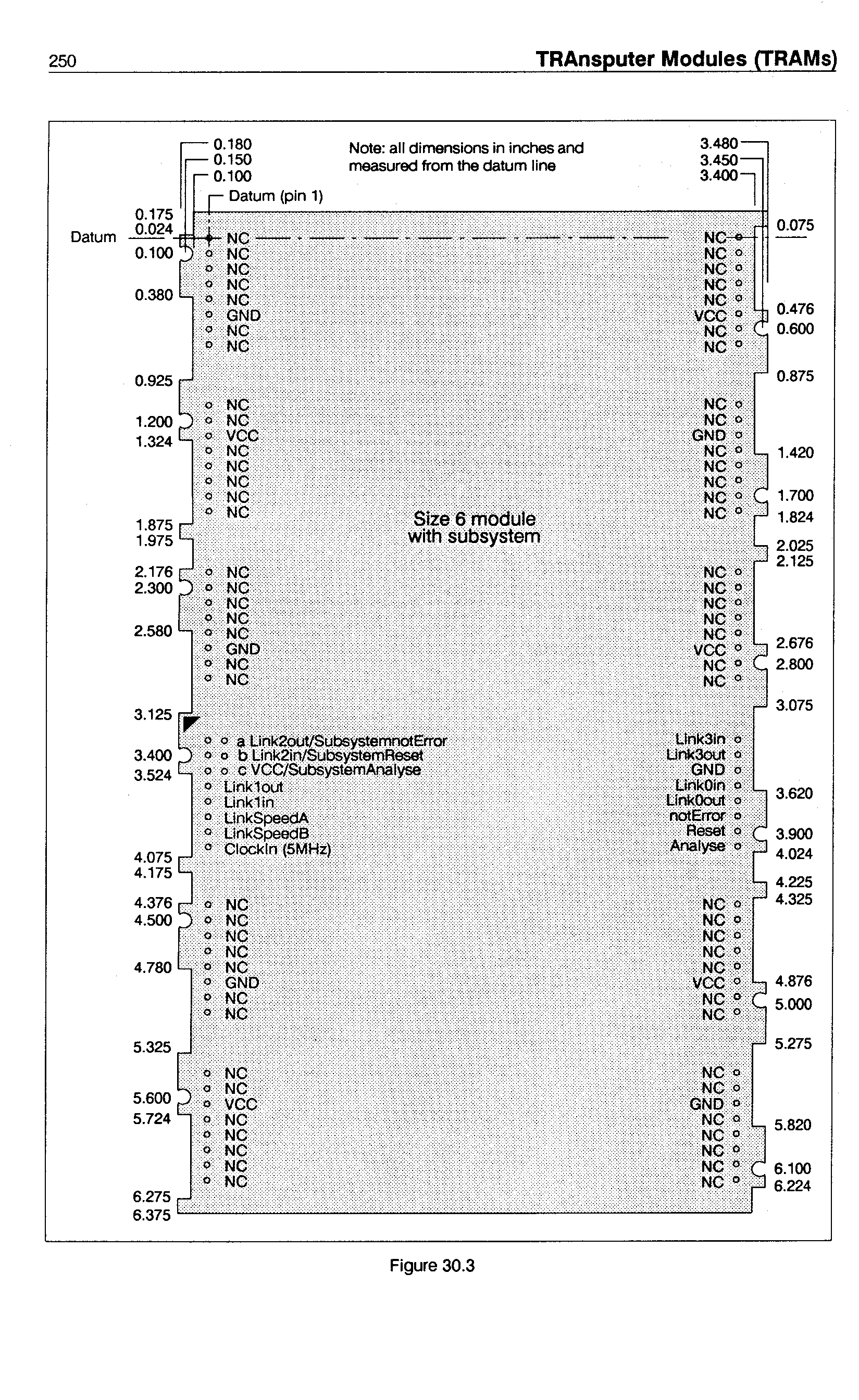

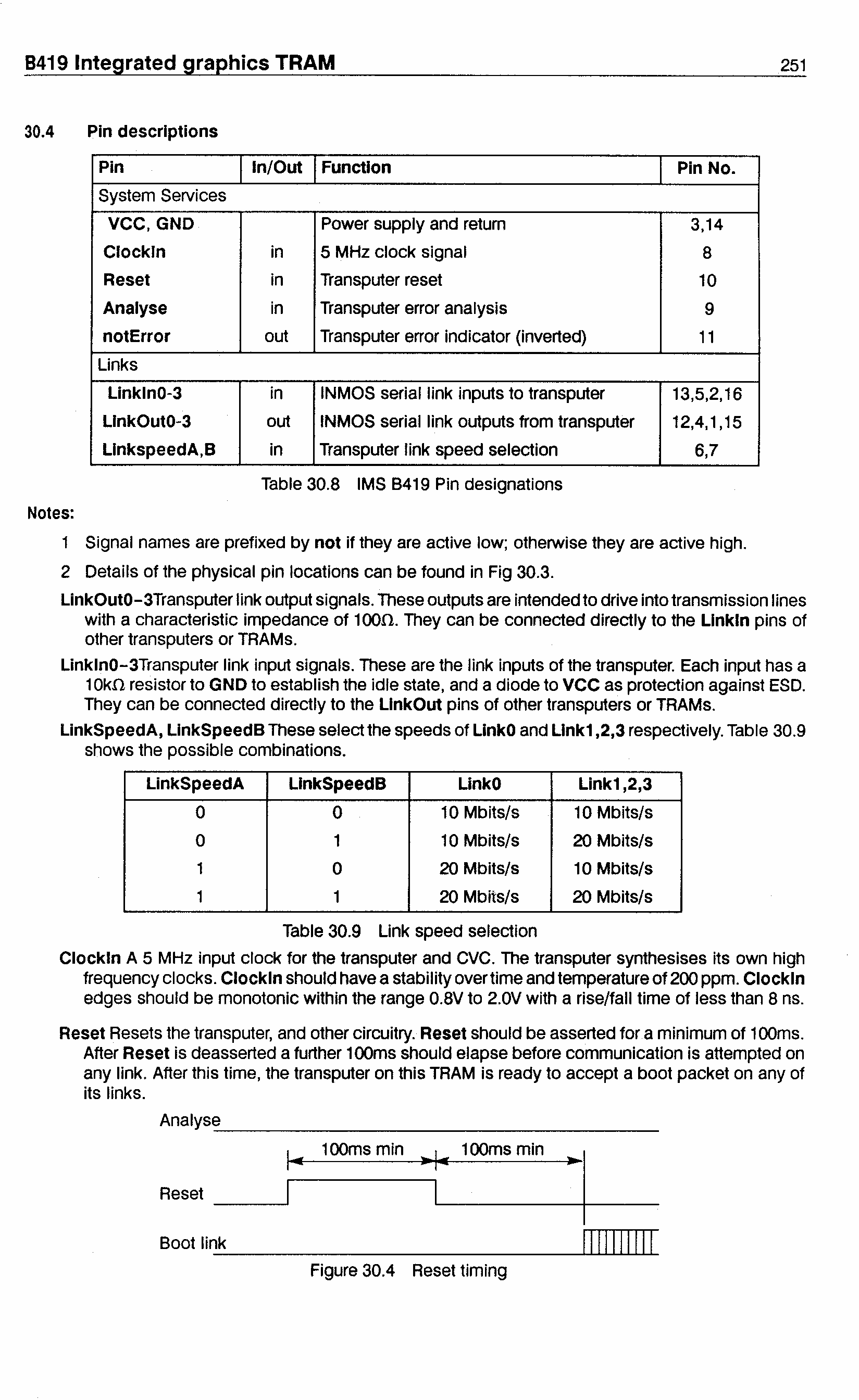

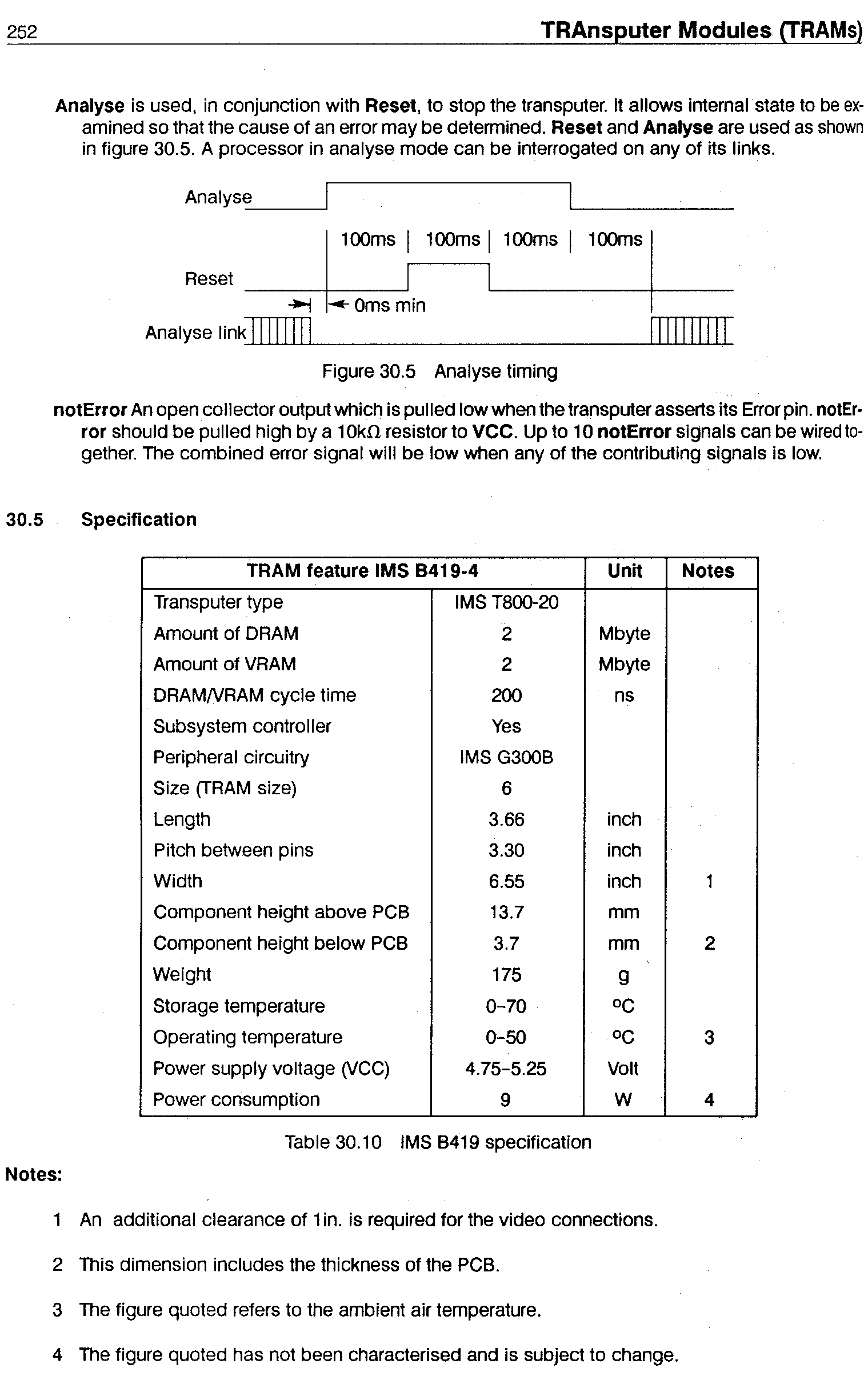

1. Further details of the TRAM/motherboard philosophy and the full electrical and mechanical specification of TRAMs can be found in technical notes Dual-In-Line Transputer Modules (TRAMs) and Module Motherboard Architecture which are included later in this databook. The Transputer Databook may also be required. This is available as a separate publication from INMOS (72 TRN 203 01).