# SPERRY UTS 30 CP/M Plus™

**Programmer's Technical Reference**

CP/M Plus™ is a trademark of Digital Research, Incorporated

This document contains the latest information available at the time of preparation. Therefore, it may contain descriptions of functions not implemented at manual distribution time. To ensure that you have the latest information regarding levels of implementation and functional availability, please consult the appropriate release documentation or contact your local Sperry representative.

Sperry reserves the right to modify or revise the content of this document. No contractual obligation by Sperry regarding level, scope, or timing of functional implementation is either expressed or implied in this document. It is further understood that in consideration of the receipt or purchase of this document, the recipient or purchaser agrees not to reproduce or copy it by any means whatsoever, nor to permit such action by others, for any purpose without prior written permission from Sperry.

FASTRAND, SPERRY, SPERRY UNIVAC, UNISCOPE, UNISERVO, and UNIVAC are registered trademarks of the Sperry Corporation. ESCORT, MAPPER, PAGEWRITER, PIXIE, SPERRYLINK, and UNIS are additional trademarks of the Sperry Corporation.

### Preface

i

This manual describes the unique characteristics of the SPERRY Universal Terminal System 30 (UTS 30) when operating in CP/M Plus<sup>™</sup> mode. The manual is divided into the following sections:

- Section 1 Introduction

- Section 2 Hardware Characteristics

- Section 3 I/O Port Definitions

- Section 4 Interrupt Interface

- Section 5 Keyboard Functions

- Section 6 CP/M Plus Screen Functions

- Appendix A ASCII Code Chart

This document is not intended to describe basic UTS 30 terminal operation, nor is it intended as a substitute for the Digital Research manuals describing CP/M Plus. Only features unique to SPERRY UTS 30 CP/M Plus are covered in this manual.

For information regarding basic UTS 30 terminal operation, refer to the Sperry UTS 30 Single Station Operator's Reference, UP–9798. Additional publications which provide related information include the current versions of the following documents:

UTS 30 CP/M Plus<sup>™</sup> Release Description, UP–9838.2

UTS 30 CP/M Plus<sup>™</sup> Operator's Guide, UP-9839

UTS 4000 CP/M Plus<sup>™</sup> User's Guide, UP-9847

UTS 4000 CP/M Plus<sup>™</sup> Programmer's Utilities Guide, UP-9848

UTS 4000 CP/M Plus<sup>™</sup> Programmer's Guide, UP-9849

UTS 4000 CP/M Plus<sup>™</sup> Symbolic Instruction Debugger (SID<sup>™</sup>) Reference Manual, UP–9844

UTS 4000 CP/M Plus<sup>™</sup> Symbolic Instruction Debugger (SID<sup>™</sup>) Command Summary, UP–9867

Related Sperry Publications

CP/M Plus™ and SID™ are trademarks of Digital Research, Incorporated

# **Contents**

### PREFACE

### CONTENTS

### 1. INTRODUCTION

| 1.1. | GENERAL DESCRIPTION | 1–1 |

|------|---------------------|-----|

|      | SOFTWARE            |     |

| 1.3. | HARDWARE            | 1–2 |

### 2. HARDWARE CHARACTERISTICS

|    | 2.1.   | HARDWARE FUNCTIONS AND SPECIFICATIONS 2-   | -1 |

|----|--------|--------------------------------------------|----|

|    | 2.2.   | COMMUNICATIONS SYSTEM 2-                   | -2 |

|    | 2.2.1. | Serial Communications                      | -3 |

|    | 2.2.2. | Modem Communications 2-                    | -3 |

|    | 2.2.3. | Terminal Multiplexer 2-                    | -5 |

|    | 2.2.4. | Direct Connection 2-                       | -6 |

|    | 2.3.   | MEMORY CONFIGURATION 2-                    | -6 |

|    | 2.4.   | AUXILIARY RS-232 ASYNCHRONOUS INTERFACE 2- | -8 |

| 3. | I/O PO | RT DEFINITIONS                             |    |

|    | 3.1.   | GENERAL PORT DEFINITIONS                   | -1 |

|    | 3.2.   | I/O PORT 4A                                | -6 |

|    | 3.3.   | I/O PORT 67                                | -8 |

|    | 3.4.   | I/O PORT 48                                | -8 |

|    | 3.5.   | I/O PORT 49                                | 10 |

| 4. | INTER  | RUPT INTERFACE                             |    |

|    | 4.1.   | GENERAL DESCRIPTION                        | -1 |

### 5. KEYBOARD FUNCTIONS

| 5.1. | CP/M PLUS MODE KEYS         | 5–1 |

|------|-----------------------------|-----|

| 5.2. | OPERATIONAL CHARACTERISTICS | 5–2 |

RESTRICTIONS ...... 4–2

4.2.

### 6. SCREEN FUNCTIONS FOR CP/M PLUS MODE

|        | SCREEN DISPLAY                     |

|--------|------------------------------------|

| 6.2.   | DEFINITIONS                        |

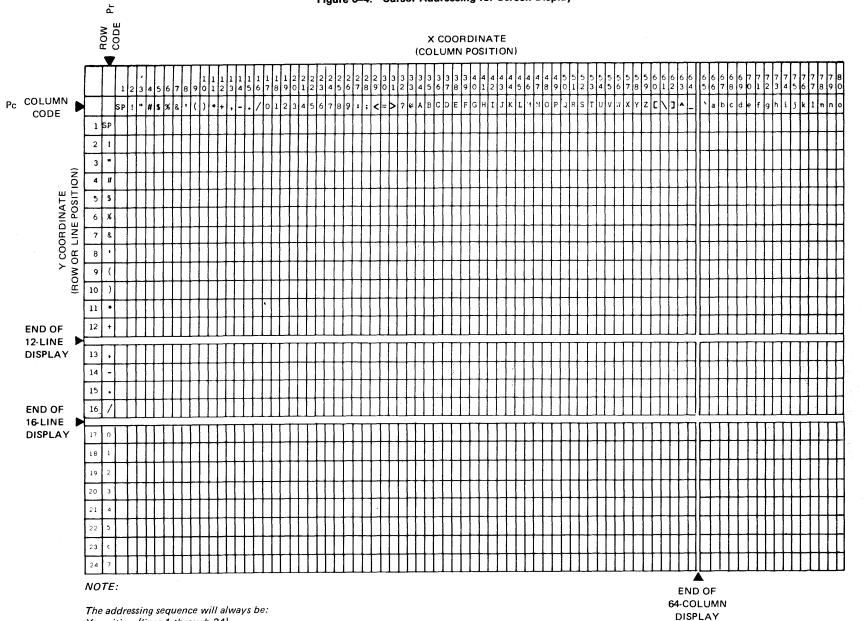

| 6.3.   | CURSOR POSITIONING                 |

| 6.3.1. | Cursor Address Sequence 6-4        |

| 6.3.2. | Cursor Address Codes               |

| 6.4.   | SCREEN CONTROL                     |

| 6.4.1. | Basic Screen Control Functions 6–8 |

| 6.4.2. | Special Emphasis Functions         |

| 6.4.3. | Emphasis Character Sequence        |

| 6.4.4. | Other Screen Functions             |

### APPENDIX A. ASCII CHART

### **USER COMMENT SHEET**

### **FIGURES**

| 1–1.                                         | Relationship Between CCP, BIOS, and BDOS 1-1                                                                                                                                                                                                                  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

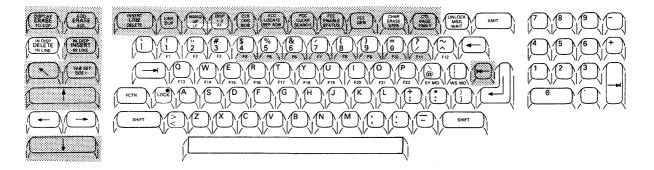

| 5–1.                                         | Keys Used in CP/M Plus Mode (Low-Profile Keyboard)                                                                                                                                                                                                            |

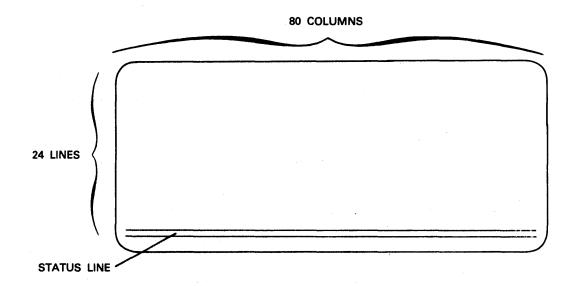

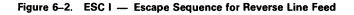

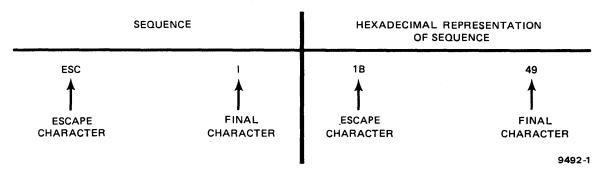

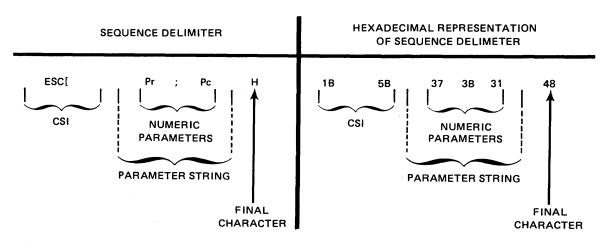

| 6–1.<br>6–2.<br>6–3.<br>6–4.<br>6–5.<br>6–6. | CP/M Screen Display6–1ESC I-Escape Sequence for Reverse Line Feed6–3CSI Pr;Pc H-ANSI Sequence for Direct Cursor Positioning6–3Cursor Addressing for Screen Display6–6An Example of Expanded Special Emphasis Byte6–12Combined Special Emphasis Characters6–13 |

| TABL                                         | ES                                                                                                                                                                                                                                                            |

| 2–1.<br>2–2.                                 | UTS 30 Functions and Abbreviated Specifications                                                                                                                                                                                                               |

| 3–1.                                         | I/O Port Assignments                                                                                                                                                                                                                                          |

| 4–1.                                         | Interrupt Vector Table 4–2                                                                                                                                                                                                                                    |

| 5–1.                                         | Normal Operating Characteristics of Keys in CP/M Plus Mode                                                                                                                                                                                                    |

| 6–1.<br>6–2.                                 | Cursor Positioning Sequences                                                                                                                                                                                                                                  |

# 1. Introduction

### **1.1. GENERAL DESCRIPTION**

CP/M<sup>®</sup> is a disk-operating system designed to operate as a stand-alone microcomputer system supporting peripheral and file management.

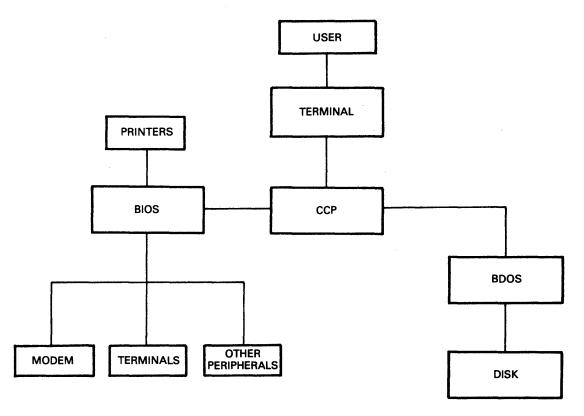

The CP/M operating system consists of three major components: the Console Command Processor (CCP), the Basic Disk Operating System (BDOS), and the Basic Input and Output System (BIOS). See figure 1-1.

CP/M® is a registered trademark of Digital Research, Incorporated

The CCP interprets commands entered at the keyboard, channeling appropriate tasks to the various resources available through BIOS and BDOS. The BIOS routines manage the flow of data to and from the various devices connected to the system. The BDOS routines manage the disk files.

### 1.2. SOFTWARE

With SPERRY UTS 30 CP/M Plus, you can take advantage of the wide variety of CP/M-based software packages available. You can also use numerous computer program development languages as well as utilities for the construction, storage, and editing of application programs.

CP/M Plus utilities provide file transfer between peripherals, unattended batch processing, a string-oriented text editor, an Intel-compatible 8080 assembler, hexadecimal display of file contents, conversion of hexadecimal files to CP/M Plus executable files, time and date stamping, and password protection.

SPERRY UTS 30 CP/M Plus also provides several special SPERRY CP/M utilities that take advantage of advanced capabilities of the UTS 30 hardware. These utilities prepare and copy diskettes, configure UTS 30 peripheral devices for use with CP/M, generate and load limited graphics and custom character sets, and reassign default keyboard functions.

### 1.3. HARDWARE

The SPERRY UTS 30 CP/M Plus system requires a programmable UTS 30 terminal and an 8439 double-sided diskette subsystem with at least one drive. In addition, the optional loadable character set hardware must be installed if custom character sets are to be generated and loaded.

The system also supports one of the following SPERRY printers:

- 0797 serial dot matrix printer

- 0798 serial dot matrix printer

- Model 31 correspondence quality printer

- Model 35 graphics printer

- Model 25 serial dot matrix printer

Refer to the UTS 30 CP/M Plus operator's guide, UP-9839, for instructions on configuration of peripheral devices for use with CP/M Plus.

# 2. Hardware Characteristics

### 2.1. HARDWARE FUNCTIONS AND SPECIFICATIONS

Many aspects of the CP/M Plus implementation are dependent on specific hardware characteristics of the UTS 30 terminal. Table 2-1 lists the functions and abbreviated specifications for the UTS 30.

| Table 2-1. | UTS 30 | Functions | and | Abbreviated | Specifications | (Part | 1 o | of 2) |

|------------|--------|-----------|-----|-------------|----------------|-------|-----|-------|

|            |        |           |     |             |                |       |     |       |

| Function       | Specification                                                                                                                                                                                                                                                                                                                                                 |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor | Z80 CPU (2892668), 4.000 MHz<br>clock<br>No-wait states for local memory<br>Vectored interrupts for peripherals<br>Reset or parity generated NMI                                                                                                                                                                                                              |

| Peripheral LSI | 78530 (2893610), serial<br>communication controller<br>MK3801 (2893942), serial/timer/<br>interrupts<br>HD6845 (2893939), CRT controller                                                                                                                                                                                                                      |

| Peripherals    | Serial interface keyboard<br>Serial communications channel<br>– full duplex<br>– asynchronous or synchronous<br>– dual baud rate generator<br>– terminal multiplexer 5000 feet<br>max<br>– direct connect 200 feet max<br>– baud rates to 19.2K baud<br>Auxiliary RS-232 (DCE end), up to<br>900 baud async, full duplex<br>RS-232 standard DCE pinout subset |

| Memory         | 128K RAM accessed via address-<br>dependent pages<br>8K ROM overlay<br>256 nibbles non-volatile RAM<br>Loadable 512 character generator<br>with all 10 x 16 dots addressable                                                                                                                                                                                  |

| Function           | Specification                                                                                                                                                                                                                               |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Memory     | 32 addressable 80-character rows<br>that can be located anywhere<br>in memory<br>8-bit read/write register for<br>character attribute manipulation                                                                                          |

| Display Attributes | 7 visual character attributes for each character of the display                                                                                                                                                                             |

| Display Format     | Three Z80 bus interface<br>connections<br>– one for full PC board (graphics)<br>– two for small features<br>80 columns by 25 lines standard<br>selectable lines from 1 to 32<br>Standard characters, 7 by 9 in 10<br>by 15 character matrix |

| Indicators         | Display separator (dotted horizontal<br>line)<br>Audio alarm with programmable<br>frequency<br>No straps<br>Programmable options stored in<br>non-volatile RAM                                                                              |

| Keylock            | 3-position keylock input for terminal and parameter locking                                                                                                                                                                                 |

### Table 2–1. UTS 30 Functions and Abbreviated Specifications (Part 2 of 2)

### 2.2. COMMUNICATIONS SYSTEM

The serial communication controller (SCC) and serial/timer/interrupt controller (STI) combine to support communications. The critical lines, receive data, transmit and receive clock, and clear-to-send B and A are serviced by differential line receivers to reduce noise and improve sensitivity for terminal multiplexer operations. The rest of the signals are lower grade RS-232 receivers. The differential receivers are not biased so that a float results in an indeterminate output. The RS-232 receivers bias the signals to the off state, even though some noise susceptibility exists. The keyboard data is differential and is handled by a differential receiver. The drivers are RS-232 except the transmit data driver, which is assisted to improve capacitive drive capability for long distances on a multiplexer connection. Direct connect is achieved by switching drivers onto the transmit and receive clock lines via a mechanical relay. These drivers do not have extensive drive capability, but should handle 1000 feet of shielded cable. The interface is specified at 200 feet. Longer distances may be permitted in some cases, but you must accept the possibility that it will not operate with an adequate error rate unless the baud rate is reduced.

### 2.2.1. Serial Communications

The serial communications controller (SCC) integrated circuit (IC) uses channel A for host communications. The SCC is a flexible device, similar to the Z80<sup>TM</sup> SIO used on the UTS 20 and UTS 40, but with added capabilities. (Details of these capabilities are covered in separate specifications for the IC and in Zilog Corporation vendor literature.) Specific capabilities of the SCC and the applications related to the UTS 30 are discussed in detail in this section.

The other serial communications IC, the serial/timer/interrupt (STI) controller also supports some host communication functions. Channel B of the SCC handles the serial keyboard data. The communications section of the STI handles the auxiliary RS-232 interface for devices. Because these two ICs form an intimate peripheral control group, they are combined in the following paragraphs.

Where reasonable, signals that interface to the ICs are titled by the IC pin name; while actual details of the manipulation of the pins and signals are defined in the specification for that particular IC.

### 2.2.2. Modem Communications

Most of the modem communication functions are handled by the SCC channel A. The SCC operates in synchronous or asynchronous mode. When asynchronous mode is used, the internal baud rate generator is used. The basic clock frequency is 4.000MHz. The internal receiver divider should be set to the highest value consistent with the baud rate generator. A division by 16 can result in higher error rates than 32 or 64. The maximum asynchronous baud rate is 19.2K, achieved by setting the baud rate generator to divide by 13 and the receiver to divide by 16. The small frequency error is of little consequence.

The signals are supported via the communication cables, features F8209, F8201, and F8211, and are discussed in the following paragraphs.

The transmit data signal, CCITT-103, is routed to the SCC TxDA pin 15. Depending upon whether the mode is synchronous or asynchronous, the clock can be programmed to come from the host modem or internally.

*Receive from Host* The receive data signal, CCITT–104, is routed to the SCC RxDA pin 13.

I/O port 41. CTS is also routed to STI interrupt 5.

Request-to-send

pin 17.

Clear-to-send

Transmit to Host

Carrier Detect

The carrier detect (CD) signal, CCITT-109, is routed to the communications status register port 42, bit 1. This line (CD) is logically ORed with CTS and routed through a 30 microsecond delay. This delay

The request-to-send (RTS) signal, CCITT-105, is routed to the SCC RTSA

The clear-to-send (CTS) signal, CCITT-106, is routed to the communication status register port 41, bit 0. The register must be strobed by an I/O read or write of port 42. The status is then read via

<sup>&</sup>lt;sup>™</sup>Z80 is a registered trademark of Zilog Corporation.

UP-9840

generates a high true input at the STI interrupt 7 (pin 15) input. Thus, 30 microseconds after the assertion of CTS or CD, an interrupt occurs. The delay also strobes the register at port 42, latching all the bits. This interrupt function is used primarily for terminal multiplexer handshaking, but can also serve modem operation. A positive interrupt at STI interrupt 7 occurs when CD or CTS asserts (after 30 microseconds); a negative interrupt at STI interrupt 7 occurs when CD and CTS negate (with negligible delay, the 30 microsecond delay does not operate on negation).

The data-set-ready signal, CCITT-107, is routed to input port 42, bit 7.

The transmit clock signal, CCITT-114, is routed to the SCC TRxCA pin 14. This is a bidirectional line. When in the input mode, it receives the timing for transmit data. It is used in the output mode for direct connect mode, and generates both transmit and receive clocks. This line is XORed with the output of I/O port 49, bit 3, for use with the RS-232/V.24 test adapter 2826629. The clocks generated for direct connect mode are out of phase and are used for loopback with the test adapter. The clock must be inverted via I/O port 49, bit 3 in order to generate the proper clock polarity at the SCC.

Receive Clock

Data Terminal Ready

Data-Set-Ready

Transmit Clock

The receive clock signal, CCITT-115, is routed to the SCC RTxCA pin 12. When in direct connect mode, this line is driven indirectly by the TRxCA pin.

The data terminal ready (DTR) signal, CCITT-108.2, is routed to I/O port 49, bit 4. This port bit also turns on an amber light, visible from outside the terminal, that indicates the terminal is operational. Turning off the line will extinguish the light and make the operator aware of a fault condition. This bit and all bits in the port are reset when any reset occurs; therefore, DTR is negated by the reset switch, and some modems are disconnected.

This signal also goes to the DTR timer. The timer is not activated until the following conditions are met:

DTR must be asserted.

Port 49, bit 3 must be equal to 1.

When these conditions are met, the timer remains set for 128 cycles of the vertical synchronous from the CRTC, then asserts at the CTS A pin on the SCC, and inhibits DTR, the light, and RTS A. The timer is retriggered, or kept running, by any interrupt acknowledge by the CPU (IORO-M1 cycle) that prevents timeout. This system provides for the event that the microcode ceases to function when operating in an interrupt environment, and the DTR is asserted. Microcode should provide a timer that prevents the RTS and DTR lines from being active too long, locking up the communication system or the telephone line. The DTR timer is provided to back up the microcode timer. The DTR timer does not function if port 49, bits 3 or 4 are negated, or the CRTC is not generating synchronous pulses. The CRTC must be activated (and vertical synchronous generated) when DTR is asserted and the timer is required.

2–4

**Ring Indicator**

Data Rate Select

The ring indicator (RI) signal, CCITT-125, is routed to the STI interrupt 0. This interrupt should be enabled only when RI is expected, since modems and other equipment generate spurious signals on this line.

The data rate select signal, CCITT-112, is routed to the SCC DTR/REQA pin 16. It serves as the RTS-B signal on the SPERRY terminal multiplexer interface. No other CCITT signals are supported on this interface except grounds 101 and 102. The RS-232 and V.24 cables provide for proper routing of the signals on this interface. The use of other cables is not necessarily nonfunctional, but may cause erratic operation on some equipment. The terminal multiplexer cable is suitable for communications with the SPERRY terminal multiplexer described in the following paragraphs.

### 2.2.3. Terminal Multiplexer

Terminal multiplexer operation is supported via terminal multiplexer cable feature F8217 (with exceptions noted in this section). Operation on the terminal multiplexer is allowed up to 5000 feet at 9600 baud, or 2000 feet at 19.2K baud. A 10000-foot operation is allowed at 4800 baud. The transmit data driver has an output impedance of about 50 ohms, allowing long distances for terminal multiplexer systems.

Handshake with the terminal multiplexer is facilitated by control of RTS A, RTS B, and transmit data. The inputs CTS A, CTS B, and transmit clock are latched in a register, and generate only one interrupt to the STI (0) when they are latched by an assertion from CTS A or CTS B. The data remains in the latch until both CTS A and CTS B negate and one of them asserts again. An interrupt occurs when both negate (1) if so programmed. The latch is strobed about 30 microseconds after the assertion of CTS A or CTS B. This guarantees that the state of send clock during this operation is valid, including cable and receiver skew. If a glitch occurs on CTS A or CTS B while it is asserting, the latch stores the status after the glitch, possibly losing the transmit clock status.

The lines transmit data, receive data, transmit clock, and receive clock are the same as the modem interface to the SCC.

Clear-to-send A and clear-to-send B are routed to an input I/O register at I/O port 42. Transmit clock is also routed to this port. These three lines are latched 30 microseconds after assertion of CTS A or CTS B. Also, at the 30 microsecond delay point, SCC interrupt input 7 is driven high, generating an interrupt and status, indicating that the terminal multiplexer has issued status and is available in port 42 (bit 0 = CTSA, bit 1 = CTS B, and bit 2 = transmit clock). When the terminal multiplexer has negated both CTS A and CTS B, the STI interrupt 7 input goes low. The status in the register is still valid. When the terminal multiplexer again asserts CTS A or CTS B, the status is relatched after 30 microseconds, generating a positive transition at STI interrupt 7. The microcode has a limited time to capture the status, before the terminal multiplexer reasserts the CTS lines. Request-to-send A is routed to the SCC RTSA pin 17.

Request-to-send B is routed to the SCC DTR/REQA pin 16.

Request status to the terminal multiplexer requires that the transmit data line be either marking or spacing (1 or 0) when RTS is asserted. The SCC internal register 5 can be used for this purpose. The output is marking (1) when the transmitter is not enabled; the output is spacing (0) when the transmitter is enabled and the command "send break" is issued.

### NOTE:

The send break function of the SCC requires transmit clock. It cannot be guaranteed when break is required (on and off): the internal baud rate generator should be used during the break duration.

Modem lines not used for terminal multiplexer operation should have interrupts disabled to prevent noise from generating spurious interrupts.

### 2.2.4. Direct Connection

Operation up to 200 feet and 19.2K baud is provided by generating the required transmit and receive clocks from the SCC internal baud rate generator. The clocks are both routed from the SCC TRxC pin 14. The external circuits must also be programmed to drive the clocks. Set I/O port 49, bit 2 = 1. When operating in this mode, interrupts should be disabled for all modem control lines, since they are unterminated and generate spurious inputs. The SCC internal register 11 must be set to generate the clock at the TRxC pin. The clock input is 4.000 MHz, used in calculating the baud rate values for registers 12 and 13 in the SCC.

Direct connection at distances longer than 200 feet can be accomplished by reducing the baud rate or operating with a direct connection module (DCM). When the DCM is used, it generates the clocks. It does not necessarily terminate all control lines, so unused lines should not be interrupt enabled. J8 interfaces to the communications line via IC's 2892905, 2899272, 3007893, and 3007894.

### 2.3. MEMORY CONFIGURATION

Specifications regarding memory configuration are described in the following paragraphs.

Main Memory Architecture The main memory consists of 128K bytes of dynamic RAM. The RAM is organized so that the CPU has access to all 128K of memory in a page-swapping scheme. The memory is divided into a main bank and a user bank, each 64K bytes deep, selected by address bit 16. Address bit 16 is generated using an 8-bit register (I/O port 4B). The bits in this register become address bit 16 (A16) for each of 8 address blocks, 8K bytes each, resulting in 16 pages. Eight at a time are selected. Address bits 15, 14, and 13 determine which bit is A16. If the three bits are zeros, port 4B bit 0 is A16. This relationship is shown in table 2-2.

| Register Bit |      |            |  |  |

|--------------|------|------------|--|--|

| Address Page | Bank | (Port 4B)* |  |  |

| E000         | user | D7 = 1     |  |  |

| C000         | main | D6 = 0     |  |  |

| A000         | main | D5 = 0     |  |  |

| 8000         | user | D4 = 1     |  |  |

| 6000         | user | D3 = 1     |  |  |

| 4000         | main | D2 = 0     |  |  |

| 2000         | user | D1 = 1     |  |  |

| 0000         | main | D0 = 0     |  |  |

Table 2-2. Memory Addressing Architecture

\*Register 4B has been written to 9A.

Writing port register 4B will cause the RAM map to switch during the I/O instruction. Four control bits are provided to allow microcode to reside in any address space as well as access or jump to any other address space.

Read only memory (ROM) of 8K bytes is located onboard (addressed at 0000), independent of the state of the user bank control logic. The ROM can be switched in and out via I/O port 48, bit 0. If bit 0 = 0, ROM is selected. If bit 0 = 1, ROM is not selected. The RAM at the ROM address space can always be written, even if ROM is selected. A write to ROM actually goes to RAM. The bit is delayed until the beginning of the second M1 cycle, allowing programs to jump in and out of ROM from RAM at the same address. Since write is allowed, loading data into RAM while ROM is selected is simple. In order to read RAM at the ROM address using ROM code (POC), address bit 13 must be inverted via I/O port 4A, bit 1.

Non-volatile RAM A RAM that stores data with power off is provided for parameter storage. This RAM is actually two memories in one IC, a conventional static RAM and an electrically alterable ROM (EEROM). The RAM data is transferred into EEROM when it receives a store command. This command is issued by hardware when a power fail warning occurs. This warning occurs at least 10 milliseconds before power drops, and the system is reset. An interrupt input to the SCC DCDA pin indicates that the warning has started a store cycle. The NVR is unavailable to the CPU for a maximum of 10 milliseconds. The EEROM is able to execute 5K store cycles before wearout. Wearout aging occurs only if a bit in EEROM must change states. Store cycles without changed bits do not age these bits. The 5K store cycles should be adequate for the life of the terminal, since the cycles occur only on power down. It is reasonable to use the NVR for error logs and control page parameters, as well as basic terminal parameters. The NVR is organized in 256 fourbit nibbles. If it is selected by setting I/O port 48, bit 7, it is addressed at the beginning of attribute display memory.

ROM

Address 16 Generation Address 16 is needed by the CPU to access 128K of RAM. An ordinary I/O controlled paging mechanism is not suitable for all applications and a RAM mapping mechanism is not used. Instead, an 8-bit register with a bit assigned for each of 8 memory address blocks is incorporated. This register output goes to an 8:1 multiplexer. The output of the multiplexer is passed through a buffer and becomes address 16. The multiplexer is selected by address bits 13, 14, and 15. These select 8K blocks of memory. Thus, if the address bits point to bit 3 of the 8-bit register, that bit determines A16.

Two control bits in port 4A serve to enable the multiplexer, and therefore, address 16. One bit is delayed by 4 MI assertions and the other is immediate.

Address 13 is inverted as a result of three possible conditions. Each is a special purpose function. One condition controlled by port 4A, bit 0 is used by the microcode to create a two-state machine for use in the screen bypass mode, where there are two virtual terminals created. This bit inverts address 13 for all addresses at the display location and above. Therefore all display information, pointers, and data buffers in RAM can be selected by changing the state of port 4A, bit 0 without changing or keeping track of addresses in the CPU. This bit has no other practical use.

Address 13 is also inverted conditionally on the state of address 16, in order to allow microcode to manipulate RAM data, regardless of the microcode location doing the manipulation. The inversion is accomplished by the Boolean expression:

# A13 = A13c XOR ((A not < DSR x 4A0) + (A16 not x 4A1 x r) + (A16 x 4A2 x r))

where:

A13 = external address bit 13

A13c = CPU address 13

- A = CPU address

- **DSR** = address pointed to by the DSR

- 4A0 = port 4A bit 0, etc.

- = any address not in ROM space

### 2.4. AUXILIARY RS-232 ASYNCHRONOUS INTERFACE

This interface is connected both to the SCC channel B control lines and the STI serial channel. The STI does not buffer data, so it is not used for the keyboard which sends bytes in pairs. When the STI receiver is operating, it is important to read the data from the receive register before the next byte is assembled or data is lost. Thus, it may be necessary to force the keyboard to wait if the STI receiver is operating. The keyboard internally buffers up to eight keystrokes if the SCC channel B receiver still has data in it.

Address 13 Manipulation Aux transmit data (from the device) is routed to the STI serial input pin 38.

Aux receive data (to the device) is routed to the STI serial output pin 37.

The asynchronous clock input to STI pins 36 and 39 is driven by SCC TRxCB pin 26. Thus the SCC internal baud rate generator for channel B serves as the generator for the STI channel. The maximum baud rate for this channel is 9600, since the input to the STI cannot be driven at twice that speed.

Aux request-to-send data is routed to the SCC input DCDB pin 22.

Aux clear-to-send data is routed to the SCC output RTSB pin 23.

Aux data set ready is routed to the SCC output DTR/REQB pin 24. This line must be negated prior to power off to prevent the printer from accumulating garbage in its buffer, as one piece of junk might be a CR. The power fail interrupt can be used to negate the line.

Aux data terminal ready is routed to the SCC input SYNCB pin 29.

Aux K-ready is routed to the SCC input CTSB pin 22.

Aux carrier detect is not supported.

# 3. I/O Port Definitions

### 3.1. GENERAL PORT DEFINITIONS

The I/O port bit assignments used in the UTS 30 are described in the following table. For each bit position described, the true or assert condition is 1. In some cases, the negate or 0 state is identified.

| Table 3–1. I/O Bit Port Assignments (Pa | rt 1 | of 6) |  |

|-----------------------------------------|------|-------|--|

|-----------------------------------------|------|-------|--|

| Address | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00*     | ln/Out    | SCC channel B control registers<br>DTR line drives DSR (AUX)<br>RTS line drives CTS (AUX)<br>DCD line driven by RTS (AUX)<br>CTS line driven by K-Ready (AUX)<br>SYNC line driven by DTR (AUX)<br>TRxC line drives printer clock into STI<br>RTxC line driven by 615.38 KHz keyboard clock (9600X64)<br>REQ/READY drives keyboard enable<br>(ready-receive mode)<br>(receive buffer not empty inhibits keyboard)                                                              |

| 01*     | In/Out    | SCC channel B keyboard data                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 02*     | ln/Out    | SCC channel A control registers<br>DTR line drives RTS B/RATE<br>RTS line drives RTS A<br>DCD line driven by 1 = NVR store cycle started<br>CTS line driven by 1 = DTR timer expired<br>SYNC line not connected<br>TRxC line driven by send clock (modem, terminal<br>multiplexer) or by keyboard clock (19200X32)<br>Drives connect clocks<br>RTxC line driven by receive clock (modem, terminal<br>multiplexer) or by STI channel D timer output<br>REQ/READY not connected |

| 03*     | In/Out    | SCC channel A communications data                                                                                                                                                                                                                                                                                                                                                                                                                                             |

\* Ports 00 through 03 do not use address bits 2 or 3.

ł

٠

•

Table 3-1. I/O Bit Port Assignment (Part 2 of 6)

| Address | Direction | Function                                                                                                                                                                                                                                                                            |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10      | In/Out    | STI control registers, actual addresses are 10 through 1F corresponding to register addresses 0 through F. Clock input is 615.38KHz. Timer outputs are half the channel interrupt rate.                                                                                             |

|         |           | Timer Output:                                                                                                                                                                                                                                                                       |

|         |           | <ul> <li>A – Not used (input intrpt 4 vert sync)</li> <li>B – Audio (reset to 0 after beep or click)</li> <li>C – 16X field Register 9 (OE)–Character field size, default to 15</li> <li>D – Drives RTxC A (if enabled)</li> </ul>                                                  |

|         |           | Interrupts:                                                                                                                                                                                                                                                                         |

|         |           | <ul> <li>Modem ring indicator</li> <li>0 = port B interrupt</li> <li>0 = port C (graphics) interrupt</li> <li>Cursor blink (8X cursor)</li> <li>Positive vertical synchronization</li> <li>Modem CTS</li> <li>0 = port A interrupt</li> <li>CTS assertion, check port 42</li> </ul> |

| 20*     | Out       | CRT controller register select port                                                                                                                                                                                                                                                 |

| 21*     | Out       | CRT controller parameterization registers                                                                                                                                                                                                                                           |

| *       |           | Hex Value of Registers                                                                                                                                                                                                                                                              |

|         |           | Register 0 (68**) – Must set to 105 char.                                                                                                                                                                                                                                           |

|         |           | Register 1 (59**) – Horiz. displayed 80th char.                                                                                                                                                                                                                                     |

|         | · •       | Register 2 (59**) – Must set H sync to 85th char.                                                                                                                                                                                                                                   |

|         |           | Register 3 (8C**) – Must set sync width                                                                                                                                                                                                                                             |

|         |           | Register 4 (1C) – Vert total, 70 Hz                                                                                                                                                                                                                                                 |

|         |           | Register 5 (00) – Vert adjust, 80 Hz                                                                                                                                                                                                                                                |

|         |           | Register 6 (19) – Vert displayed, default 25 lines                                                                                                                                                                                                                                  |

|         |           | Register 7 (1B) – Vert sync<br>Register 8 (AO**) – Interlace/skew<br>Register 9 (OP) – Character field size, default to 15                                                                                                                                                          |

|         | 3         | Register A (00) – Display separator width/blink (default)                                                                                                                                                                                                                           |

|         |           | Register B (00) – One line at top of character row                                                                                                                                                                                                                                  |

|         | 4         | Register C(H) (08**) – Display start, set to 0800<br>Register D(L) (00)                                                                                                                                                                                                             |

|         | In/Out    | Register E(H) – Display separator position, screen address referenced to screen physical start.**                                                                                                                                                                                   |

|         | In/Out    | Register F(L) – Display separator position, screen address                                                                                                                                                                                                                          |

|         | in Out    | referenced to screen physical start.**                                                                                                                                                                                                                                              |

|         | In        | Register 10(H) – Graphics cursor position under closest display character, absolute address referenced to screen physical start.**                                                                                                                                                  |

|         | In        | Register 11(L) – Graphics cursor position under closest display                                                                                                                                                                                                                     |

\*Ports 20 and 21 do not use address bits 1, 2, or 3.

\*\*These values affect display stability and centering and should not be changed.

5

An address bit is used for timing the row counter. Add 08 to E and 10. The vertical value can be changed if the total number of scan lines including retrace is unchanged from that shown above (vertical total X character field size). The vertical synchronization position affects screen vertical centering. To turn off the display separator, write FF to register A.

| Address | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60*     | In/Out    | Access of this port serves to reset the nonmaskable interrupt latch if the reset switch is not being actuated.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 61*     | In/Out    | Access strobes port 42; data is arbitrary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 62*     | In        | Communications status, latches terminal multiplexer<br>handshake lines. Strobed by assertion of CTS A,<br>CTS B, or port 42.<br>Data Bit Status:<br>Bit 0 1 = CTS A — { terminal multi-<br>plexer handshake } or modem CTS<br>or modem CD<br>or modem TxC<br>Bit 2 1 = Send clock lines } or modem TxC<br>Bit 3 1 = Set up enabled keylock position<br>Bit 4 1 = Terminal locked keylock position<br>Bit 5 1 = Reset switch caused last system reset (0 = power on)<br>Bit 6 AHR parity bit<br>Bit 7 1 = Modem data set ready |

| 63* .   | Out       | Character generator, character holding register. Write character to be formed (i.e., ASCII "A", write 40).                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 64*     | Out       | Segment pattern for character in port 43, 16-bit I/O write using "OUT C, A" instruction, with 44 in CPU register C.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 67*     | Out       | Strobes 4A bit 7. Address 16 will become valid after 4<br>memory cycles.<br>Interrupts are inhibited between the time 4A bit 7 differs from the<br>strobed and delayed 4A bit 7, if the strobe will change the state<br>of the flip-flop.                                                                                                                                                                                                                                                                                     |

| Table 3_1  | I/O Bit Port | Assignments | (Part 3 of 6) |

|------------|--------------|-------------|---------------|

| 10016 3-1. | NO DIL FOIL  | Assignments | (rait 5 01 0) |

\*Ports 60 through 67 do not use address bit 3.

Table 3-1. I/O Bit Port Assignments (Part 4 of 6)

| Address | Direction | Function                                                                                                                                                                        |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48*     | Out       | Display control register; cleared by power on.                                                                                                                                  |

|         |           | Data bit status:                                                                                                                                                                |

|         |           | Bit 0 1=Disable ROM after 4th following memory cycle<br>0=Enable ROM after 4th following memory cycle ROM forced on<br>by NMI flip-flop; bit not affected                       |

|         |           | Bit 1 1=RSR(H)-RSR(L)=4K Screen attributes; 4K above characters<br>0=RSR(H)-RSR(L)=32K Screen attributes; 32K above characters. If<br>bit=1, changes CPU A12 and CPU A15 to RAM |

|         |           | Bit 2 1=CG write mode; set before port 44, Display=junk<br>0=Display mode; characters displayed                                                                                 |

|         |           | Bit 3 1=Blank characters with blank bit in CG                                                                                                                                   |

|         |           | Bit 4 1=Reverse-video screen (black on light)                                                                                                                                   |

|         |           | Bit 5 1=Attribute bit 3 selects upper 256 CG characters<br>0=Attribute bit 3 selects strike-through character attribute                                                         |

|         |           | Bit 6 Not used                                                                                                                                                                  |

|         |           | Bit 7 1 = Enable non-volatile RAM overlay at DSR<br>0 = NVR is disabled                                                                                                         |

| 49*     | Out       | Communications control port; cleared by power on.                                                                                                                               |

|         |           | Data bit status:                                                                                                                                                                |

|         |           | Bit 0 1=Invert CPU address bit 13 above DSR (screen bypass)                                                                                                                     |

|         |           | Bit 0 $1 = TRxC$ A driven by keyboard clock (19.2K x 32)<br>0 = TRxC A driven by line receiver                                                                                  |

|         |           | Bit 1 1=Select long distance receiver hysteresis (multiplexer, DC)                                                                                                              |

|         |           | Bit 2 1=Select direct connect clock driver                                                                                                                                      |

|         |           | Bit 3 0=Invert Xmit clock receiver for loopback plug; inhibit punt timer                                                                                                        |

|         |           | Bit 4 1=Data terminal ready (modem), and maintenance light.                                                                                                                     |

|         |           | Bit 5 1=RTxC A driven by STI channel D output<br>0=RTxC A driven by line receiver                                                                                               |

|         |           | Bit 6 1=Enable peripheral ports 1 and 2<br>0=Reset ports                                                                                                                        |

|         |           | Bit 7 1=Invert RAM write parity; reset cursor counter (test)                                                                                                                    |

\*Ports 48 and 49 do not use address bit 3.

1

Address

|   | Direction | Function                                                        |  |  |  |  |  |

|---|-----------|-----------------------------------------------------------------|--|--|--|--|--|

|   | Out       | Memory address control; cleared by power on or interrupt ACK.   |  |  |  |  |  |

|   |           | Data bit status:                                                |  |  |  |  |  |

| ļ |           | Bit 0 1=Invert CPU address bit 13 above DSR (screen bypass)     |  |  |  |  |  |

| 1 |           | Bit 1 $1 = $ Invert CPU address bit 13, if bit 16=0, except ROM |  |  |  |  |  |

|   |           | Bit 2 1=Invert CPU address bit 13, if bit 16=1, except ROM      |  |  |  |  |  |

### Table 3-1. I/O Bit Port Assignments (Part 5 of 6)

| 4A* | Out | Memory address control; cleared by power on or interrupt ACK.                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|     |     | Data bit status:                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|     |     | Bit 0 1=Invert CPU address bit 13 above DSR (screen bypass)                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|     |     | Bit 1 $1 = $ Invert CPU address bit 13, if bit 16=0, except ROM                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|     |     | Bit 2 1=Invert CPU address bit 13, if bit 16=1, except ROM                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|     |     | Bit 3 1=Enable user RAM bank logic, if bit 7 delayed is 1                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|     |     | Bit 4 1=Enable attribute holding register between DSR and DER                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|     |     | Bit 5 1=Enable attribute holding register read operation<br>0=Hold contents of attribute holding register                                                                                                                                                                               |  |  |  |  |  |  |  |

|     |     | Bit 6 1=Inhibit interrupt ACK from clearing register                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|     |     | Bit 7** 1=Enable RAM bank 2 (A 16) into delay latch, see port 67.<br>0=Disable RAM bank 2**                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 48* |     | Memory bank register (A16 control); cleared by power on only. Eight bits<br>select address blocks where A16=1 in 64K address space. Bits 0 through<br>7 enable blocks 0 through 7. Blocks are 2000 hex bytes. Block 0 is at 0000<br>through 1FFF; block 7 is at E000 through FFFF, etc. |  |  |  |  |  |  |  |

| 4C* |     | Port 4A bits 1 and 2 swap the even and odd blocks. Display start and display end registers (DSR and DER) cleared by power on only.                                                                                                                                                      |  |  |  |  |  |  |  |

|     |     | CPU display addr if port 48 bit 1=0–A16 A14 A13 A12 A11                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|     |     | CPU display addr if port 48 bit $1 = 1 - A16$ A15 A14 A13 A11                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|     |     | Display counter address (and RSR) A15 A14 A13 A12 A11                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|     |     | DSR register bits\D7—D6—D5—D4/                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|     |     | DER register bits\D3D2D1D0/                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|     |     | A. DSR and DER limit address range of the attribute holding register.<br>The AHR effectiveness is from DSR to DER+07FF.                                                                                                                                                                 |  |  |  |  |  |  |  |

|     |     | B. DER determines the address of the RSR(L); RSR(H) = RSR(L) + 1000<br>OR 8000. The RSR(L) is at DER + 07E0.                                                                                                                                                                            |  |  |  |  |  |  |  |

|     |     | C. DSR determines the address of the NVR which is at DSR, if selected.                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|     |     | D. DSR determines the address above which port 4A bit 0 operates.<br>This carries into the user bank, if DSR is in the main bank. When<br>port 4A bit $0=1$ , DSR bits 4 and 5 must be 0 or a fault will<br>result.                                                                     |  |  |  |  |  |  |  |

|     |     | The most significant address bit in the RSR determines the logical bank<br>where the display resides (A15). If it is set, that display line is accessed<br>from the user bank. DER bit 7 determines the bank (user or main) where<br>the RSRs are located.                              |  |  |  |  |  |  |  |

\*Ports 4A through 4C do not use address bit 3.

\*\*These bits take effect in both directions at the end of the indicated M1 cycle after the output instruction. NMI has no effect. NMI latch must not be cleared until all registers are initialized.

### Table 3–1. I/O Bit Port Assignments (Part 6 of 6)

| Address | Direction | Function                                                                                                                                                                                                                                                                              |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4D      | Out/In    | Generates interrupt pulse to external port A.                                                                                                                                                                                                                                         |

| 4E*     | Out/In    | Generates interrupt pulse to external port B.                                                                                                                                                                                                                                         |

| 4F*     | Out/In    | Generates interrupt pulse to external port C (graphics).                                                                                                                                                                                                                              |

| 50-5F   | In/Out    | Addresses 50 through 5F select ports on the graphics board. These ports generally serve to override the graphics processor for fundamental initialization and RAM access control.                                                                                                     |

| 80-8F   |           | Port addresses 80 through 8F are reserved for devices that reside in the external ports 1, 2, or 3. Port 3 uses this space in the event that addresses 50 through 5F are full or unavailable.<br>The program cartridge load device is I/O accessible only via any I/O input above 80. |

\*Ports 4E through 4F do not use address bit 3.

### NOTE:

The I/O port addresses below 40 are located on the internal bus, and the remaining ports are located on the external bus. All ports are affected by read or write. Input of an output port will cause that port to receive indeterminate data.

The following port addresses are decoded but not used in the UTS 30. Changes to this list may occur at a later date.

30 - 3F

65, 66 (next in line for use)

70 - 7F

### 3.2. I/O PORT 4A

A detailed description of the bit definitions for I/O port 4A follow. This port controls the memory addressing by the CPU.

Bit 0

Bit 0, when set to 1, causes address bit 13 to be inverted at all addresses (including A16) that exceed that value loaded in the 4-bit DSR register (4C).

This condition is used by the screen bypass function and is very specific. This function is limited. If DSR bit 4 is not 0, erratic memory addressing or undefined AHR operation may result.

Bit 1

Bit 1, when set to 1, causes address bit 13 to be inverted for all addresses where A16 = 0.

This bit is used when the microcode is resident in the user bank. This bit has no effect on ROM addressing, but does affect RAM that is written at the ROM address.

Bit 2, when set to 1, causes address bit 13 to be inverted for all addresses where A16 = 1.

This bit is used when the microcode is resident in the main bank. This bit has no effect on ROM addressing, but does affect RAM that is written at the ROM address. Bits 0, 1, and 2 are logically ORed before the inversion takes place (setting two bits does not cause a double inversion).

Bit 3

Bit 4

Bit 2

Bit 3 must be set in order for address bit 16 to be set.

This bit changes during the I/O output instruction and is handy for selecting the pages enabled via port 4B. Bit 7 delayed must also be 1 for this bit to operate.

Bit 4 enables the attribute holding register (AHR).

When this bit is 1, the byte in the AHR transfers to RAM if the address of the write is in display space (see port 4C).

If bit 5 is set, a read of RAM in display space causes that data to be loaded into the AHR. The data that is affected by the AHR is that byte corresponding to the attribute of the data character being written.

For example, if a character is read from display space by the CPU, its corresponding attribute is loaded into the AHR. If the CPU then writes to another location in display space, the byte in the AHR is also written into the attribute location for that character. Display attributes are fixed at an address offset from the data character. This offset is either +2000 or +8000 (see port 48, bit 1).

Bit 5 is used to enable the read function that causes the AHR to be loaded with the memory data that is in the attribute space. This bit operates only if bit 4 is set.

If bit 5 = 0, the AHR serves as a holding register to propagate attributes for each display space write. If bit 5 = 1, the AHR assists in moving data around in display space as the attribute is automatically transferred. When bit 4 is enabled, other reads or writes in display space must be avoided or the attribute space and the AHR contents may inadvertently change. The AHR carries parity and is discussed in the following paragraphs.

Bit 6 is reset to 0 if interrupts are to be handled in only the main bank.

Interrupt acknowledge clears all bits in port 4A. This causes the vector and instructions to be accessed in the main bank regardless of the contents of port 4B or the previous value of port 4A. If bit 6 = 1, interrupts do not affect the memory configuration.

Bit 5

Bit 6

Bit 7

Bit 7, when set to 1, enables address bit 16, as defined by port 4B.

This bit is delayed until after Port 67 is written and 4 memory cycles have occurred. This allows the microcode to jump from one bank to the other and properly return from interrupts if bit 6 is reset. It allows for either a jump, branch, or call. This bit should be left in the 1 state, and bit 3 should be used for bank selection if this function is not to be delayed. Port 4B can also be used for immediate selection.

### 3.3. I/O PORT 67

Port 67 is used to delay the action of port 48 bit 7 so that microcode may recover the environment. A detailed description of the bit definitions for Port 67 follows. The four memory cycle instruction fetches (opcodes) use two cycles. The position of the out to 67 in relation to the call or return determines whether bank switching occurs before or after the stack operation interrupts are inhibited during the bank switching operation. When 4A bit 7 state disagrees with the delayed state of the 4A bit 7 strobed and delayed value, interrupts will be blocked. This action takes two instructions to activate. The following example may clarify this operation.

Assume that code is executing in the user bank and desires to switch to the main bank via a call.

- 1. Switch port 4A bit 7. After 2 more instructions, interrupts will be blocked.

- 2. Set up all registers as desired.

- 3. Write to port 67.

- 4. Call routine; stack will occur in the user bank. Interrupts will be enabled after the first instruction in the main bank.

### NOTE:

Insert an instruction that uses two memory cycles, such as an NOP between step 3 and 4 if the stack is to be in the main bank.

Returns and jumps are implemented in a similar way. Do not use branch instructions.

### 3.4. I/O PORT 48

Port 48 controls the display parameters and the ROM. A detailed description of the bit definitions for I/O port 48 follows.

Bit Q

Bit 0 selects the ROM always addressed at 0000 through 1FFF.

If bit 0 = 0, the ROM is enabled, and overlays RAM at its address. The RAM at the ROM address can be written to when the ROM is selected, but all reads at the ROM address result in ROM data. If bit 0 = 1, the ROM is deselected. The ROM remains selected for the next four memory cycles after the output instruction to port 48, allowing a PC HL or jump to any address, including one at the ROM address. The ROM is not affected by any of the bits in port 4B or 4A except bit 0 in port 4A.

This bit causes ROM to be displaced by 2000 if the DSR is 00. ROM can also be deselected by activating the signal, inhibit ROM, available at J3. This is generally used by the maintenance panel or for test purposes.

The ROM is selected whenever the NMI latch is set; however, the NMI latch does not affect the state of bit 0. The NMI latch is set whenever RAM parity is read incorrectly from any source, or when the reset switch is activated. If the NMI latch is cleared (by accessing port 40) while bit 0 = 1 the ROM is immediately deselected. When set, the NMI latch generates one nonmaskable interrupt. All NMI handling must start in ROM at address 0066. The NMI latch can be set on power up, but no NMI occurs. Before exiting ROM, the latch must be reset or bit 0 is ignored.

Bit 1 determines the address separation of the display attributes and display data.

When bit 1 = 0, the attributes are 8000 hex greater than the display characters. The row start registers (RSR) are also split by the same 8000 bytes (RSR L + 8000 = RSR H). In other words, the low order byte of the row start address is in the display area, and the high order byte is in the attribute area.

When bit 1 = 1, the attributes are 1000 hex greater than the display characters (RSR L + 1000 = RSR H).

Bit 2 controls the character generator.

When bit 2 = 0, the character generator is in display mode. When bit 2 = 1, the character generator is in write or load mode; displayed characters are arbitrary. This bit must be set prior to loading the data via port 43 and 44.

Bit 3 controls the characters in the character generator having the blank bit set.

If bit 3 = 1, those characters are blanked. If bit 3 = 0, the characters are displayed normally. This is used either for special characters that must be conditionally displayed, or for characters that must be blinked at a rate different from that provided by the blink character timer.

Bit 4 controls the polarity of the video information.

When bit 4 = 1, light characters on a dark background are displayed. When bit 4 = 0, dark characters on a light background are displayed. This bit also affects graphics data.

Bit 5

Bit 5 selects the function of attribute bit 3.

When bit 5 = 0, attribute bit 3 causes a strike-through to appear over the corresponding display character. When bit 5 = 1, the alternate character set is selected. This bit must be used when loading the character generator and should be set prior to ports 43 or 44. If the alternate character set is not installed, the characters are generally displayed as a solid block. This is not guaranteed, but an indication of whether the feature is present. If it is present, random dots are displayed.

Bit 6 is not used.

Bit 2

Bit 3

Bit 4

Bit 6

Bit 7

Bit 7 selects the non-volatile RAM (NVR). When bit 7 = 1, the NVR overlays the beginning of display RAM as defined by the DSR. The NVR address is at DSR to DSR + 00FF. When bit 7 = 0, the main RAM is again selected. When this bit is set, the action of the AHR is inhibited at DSR to DSR + 0FFF.

### 3.5. I/O PORT 49

Port 49 controls some communications parameters and the parity generator. A detailed description of the bit definitions for I/O port 49 follows.

Bit O

Bit 1

Bit 0 determines the driver of the TRxC A pin of the SCC IC.

When bit 0 = 0, the TRxC A pin is driven by the line receiver for online synchronous communications. This bit is not used when bit 2 of this port is set (direct connect mode).

Bit 1 is used to select the receiver sensitivity to control noise susceptibility.  $1 = \log \operatorname{distance}$ ;  $0 = \operatorname{short} \operatorname{distance}$  cable less than 50 feet. When bit 1 = 0, it reduces the receiver sensitivity on some lines, improving noise immunity.

### NOTE:

This function is not implemented, but may be in the future if the need arises. To allow for future implementation, this parameter should be supported in the microcode to avoid future code changes.

This bit is dependent only on cable length, not on communications mode.

Bit 2 is used to select the direct connect clock driver. When bit 2 = 1, it selects direct connect. The TRxC A pin of the SCC drives both the transmit and receive clocks on the communications interface. This bit must be set prior to setting the TRxC A pin to output, or driver conflict (because of noise generation) will result causing possible system malfunction.

Bit 3 controls the polarity of the transmit clock receiver.

When bit 3 = 0, the receiver is inverted for loopback testing with the loopback adapter, 2832471. In loopback, the transmit clock is inverted from the receive clock to reduce cable crosstalk. This bit also serves to disable the punt timer which is active when RTS is active. The punt timer serves no purpose in asynchronous applications so this bit can be left 0. When bit 3 = 1, it allows normal reception of the transmit clock signal and is used for synchronous communications. It also enables the RTS timer causing DTR and RTS to be negated if interrupts are ignored for longer than about 2 seconds.

Bit 4, when set to 1, activates DTR and lights the maintenance indicator on the top edge of the card.

Bit 2

Bit 3

Bit 4

This light should be on whenever the terminal is operating, indicating to a service operator that the system is operational from the point of view of the CPU. However, if the terminal is connected to an auto answer modem, the DTR line should only be active when a connection can be made. POC should not activate DTR except under special conditions.

Bit 5 determines the driver source for the SCC RTxCA pin.

If bit 5 = 0, the pin is driven by the communications receive clock line receiver. If bit 5 = 1, the pin is driven by the STI channel D output. This configuration prevents the use of timer D for system uses, but provides for dual asynchronous baud rates for transmit and receive during the video-text application.

Bit 6

Bit 5