STD 7000 7704 BYTE-WIDE Memory Card

**USER'S MANUAL**

### NOTICE

The information in this document is provided for reference only. Pro-Log does not assume any liability arising out of the application or use of the information or products described herein.

This document may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of Pro-Log, nor the rights of others.

Printed in U.S.A. Copyright<sup>®</sup> 1981 by Pro-Log Corporation, Monterey, CA 93940. All rights reserved. However, any part of this document **may be reproduced** with Pro-Log Corporation cited as the source.

# **STD 7000**

7704 BYTE-WIDE Memory Card

**USER'S MANUAL**

# PRELIMINARY

### FOREWARD

This manual explains how to use Pro-Log's 7704 Byte-Wide Memory Card It is structured to reflect the answers to basic questions that you, the user, might ask yourself about the 7704. We welcome your suggestions on how we can improve our instructions.

The 7704 is part of pro-Log's Series 7000 STD BUS hardware. Our products are modular, and they are designed and built with second-sourced parts that are industry standards. They provide the industrial manager with the means of utilizing his own people to control the design, production, and maintenance of the company's proucts that use STD BUS hardware.

Pro-Log supports its products with thorough and complete documentation. Also, to provide maximum assistance to the user, we teach courses on how to design with, and to use, microprocessors and the STD BUS products.

You may find the following Pro-Log documents useful in your work: *Microprocessor User's Guide* and the *Series 7000 STD BUS Technical Manual*. If you would like a copy of these documents, please submit your request on your company letterhead.

ïi

## Contents

17

()

| Foreword                                    | ii      |

|---------------------------------------------|---------|

| Figures                                     | v       |

| Section 1 - Purpose and Main Features       | 1-1     |

| Section 2 - Installation and Specifications | 2-1     |

| Installation                                | 2 - 1   |

| Wire Jumpers                                | 2 - 3   |

| Memory Decoder                              | 2 - 4   |

| Memory Type                                 | 2 - 2 2 |

| Unused Sockets                              | 2 - 2 5 |

| Memex                                       | 2 - 2 5 |

| Segment Select                              | 2 - 26  |

| Specifications                              | 2 - 26  |

| Section 3 - Operation and Programming       | 3-1     |

| Introduction                                | 3-1     |

| Memex                                       | 3-1     |

| Memex Example                               | 3-1     |

| Memex Control Software Introduction         | 3 - 4   |

| Memex Control Software Example One          | 3 - 4   |

| Memex Control Software Example Two          | 3-6     |

| Memex Control Software Example Three        | 3-7     |

| Memex Control Software Example Four         | 3 - 8   |

| Memex Interrupt Control Software            | 3-10    |

| Segment Select                              | 3-13    |

| Segment Select Control Software             | 3-16    |

| Section 4 - Operating Software              | 4-1     |

| Section 5 - Maintenance                     | 5-1     |

| Reference Drawings                          | 5 - 1   |

| Return for Repair Procedures                | 5 - 4   |

| Limited Warranty                            | 5 - 4   |

# Figures

| Figure | P                                           | age              |

|--------|---------------------------------------------|------------------|

| 1-1    | 7704 Byte Wide Memory Card                  | 1-1              |

| 1-2    | Block Diagram of 7704 Byte Wide Memory Card | 1-2              |

| 2-1    | 7704 Installation                           | 2 - 1            |

| 2 - 2  | Segment Select Interconnect                 | 2 - 2            |

| 2-3    | Part Numbers for 7704 Option Jumpers        | 2 - 3            |

| 2 - 4  | Physical Location of Features               | 2 - 4            |

| 2-5    | 7704 Memory Decoder Option                  | 2 <del>-</del> 5 |

| 2-6    | 7704 Option 0                               | 2-6              |

| 2-7    | 7704 Option 1                               | 2-7              |

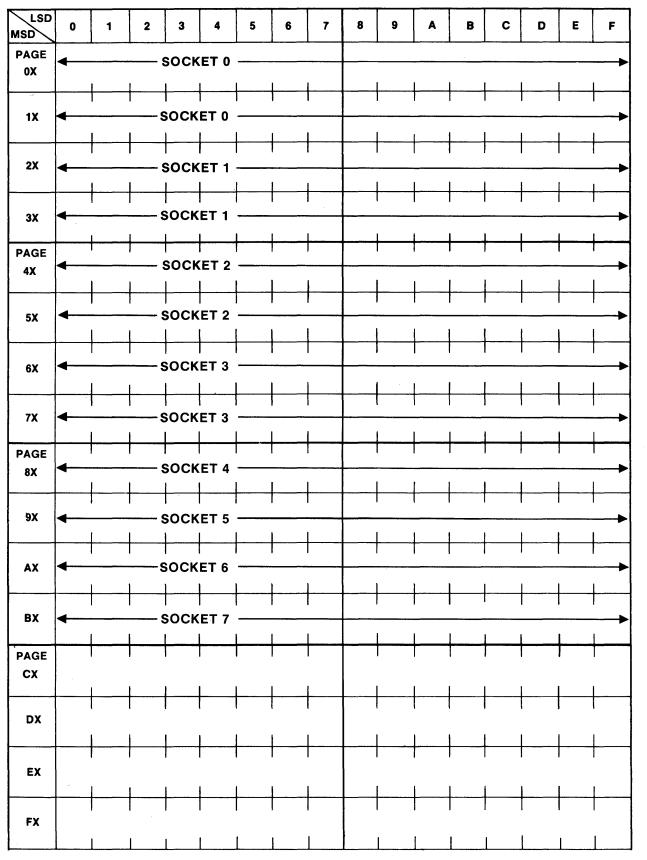

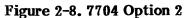

| 2-8    | 7704 Option 2                               | 2 - 8            |

| 2-9    | 7704 Option 3                               | 2-9              |

| 2-10   | 7704 Option 4                               | 2-10             |

| 2-11   | 7704 Option 5                               | 2-11             |

| 2-12   | 7704 Option 6a                              | 2 - 1 2          |

| 2-13   | 7704 Option 7                               | 2-13             |

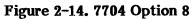

| 2-14   | 7704 Option 8                               | 2-14             |

| 2-15   | 7704 Option 9                               | 2-15             |

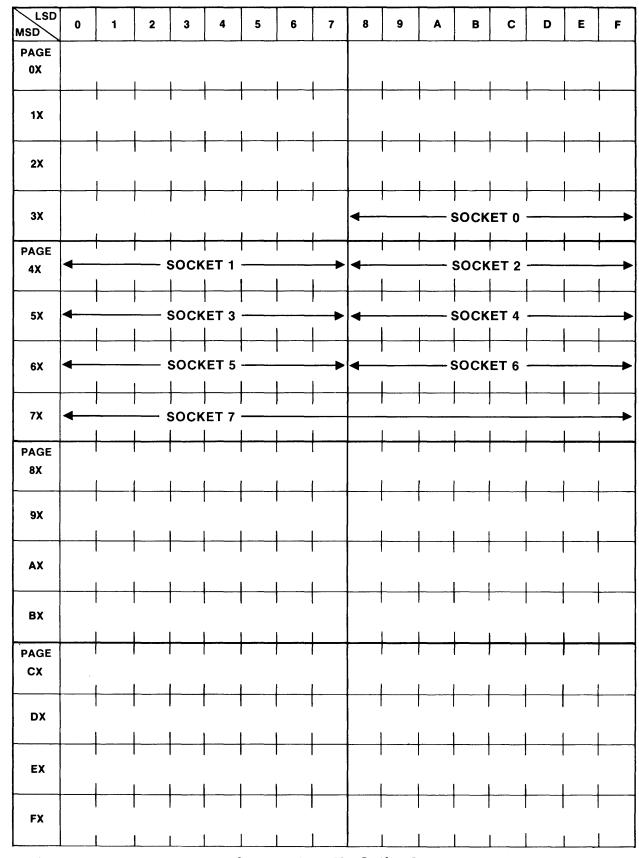

| 2-16   | 7704 Option 10                              | 2-16             |

| 2-17   | 7704 Option 11                              | 2-17             |

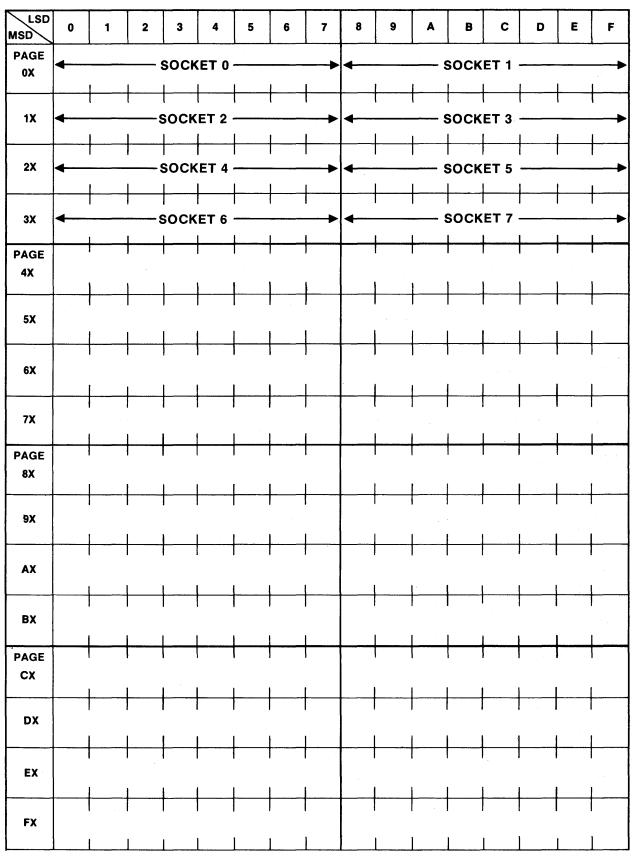

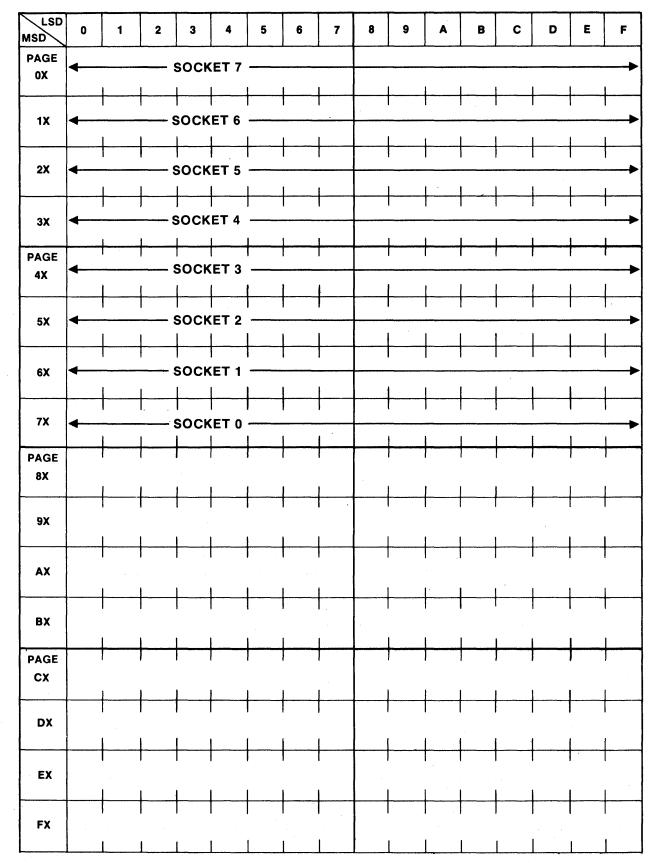

| 2-18   | 7704 Option 12                              | 2-18             |

| 2-19   | 7704 Option 13                              | 2-19             |

| 2-20   | 7704 Option 6b                              | 2 - 2 0          |

| 2-21   | 7704 Option 15                              | 2-21             |

| 2-22   | Socket Configurations                       | 2 - 2 3          |

| 2-23   | Memory Components                           | 2 - 24           |

| 2-24   | Electrical and Environmental Specifications | 2 - 26           |

| 2-25   | Electrical Characteristics                  | 2 - 27           |

| 2-26   | Interface Specifications                    | 2 - 27           |

| 2-27   | Edge Connector Pin List                     | 2 - 27           |

| 2-28   | 7704, Timing for Write                      | 2 - 28           |

| 2-29   | 7704, Timing for Read                       | 2 - 29           |

| 2-30   | 7704, Memex Timing                          | 2-29             |

| 2-31   | 7704, Segments Timing                       | 2-30             |

0

# Figures (continued)

| 2-32  | 7704, Segments MEMRQ                            | 2-30  |

|-------|-------------------------------------------------|-------|

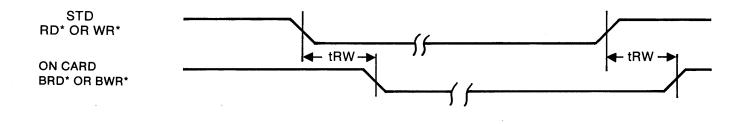

| 2-33  | 7704, RD* or WR* Timing                         | 2-31  |

| 3-1   | 7704 Memex Example                              | 3 - 2 |

| 3-2   | 7704 Memex Example                              | 3 - 3 |

| 3 - 3 | 7704 Memex Software Example One                 | 3 - 5 |

| 3-4   | 7704 Memex Software Example Two                 | 3-6   |

| 3 - 5 | 7704 Memex Software Example Three               | 3-7   |

| 3-6   | 7704 Running Example Three                      | 3 - 8 |

| 3-7   | 7704 Memex Software Example Four                | 3-9   |

| 3-8   | 7704 Running Example Four                       | 3-9   |

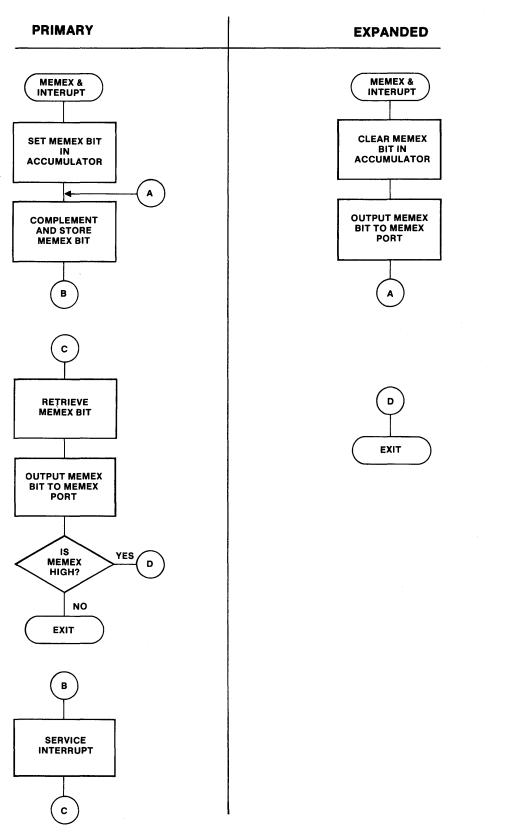

| 3-9   | Memex, Interrupt Software, Primary Memory       | 3-11  |

| 3-10  | 7704, Memex, Interrupt Software Expanded Memory | 3-11  |

| 3-11  | 7704 Memex, Interrupt Software Flow Chart       | 3-12  |

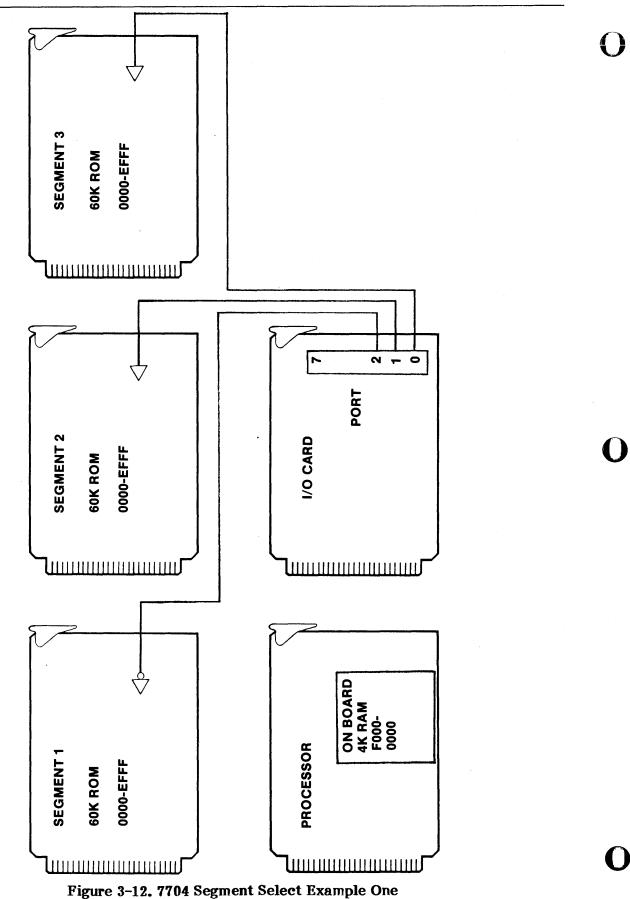

| 3-12  | 7704 Segment Select Example One                 | 3-14  |

| 3-13  | 7704 Segment Select Example Two                 | 3-15  |

| 3-14  | 7704 Segment Control Software                   | 3-16  |

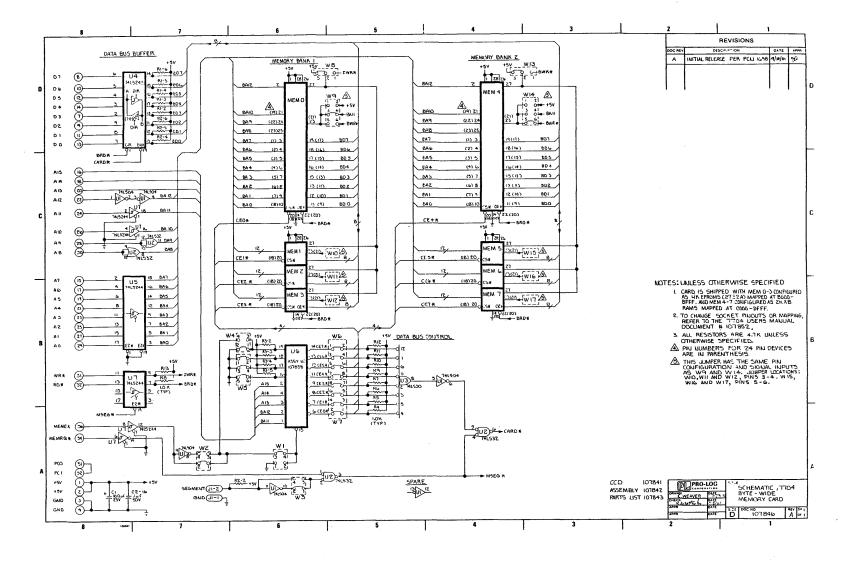

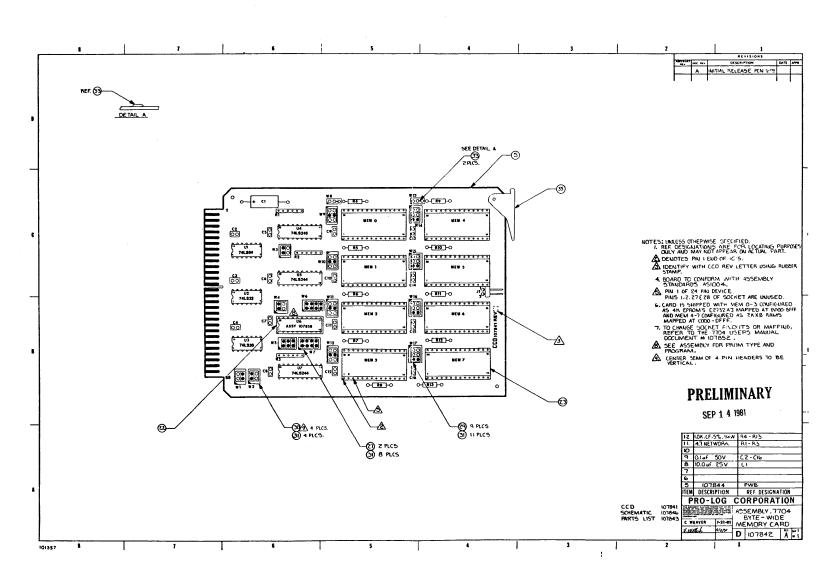

| 5-1   | Schematic, 7704                                 | 5 - 2 |

| 5 - 2 | Assembly, 7704                                  | 5 - 3 |

v

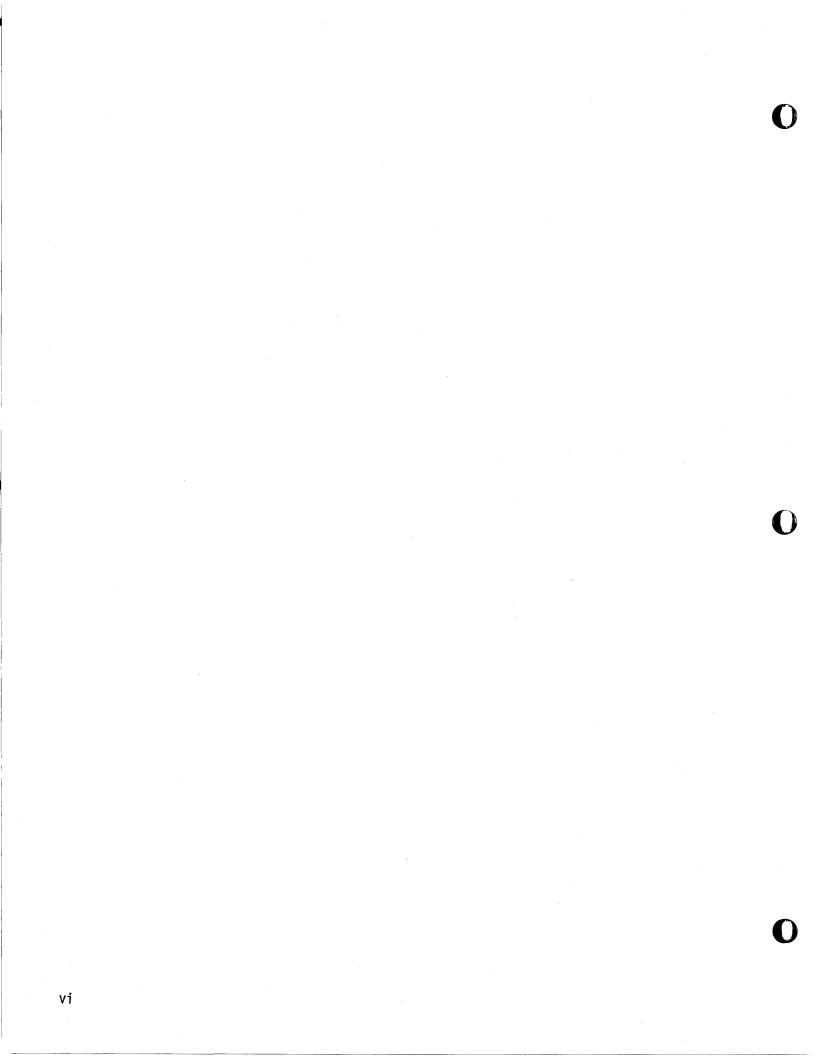

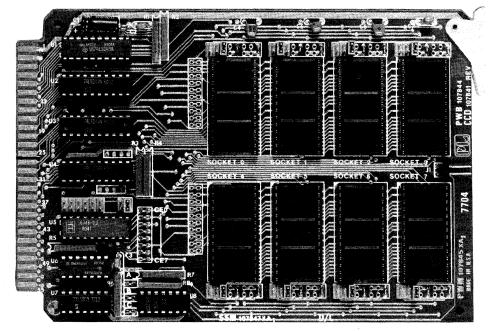

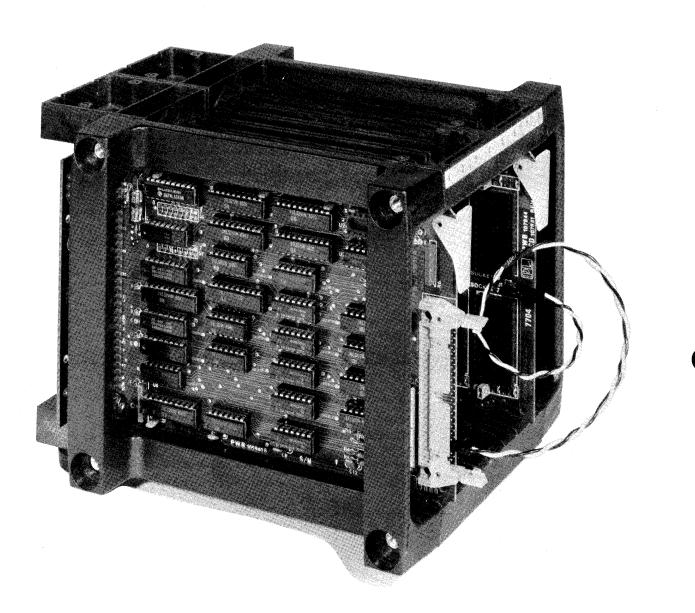

The 7704 Byte-Wide Memory card is designed to be a flexible part of the memory in your system. Its eight sockets, designed for devices conforming to the JEDEC 28 pin dual inline standard pinout, allow the use of 2K, 4K, and 8K ROMs and RAMS all of one size or in combinations.

The card can respond the the STD BUS MEMEX line in one of two ways. The memory on the card can be separated into two banks, each bank selected by the MEMEX line. This allows up to 64K on one card. Alternately, two cards, with up to 64K on each card, can be used in a system, each card selected by the MEMEX line.

The MEMEX line can be used to implement a maximum of memory with a minimum of cards. A system using Pro-Log's 7804 Z80A processor card, and two 7704 cards, can have up to 124K of memory with no additional signal lines or cards.

The 7704 can also respond to an external Segment Select line, allowing it to participate in large scale bank select schemes. The Segment Select line can be controlled by a memory segment controller or by I/O ports. One output port can control eight 7704 cards. Also, it can be tailored to fit small scale applications. Unused sockets can be disabled, allowing the card to occupy as little as 2K bytes of memory space which can be mapped anywhere within a 64K byte address field.

The 7704 has 12 specific jumper-selectable combinations for memory parts. Some of these are designed to complement the memory provided on Pro-Log processor cards. Any of the memory parts can be either ROM or RAM. The address decoder for the specific memory configurations is a PROM, which can be reprogrammed by the user to provide any combination desired.

#### Features

- \* All one size or combinations 2K, 4K, and 8K ROMs and RAMs

- \* 28 pin JEDEC standard sockets

- \* Responds to STD BUS MEMEX line

- \* Responds to external Segment Select line

- Onboard flexible address decoding

- \* Processor independent -use with 8085, Z80, 6800, 6809, 8088 and others

Figure 1-1. 7704 BYTE-WIDE Memory Card

Figure 1-2. Block Diagram of 7704 BYTE-WIDE Memory Card

1-2

#### Installation and Specification

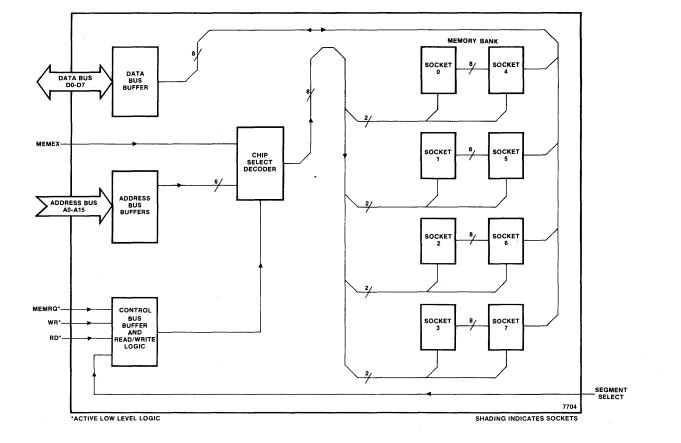

### Installation

The 7704 operates as part of an STD BUS card rack system. You can plug it directly into the STD BUS backplane, as shown in Fig. 2-1, or extend it from the motherboard with a 7901 card extender. To use the 7901 card extender, plug it into any slot in the card rack, and plug the 7704 into the connector on the 7901 card. This makes the 7704 accessible for testing, etc.

The 7704 can occupy any slot in the card cage. It should be installed with the card ejector towards the top of the card rack as shown in Fig. 2-1.

If the external Segment Select line is used, it should be attached as shown in Fig. 2-2. The connector type is a 2-pin 0.1 inch center connector. The cable should be a twisted pair, consisting of one signal line and one ground line for added noise immunity. The Pro-Log RC704 cable can be used for this purpose and can connect the 7704 card to an I/O card such as Pro-Log's 7605 card.

Figure 2-1. 7704 Installation

Figure 2-2. 7704 Segment Select Connector

#### WIRE JUMPERS

Some 7704 optional functions are selected by wire jumpers. When removing and replacing these jumpers, cut the jumper in half, then desolder and remove each half individually. Remaining solder should be removed, and new jumpers installed in the appropriate places. This procedure will prevent damage to circuit traces.

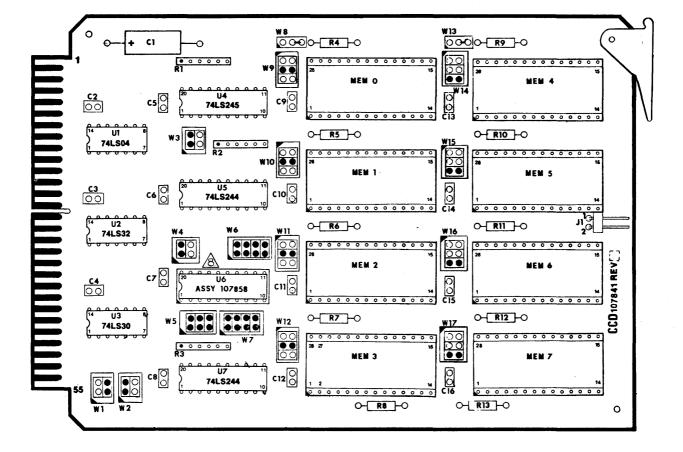

Most 7704 optional functions are selected by permanent 0.025 in. square posts which can be connected by slip on, slip off connectors. Part numbers for these connectors and headers are listed in Fig. 2-3. Figure 2-4 shows the location of these jumpers and some of the other features of the 7704.

| Manufacturer Part Number |                                                                                           |  |  |  |  |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Elco Corp.               | Berg Electronics                                                                          |  |  |  |  |  |  |  |  |

| 00 8261 02 32 00 852     | 65611-102                                                                                 |  |  |  |  |  |  |  |  |

| 00 8261 04 32 00 852     | 65611-104                                                                                 |  |  |  |  |  |  |  |  |

| 00 8261 06 32 00 852     | 65611-106                                                                                 |  |  |  |  |  |  |  |  |

| 00 8261 08 32 00 852     | 65611-108                                                                                 |  |  |  |  |  |  |  |  |

| 00 8261 02 42 00 870     |                                                                                           |  |  |  |  |  |  |  |  |

|                          | 00 8261 02 32 00 852   00 8261 04 32 00 852   00 8261 06 32 00 852   00 8261 08 32 00 852 |  |  |  |  |  |  |  |  |

Figure 2-3. Part Numbers for 7704 Option Jumpers

Figure 2-4. Physical Locations of Features on the 7704 Card

#### **MEMORY DECODER**

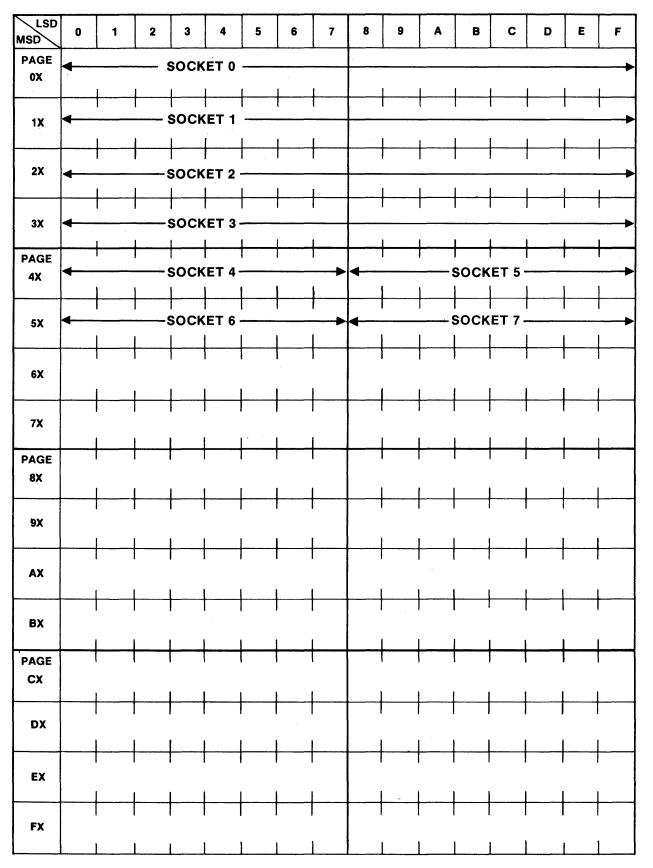

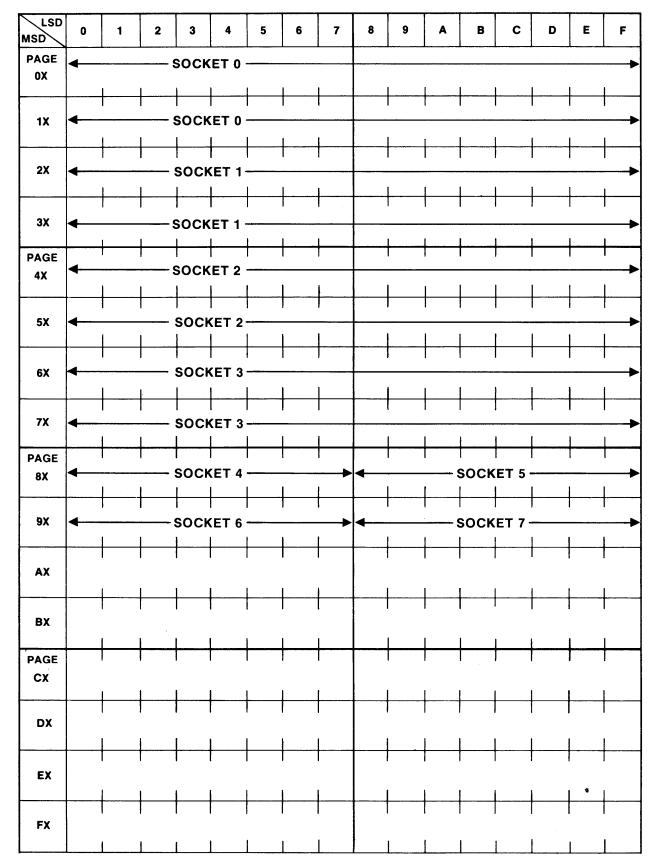

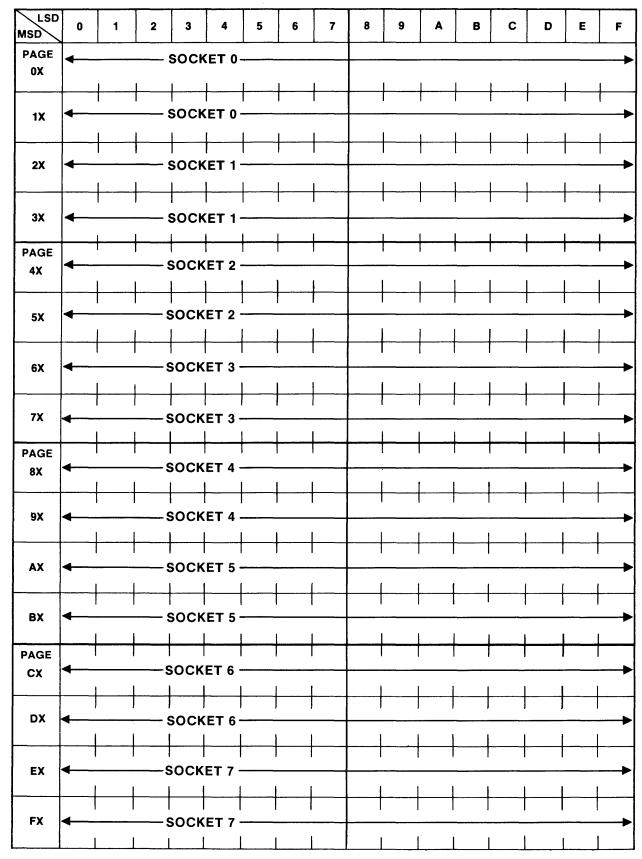

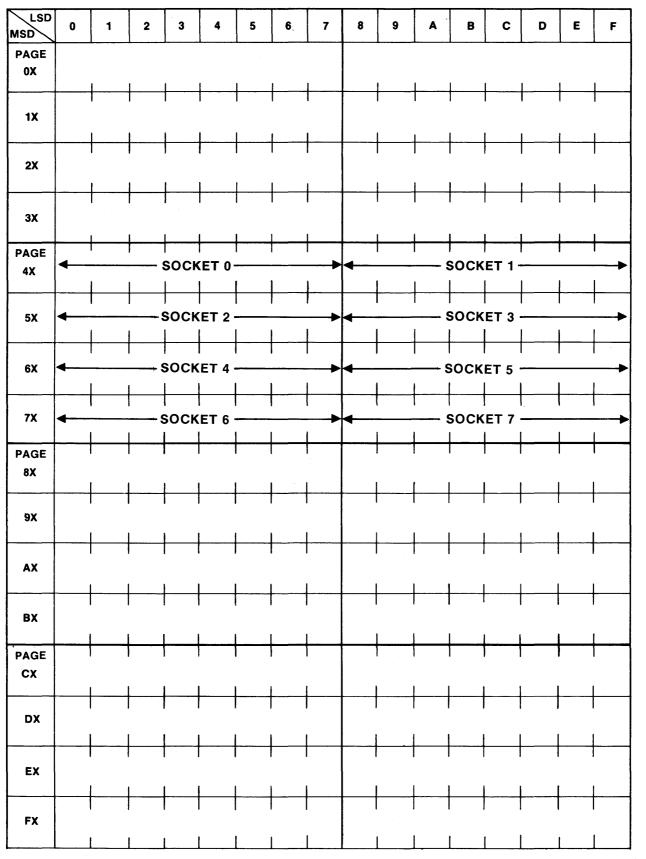

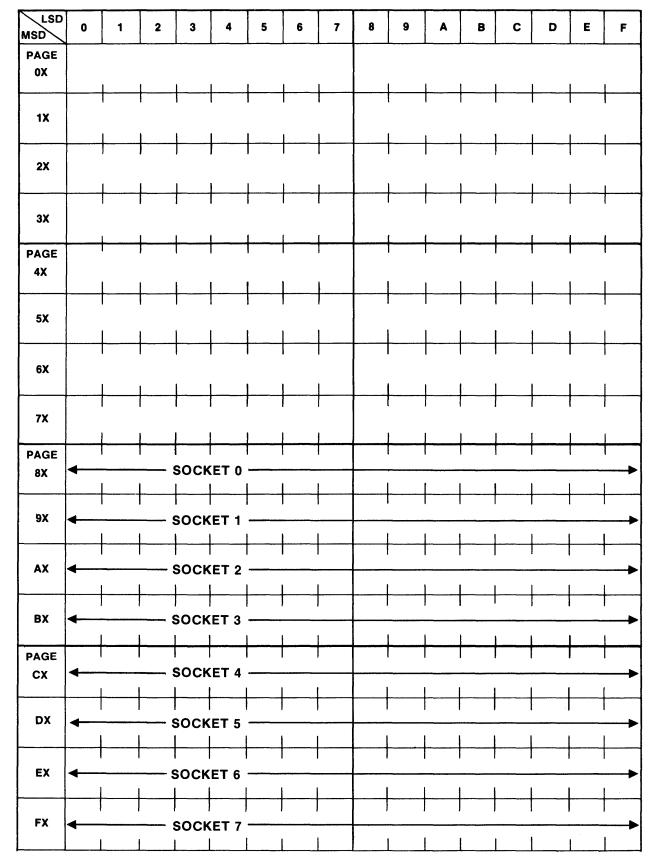

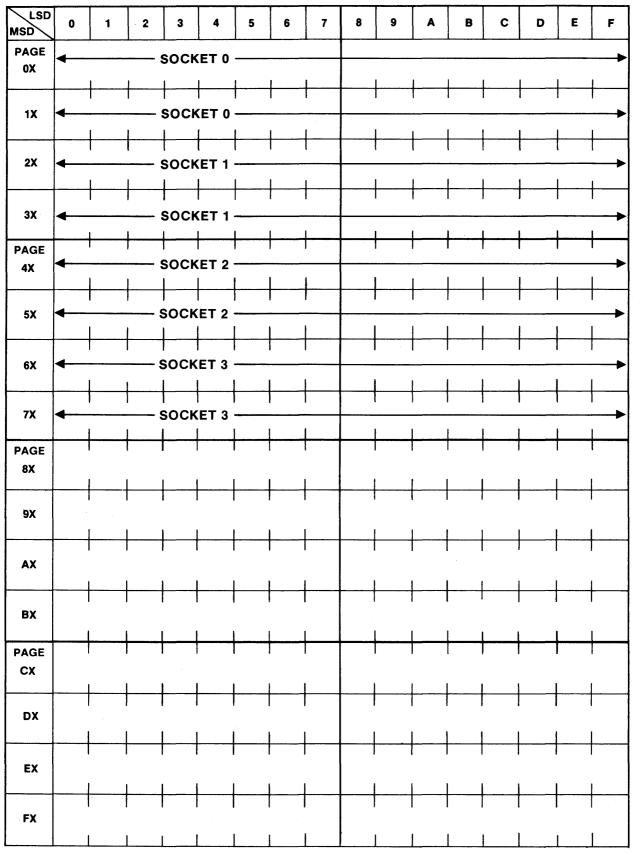

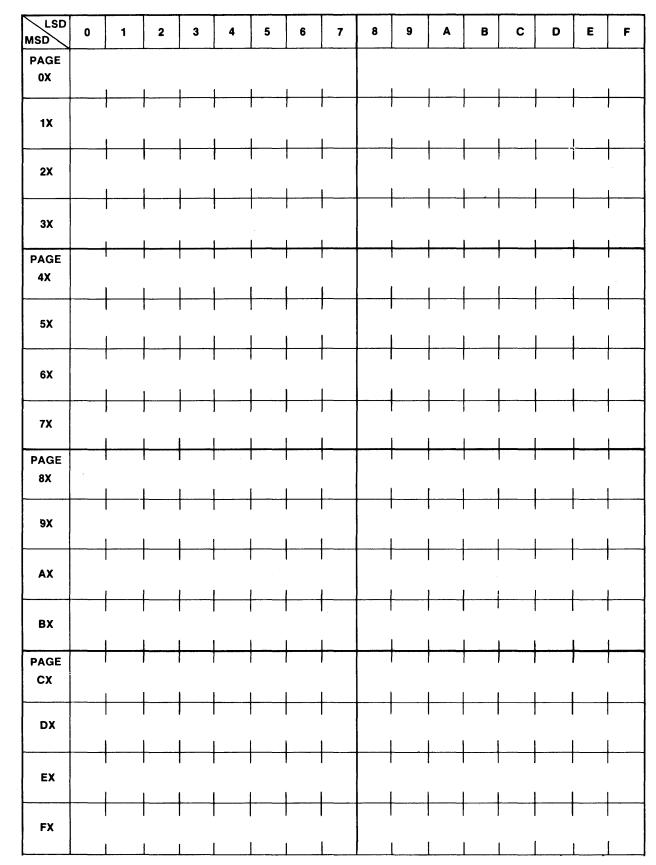

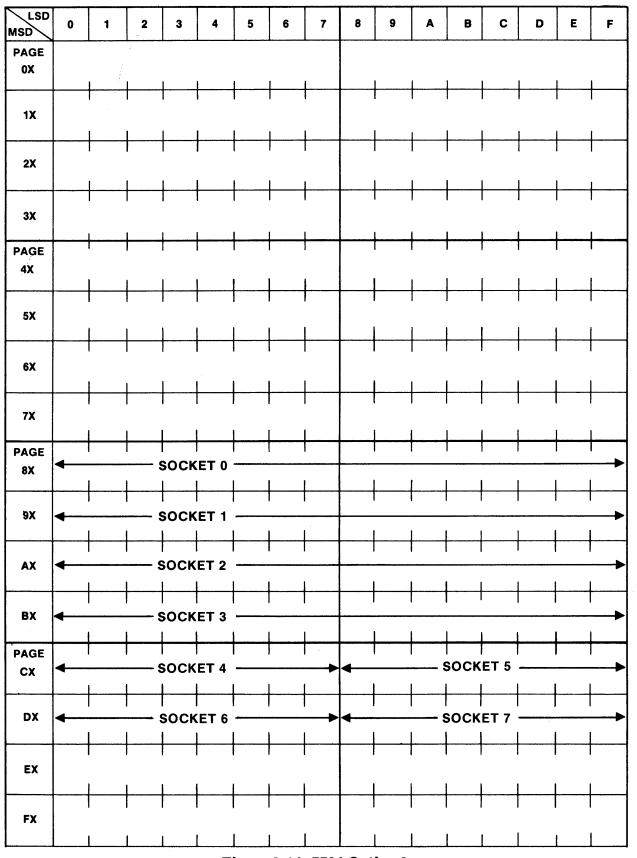

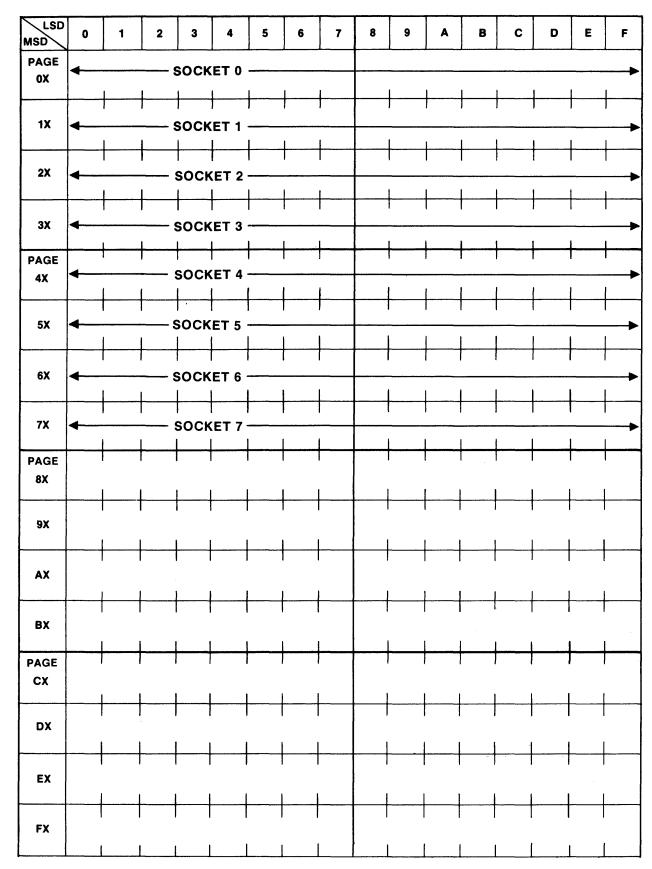

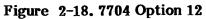

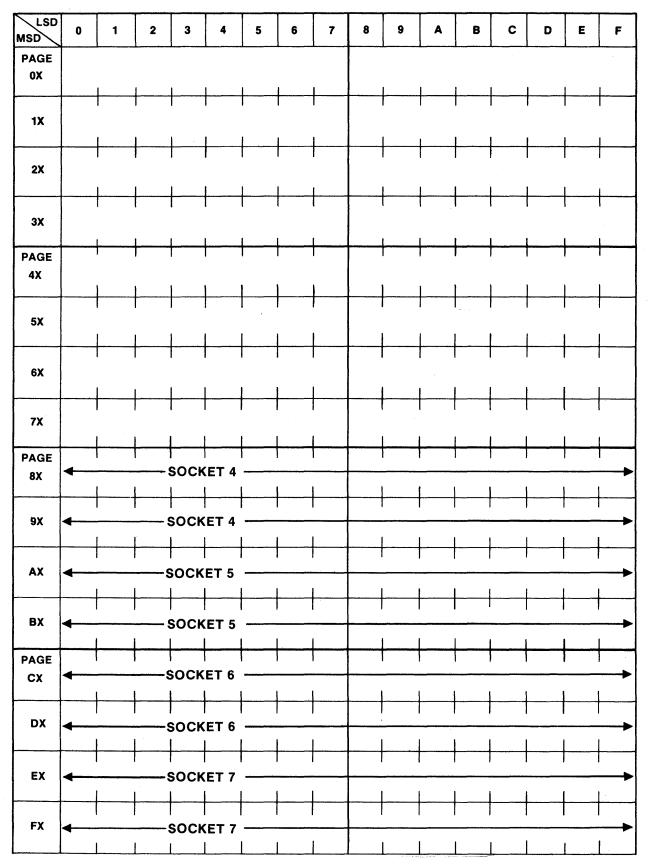

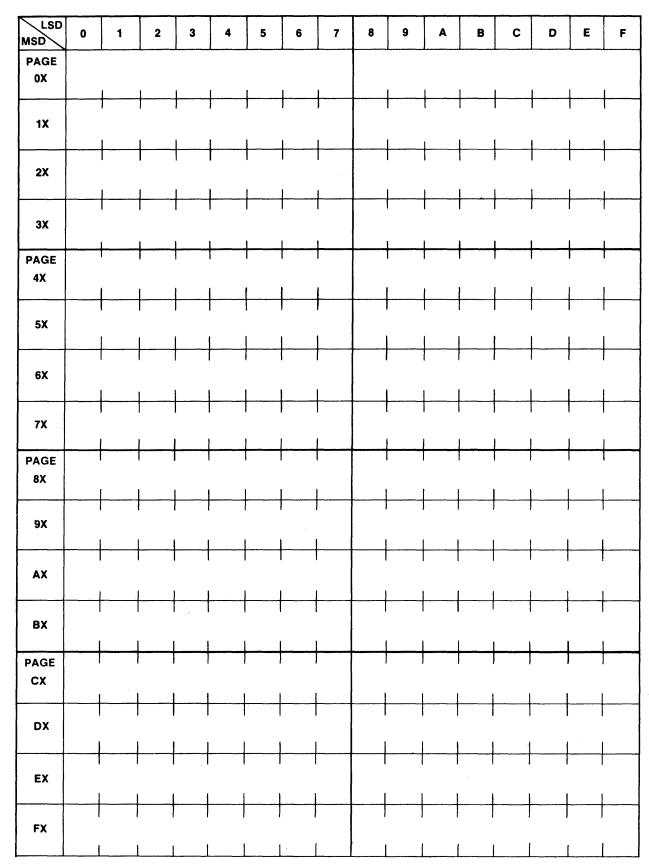

The eight memory sockets of the 7704 can accept any combiantion of 2K, 4K, and 8K ROMs and RAMs which conform to the specifications described in the Memory Type section. The combination of memory sizes and the address range each socket occupies are controlled by the Memory Decoder. The Memory Decoder contains 12 optional combinations, which are selected by jumper W4 1-2, 3-4, and jumpers W5, 1-2, 3-4, and 5-6. The physical locations of these jumpers can be found in Fig. 2-4. The 12 combinations and how to select them are shown in Fig. 2-5. Figures 2-6 through 2-21 are 64K memory maps which show the address field occupied by each socket for each option.

The Memory Decoder is a PROM. If other combinations of memory types or other address mapping is required, the PROM can be programmed with your own option. Two sections of the PROM have been left blank specifically for this purpose. The options contained in the Memory Decoder as shipped should suffice for most applications. If other options are required, the writing of the program and the programming of the PROM would be the responsibility of the user.

| _   |

|-----|

| - 3 |

|     |

|     |

| OPTION        | JUMPERS<br>(X = JUMPER INSTALLED)<br>W5 W4 |   |     |   |     |    | TOTAL ADDRESS |    |     | MEMORY PER SOCKET      |   |   |   |   | ET |   | COMMENTS |   |                                                                                                                                                                                                        |

|---------------|--------------------------------------------|---|-----|---|-----|----|---------------|----|-----|------------------------|---|---|---|---|----|---|----------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ĺ             | 5-6                                        |   | 1-2 |   | -   | 8K |               | 2K |     |                        | 0 | 1 | 2 | 3 | 4  | 5 | 6        | 7 |                                                                                                                                                                                                        |

| As<br>Shipped | х                                          | х | х   | х | -   | 0  | 4             | 4  | 24K | 8000-DFFF              | 4 | 4 | 4 | 4 | 2  | 2 | 2        | 2 | Standard as shipped from Pro-Log (4K, 2K mixed).                                                                                                                                                       |

| 1             | -                                          | х | х   | x | _   | 4  | 0             | 4  | 40K | 0000-9FFF              | 8 | 8 | 8 | 8 | 2  | 2 | 2        | 2 | 8K, 2K mixed.                                                                                                                                                                                          |

| 2             | х                                          | _ | x   | x | —   | 4  | 4             | 0  | 48K | 0000-BFFF              | 8 | 8 | 8 | 8 | 4  | 4 | 4        | 4 | 8K, 2K mixed.                                                                                                                                                                                          |

| 3             | _                                          | _ | х   | х | —   | 8  | 0             | 0  | 64K | 0000-FFFF              | 8 | 8 | 8 | 8 | 8  | 8 | 8        | 8 | All 8K.                                                                                                                                                                                                |

| 4             | х                                          | х | _   | x | —   | 0  | 0             | 8  | 16K | 4000-7FFF              | 2 | 2 | 2 | 2 | 2  | 2 | 2        | 2 | All 2K.                                                                                                                                                                                                |

| 5             | —                                          | х | .—  | x | _   | 0  | 8             | 0  | 32K | 8000-FFFF              | 4 | 4 | 4 | 4 | 4  | 4 | 4        | 4 | All 4K.                                                                                                                                                                                                |

| 6a            | x                                          | _ | _   | _ | x⁺  | 4  | 0             | 0  | 32K | 8000-FFFF              | 8 | 8 | 8 | 8 | _  | _ | -        | _ | This option and option 6b go together. The MEMEX line is tied to decoder PROM input A8, so a low MEMEX state will select 6a and a high will select 6b.                                                 |

| 7             | .                                          | _ | _   | x | _   | _  | _             | _  |     | _                      | — | ÷ | - | _ |    | _ |          | - | Not programmed. Intentionally left blank for customer's own configuration.                                                                                                                             |

| 8             | х                                          | х | х   | _ | —   | 0  | 4             | 4  | 24K | 0000-5FFF              | 4 | 4 | 4 | 4 | 2  | 2 | 2        | 2 | 4K, 2K mixed; alternate standard.                                                                                                                                                                      |

| 9             |                                            | x | x   | _ | _   | 0  | 1             | 7  | 18K | 3800-7FFF              | 2 | 2 | 2 | 2 | 2  | 2 | 2        | 4 | Use with 7804's standard configuration: three 4K ROM and on<br>2K RAM. Total memory on both cards is 32K. If all 4Ks ar<br>ROM and all 2Ks are RAM, you have 16K ROM and 16K RAM                       |

| 10            | x                                          |   | x   | _ | _   | 0  | 5             | 3  | 26K | 1000-1FFF<br>2800-7FFF | 4 | 2 | 2 | 2 | 4  | 4 | 4        | 4 | Use with 7880 which has 4K ROM and 2K RAM. Option does no<br>have consecutive addresses. Total memory for both cards i<br>32K. If all 4Ks are ROM and all 2Ks are RAM, you have 24K ROM<br>and 8K RAM. |

| 11            | -                                          | _ | х   | - | —   | 0  | 8             | 0  | 32K | 0000-7FFF              | 4 | 4 | 4 | 4 | 4  | 4 | 4        | 4 | All 4Ks. Like option 5 except occupies addresses 0000-7FFF.                                                                                                                                            |

| 12            | x                                          | х | _   |   |     | 0  | 0             | 8  | 16K | 0000-3FFF              | 2 | 2 | 2 | 2 | 2  | 2 | 2        | 2 | All 2Ks. Like option 4 except occupies addresses 0000-3FFF.                                                                                                                                            |

| 13            | —                                          | х | —   | - | X** | 0  | 8             | 0  | 32K | 7FFF-0000              | 4 | 4 | 4 | 4 | 4  | 4 | 4        | 4 | Test option for Pro-Log use only.                                                                                                                                                                      |

| 6b            | x                                          |   | _   | - | X   | 4  | 0             | 0  | 32K | 8000-FFFF              | _ | — | _ | _ | 8  | 8 | 8        | 8 | Dual bank for 2764s; to work with option 6a using MEMEX hig to select.                                                                                                                                 |

| 15            | -                                          |   |     | - |     | _  | _             | -  |     | -                      |   | _ | _ | _ | _  | - | -        | - | Not programmed. Intentionally left blank for customer's owr configuration.                                                                                                                             |

Figure 2-5. Memory Decoder Options

\* Uses MEMEX with a low state at W4. \*\* Uses MEMEX with a high state at W4.

٠

.

Installation and Specification

,

٠

2-5

Installation and Specification

Figure 2-6. 7704 Option 0

2-6

1

Figure 2-7. 7704 Option 1

Installation and Specification

2-8

$\sim$

Figure 2-9. 7704 Option 3

2-10

1

$\bigcirc$

Figure 2-11. Option 5

Figure 2-12. 7704 Option 6a

0

•

Figure 2-13. 7704 Option 7

2-14

Figure 2-15. 7704 Option 9

.

ſ'n

Figure 2-17. 7704 Option 11

.

Figure 2-19. 7704 Option 13

Installation and Specification

Figure 2-20. 7704 Option 6b

.

٠

¢

Figure 2-21. 7704 Option 15

#### MEMORY TYPE

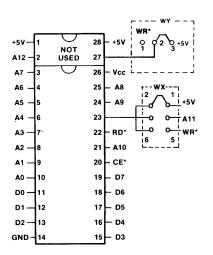

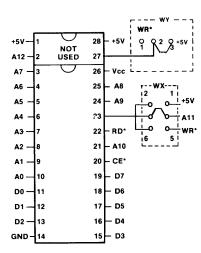

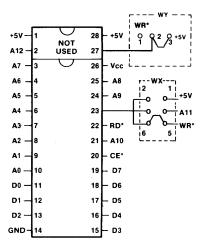

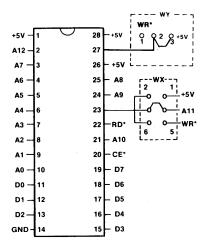

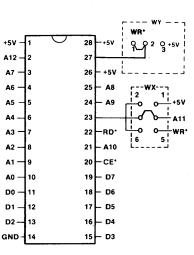

The 7704 uses six kinds of memory: 2K, 4K, and 8K ROMs and RAMs. The eight memory sockets are designed to accept memory components compatible with the JEDEC 28 pin standard pinout. Each socket can be individually configured for the 2K RAMs or any of the ROMs. The 4K and 8K RAMs are the exception. The sockets can only be configured for these in groups of four. The groups will consist either of sockets 0, 1, 2, and 3, or sockets 4, 5, 6, and 7.

After having chosen the memory combination best suited to your needs, as discussed in the Memory Decoder section, the sockets should be configured accordingly. Figure 2-22 shows where to place the memory socket jumpers for each kind of memory. The location of these jumpers is shown in Fig. 2-4. Jumpers W9, W10, W11, W12, W14, W15, W16 and W17 correspond to sockets 0 through 7 respectively. Jumpers W8 and W13 are used to configure the sockets for 4K or 8K RAMs. Jumper W8 affects sockets 0, 1, 2, and 3, jumper W13 affects sockets 4, 5, 6, and 7.

Figure 2-23 is a list of pin compatible memory components for use on the 7704 card. The recommended memory components are indicated by an asterisk. If you wish to use another memory component, compare its data sheet to the socket configurations. Also, check the data sheet for any special requirements, and be sure the parts are fast enough for the processor you will be using.

Note: As of this writing, 4K and 8K byte-wide RAMs are not available and have not been tested on the 7704. Any 4K or 8K byte-wide RAM that conforms to the JEDEC 28 pin standard and is fully static should be able to be used on the 7704. Pro-Log will be evaluating some of these parts as they become available.

t

t

#### 2K EPROM/ROM CONFIGURATION

#### 4K EPROM/ROM CONFIGURATION

#### **2K RAM CONFIGURATION**

### **8K EPROM/ROM CONFIGURATION**

8K or 4K RAM CONFIGURATION (MUST BE USED IN GROUPS OF FOUR)

Figure 2-22. Socket Configurations

| CHIP #                      | ORGANIZATION | ACCESS      |

|-----------------------------|--------------|-------------|

| INTEL CORPORATION           |              |             |

| 218122K                     | 2K SRAM      | 150         |

|                             |              | ]           |

| 2716*                       | 2K EPROM     | 350-650     |

| 2732*                       | 4K EPROM     | 450-550     |

| 2732A*                      | 4K EPROM     | 200-250     |

| 2764*                       | 8K EPROM     | 200-250     |

| MOSTEK CORPORATION          |              |             |

| MK34000                     | 2K ROM       | 350         |

| MK37000                     | 8K ROM       | 300         |

| MK2716*                     | 2K EPROM     | 300         |

| MK2764*                     | 8K EPROM     | 450         |

| MK4802                      | 2K SRAM      |             |

| NATIONAL SEMICONDUCTOR      |              |             |

| MM2716*                     | 2K EPROM     | 350-450     |

| MOTOROLA                    |              |             |

| MCM2716*                    | 2K EPROM     | 250-450     |

| TEXAS INSTRUMENTS           |              |             |

| TMS2516*                    | 2K EPROM     |             |

| MITSUBISHI                  |              |             |

| M58725*                     | 2K SRAM      | 200         |

| NEC MICROCOMPUTERS          |              |             |

| uPD2716*                    | 2K EPROM     | 450         |

| uPD2732*                    | 4K EPROM     | no spec     |

| AMERICAN MICROSYSTEMS (AMI) |              |             |

| S4028                       | 2K SRAM      | 200         |

| SYNERTEK                    |              |             |

| SY2716*                     | 2K EPROM     | 350-450     |

| ОКІ                         |              |             |

| MSM5128*                    | 2K SRAM      | 150-200-250 |

| TOSHIBA                     |              |             |

| TMM2016*                    | 2K SRAM      | 150-250     |

1

1

\*

\*Recommended Devices

Figure 2-23. Memory Components List

#### UNUSED SOCKETS

Aside from different memory types that can be used and the different combinations that can be selected, further tailoring can be done to suit the 7704 card to your application. This can be done by disabling any unused sockets.

Jumpers W7, 1-2 through 7-8, and W6, 7-8 through 1-2, correspond to sockets 0-7 respectively.

When a socket is disabled, the chip select signal is disconnected from the socket. Also the data bus buffer no longer responds to memory requests in the address range of the unused socket. This means that memory on other cards in the system can occupy this address space, without interference from the 7704 card.

Any number and combination of sockets may be disabled. By this method, the 7704 card can be configured to occupy as little as 2K of memory space. These 2K blocks may occupy adjacent address fields or be widely separated. They may be mapped anywhere within a 64K memory system on the natural 2K boundaries.

#### MEMEX

The function and operation of the MEMEX will be explained in Section 3. This section is to explain the jumper options affecting MEMEX.

On the 7704 card, MEMEX can be used in one of two ways. The first method is to use the MEMEX line to enable the card. Using this method, two 7704's can occupy the same address field, only one of which is enabled at a time depending on the logic state of the MEMEX line. The second method seperates the memory on the 7704 into two banks. Only one half of the card is enabled at a time. Therefore, both halves can occupy the same address field.

As shipped, the card employs the first method. The 7704 card is enabled when MEMEX is low. To reverse its polarity, remove jumper W2 from position 1-2 and replace it with one at position 3-4. The location of this jumper is shown in Fig. 2-4. When using two of these cards which are both going to occupy the same address field, one must have its polarity changed.

It is important to ensure that the MEMEX line is not left floating. The line must be either controlled by some other card in the system, or tied to ground on the 7704 itself. Pro-Log processor cards either control the MEMEX line or simply tie it to ground. If there is no card in the system controlling MEMEX, or if you want the card to disregard MEMEX, jumper W1 can be removed from position 3-4 and be replaced by one at position 1-2. This will tie the line to ground and permanently enable the card.

If MEMEX will be used to divide the 7704 into two banks, jumper W1 should be in position 1-2 to permanently enable the card. Also, jumper W4 should be in position 3-4.

Jumper W4 serves two purposes. It is part of the Memory Decoder Control jumpers. A jumper in position 1-2 serves as a low level input to the Memory Decoder. With no jumper installed it is a high level input. A jumper in position 3-4 connects the MEMEX line to the Memory Decoder input. Therefore, by changing the state of the MEMEX line, you can select a different Memory Decoder option. This is not something you would want to do with most of the options. However, with options 6A and 6B it can be done. Option 6A only uses sockets 0-3. Option 6B only uses sockets 4-7. Both options use the same memory address field. Therefore, by controlling the MEMEX line, you can select one of two memory banks on the 7704 card.

#### Segment Select

The function and operation of the Segment Select line will be explained in Section 3. This section is to explain the jumper options affecting Segment Select.

The Segment Select line is not a part of the STD BUS. It is an external line which must be connected on the card ejector side of the 7704, when it is used. Figure 2-2, shows the location of the connector.

The connector type is a 2-pin 0.1 inch center connector. The cable should be a twisted pair, consisting of one signal line and one ground line for added noise immunity. Figure 2-26 shows which pin is signal and which is ground.

An I/O card, such as Pro-Log's 7605 card, along with an RC704 cable can be used to control the line. One output bit, or line, per 7704 card is required. Therefore, one output port can control eight 7704 cards.

As shipped the card is enabled when the Segment Select line is in the high state. Its polarity can be reversed by removing jumper W3 from position 1-2 and replacing it with one at position 3-4. See Fig. 2-4.

With jumper W3 in position 1-2, the Segment Select line can be left unconnected. A pull-up resistor on the line will hold it in the active condition. If jumper W3 is in position 3-4 however, the line must be controlled in some manner, or the card will remain permanently disabled.

#### Specifications

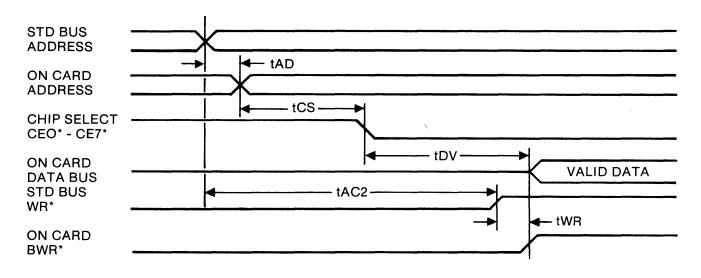

Figures 2-24 and 2-25 are electrical and environmental specifications. Figures 2-26 and 2-27 describe the specifications for the interface connections and card edge connections. Figures 2-28 through 2-33 are the timing requirements necessary for the 7704.

|       | Recommended                         | Operati | ng Limits | Absolute Non-Operating Limits |      |      |       |  |  |

|-------|-------------------------------------|---------|-----------|-------------------------------|------|------|-------|--|--|

| Mnem. | Parameter                           | Min.    | Тур.      | Max.                          | Min. | Max. | Units |  |  |

| Vcc   | Supply Voltage                      | 4.65    | 5.00      | 5.35                          | 0    | 7.00 | Volts |  |  |

| _     | Free Air Temp.                      | 0       | +25       | +55                           | -40  | +75  | °C    |  |  |

|       | Non-Condensing<br>Relative Humidity | 5       |           | 95                            | 5    | 95   | %RH   |  |  |

Figure 2-24. Electrical and Environmental Specifications

| Mnem. | Parameter          | Min. | Тур. | Max  | Units    |

|-------|--------------------|------|------|------|----------|

| lcc   | Vcc Supply Current |      |      | 500* | MilliAmp |

\*With memory sockets empty

۲

ł

+

| Figure | 2-25. | Electrical | Characteristics |

|--------|-------|------------|-----------------|

| Ŭ      |       |            |                 |

|                      | PIN NUMBER |   |   |     | IBER                |

|----------------------|------------|---|---|-----|---------------------|

| OUTPUT (LSTTL DRIVE) |            |   |   | οι  | JTPUT (DRIVE)       |

| INPUT (LSTTL LOADS)  |            |   |   | Г   | INPUT (LSTTL LOADS) |

| MNEMONIC             |            |   |   |     | MNEMONIC            |

| SEGMENT 0*           | 5          | 2 | 1 | GND | GROUND              |

\*Active low-level logic

| <b>Figure 2-26.</b> | Interface Specifications |

|---------------------|--------------------------|

|---------------------|--------------------------|

| PIN NUMBER           |                     |    |    |    | PIN NUMBER     |     |                    |  |

|----------------------|---------------------|----|----|----|----------------|-----|--------------------|--|

| OUTPUT (LSTTL DRIVE) |                     |    |    |    | OUTPUT (DRIVE) |     |                    |  |

| INPUT (LSTTL LOADS   | INPUT (LSTTL LOADS) |    |    |    |                |     | NPUT (LSTTL LOADS) |  |

| MNEMONIC             |                     |    |    |    |                |     | MNEMONIC           |  |

| +5 VOLTS             | vcc                 |    | 2  | 1  |                | vcc | +5 VOLTS           |  |

| GROUND               | GND                 |    | 4  | 3  |                | GND | GROUND             |  |

| -5V                  |                     |    | 6  | 5  |                |     | -5V                |  |

| D7                   | 1                   | 55 | 8  | 7  | 55             | 1   | D3                 |  |

| D6                   | 1                   | 55 | 10 | 9  | 55             | 1   | D2                 |  |

| D5                   | 1                   | 55 | 12 | 11 | 55             | 1   | D1                 |  |

| D4                   | 1                   | 55 | 14 | 13 | 55             | 1   | D0                 |  |

| A15                  | 1                   |    | 16 | 15 |                | 1   | A7                 |  |

| A14                  | 1                   |    | 18 | 17 |                | 1   | A6                 |  |

| A13                  | 1                   |    | 20 | 19 |                | 1   | A5                 |  |

| A12                  | 1                   |    | 22 | 21 |                | 1   | A4                 |  |

| A11                  | 1                   |    | 24 | 13 |                | 1   | A3                 |  |

| A10                  | 1                   |    | 26 | 25 |                | 1   | A2                 |  |

| A9                   | 1                   |    | 28 | 27 |                | 1   | A1                 |  |

| A8                   | 1                   |    | 30 | 29 |                | 1   | A0                 |  |

| RD*                  | 1                   |    | 32 | 31 |                | 1   | WR*                |  |

| MEMRQ*               | 1                   |    | 34 | 33 |                |     | IORQ*              |  |

| MEMEX*               | 1                   |    | 36 | 35 |                |     | IOEXP*             |  |

| MCSYNC*              |                     |    | 38 | 37 |                |     | REFRESH*           |  |

| STATUS 0*            |                     |    | 40 | 39 |                |     | STATUS 1*          |  |

| BUSRQ*               |                     |    | 42 | 41 |                |     | BUSAK*             |  |

| INTRQ*               |                     |    | 44 | 43 |                |     | INTAK*             |  |

| NMIRQ*               |                     |    | 46 | 45 |                |     | WAITRQ*            |  |

| PBRESET*             |                     |    | 48 | 47 |                |     | SYSRESET*          |  |

| CNTRL*               |                     |    | 50 | 49 |                |     | CLOCK*             |  |

| PC1                  | IN                  |    | 52 | 51 | Ουτ            |     | PC0                |  |

| AUX GND              |                     |    | 54 | 53 |                |     | AUX GND            |  |

| AUX -V               |                     |    | 56 | 55 |                |     | AUX +V             |  |

\* Active low-level logic

Figure 2-27. Edge Connector Pin List

#### Installation and Specification

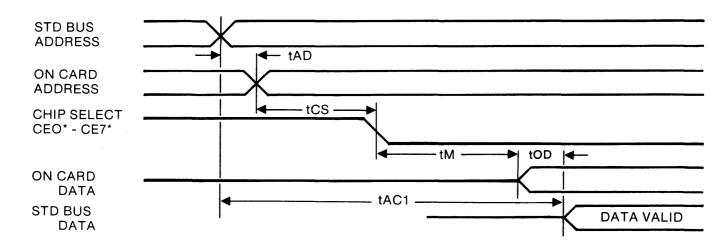

|                                 |                                                                                                                                                                                                                                                                | NA   | NOSECON              | IDS                   |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|-----------------------|

| SYMBOL                          | PARAMETER                                                                                                                                                                                                                                                      | MIN. | TYP.                 | MAX.                  |

| tAC<br>tAD<br>tCS<br>tDV<br>tWR | 7704 minimum safe write cycle time<br>Addreses buffer delay time (STD Bus to memory socket)<br>Chip select logic time (STD Bus to memory socket)<br>Chip select to data valid time (STD Bus to memory socket)<br>Write buffer delay (STD Bus to memory socket) | 220  | 18<br>45<br>74<br>12 | 30<br>70<br>112<br>18 |

All above times are assuming that WR\*, MEMRQ\*, MEMEX and SEGMENT are true prior to STD BUS address becoming true.

A memory device with an access time equal to tDV was used here. A memory device faster than tDV will not improve the access time of the card.

To find write access time of the 7704 with a specific memory device of longer than 112 nsec access time use the following equations.

# tWA = tAC - tDV + tAA $tWA \ge tAC$

Where: tWA = Total access time of card and memory device for write.

tAC = 7704 minimum safe write cycle time.

tDV = 7704 chip select till data valid at memory chips.

tAA = Memory device access time.

If device access time (tAA) is less than or equal to 112 nsec then tAC is the total access time (200 nsec).

\* LOW LEVEL ACTIVE

#### Figure 2-28. 7704 Timing for Write

| SYMBOL | PARAMETER                                            | NA  | NANOSECONDS |     |  |  |

|--------|------------------------------------------------------|-----|-------------|-----|--|--|

| STMDUL | FARAMETER                                            | MIN | ТҮР         | MAX |  |  |

| tAC    | Minimum safe access time for read                    | 220 |             |     |  |  |

| tAD    | Address buffer time delay                            |     | 18          | 30  |  |  |

| tCS    | Chip select logic time<br>Data bus buffer time delay |     | 45          | 70  |  |  |

| tOD    |                                                      |     | 8           | 12  |  |  |

| tM     | Data buffer enable time                              |     | 64          | 100 |  |  |

All above times are assuming that RD\*, MEMRQ\*, MEMEX and SEGMENT are active prior to STD BUS address becoming true.

# Figure 2-29. 7704 Timing for Read

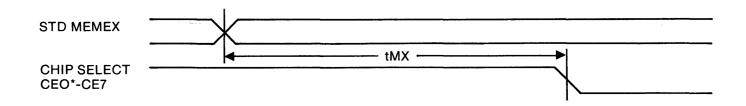

| SYMBOL | PARAMETER                        | NANOSECONDS |     |  |

|--------|----------------------------------|-------------|-----|--|

|        |                                  | TYP         | MAX |  |

| тмх    | Time MEMEX valid to chip select* | 77          | 118 |  |

The above parameter true if all other signals are active prior to MEMEX going active.

# Figure 2-30. 7704 MEMEX Timing

## Installation and Specification

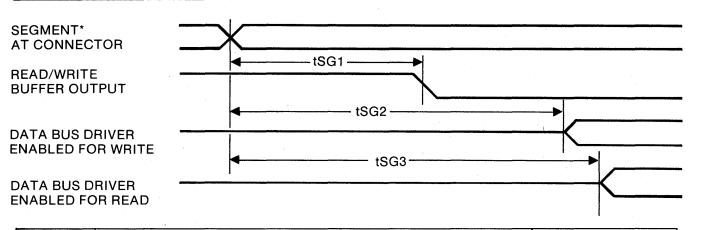

|                      |                                                                                                                                                              | NANOSI         | ECONDS           |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|

| SYMBOL               | PARAMETER                                                                                                                                                    | ТҮР            | MAX              |

| tSG1<br>tSG2<br>tSG3 | SEGMENT* valid to RD* + WR* buffer output valid<br>SEGMENT* valid to data bus driver enabled for write<br>SEGMENT* valid to data bus driver enabled for read | 54<br>75<br>81 | 82<br>114<br>122 |

The above parameters are true if all other signals are active prior to Segment\* going active.

# Figure 2-31. 7704 Segments Timing

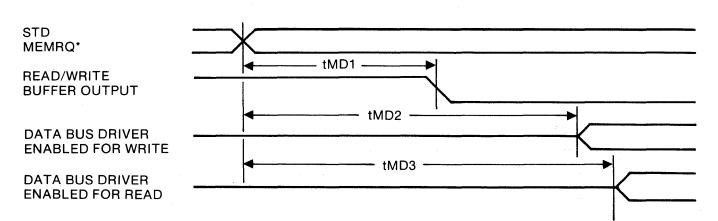

| SYMBOL       |                                                                                                     | NANOSECONDS |            |  |

|--------------|-----------------------------------------------------------------------------------------------------|-------------|------------|--|

| SYMBOL       | PARAMETER                                                                                           | ТҮР         | MAX        |  |

| tMD1         | Time MEMRQ* to RD* + WR* buffer enabled                                                             | 46          | 70         |  |

| tMD2<br>tMD3 | Time MEMRQ* to data bus driver enabled for write<br>Time MEMRQ* to data bus driver enabled for read | 67<br>73    | 102<br>110 |  |

Above parameters valid if all other signals are active prior to MEMRQ\* going active.

Figure 2-32. 7704 Segments MEMRQ\*

| SYMPOL | SYMBOL PARAMETER                               | NANOSEC | NANOSECONDS |  |

|--------|------------------------------------------------|---------|-------------|--|

| STMBUL | PARAMETER                                      | ТҮР     | MAX         |  |

| tRW    | Time RD* or WR* till BRD* or BWR* on 7704 card | 12      | 18          |  |

Above parameter valid if all other signals are active prior to RD\* or WR\* changing state.

# Figure 2-33. 7704 RD\* or WR\* Timing

This section describes the functions and use of the 7704 card. The card is designed to be a versatile part of your memory system.

It can be used in both small and large scale applications. By using the memory size and mapping options described in Section 2 and the MEMEX and Segment Select lines described in this section, the 7704 can fill the memory requirements of virtually any system.

#### MEMEX

The MEMEX line is a part of the STD BUS. It is used as a memory bank select line. Using this line allows two banks of memory to occupy the same address field. Only one of the banks is selected at a time, depending on the logic state of the MEMEX line.

It is normally controlled by a memory segment controller, or an output port. The segment controller or output port can be either on the processor card, or on some other card in the system. Some Pro-Log processor cards have an onboard output port for controlling MEMEX.

#### MEMEX Example

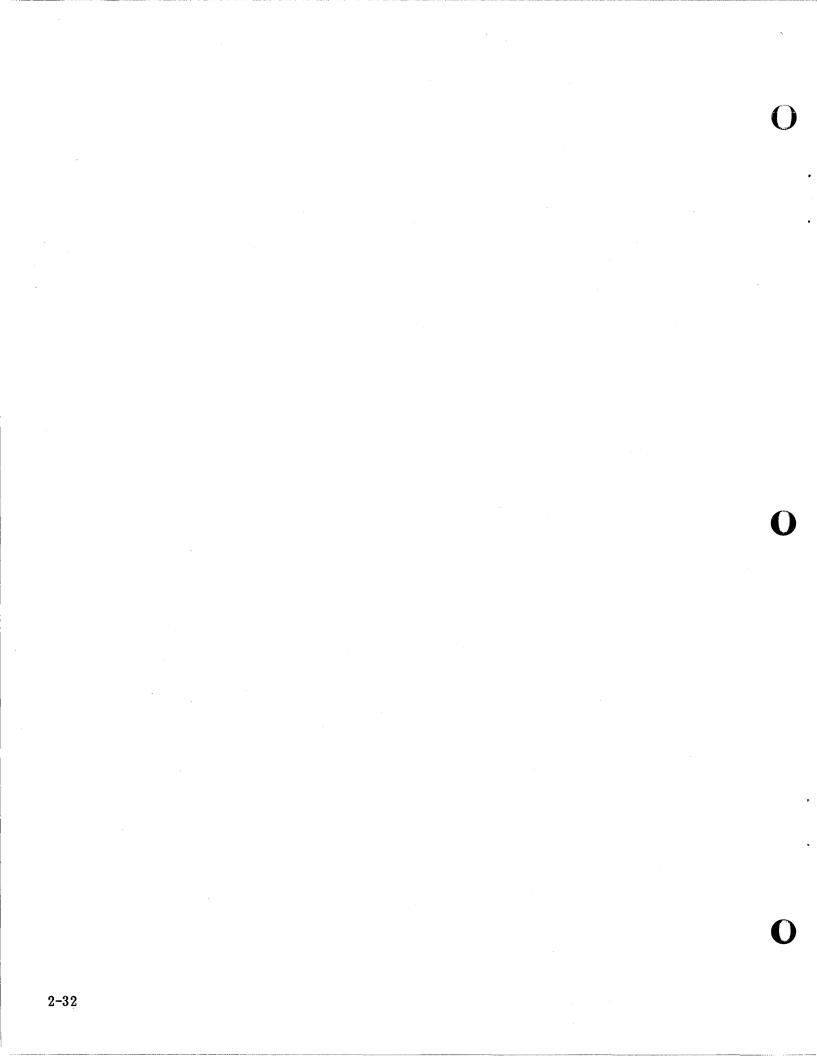

An example of how MEMEX can be used is shown in Fig. 3-1. It shows a 124K memory system. It is comprised of 4K of RAM and 120K of ROM. The RAM is on the processor card and is permanently enabled. That is, it ignores MEMEX. The ROM is in two 60K banks, one bank on each 7704 card. Only one card is enabled at a time dash the one on the left when MEMEX is low, and the one on the right when it is high.

At power up, the MEMEX port is low. The Primary memory bank is therefore enabled. The processor can then choose Primary or Expanded memory simply by manipulating the MEMEX line.

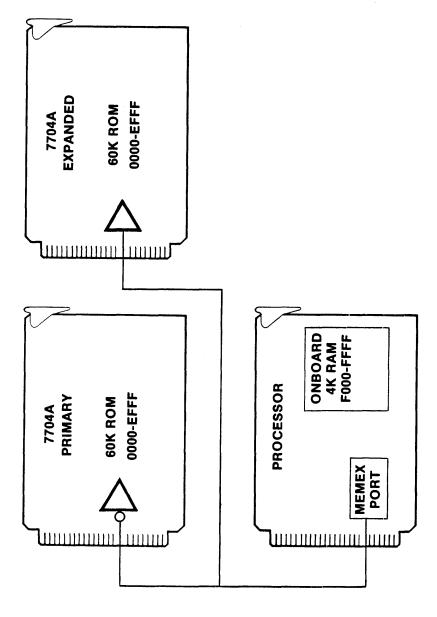

A second example is shown in Fig. 3-2. In this example the two memory banks both reside on one 7704 card. The system has 96K of memory, consisting of 64K ROM and 32K RAM. The 64K ROM is in two banks of 32K each. The RAM is on two 16K RAM cards, and is permanently enabled.

At power up, the MEMEX port is low. Primary memory is therefore enabled. Again, the processor can choose between Primary and Expanded memory simply by manipulating the MEMEX line.

Figure 3-1. 7704 MEMEX Example

Figure 3-2. 7704 MEMEX Example

.

.

#### MEMEX Control Software

The software for controlling MEMEX requires some special consideration. Care must be taken to avoid confusion when changing memory banks.

There are a number of ways to deal with this. What follows are a few examples.

#### **MEMEX Control Software Example One**

In many systems using MEMEX, it will be advantageous to keep some section of memory permanently enabled, a section which disregards MEMEX. This may be a section of ROM memory at the low order addresses, or a section of RAM used to store registers, program variables, and the stack, or a section of ROM containing interrupt service routines that need to be quickly accessible at all times.

If your system will have a permanently enabled section of memory, the MEMEX Control software can reside in this section. If the section is ROM, the program would simply reside in the ROM. If the section is RAM, the processor could load the program into the RAM. The program would be stored in ROM, disc, or some other nonvolatile memory. The processor would load the program into RAM as part of the power-up intialization process.

Using the system in Fig. 3-1 as a model, a program could be written like the one shown in Fig. 3-3. It assumes you are jumping from a main program in one bank to a subroutine in the other bank. The address of the subroutine you are jumping to must be in the HL register pair. The program selects the proper memory bank and jumps to the subroutine. When the subroutine is exited, the processor returns to the MEMEX control program. The program reselects the original bank, then returns to the program from which it came.

Fig. 3-3 shows two programs. One to jump to a subroutine in Expanded memory, and one to jump to a subroutine in Primary memory.

| HE          | ADECIN | AL        |          | MNEMONIC |          | Т        | LE MEMER SAFEWARE ET I DATE  |

|-------------|--------|-----------|----------|----------|----------|----------|------------------------------|

| PAGE<br>ADR |        | INSTR.    | LABEL    | INSTR.   | MODIFIER | COMMENTS |                              |

| FF          | Εo     | 3E        | LTO EXP) | LDAI     |          |          | T SET MEMER MILH ENABLES     |

|             | 1      | 01        |          |          | 01       |          | EXMANDED MEMORY              |

|             | 2      | 03        |          | OPA      |          |          |                              |

|             | 3      | XX        |          | -        | XX       |          | PORT ADORESS                 |

|             | 4      | ES        |          | 25P      | HL_      |          | T PUSH RETURN ADDRESS (FFEA) |

|             | 5      | 21        |          | LOPE     | HL       | 2        | ON TO STOCK                  |

|             | 6      | EA        |          |          |          | a        |                              |

|             | 7      | EP        |          | -        |          | 7        |                              |

|             | 8      | E3        |          | XUT      | HL       | 3        | 4                            |

|             | 9      | Eg        |          | JAN      |          | ₽        | JUMP TO SUBRIUTINE AT HIL    |

|             |        | 3E        |          | LDAI     |          | 2        | T SET MEMER LOW ENABLES      |

|             | В      | 8         |          | -        | 00       | m        | PRIMARY MEMORY               |

|             | C      | D3        |          | DPA      |          | 2        |                              |

|             | D      | XX        |          | -        | XX       | 1        | - PORT ADDRESS               |

|             | E      | 69        |          | RTS      |          |          | J BIT                        |

|             | F      |           | -        |          |          | 2        |                              |

|             | Fo     | 3E        | (TO PRI) | LDAT     |          | E        | T SET MEMER LOW ENABLES      |

|             | 1      | 00        |          | -        | 00       | 3        | PRIMARY MEMORY               |

|             | 2      | 50        |          | OPA      |          | 0        |                              |

|             | 3      | XX        |          | -        |          | X        | PORT ADDRESS                 |

|             | 4      | E5        |          | PSP      | H_       | く        | T PUSH RETURN ADDRESS (FEPA) |

|             | 5      | 21        |          | LDPI     | HL       |          | ONTO STACK                   |

|             | 6      | FA        |          | -        |          |          |                              |

|             | 7      | EE        |          |          |          |          |                              |

|             | 8      | EZ        |          | XCM      | HL       |          |                              |

|             | 9      | Eg        |          | JPN      | HL       |          | JUMP TO JUBRIUTINE AT HL     |

|             | A      | 3E        |          | LDAT     |          |          | T SET MEMER HIGH, ENABLES    |

|             | В      | 01        |          | -        |          |          | EXAMOED MEMORY               |

|             | С      | D3        |          | O?A      |          |          |                              |

|             | D      | XX        |          | -        | XX       |          | - PORT ADORES                |

|             | E      | <u>C9</u> |          | RTS      |          |          | EKIT                         |

|             | F      |           |          |          |          |          |                              |

.

.

$\mathbb{C}$

٠

Figure 3-3. 7704 MEMEX Software Example One

#### **MEMEX** Control Software Example Two

In the first example it was assumed that anytime the program jumped from one bank to the other it was to jump to a subroutine. Fig. 3-4 is a program for jumping from one bank to the other, but not as a subroutine.

The program simply changes the state of the MEMEX line, and then jumps to the address in the HL register pair. Again the program is divided up into two sections dash one to go from Primary to Expanded memory, and one to do the opposite.

| HE   | HEXADECIMAL |          | MNEMONIC |          |          | TITLE MEMEK SOFTWARE EX2. DATE   |  |  |  |  |

|------|-------------|----------|----------|----------|----------|----------------------------------|--|--|--|--|

| PAGE | ADR         | INSTR.   | LABEL    | INSTR.   | MODIFIER |                                  |  |  |  |  |

| FF   | FO          | 3E       | TO EXP   | LDAI     |          | T SET HEMEX HILH SELECT EXPANDED |  |  |  |  |

|      | 1           | 01       |          | -        |          | In Algebrad V                    |  |  |  |  |

|      | 2           | 63       |          | OPA      |          |                                  |  |  |  |  |

|      | 3           | XX       |          | -        |          | PORT ADORESS                     |  |  |  |  |

|      | 4           | Eg       |          | JEN      | H.L      | T JUNP TO ADDREN IN H.L          |  |  |  |  |

|      | 5           |          |          |          |          | S.                               |  |  |  |  |

|      | 6           |          |          |          |          |                                  |  |  |  |  |

|      | 7           |          |          |          |          | 3                                |  |  |  |  |

|      | 8           |          |          |          |          |                                  |  |  |  |  |

|      | 9           | 3E       | TO PRI   | LDAI     |          | T SET MEMER LOW SELECT PLINARY   |  |  |  |  |

|      | •           | $\infty$ |          | -        |          | R MEMORY                         |  |  |  |  |

|      | B           | рз       |          | ASO      |          |                                  |  |  |  |  |

|      | C           |          |          | -        |          | POET ADDRESS                     |  |  |  |  |

|      | D           | Eg       |          | JPN      | м        | FJUMP TO ADDRESS IN HIL PAIR.    |  |  |  |  |

|      | E           |          |          |          |          |                                  |  |  |  |  |

|      | F           |          |          |          |          |                                  |  |  |  |  |

|      | 0           |          |          |          |          |                                  |  |  |  |  |

|      | 1           |          |          |          |          |                                  |  |  |  |  |

|      | 2           |          |          |          |          |                                  |  |  |  |  |

|      | 3           |          |          |          |          |                                  |  |  |  |  |

|      | 4           |          |          |          |          |                                  |  |  |  |  |

|      | 5           |          |          |          |          |                                  |  |  |  |  |

|      | 6           |          |          | l        |          |                                  |  |  |  |  |

|      | 7           |          |          |          |          |                                  |  |  |  |  |

|      | 8           |          |          |          |          |                                  |  |  |  |  |

|      | 9           |          |          | L        |          |                                  |  |  |  |  |

|      | A           |          |          | ļ        |          |                                  |  |  |  |  |

|      | В           |          |          | <u> </u> |          |                                  |  |  |  |  |

|      | c           |          |          |          |          |                                  |  |  |  |  |

|      | D           |          |          |          |          |                                  |  |  |  |  |

|      | E           |          |          | <u> </u> |          |                                  |  |  |  |  |

|      | F.          |          | L        |          |          |                                  |  |  |  |  |

|      |             |          |          |          |          | 199991 2/77                      |  |  |  |  |

Figure 3-4 7704. MEMEX Software Example Two

#### **MEMEX Control Software Example Three**

So far we have looked at MEMEX control software residing in a section of memory which is permanently enabled. Figures 3-5 and 3-6 show how the control software can reside in memory that is affected by MEMEX.

Figure 3-5 shows how a program can be written to jump from a program in Primary memory to a subroutine in Expanded memory. Note that both sections of the program reside at the same addresses. However, one part is in Primary memory and one part is in Expanded memory.

Figure 3-6 shows how the program looks to the processor. When it is run, it becomes one coherent program.

This program only allows for jumping from Primary memory to a subroutine in Expanded memory and then returning. In normal operation you would probably also want one to do the opposite.

To use the program, you must be in Primary memory. When you want to jump to a subroutine in Expanded memory, you load the address of the subroutine into the HL register pair. Then perform a Jump to Subroutine to the MEMEX control program. The program will direct the processor to change memory banks and jump to the subroutine. After running the subroutine, the processor will return to your original program.

| HEXADECIMAL |             | AL     | MNEMONIC |        |          |     |        | NEMEX SOFTWARE EX. 3 DATE   |

|-------------|-------------|--------|----------|--------|----------|-----|--------|-----------------------------|

| PAGE        | LINE<br>ADR | INSTR. | LABEL    | INSTR. | MODIFIER |     |        | NEMEX SOFTWARE EX.3 DATE    |

| FF          | FO          | 3E     |          | LDAT   |          |     | 11     | JUMP TO EXPAND NEMOKY       |

|             | 1           | 01     |          | -      | 01       | P   |        |                             |

|             | 2           |        |          | OPA    |          | 70  | П      |                             |

|             | 3           | XX     |          | -      |          | -   | 1      | - POFT ADORESS              |

|             | 4           | 00     |          | NOP    |          | 2   | F      | T UNUSED                    |

|             | 5           | 60     |          | NOP    |          | Þ   |        |                             |

|             | 6           | 60     |          | NOP    |          | 70  | Π      |                             |

|             | 7           | 00     |          | NOP    |          | X   |        |                             |

|             | 8           | 00     |          | NOP    |          |     |        |                             |

|             | 9           | .00    |          | NOP    |          | Z   |        |                             |

|             | A           | 00     |          | NOP    |          | n,  | Π      |                             |

|             | B           | 00     |          | NOP    |          | Z   | Π      |                             |

|             | C           | 00     |          | NOP    |          | þ   | Π      |                             |

|             | D           | 00     |          | NOP    |          | RX  |        | 1                           |

|             | E           | Ca     |          | RTS    |          |     | 1      | EXIT                        |

|             | F           |        |          |        |          |     |        |                             |

| FF          | FO          | 00     |          | NOP    |          |     | 1.     | T UNWED                     |

|             | 1           | 00     |          | NOP    |          | m   |        |                             |

|             | 2           | 00     |          | NoP    |          | X   |        |                             |

|             | 3           | 00     |          | Nof    |          | 9   |        | <u>.</u>                    |

|             | 4           | E5     |          | PSP    | HL       | >   |        | T PULH RETURN ADDAEX (EFFA) |

|             | 5           | 21     |          | LOPT   | HL       | Z   |        | ONTO STACK                  |

|             | 6           | FA     |          |        |          | 0   | 1      |                             |

|             | 7           | EF     |          |        |          | n . | L      |                             |

|             | 8           | E3     |          | XCPT   | HL       | Ø   | 1      | ¥                           |

|             | 9           | _69_   |          | JPN    | <u> </u> |     |        | JUMP TO SUBRITINE AT HIL    |

|             | A           | 3E     |          | LDAT   |          | 2   |        | T JUMP TO PRIMARY MEMORY    |

|             | B           | 00     | ·····    |        | 00       | m   |        |                             |

|             | <u>c</u>    |        |          | ASO    |          | 2   |        |                             |

| L           | D           | XX     |          | -      |          | 2   |        | + - PORT ADDRESS            |

|             | E           | 00     |          | NOP    |          | K   | $\bot$ | UNUSED                      |

| L           | F           |        | L        |        |          |     | 1      |                             |

#### Figure 3-5. 7704 MEMEX Software Example Three

| HEXADECIMAL |            | AL     | MNEMONIC                              |            |            | TITLE RUNNING EX3 DATE                  |

|-------------|------------|--------|---------------------------------------|------------|------------|-----------------------------------------|

| PAGE        | LINE       | INSTR. | LABEL                                 | INSTR.     | MODIFIER   |                                         |

| FF          | F٥         | 3E     |                                       | LDAI       |            | TJUMP TO EXPAND MEMORY                  |

|             | 1          | 01     |                                       | -          | 01         | A JUMP TO EXPAND MEMORY                 |

|             | 2          | D3     |                                       | OPA        |            |                                         |

|             | 3          | XX     |                                       |            |            | PORT ADDRESS                            |

|             | 4          | ES     |                                       | PSP        | HL         | T PUSH RETURN ADDRESS ONTO STACK (FEFA) |

|             | 5          | 21     |                                       | LOPI       | HL         |                                         |

|             | 6          | FA     |                                       |            |            |                                         |

|             | 7          | FF     |                                       |            |            |                                         |

| L           | 8          | ЕĴ     |                                       | XCPT       | HL         | - <b>*</b>                              |

|             | 9          | Eg     |                                       | JPN        | HL         | Z JUMP TO SUBROUTINE AT HIL             |

|             | A          | 3E     |                                       | LDAI       |            | & T JUMP TO PLIMARY MEMORY              |

|             | B          | 8      |                                       |            |            | 4                                       |

| L           | _ c        | D3     |                                       | D?A        |            |                                         |

|             | D          | XX     |                                       | -          |            | PORT ADDRESS                            |

|             | E          | C9     |                                       | RTS        |            | EXIT                                    |

|             | F          |        |                                       |            |            |                                         |

|             | 0          |        |                                       |            |            |                                         |

|             | 1          |        | · · · · · · · · · · · · · · · · · · · |            |            |                                         |

|             | 2          |        |                                       |            |            |                                         |

|             | 3          |        |                                       |            |            |                                         |

|             | 4          |        |                                       |            |            |                                         |

|             | 5          |        |                                       | <u> </u> i |            |                                         |

|             | 6          |        |                                       |            |            |                                         |

|             | 7          |        |                                       | <u> </u>   |            |                                         |

|             | 8          |        |                                       |            |            |                                         |

|             | 9          |        |                                       |            |            |                                         |

| <u> </u>    | <u>A</u>   |        |                                       |            |            |                                         |

| ┣           | B          |        |                                       |            |            |                                         |

|             | <u>.</u> C |        |                                       |            |            |                                         |

| <u> </u>    | D          |        |                                       |            | ···· • • • |                                         |

|             | E          |        |                                       |            |            |                                         |

| L           | F          | L      | L                                     | 1          |            | 100001 2/77                             |

Figure 3-6. 7704 Running Example Three

#### **MEMEX Control Software Example Four**

The example shown in Fig. 3-7 is similar to the last example. In this one however, rather than jumping from one bank to another as a subroutine, this program performs a simple jump.

This program is in two sections. One to go from Primary to Expanded memory, and one to do the opposite.

Fig. 3-8 shows how the programs looks to the processor. To the processor, either program appears to be one coherent program.

To use the program, load the address of the program you want to jump to into the HL register pair. Then jump to the MEMEX control program. The processor is directed to change memory banks, then jump to the program you requested.

| HEXADECIMAL |            | MNEMONIC |    |     |        |          | TITLE MEMER SOFTWARE EX4. DATE |              |                                       |  |

|-------------|------------|----------|----|-----|--------|----------|--------------------------------|--------------|---------------------------------------|--|

| PAGE<br>ADR | ADB        | INSTR.   | LA | BEL | INSTR. | MODIFIER |                                | -=. <i>I</i> | COMMENTS                              |  |

| FF          | FO         |          | То | EXP | LDAI   |          |                                | I T          | Jime TO EXEMDED MEMORY                |  |

|             | 1          | 01       |    |     |        | 01       |                                |              |                                       |  |

|             | 2          | 13       |    |     | OPA    |          | P                              |              |                                       |  |

|             | 3          | XX       |    |     | -      |          | 79                             | ¥            | - PORT ADDRESS                        |  |

|             | 4          | 00       |    |     | NOP    |          | -                              | Ŧ            | UNUSED                                |  |

|             | 5          |          |    |     |        |          | Z                              |              |                                       |  |

|             | 6          |          |    |     |        |          | A                              |              |                                       |  |

|             | 7          |          |    |     |        |          | R                              |              |                                       |  |

|             | 8          | 00       | 10 | PRI | NOP    |          | ×                              | T            | UNUSED                                |  |

|             | 9          | 00       |    |     | NOP    |          |                                |              |                                       |  |

|             |            | 00       |    |     | NOP    |          | 3                              |              |                                       |  |

|             | ·B         | $\infty$ |    |     | NOP    |          | <u>n</u>                       |              |                                       |  |

|             | .c         | Eg       |    |     | JPN    | HL       | 3                              | _            | JUMP TO ADDRESS W H,L                 |  |

|             | <u>; D</u> |          |    |     |        |          | 0                              |              | · · · · · · · · · · · · · · · · · · · |  |

|             | E          |          |    |     |        |          | 70                             |              |                                       |  |

|             | F          |          |    |     |        |          | X                              |              |                                       |  |

| FF          | FO         | $\infty$ | TO | EX? | NOP    |          |                                | 1            | UNDSED                                |  |

|             | 1          | 00       |    |     | NOP    |          | m                              |              |                                       |  |

|             | 2          | 00       |    |     | NOP    |          | ×                              |              |                                       |  |

|             | 3          | 00       |    |     | NOP    |          | P                              | _            | L                                     |  |

|             | 4          | E9       |    |     | JPN    | HL.      | >                              | - 1          | E JUMP TO MODIESS IN HIL              |  |

|             | 5          |          |    |     |        |          | 2                              |              |                                       |  |

|             | 6          |          |    |     |        |          | v                              |              |                                       |  |

|             | 7          |          |    |     | +      |          | n                              |              |                                       |  |

|             |            | 3E       | TO | IFI | LDAI   |          | Ø                              |              | SUMP TO PRIMARY MEMORY                |  |

|             | 9          | 00       |    |     |        | 00       |                                |              | · · · · · · · · · · · · · · · · · · · |  |

|             | A          | 22       |    |     | OPA    |          |                                |              |                                       |  |

|             | 8          | XX       |    |     |        |          | m                              | _1           | - PORT ADDLESS                        |  |

|             | c          | 00       |    |     | NOP    |          | 3                              |              | E UNUSED                              |  |

|             | D          |          |    |     |        |          | 80                             |              |                                       |  |

|             | E          |          |    |     |        |          | - K                            |              |                                       |  |

|             | F          | L        |    |     |        |          |                                |              | 1400                                  |  |

Figure 3-7. 7704 MEMEX Software Example Four

| HE            | HEXADECIMAL |            | MNEMONIC |        |          | TITLE RUNNING EX4 DATE    |

|---------------|-------------|------------|----------|--------|----------|---------------------------|

| ADR           |             | INSTR.     | LABEL    | INSTR. | MODIFIER | COMMENTS                  |

| FF            | FO          | 3E         | TO EXP   | LPAT   |          | T JUNI TO EXPANOED MEMORY |

|               | 1           | 01         |          | -      | 01       |                           |

|               | 2           | 03         |          | OPA    |          | ROLT MODERS               |

|               | 3           | XX         |          | -      |          | PORT MODERSS              |

|               | 4           | 19         |          | JPN    | HL       | T JUMP TO ADDRESS IN HL   |

|               | 5           |            |          |        |          |                           |

|               | 6           |            |          |        |          | m<br>X                    |

|               | 7           |            |          |        |          |                           |

|               | 8           | 3E         | TO PPI   | LDAI   |          | Z JUMP TO PRIMARY MEMORY  |

|               | 9           | 00         |          |        | 00       | X                         |

|               |             | <u>b</u> 3 |          | OPA    |          |                           |

|               | 8           | XX         |          | -      |          | - RET ADDERSS             |

|               | ç           | E9         |          | JPN    | HL       | R JUMP TO ADDRESS IN HL   |

|               | D           |            |          | _      |          |                           |

|               | E           |            |          |        |          | <u><u> </u></u>           |

|               | F           |            |          |        |          |                           |

|               | 0           |            |          |        |          |                           |

|               | 1           |            |          |        |          |                           |

|               | 2           |            |          |        |          |                           |

|               | 3           |            |          |        |          |                           |

|               | 4           |            |          | _      |          | ·                         |

|               | 5           |            |          |        |          |                           |

|               | 6           |            |          |        |          |                           |

|               | 7           |            |          |        |          |                           |

|               | 8           |            |          |        |          |                           |

|               | 9           |            |          |        |          |                           |

| J             |             |            |          |        | ·        |                           |

|               | B           |            |          |        |          |                           |

|               | _ç          |            |          |        |          |                           |

|               | 0           |            |          |        |          |                           |

| <b>├</b> ───┤ | 6           |            |          |        |          |                           |

| L             | F           |            | <u> </u> |        |          |                           |

Figure 3-8. 7704 Running Example Four

#### **MEMEX Interrupt Control Software**

This last example shows how interrupt service can be handled in a system using MEMEX.

One method previously mentioned is to set aside an area of memory for interrupt service. This area would be permanently enabled.

A second method can be used if the interrupt service routines are short enough. This method has identical service routines in both Primary and Expanded memory. Both routines would reside at the same addresses. This method may, however, use up too much memory space.

A third method is shown in Fig. 3-9, 3-10, and 3-11. In this method, the service routines reside in only one bank of memory. In the example shown, they reside in Primary memory.

The function of the program is to coordinate the jumping to and returning from the interrupt routine. The program ensures that the processor gets to the service routine. If the processor is in Expanded memory, it directs it to switch to Primary memory. It also ensures that the processor returns to the correct bank, after the interrupt is serviced.