# iSBC 012B TECHNICAL MANUAL

112748

**Revision** A

ţ

April 1982

Copyright<sup>©</sup>1982 Intel Corporation<sup>®</sup>

INTEL CORPORATION Memory Systems Operation 3065 Bowers Avenue Santa Clara, California 95051

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP    | Intel        | iSBX            | Multichannel  |

|--------|--------------|-----------------|---------------|

| CREDIT | Intel        | Library Manager | Multimodule   |

| i      | Intelevision | MCS             | Plug-A-Bubble |

| ICE    | Intellec     | Megachassis     | PRÔMPT        |

| iCS    | iOSP         | Micromainframe  | RMX/80        |

| im     | irmx         | Micromap        | System 2000   |

| iMMX   | iSBC         | Multibus        | UPI           |

| Insite |              |                 |               |

| Revisions |                                              |       |       |  |  |

|-----------|----------------------------------------------|-------|-------|--|--|

| REV       | DESCRIPTION                                  | DATE  | APPR  |  |  |

|           | Released                                     |       |       |  |  |

| A         | RELEASED TO PRODUCTION<br>Per ECO # 12-13406 | 04/82 | MB/kf |  |  |

|           |                                              |       |       |  |  |

|           |                                              |       |       |  |  |

~

# TABLE OF CONTENTS

| HEADING                                 | <u>TITLE</u>                     | PAGE                            |

|-----------------------------------------|----------------------------------|---------------------------------|

|                                         | SECTION 1. GENERAL DESCRIPTION   |                                 |

| 1.1                                     | INTRODUCTION                     | 1 - 1                           |

| 1.2                                     | HARDWARE CHARACTERISTICS         | 1 - 1                           |

| 1.3                                     | OPERATION                        | 1 - 1                           |

| 1.4                                     | SPECIFICATIONS                   | 1-2                             |

|                                         | SECTION 2. INSTALLATION          |                                 |

| 2.1                                     | INTRODUCTION                     | 2-1                             |

| 2.2                                     | SAFETY PRACTICES                 | 2-1                             |

| 2.3                                     | UNPACKING AND INSPECTION         | 2-2                             |

| 2.4                                     | TEST EQUIPMENT AND SPECIAL TOOLS | 2-2                             |

| 2.5                                     | POWER REQUIREMENTS               | 2-2                             |

| 2.6                                     | COOLING REQUIREMENTS             | 2-4                             |

| 2.7                                     | INTERFACE SPECIFICATIONS         | 2-4                             |

| 2.8                                     | JUMPER CONFIGURATIONS            | 2-4                             |

| 2.9                                     | ADDRESS RANGE SELECTION          | 2-12                            |

| 2.10                                    | iSBC 012B INSTALLATION PROCEDURE | 2-13                            |

|                                         | SECTION 3. OPERATION             |                                 |

| 3.1                                     | INTRODUCTION                     | 3-1                             |

| 3.2                                     | OPERATING PRINCIPLES             | 3-1                             |

| 3.3                                     | INPUT/OUTPUT SIGNAL DESCRIPTION  | 3-1                             |

| 3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4 | STANDARD OPERATING MODES         | 3-4<br>3-4<br>3-5<br>3-7<br>3-9 |

## TABLE OF CONTENTS (Continued)

# HEADING

# TITLE

- -

#### SECTION 3. OPERATION (Continued)

| 3.5   | SPECIAL OPERATING FEATURES.    | • |   |   |   | • | • | • | • |   |   |   | • | • |   |   | • | 3-10 |

|-------|--------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|

| 3.5.1 | Parity Generation and Checking | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 3-10 |

| 3.5.2 | Powerfail Memory Protection .  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |

### SECTION 4. THEORY OF OPERATION

| 4.1   | INTRODUCTION                    | 1  |

|-------|---------------------------------|----|

| 4.2   | STANDARD LOGIC SYMBOLS          | 1  |

| 4.2.1 | Electrical Criteria             | l  |

| 4.2.2 | Logical Criteria                | 2  |

| 4.3   | iSBC 012B IC DEVICE DESCRIPTION | 3  |

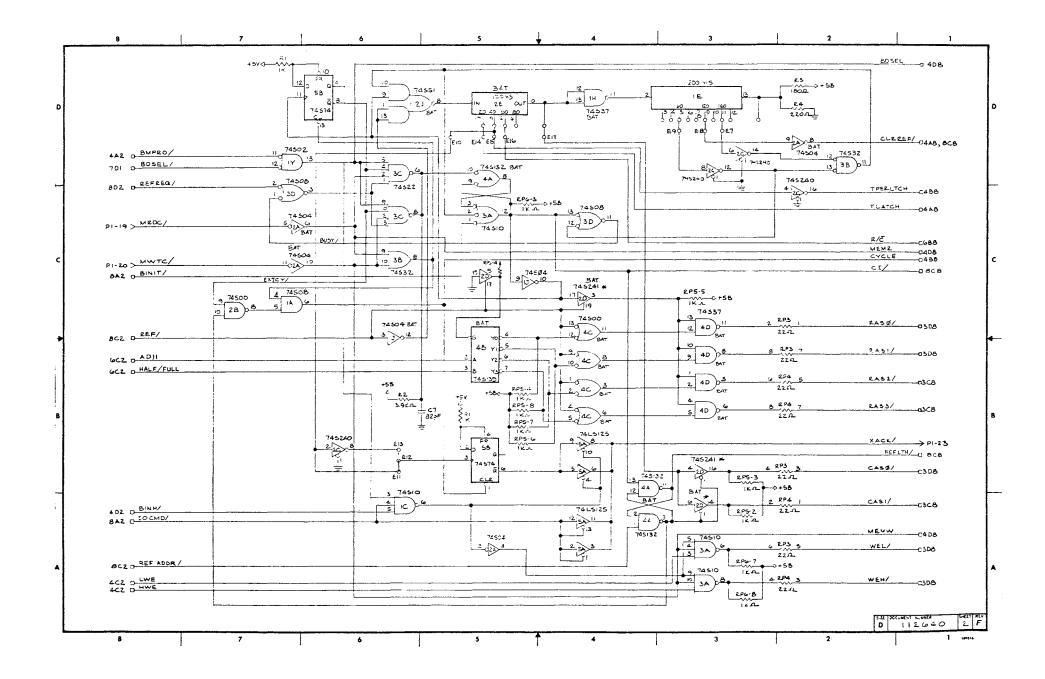

| 4.4   | OVERVIEW OF ISBC 012B CIRCUITRY | 14 |

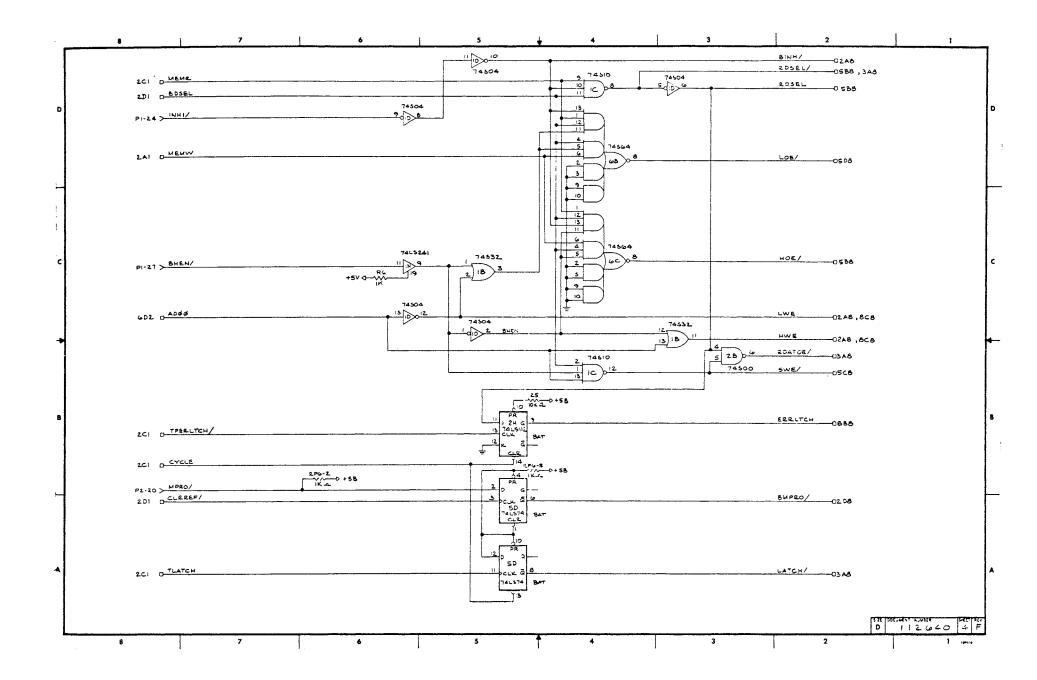

| 4.5   | DESCRIPTION OF CIRCUITRY BLOCKS | 18 |

| 4.5.1 | Address Circuitry               | 18 |

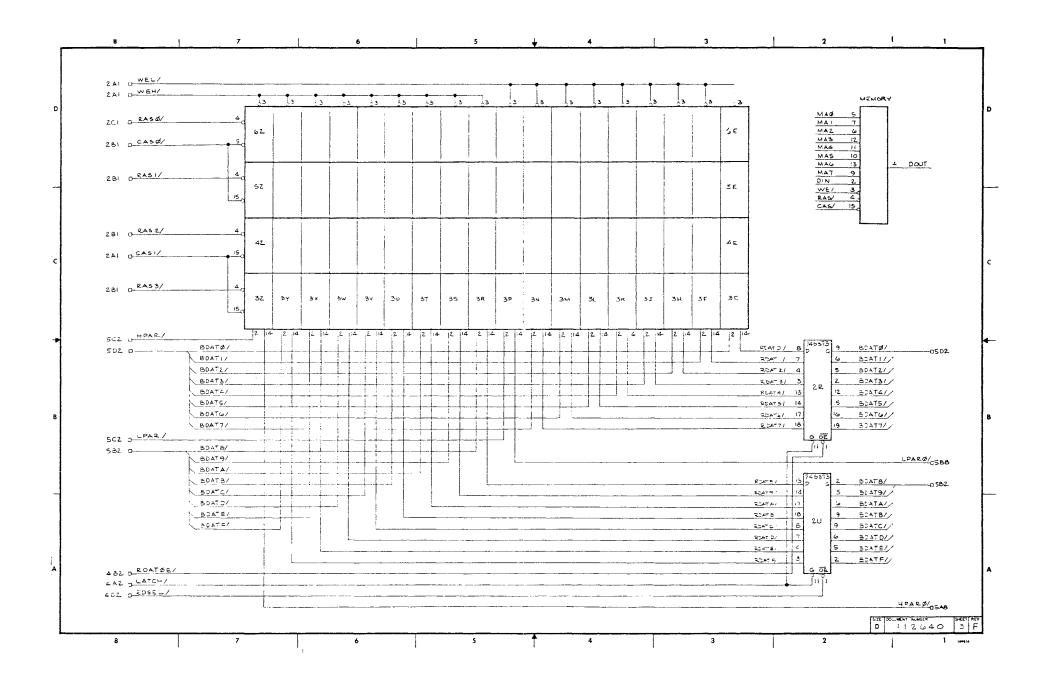

| 4.5.2 | Data Circuitry                  | 23 |

| 4.5.3 |                                 | 26 |

| 4.5.4 | Memory/Refresh Cycle Circuitry  | 28 |

| 4.5.5 | Address Strobe Circuitry        | 34 |

| 4.5.6 | Acknowledge Circuitry           | 35 |

| 4.5.7 | Memory Protection Circuitry     | 37 |

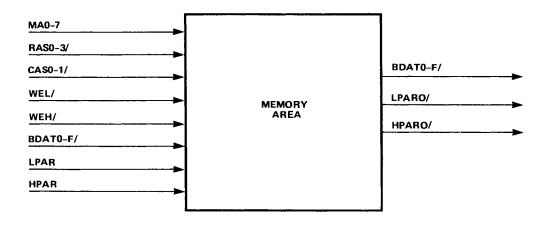

| 4.5.8 | Memory Area                     | 37 |

### SECTION 5. MAINTENANCE

| 5.1 | INTRODUCTION                    | 5-1 |

|-----|---------------------------------|-----|

| 5.2 | PREVENTIVE MAINTENANCE          | 5-1 |

| 5.3 | TROUBLESHOOTING                 | 5-1 |

| 5.4 | ISOLATING A FAILING MEMORY CHIP | 5-2 |

| 5.5 | SERVICE AND REPAIR              | 5-3 |

# TABLE OF CONTENTS (Continued)

| HEADING | TITLE                                              | PAGE  |

|---------|----------------------------------------------------|-------|

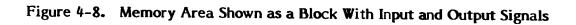

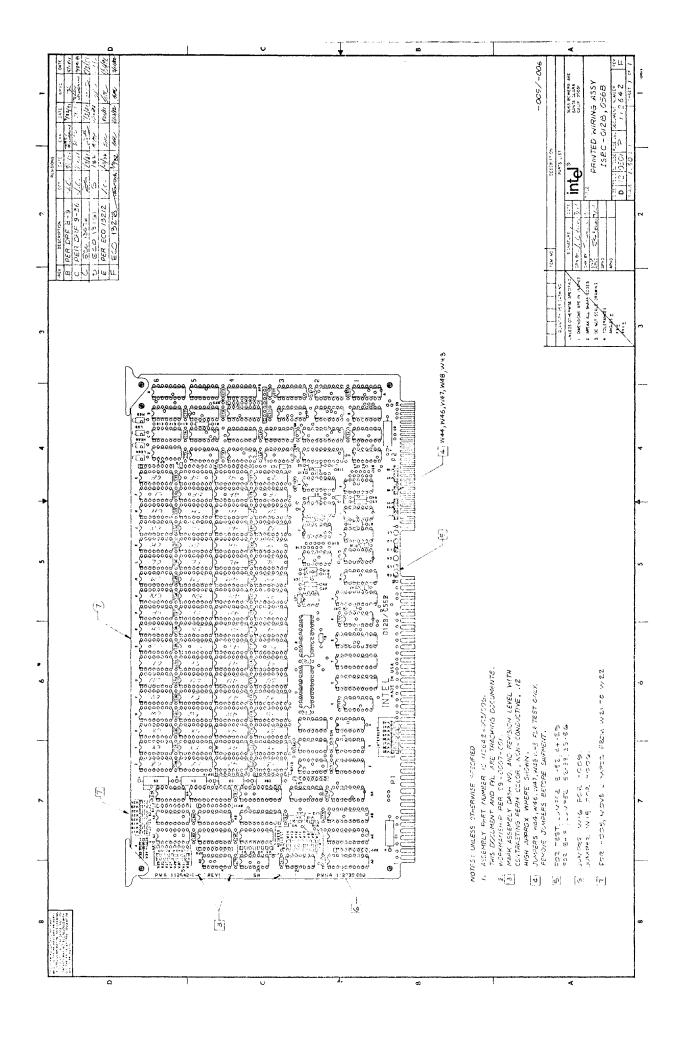

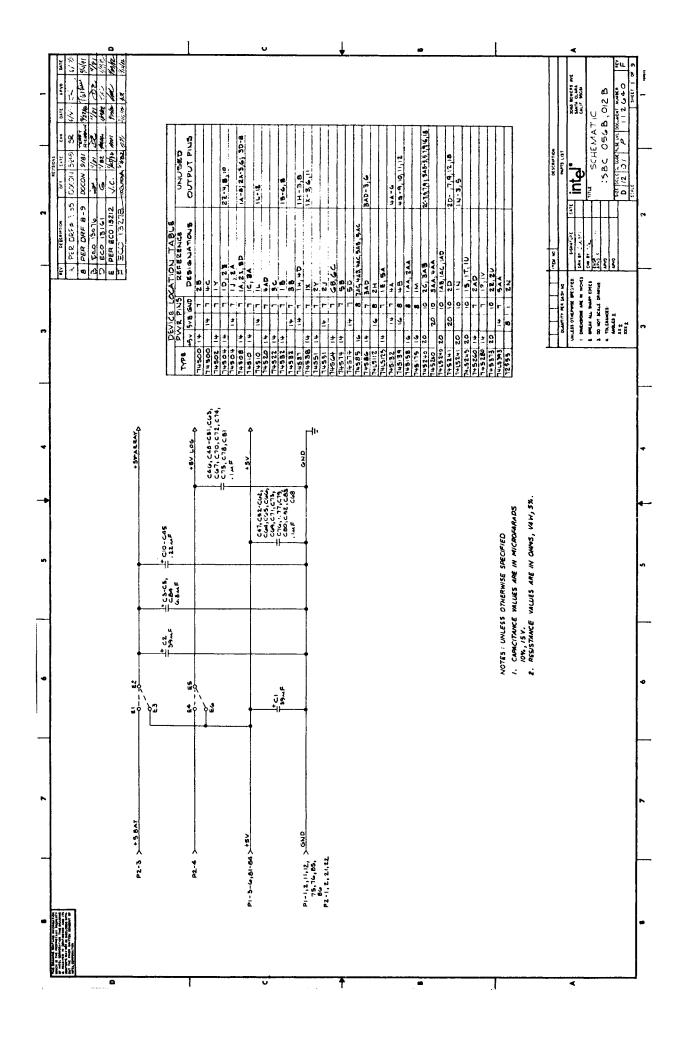

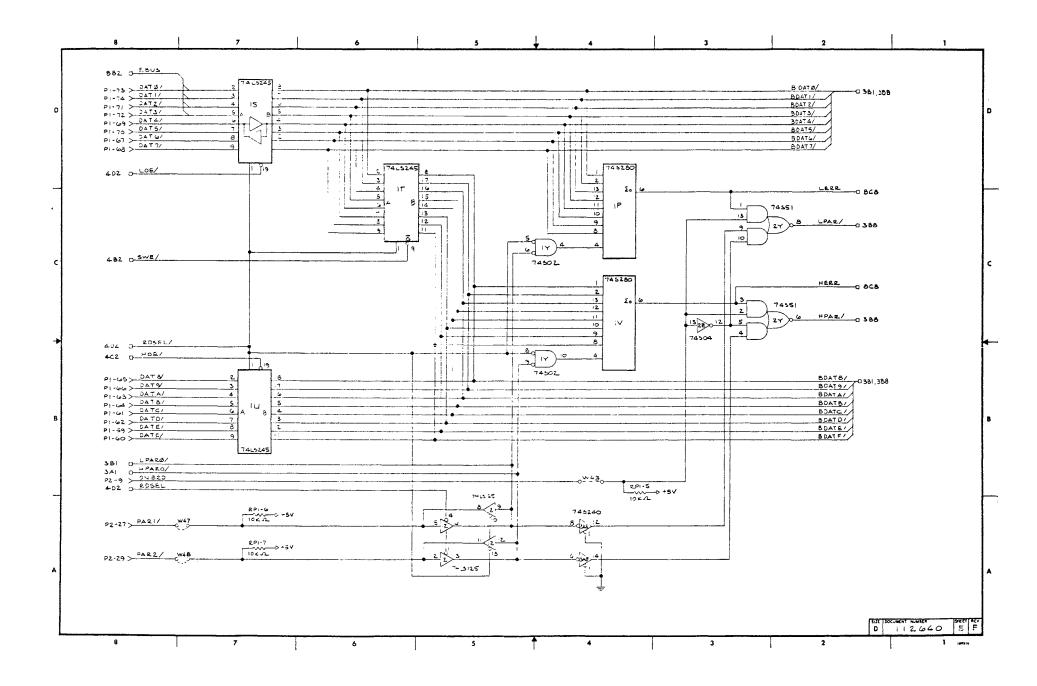

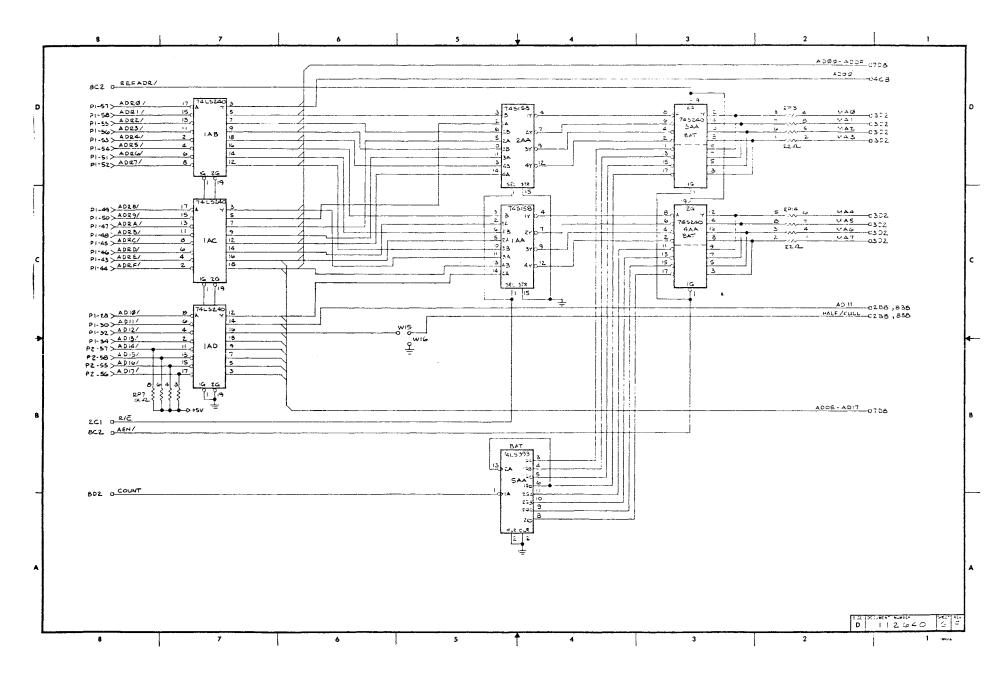

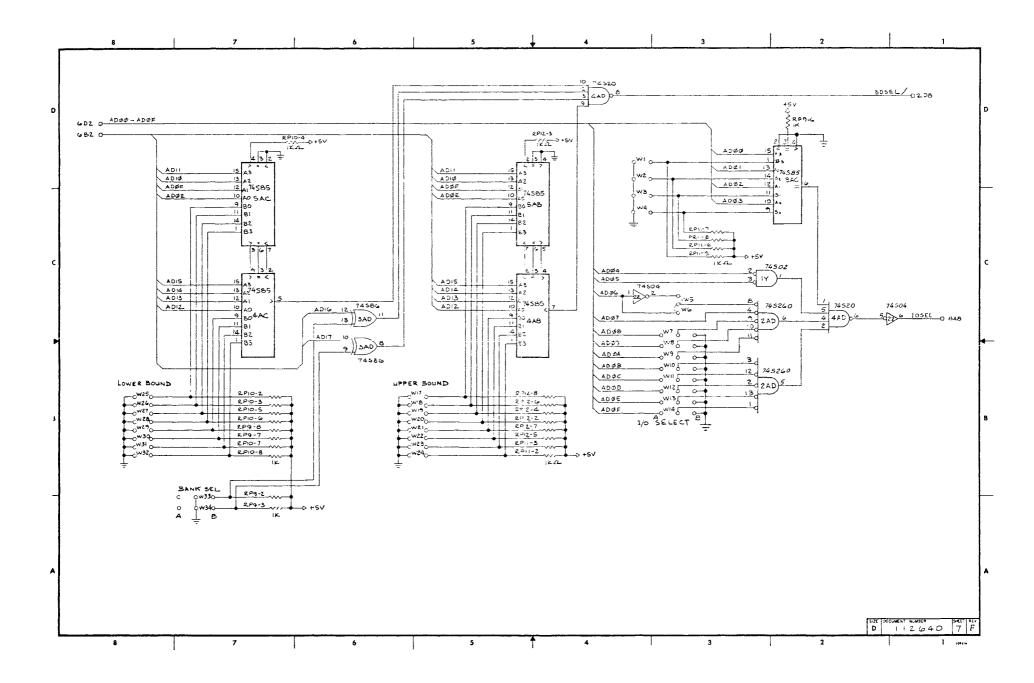

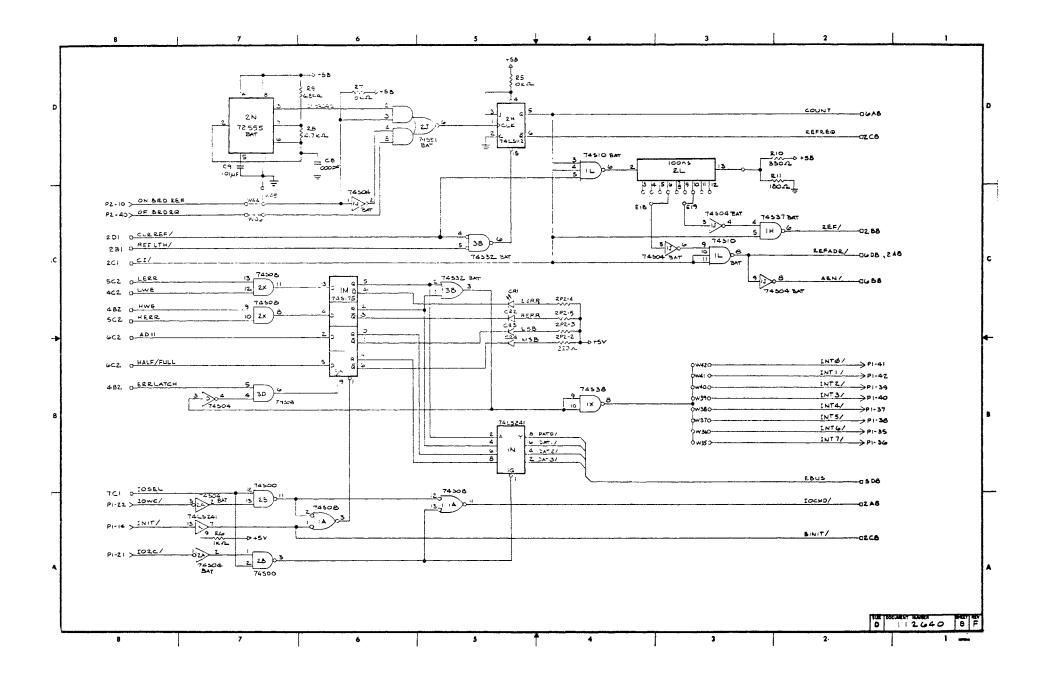

|         | SECTION 6. ENGINEERING DRAWINGS                    |       |

| 6.1     | INTRODUCTION                                       | 6-1   |

| 6.2     | ASSEMBLY DRAWING, PARTS LIST AND SCHEMATIC DIAGRAM | 6-1   |

|         | APPENDIX A. FILING A FREIGHT CLAIM                 | A-1   |

|         | APPENDIX B. SERVICE INFORMATION                    |       |

| B.1     | INTRODUCTION                                       | B-1   |

| B.2     | SERVICE AND REPAIR ASSISTANCE                      | B-1   |

|         | READER COMMENT CARD Located Inside Back            | Cover |

#### LIST OF ILLUSTRATIONS

| FIGURE            | TITLE                                                                                                                   | PAGE                    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|

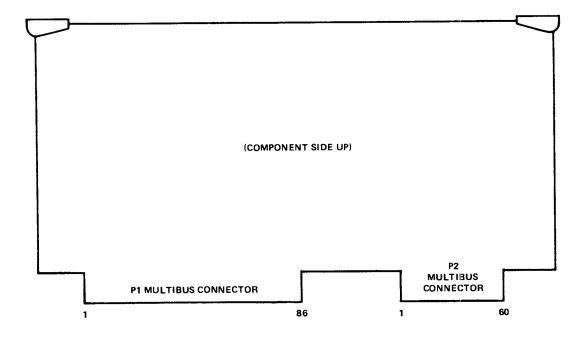

| 2-1               | P1 and P2 Multibus Connectors                                                                                           | 2-4                     |

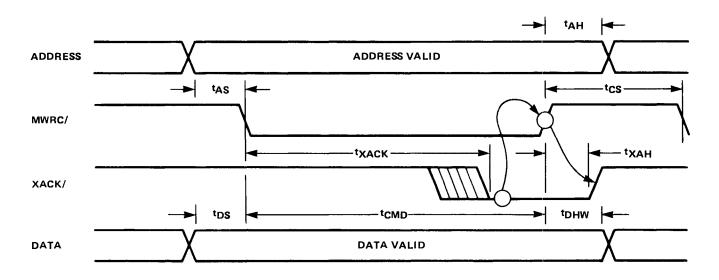

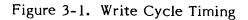

| 3-1<br>3-2        | Write Cycle Timing                                                                                                      | 3-6<br>3-8              |

| 4-1<br>4-2<br>4-3 | iSBC 012B Overall Block Diagram                                                                                         | 4-17/18<br>4-21<br>4-22 |

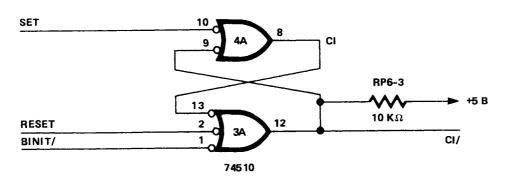

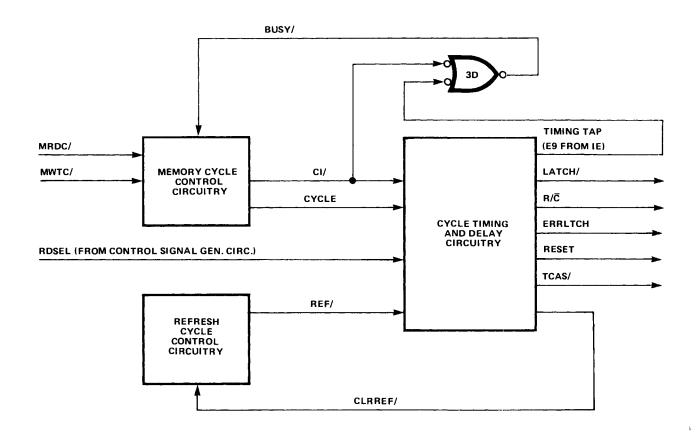

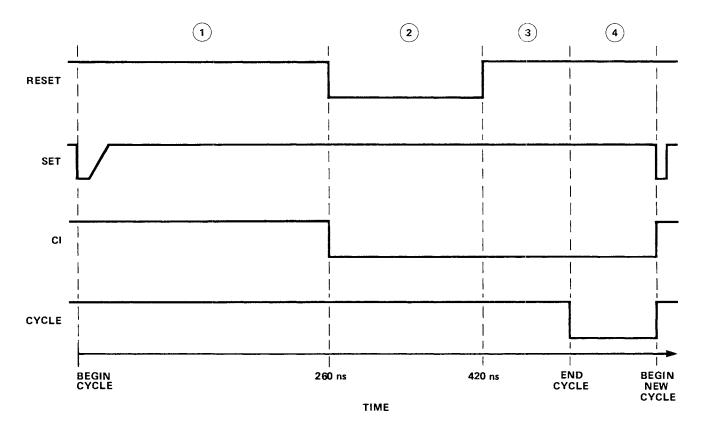

| 4-4<br>4-5        | R-S Flip-Flop in Memory Cycle Control Circuitry                                                                         | 4-28<br>4-29            |

| 4-6<br>4-7        | Simplified Block Diagram of Memory/Refresh Control Circuitry<br>Memory Chip Layout on iSBC 012B Board, Showing Rows 0-3 | 4-32                    |

| 4-8               | and the Low and High Banks                                                                                              | 4-38<br>4-38            |

| 5-1               | Row/Bank Diagram for Bad Chip Determination                                                                             | 5-3                     |

# LIST OF TABLES

# TABLE

Į

# TITLE

# PAGE

| 1-1 | iSBC 012B Specifications                                  | 1-2  |

|-----|-----------------------------------------------------------|------|

| 2-1 | Test Equipment                                            | 2-3  |

| 2-2 |                                                           | 2-3  |

| 2-3 |                                                           | 2-3  |

| 2-4 |                                                           | 2-5  |

| 2-5 |                                                           | 2-7  |

| 2-6 |                                                           | 2-8  |

| 3-1 | Input/Output Signals on the P1 Connector                  | 3-2  |

| 3-2 | Input/Output Signals on the P2 Connector                  | 3-4  |

| 3-3 |                                                           | 3-5  |

| 4-1 | Ena ble and Inhibit Functions                             | 4-3  |

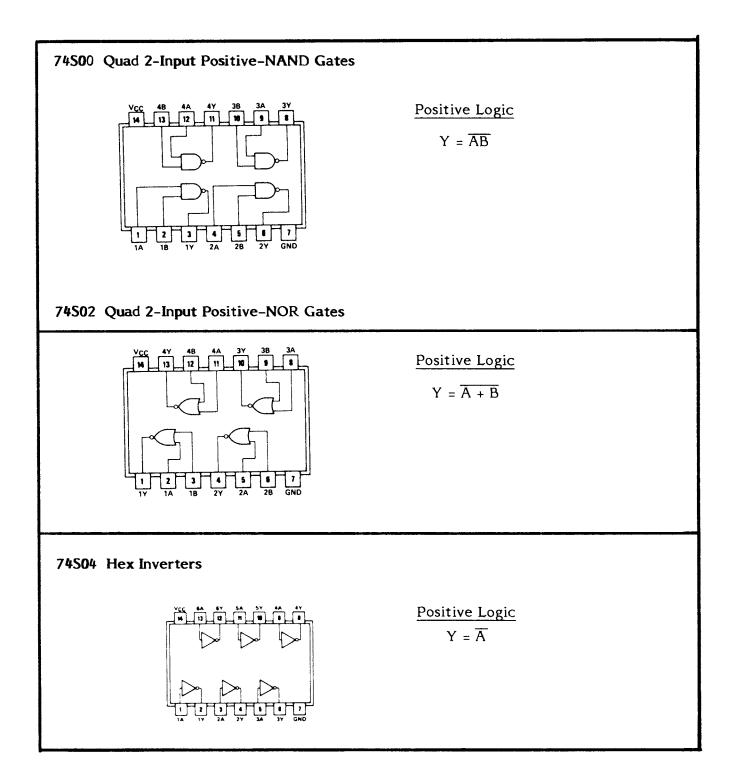

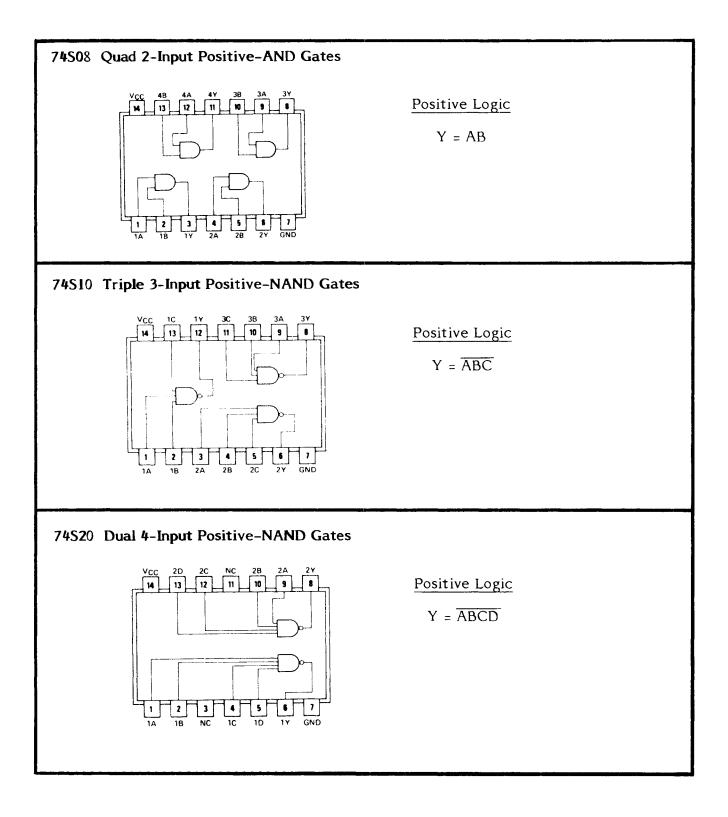

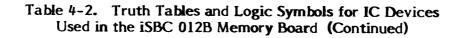

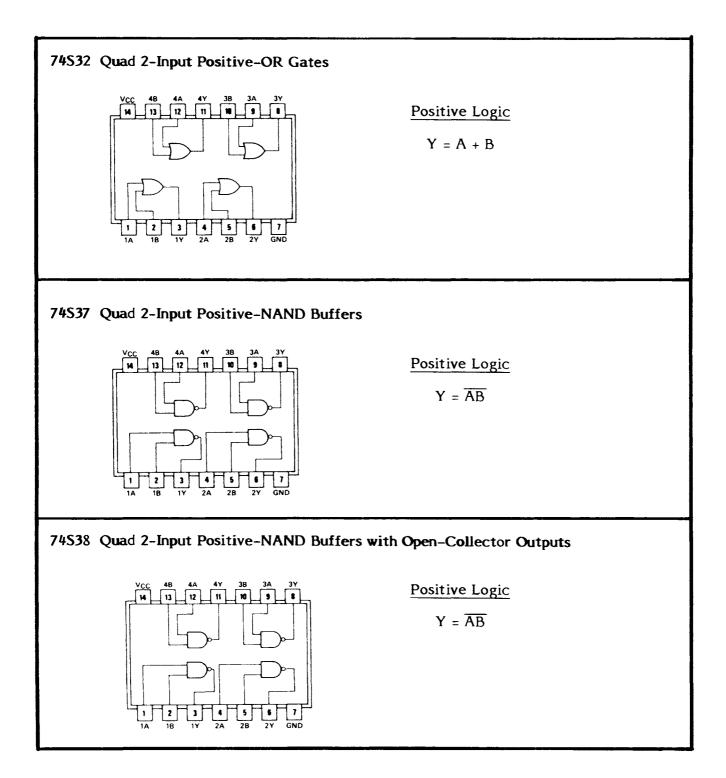

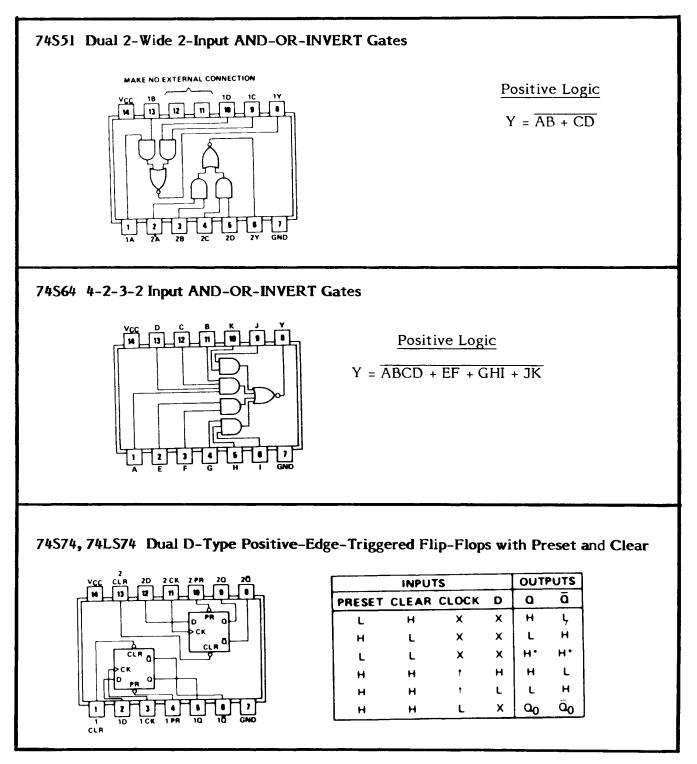

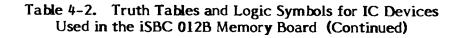

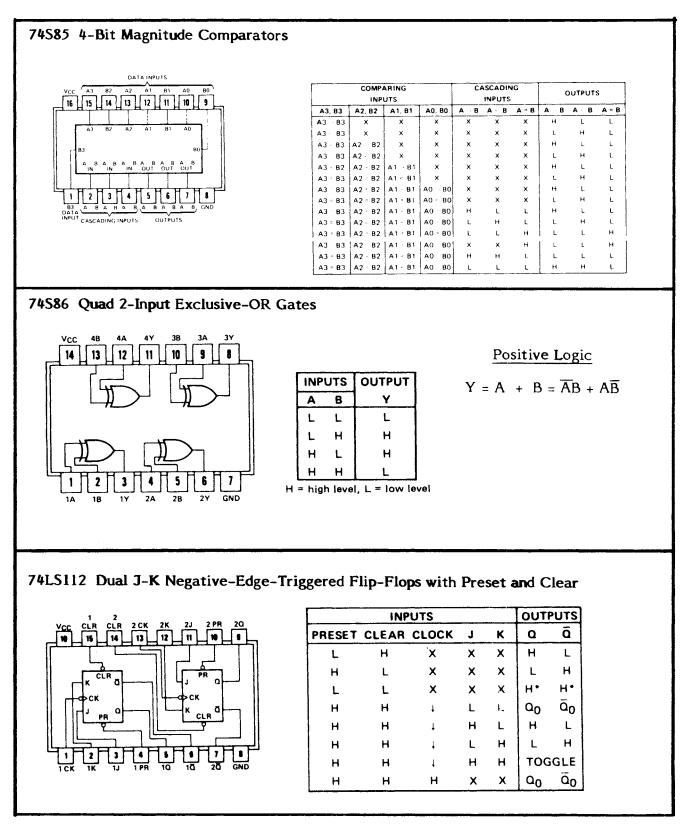

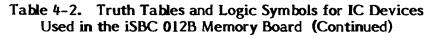

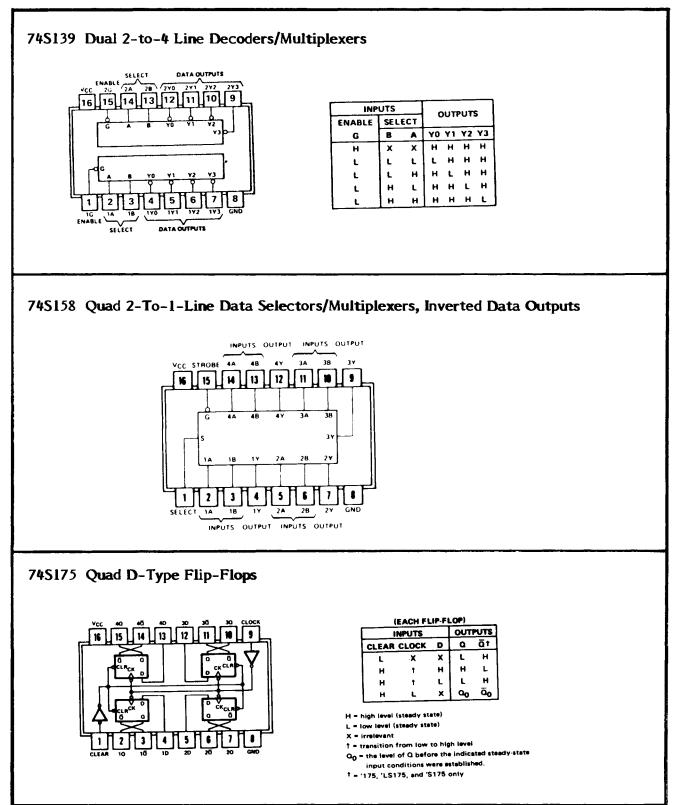

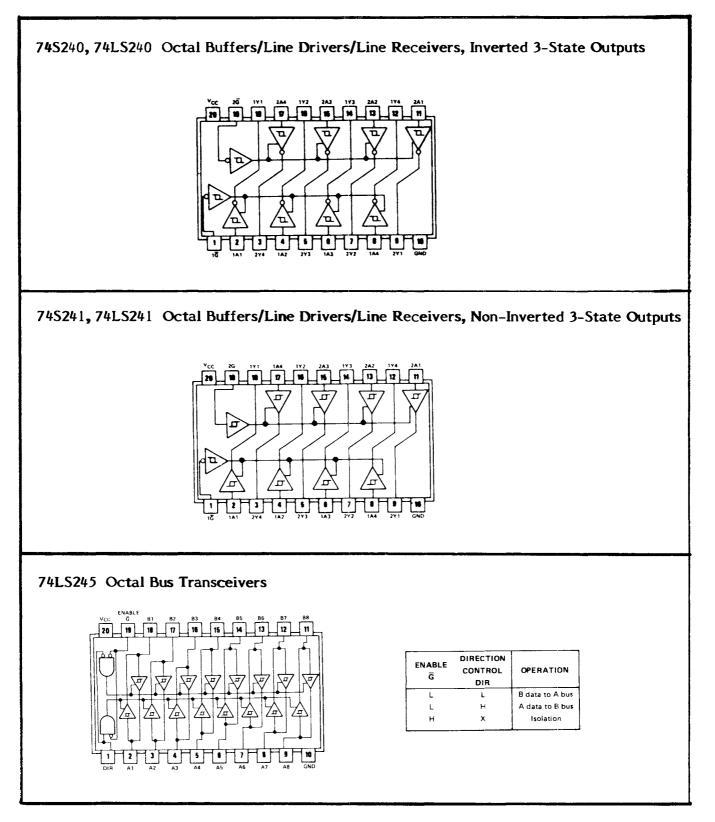

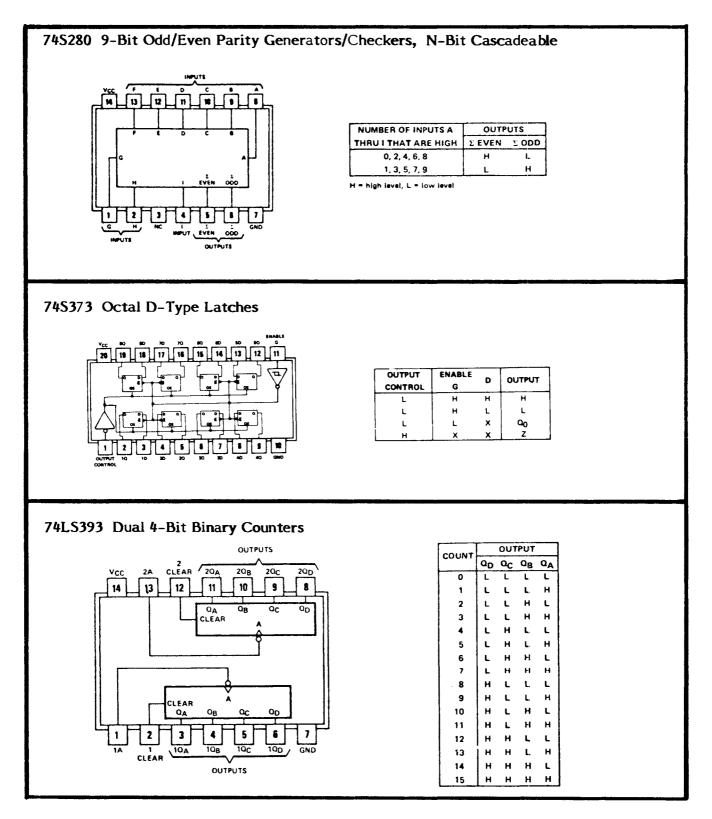

| 4-2 | Truth Tables and Logic Symbols for IC Devices Used in the |      |

|     |                                                           | 4-4  |

| 4-3 | Control Signals and Data Transfer Types                   | 4-25 |

| 5-1 | Preventive Maintenance Activities                         | 5-1  |

#### **SECTION 1**

### GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

The iSBC 012B is a 512K byte Multibus-compatible MOS dynamic RAM memory board. On-board parity generation enhances reliability, while circuitry to support battery backup is provided as protection against power failure.

### 1.2 HARDWARE CHARACTERISTICS

The iSBC 012B memory board consists of a single printed circuit board with the following functional circuit blocks:

- 1. Address Circuitry

- 2. Data Circuitry

- 3. Parity Circuitry

- 4. Memory/Refresh Cycle Circuitry

- 5. Address Strobe Circuitry

- 6. Acknowledge Circuitry

- 7. Memory Protection Circuitry

- 8. Memory Area.

These blocks are described in detail in Section 4, Theory of Operation.

### 1.3 OPERATION

The iSBC 012B operates in three modes: write, read and refresh. Write and read operations are initiated by the user, whereas refresh cycles are initiated automatically by an on-board pulse generator, or optionally by an off-board pulse generator, and are completely transparent to the user. An on-board parity generator/checker generates and stores a parity bit for each byte that is written and checks the byte against this parity bit when the byte is read out of memory. If an error is found, parity-related data may be read from the parity error I/O port.

Access to the iSBC 012B is via the Multibus lines.

### 1.4 SPECIFICATIONS

iSBC 012B specifications are summarized below:

| Item               | Description                                                                                         |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| STORAGE CAPACITY   |                                                                                                     |  |  |  |  |  |

|                    | 512K bytes (256K words)                                                                             |  |  |  |  |  |

| BYTE SIZE          | 8 bits                                                                                              |  |  |  |  |  |

| WORD LENGTH        | 2 bytes                                                                                             |  |  |  |  |  |

| ACCESS TIME        | 350ns                                                                                               |  |  |  |  |  |

| MEMORY CYCLE TIME  | 550ns                                                                                               |  |  |  |  |  |

| REFRESH CYCLE TIME | 550ns                                                                                               |  |  |  |  |  |

| OPERATING MODES    | Write, read, refresh (transparent to user)                                                          |  |  |  |  |  |

| INTERFACE          | All data, address, and control lines are TTL-<br>compatible and meet Intel Multibus specifications. |  |  |  |  |  |

|                    | Logic Level:                                                                                        |  |  |  |  |  |

|                    | Input: Logic "1" 2.0V to 5.0V<br>Logic "0" 0.0V to 0.8V                                             |  |  |  |  |  |

|                    | Output: Logic "1" 2.4V to 5.0V<br>Logic "0" 0.0V to 0.5V                                            |  |  |  |  |  |

### Table 1-1. iSBC 012B Specifications

| Table 1-1. | iSBC 012B Specifications | (Continued) |

|------------|--------------------------|-------------|

|------------|--------------------------|-------------|

| ITEM                            | DESCRIPTION                                                                                                 |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| POWERFAIL PROTECTION            | On-board circuitry to support battery backup                                                                |  |  |  |  |

| POWER                           | Voltage: +5.0 volts <u>+</u> 5%                                                                             |  |  |  |  |

|                                 | Operating current: 5 Amps max.                                                                              |  |  |  |  |

|                                 | Stand by current: 3.5 Amps max.                                                                             |  |  |  |  |

|                                 | Power down current: 1.2 Amps max.                                                                           |  |  |  |  |

| BOARD DIMENSIONS                | Length: 6.75 in.<br>Width: 12.0 in.<br>Height: 0.5 in.                                                      |  |  |  |  |

| ENVIRONMENTAL<br>SPECIFICATIONS | Operating temperature<br>0 to 55°C<br>Non-operating temperature<br>-40 to 75°C                              |  |  |  |  |

|                                 | Relative humidity<br>10% to 90% without condensation                                                        |  |  |  |  |

|                                 | Shock/vibration<br>Able to withstand class "B" tests per Intel<br>Environmental Specification 9400008 Rev C |  |  |  |  |

|                                 | Altitude<br>Up to 15,000 ft. in operation                                                                   |  |  |  |  |

### SECTION 2

### INSTALLATION

#### 2.1 INTRODUCTION

This section contains instructions for installing the iSBC 012B memory board.

### 2.2 SAFETY PRACTICES

# WARNING

Proper concern for the safety of all personnel is vital when installing equipment. The following safety practices should always be observed.

- 1. Remove all power from the system before installation begins. Remove the AC power plug from the AC receptacle. This is particularly important if modules or components are to be removed.

- 2. Tag all facility circuit breakers associated with the system with **WARNING** tags to prevent an inadvertent turn-on of power during installation.

- 3. Even if power is off, dangerous voltages may still be present. Always discharge capacitors before working on DC power supplies.

- 4. When it is necessary to work on a system with the power on, **never work alone.** Two people must always be present when work is being done within a unit, or on an interconnecting cable, if power is applied.

- Test equipment and certain tools, such as electric drills and wirewrap tools, should always be grounded before use. Follow the instructions in the instruction manuals. Do not defeat the third wire safety ground.

- 6. Keep benches and working areas clear of unnecessary articles.

- Make sure that fire extinguishers of the CO<sub>2</sub> type for electrical fires are readily available.

Throughout this manual, possible threats to personal safety will be prefixed as follows:

# WARNING

Similarly, threats to equipment safety will be prefixed as follows:

# CAUTION

### 2.3 UNPACKING AND INSPECTION

Check all parts received against the shipping list. Remove all packing material from the iSBC 012B memory board. Then check for physical damage, such as broken capacitors or resistors, broken wires, cut traces, loose components, and bent pins. Certain damage, such as a cracked printed board or a failing integrated circuit, may not be detected until power is applied and tests are conducted on the unit. In case of shipping damage, refer to Appendix A for procedures to file a freight claim, and to Appendix B for procedures to return a damaged unit.

### 2.4 TEST EQUIPMENT AND SPECIAL TOOLS

The test equipment required for checkout and trouble analysis of the iSBC 012B memory board is listed in Table 2-1. A recommended field engineering tool kit is listed in Table 2-2.

### 2.5 **POWER REQUIREMENTS**

The power requirements for an iSBC 012B memory board are shown below in Table 2-3.

| Equipment         | Description       | Use                     |

|-------------------|-------------------|-------------------------|

| Digital voltmeter | 0.1 volt accuracy | Measurement of voltage. |

# Table 2-1. Test Equipment

# Table 2-2. Field Engineering Tool Kit

| Item | Description                      |

|------|----------------------------------|

| 1    | Slotted-head screwdriver set     |

| 2    | Phillips-head screwdriver set    |

| 3    | Socket wrench set                |

| 4    | Needle-nose pliers               |

| 5    | Soldering iron                   |

| 6    | Desoldering tool (solder sucker) |

| 7    | Solder, resin core               |

| 8    | Integrated circuit test clips    |

Table 2-3. iSBC 012B Power Requirements

| Operati <b>o</b> n                   | Power (Max.)                         |

|--------------------------------------|--------------------------------------|

| Continuous<br>Memory Cycles          | +5VDC x 5.0 amps = 25.0 watts (max.) |

| Stand by –<br>Refresh Cycles<br>Only | +5VDC x 3.5 amps = 17.5 watts (max.) |

| Battery Backup                       | +5VDC x 1.2 amps = 6.0 watts (max.)  |

#### 2.6 COOLING REQUIREMENTS

The iSBC 012B memory board temperature must be maintained between 0 to 55°C.

#### 2.7 INTERFACE SPECIFICATIONS

The edge connectors P1 and P2 (shown in Figure 2-1) provide the interface to the Multibus system. P1 connector assignments are listed in Table 2-4; the P2 assignments are listed in Table 2-5.

### 2.8 JUMPER CONFIGURATIONS

Table 2-6 lists the possible jumper connections and describes the function of each.

530 - 001

Figure 2-1. P1 and P2 Multibus Connectors

#### NOTE

This figure shows the PI and P2 Multibus connectors. The odd pins are on the component side, the even pins on the solder side.

|                                   | COMPONENT SIDE                               |                                                                      |                                                                 |                                        | SOLD                                                                 | ER SIDE                                                                          |

|-----------------------------------|----------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                   | Pin                                          | Mnemonic                                                             | Description                                                     | Pin                                    | <b>Mn</b> emonic                                                     | Description                                                                      |

| Power<br>Supplies                 | 1<br>3<br>5<br>7<br>9<br>11                  | GND<br>+5V<br>+5V<br>Not Used<br>Not Used<br>GND                     | Ground<br>+5VDC<br>+5VDC<br>Ground                              | 2<br>4<br>6<br>8<br>10<br>12           | GND<br>+5V<br>+5V<br>Not Used<br>Not Used<br>GND                     | Ground<br>+ 5VDC<br>+ 5VDC<br>Ground                                             |

| Bus<br>Controls                   | 13<br>15<br>17<br>19<br>21<br>23             | Not Used<br>Not Used<br>MRDC/<br>IORC/<br>XACK/                      | Memory Read Command<br>I/O Read Command<br>Transfer Acknowledge | 14<br>16<br>18<br>20<br>22<br>24       | INIT/<br>Not Used<br>Not Used<br>MWTC/<br>IOWC/<br>INH1/             | Initialize<br>Memory Write Command<br>I/O Write Command<br>Inhibit 1 Disable RAM |

| Bus<br>Controls<br>and<br>Address | 25<br>27<br>29<br>31<br>33                   | Not Used<br>BHEN/<br>Not Used<br>Not Used<br>Not Used                | Byte High Enable                                                | 26<br>28<br>30<br>32<br>34             | Not Used<br>AD10/<br>AD11/<br>AD12/<br>AD13/                         | Address<br>Bus                                                                   |

| Interrupts                        | 35<br>37<br>39<br>41                         | INT6/<br>INT4/<br>INT2/<br>INT0/                                     | Parallel<br>Interrupt<br>Requests                               | 36<br>38<br>40<br>42                   | INT7/<br>INT5/<br>INT3/<br>INT1/                                     | Parallel<br>Interrupt<br>Requests                                                |

| Address                           | 43<br>45<br>47<br>49<br>51<br>53<br>55<br>57 | ADRE/<br>ADRC/<br>ADRA/<br>ADR8/<br>ADR6/<br>ADR4/<br>ADR2/<br>ADR0/ | Address<br>Bus                                                  | 44<br>46<br>50<br>52<br>54<br>56<br>58 | ADRF/<br>ADRD/<br>ADRB/<br>ADR9/<br>ADR7/<br>ADR5/<br>ADR3/<br>ADR1/ | Address<br>Bus                                                                   |

Table 2-4. P1 Connector Pin Assignments

|                   | COMPONENT SIDE                               |                                                                      |                                    | SOLDER SIDE                                  |                                                                      |                                    |

|-------------------|----------------------------------------------|----------------------------------------------------------------------|------------------------------------|----------------------------------------------|----------------------------------------------------------------------|------------------------------------|

|                   | Pin                                          | Mnemonic                                                             | <b>Descriptio</b> n                | Pin                                          | Mnemonic                                                             | Description                        |

| Data              | 59<br>61<br>63<br>65<br>67<br>69<br>71<br>73 | DATE/<br>DATC/<br>DATA/<br>DAT8/<br>DAT6/<br>DAT4/<br>DAT2/<br>DAT0/ | Data<br>Bus                        | 60<br>62<br>64<br>66<br>68<br>70<br>72<br>74 | DATF/<br>DATD/<br>DATB/<br>DAT9/<br>DAT7/<br>DAT5/<br>DAT3/<br>DAT1/ | Data<br>Bus                        |

| Power<br>Supplies | 75<br>77<br>79<br>81<br>83<br>85             | GND<br>Not Used<br>+5V<br>+5V<br>GND                                 | Ground<br>+5VDC<br>+5VDC<br>Ground | 76<br>78<br>80<br>82<br>84<br>86             | GND<br>Not Used<br>+5V<br>+5V<br>GND                                 | Ground<br>+5VDC<br>+5VDC<br>Ground |

Table 2-4. P1 Connector Pin Assignments (Continued)

|        | СОМР     | ONENT SIDE      |     | SO       | LDER SIDE                               |

|--------|----------|-----------------|-----|----------|-----------------------------------------|

| Pin    | Mnemonic | Description     | Pin | Mnemonic | Description                             |

| 1      | GND      | Ground          | 2   | GND      | Ground                                  |

| 3      | 5VB      | +5V Battery     | 4   | 5VB      | +5V Battery                             |

| 5      | Not Used | 197 Battery     | 6   | Not Used | , , , , , , , , , , , , , , , , , , , , |

| 7      | Not Used |                 | 8   | Not Used |                                         |

| 7<br>9 | ONBRD    | On Board Parity | 10  | ONBRDREF | On Board Refresh                        |

| 11     | Not Used |                 | 12  | Not Used |                                         |

| 13     | Not Used |                 | 14  | Not Used |                                         |

| 15     | Not Used |                 | 16  | Not Used |                                         |

| 17     | Not Used |                 | 18  | Not Used |                                         |

| 19     | Not Used |                 | 20  | MPRO/    | Memory Protect                          |

| 21     | GND      | Ground          | 22  | GND      | Ground                                  |

| 23     | Not Used |                 | 24  | Not Used |                                         |

| 25     | Not Used |                 | 26  | Not Used |                                         |

| 27     | PAR1/    | Parity 1        | 28  | Not Used |                                         |

| 29     | PAR2/    | Parity 2        | 30  | Not Used |                                         |

| 31     | Not Used |                 | 32  | Not Used |                                         |

| 33     | Not Used |                 | 34  | Not Used |                                         |

| 35     | Not Used |                 | 36  | Not Used |                                         |

| 37     | Not Used |                 | 38  | Not Used |                                         |

| 39     | Not Used |                 | 40  | OFBRDRQ  | Off Board Request                       |

| 41     | Not Used |                 | 42  | Not Used |                                         |

| 43     | Not Used |                 | 44  | Not Used |                                         |

| 45     | Not Used | 1               | 46  | Not Used |                                         |

| 47     | Not Used | 1               | 48  | Not Used |                                         |

| 49     | Not Used |                 | 50  | Not Used |                                         |

| 51     | Not Used |                 | 52  | Not Used |                                         |

| 53     | Not Used |                 | 54  | Not Used |                                         |

| 55     | AD16/    | Address Bus     | 56  | AD17/    | Address Bus                             |

| 57     | AD14/    | Address Bus     | 58  | AD15/    | Address Bus                             |

| 59     | Not Used | 1               | 60  | Not Used |                                         |

Table 2-5. P2 Connector Pin Assignments

# Table 2-6. Jumper Configurations

'X' If Connected

| Power Jumpers |                                |                                                                                                                                      |  |

|---------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Jumper        | Standard<br>Configuration      | Function                                                                                                                             |  |

| E1, E3        |                                | For battery backup of the memory chips.                                                                                              |  |

| E2, E3        | х                              | If battery backup of the memory chips is not required.                                                                               |  |

| E4, E5        |                                | For battery backup of selected board logic.                                                                                          |  |

| E5, E6        | х                              | If battery backup of selected board logic is not required.                                                                           |  |

|               | Parity Fl                      | ag Register Jumpers                                                                                                                  |  |

|               | AD03, AD06, a<br>AD04, AD05, a | re used in conjunction with AD00-<br>nd AD08-AD0F for I/O selection.<br>and AD07 do not involve jumpers<br>s be H for I/O selection. |  |

| <b>W</b> 1    | X                              | If W1 is jumpered, then AD00 must be L for                                                                                           |  |

| W2            | х                              | I/O selection.<br>If W2 is jumpered, then AD01 must be L for<br>I/O selection.                                                       |  |

| W3            | х                              | If W3 is jumpered, then AD02 must be L for I/O selection.                                                                            |  |

| W4            | х                              | If W4 is jumpered, then AD03 must be L for I/O selection.                                                                            |  |

| W 5           |                                | If W5 is jumpered, then W6 should not be jumpered and AD06 must be H for I/O selec-tion.                                             |  |

| W6            | х                              | If W6 is jumpered, then W5 should not be jumpered and AD06 must be L for I/O selec-tion.                                             |  |

| W7A           | х                              | If W7A is jumpered, then AD08 must be L for I/O selection.                                                                           |  |

| Parity Flag Register Jumpers (Continued) |                           |                                                                |  |

|------------------------------------------|---------------------------|----------------------------------------------------------------|--|

| Jumper                                   | Standard<br>Configuration | Function                                                       |  |

| W7B                                      |                           | If W7B is jumpered, then AD08 has no effect on I/O selection.  |  |

| W8A                                      | х                         | If W8 is jumpered, then AD09 must be L for $I/O$ selection.    |  |

| W8B                                      |                           | If W8B is jumpered, then AD09 has no effect on I/O selection.  |  |

| W9A                                      | х                         | If W9A is jumpered, then AD0A must be L for I/O selection.     |  |

| W9B                                      |                           | If W9B is jumpered, then AD0A has no effect on I/O selection.  |  |

| W10A                                     | х                         | If W10A is jumpered, then AD0B must be L for I/O selection.    |  |

| W10B                                     |                           | If W10B is jumpered, then AD0B has no effect on I/O selection. |  |

| W11A                                     | х                         | If W11A is jumpered, then AD0C must be L for I/O selection.    |  |

| W11B                                     |                           | If W11B is jumpered, then AD0C has no effect on I/O selection. |  |

| W12A                                     | х                         | If W12A is jumpered, then AD0D must be L for I/O selection.    |  |

| W12B                                     |                           | If W12B is jumpered, then AD0D has no effect on I/O selection. |  |

| W13A                                     | х                         | If W13A is jumpered, then AD0E must be L for I/O selection.    |  |

| W13B                                     |                           | If W13B is jumpered, then AD0E has no effect on I/O selection. |  |

| W14A                                     | х                         | If W14A is jumpered, then AD0F must be L for I/O selection.    |  |

| W14B                                     |                           | If W14B is jumpered, then AD0F has no effect on I/O selection. |  |

# Table 2-6. Jumper Configurations (Continued)

|                                                              | Memory Address Select Jumpers                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                      |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Jump <del>er</del>                                           | Standard<br>Configuration                                                                                                                                                                                                                                                              | Function                                                                                                                                                                                                                             |  |  |

|                                                              | <b>NOTE</b><br>If bits 15-22 of the lower boundry (corresponding<br>to address bits AD0E-15) are b <sub>15</sub> b <sub>14</sub> b <sub>13</sub> b <sub>12</sub><br>b <sub>11</sub> b <sub>10</sub> b <sub>0F</sub> b <sub>0E</sub> , then jumpers W25-32 should be<br>set as follows: |                                                                                                                                                                                                                                      |  |  |

| W 25<br>W 26<br>W 27<br>W 28<br>W 29<br>W 30<br>W 31<br>W 32 | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                                                                                                                                                                                                                                                   | If bOE is L, connect W25.<br>If bOF is L, connect W26.<br>If b10 is L, connect W27.<br>If b11 is L, connect W28.<br>If b12 is L, connect W29.<br>If b13 is L, connect W30.<br>If b14 is L, connect W31.<br>If b15 is L, connect W32. |  |  |

|                                                              | <b>NOTE</b><br>If bits 15-22 of the upper boundry (corresponding<br>to address bits AD0E-15) are b15 b14 b13 b12<br>b11 b10 b0F b0E, the jumpers W17-24 should be<br>set as follows:                                                                                                   |                                                                                                                                                                                                                                      |  |  |

| W17<br>W18<br>W19<br>W20<br>W21<br>W22<br>W23<br>W24         | X<br>X<br>X<br>X<br>X<br>X<br>X                                                                                                                                                                                                                                                        | If b0E is L, connect W17.<br>If b0F is L, connect W18.<br>If b10 is L, connect W19.<br>If b11 is L, connect W20.<br>If b12 is L, connect W21.<br>If B13 is L, connect W22.<br>If b14 is L, connect W23.<br>If b15 is L, connect W24. |  |  |

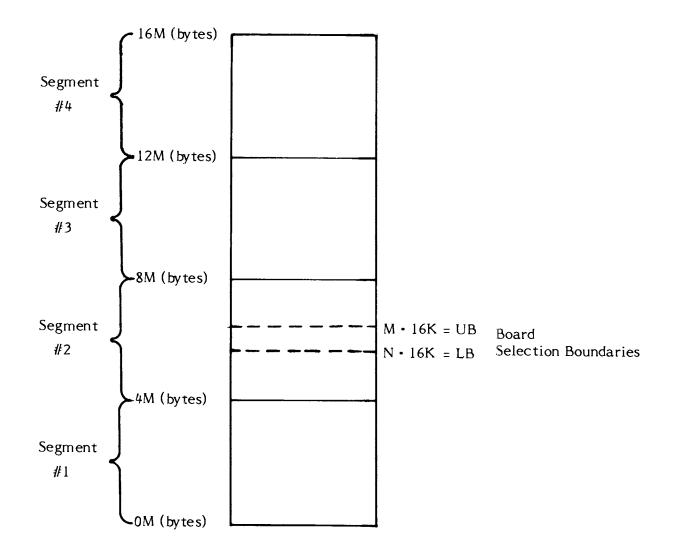

| W33 & W34                                                    |                                                                                                                                                                                                                                                                                        | Together, these determine the memory segment for the board.                                                                                                                                                                          |  |  |

# Table 2-6. Jumper Configurations (Continued)

|        | Memory Address Select Jumpers (Continued) |                                                                                                                                                                                                                                                                                                            |  |  |

|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Jumper | Stand <b>ar</b> d<br>Configuration        | Function                                                                                                                                                                                                                                                                                                   |  |  |

|        |                                           | The following table shows the relationship<br>between these jumpers and the memory<br>segment. Segment 1 consists of memory loca-<br>tions 0 to 4M-1; segment 2 consists of loca-<br>tions 4M to 8M-1; segment 3 consists of<br>locations 8M to 12-1; and segment 4 consists<br>of locations 12M to 16M-1. |  |  |

|        |                                           | Segment W34 W33                                                                                                                                                                                                                                                                                            |  |  |

|        |                                           | 1 A A<br>2 A B<br>3 B A<br>4 B B                                                                                                                                                                                                                                                                           |  |  |

|        | Inte                                      | rrupt Jumpers                                                                                                                                                                                                                                                                                              |  |  |

| ₩35    |                                           | If a parity error is to cause INT7/ to go active, connect W35.                                                                                                                                                                                                                                             |  |  |

| W 36   |                                           | If a parity error is to cause INT6/ to go active, connect W 36.                                                                                                                                                                                                                                            |  |  |

| W 37   |                                           | If a parity error is to cause INT5/ to go active, connect W37.                                                                                                                                                                                                                                             |  |  |

| W 38   |                                           | If a parity error is to cause INT4/ to go active, connect W38.                                                                                                                                                                                                                                             |  |  |

| W 39   |                                           | If a parity error is to cause INT3/ to go active, connect W39.                                                                                                                                                                                                                                             |  |  |

| W40    |                                           | If a parity error is to cause INT2/ to go active, connect W40.                                                                                                                                                                                                                                             |  |  |

| W41    |                                           | If a parity error is to cause INT1/ to go active, connect W41.                                                                                                                                                                                                                                             |  |  |

| W42    |                                           | If a parity error is to cause INTO/ to go active, connect W42.                                                                                                                                                                                                                                             |  |  |

# Table 2-6. Jumper Configurations (Continued)

|        | Memory Address Select Jumpers (Continued) |                                                                                                                                                                                                          |  |  |

|--------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Jumper | Standa <b>rd</b><br>Configuration         | Function                                                                                                                                                                                                 |  |  |

|        |                                           | Refresh Jumpers                                                                                                                                                                                          |  |  |

| W44    |                                           | For refresh requests to be generated off-<br>board and placed on OFBRDRQ, W44 may be<br>connected and ONBRDREF set false. Or, as<br>an alternative to this approach, W45 may be<br>jumpered (see below). |  |  |

| W45    |                                           | For refresh requests to be generated off-<br>board and placed on OFBRDRQ, W45 may be<br>jumpered (the state of ONBRDREF does not<br>matter in this case).                                                |  |  |

| W46    |                                           | If refresh requests are to be generated off-<br>board, they should be brought in on this line<br>(and either W44 or W45 should be connected<br>as described above).                                      |  |  |

## Table 2-6. Jumper Configurations (Continued)

### 2.9 ADDRESS RANGE SELECTION

The standard configuration of jumpers for the iSBC 012B board sets the address range for board selection at 16K to 16K + 512K-1. For other ranges, jumpers W17-32 must be set appropriately. (See Section 2.8, Jumper Configurations.) For example, if board selection for the iSBC 012B board is desired for the range 32K to 32K + 512K-1, then W17-32 must be configured as follows:

| Jumper | 'X' (if connected) |

|--------|--------------------|

| W17    |                    |

| W18    | Х                  |

| W19    | Х                  |

| W 20   | Х                  |

| W21    | Х                  |

| W22    |                    |

| W23    | Х                  |

| W 24   | Х                  |

| W 25   | Х                  |

| W 26   |                    |

| W 27   | Х                  |

| W 28   | Х                  |

| W 29   | х                  |

| W 30   | Х                  |

| W 31   | Х                  |

| W 32   | Х                  |

### 2.10 iSBC 012B INSTALLATION PROCEDURE

#### NOTE

The iSBC 012B memory board can be installed in any Multibus-compatible form factor with a Multibus-compatible configuration of pinouts.

- 1. Turn off the main AC power.

- Connect jumpers for the desired jumper configuration (see Section 2.8, Jumper Configurations) and set the jumpers for the desired range of board selection (see Section 2.9, Address Range Selection).

- 3. Install the board in any desired slot. (If the P2 connector is used, make sure that there is a P2 connector installed in the backplane and that the P2 edge connector on the iSBC 012B memory board mates with it properly.)

- 4. Power up the system.

.

### **SECTION 3**

### OPERATION

### 3.1 INTRODUCTION

This section describes the operation of the iSBC 012B memory board. It includes a discussion of:

- 1. Operating Principles

- 2. Input/Output Signals

- 3. Standard Operating Modes

- 4. Special Operating Features

#### **3.2 OPERATING PRINCIPLES**

The iSBC 012B is a semiconductor memory requiring no manual operation other than the setting of jumpers. All operating sequences are controlled by externally supplied control signals and internally generated response signals that conform to Multibus specifications. These signals are described in Section 3.3. Memory operations are described in Section 3.4.

#### 3.3 INPUT/OUTPUT SIGNAL DESCRIPTION

Table 3-1 below describes the input/output signals on the P1 connector; Table 3-2 describes the input/output signals on the P2 connector.

# Table 3-1. Input/Output Signals on the P1 Connector

| Signal Mnemonic                                                                             | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

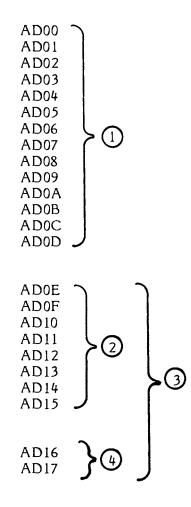

| ADR0/-ADRF/ and<br>ADR10/-ADR17/<br>( <b>Note:</b> ADR14/-ADR17<br>are on the P2 connector) | Address: In the case of the iSBC 012B memory board,<br>these address bits are used to specify the address of a<br>memory location (with a memory read or write<br>command) or the address of the Parity Flag Register I/O<br>port (with an I/O read or write command).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                             | When these addresses specify a memory location, ADR0/<br>(AD00), in conjunction with BHEN/, determines the type<br>of transfer (see Table 4-3); ADR1/-ADR10/ (AD01-<br>AD10) are used for row and column addresses to the<br>memory chips (see Section 4.4.1.A, Address Routing<br>Circuitry, for a detailed discussion of routing for par-<br>ticular chip types); for the iSBC 056B, ADR11/ (AD11) is<br>used for row selection among the two rows of memory<br>chips, while for the iSBC 012B, ADR11/ and<br>ADR12/ (AD11 and AD12) are used for row selection<br>among the four rows of memory chips; ADRE/-ADR15/<br>(AD0E-AD15) are compared for board range selection;<br>and ADR16/ and ADR17/ (AD16 and AD17) determine<br>the 4-megabyte segment selection. |

|                                                                                             | In the case of the Parity Flag Register I/O port, only address bits ADR0/-ADRF/ (AD00-AD0F) are used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BHEN/                                                                                       | <b>Byte High Enable:</b> In conjunction with ADR0/ (AD00), determines the type of transfer (see Table 4-3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DAT0/-DATF/                                                                                 | Data: These 16 bidirectional lines transmit and receive data to/from the addressed memory location or I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INH1/                                                                                       | Inhibit RAM: When active (low), this signal inhibits memory cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INIT/                                                                                       | Initialize: Resets the system to a known internal state – sets CI/ false, clears the parity error I/O port, and clears interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INT0/-INT7/                                                                                 | Interrupt Request: These eight interrupt lines transmit interrupt requests to the appropriate interrupt handler. INTO/ has the highest priority.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 3-1. | Input/Output Signals on the P1 Connector | (Continued) |

|------------|------------------------------------------|-------------|

|------------|------------------------------------------|-------------|

| Signal Mnemonic | Functional Description                                                                                                                                                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IORC/           | I/O Read Command: Indicates that the address of an I/O port is on the Multibus address lines and that the output of that port is to be read (placed) onto the Multibus data                                                      |

| IOWC/           | lines.<br>I/O Write Command: Indicates that the address of an<br>I/O port is on the Multibus address lines and that the<br>contents of the Multibus data lines are to be accepted by<br>the addressed port.                      |

| MRDC/           | <b>Memory Read Command:</b> Indicates that the address of a memory location is on the Multibus address lines and that the contents of that location are to be read (placed) on the Multibus data lines.                          |

| MWTC/           | <b>Memory Write Command:</b> Indicates that the address of a memory location is on the Multibus address lines and that the contents of the Multibus data lines are to be written into that location.                             |

| XACK/           | <b>Transfer Acknowledge:</b> Indicates that the addressed<br>memory location or I/O port has completed the specified<br>read or write operation; that is, data has been placed<br>onto or accepted from the Multibus data lines. |

| Table 3-2. | Input/Output Signals on the P2 Connector |

|------------|------------------------------------------|

|------------|------------------------------------------|

| Signal Mnemonic | Functional Description                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADR14/-ADR17    | Address: See Table 3-1, ADR0/-ADRF/ and ADR10/-ADR13.                                                                                                                                                                                                                                                                                                            |  |  |  |

| MPR0/           | <b>Memory Protect:</b> This externally generated signal is used to inhibit memory cycles during battery backup operation.                                                                                                                                                                                                                                        |  |  |  |

| OFBRDRQ         | Off-Board Request:                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                 | Note: The following applies only if W46 is jumpered. If<br>W46 is not jumpered, then refresh requests are<br>always generated on board. In the latter case,<br>W45 must be installed or W44 installed and<br>ONBRDREF held low.                                                                                                                                  |  |  |  |

|                 | When this signal goes true, it clocks (initiates) a refresh request.                                                                                                                                                                                                                                                                                             |  |  |  |

| ONBRDREF        | On-Board Refresh:                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                 | <b>Note:</b> The following applies only if W44 is jumpered.                                                                                                                                                                                                                                                                                                      |  |  |  |

|                 | When true, indicates that the pulse for the refresh cycle<br>will be generated on board by the parity pulse generator<br>(2N). When false, indicates that the pulse for the refresh<br>cycle must be generated off the board by some other<br>generator. In the latter case, W46 will also be jumpered<br>and the off-board pulse will be brought in on OFBRDRQ. |  |  |  |

# 3.4 STANDARD OPERATING MODES

Standard operating modes are write, read, and refresh. In write and read modes, various transfer types are possible. Transfer types and write, read, and refresh modes are discussed below.

### 3.4.1 Transfer Types

Address bit ADR0/ (AD00) and BHEN/ determine the transfer type. Table 3-3 below describes the type of transfer for the various combinations of AD00 and BHEN/.

| BHEN/ | AD00 | Description of Transfer<br>(Read or Write)                                           |  |  |

|-------|------|--------------------------------------------------------------------------------------|--|--|

| F     | F    | DAT0/-DAT7/ to/from the low memory bank                                              |  |  |

| F     | Т    | DAT0/-DAT7/ to/from the high memory bank                                             |  |  |

| Т     | F    | DAT0/-DAT7/ to/from the low memory bank;<br>DAT8/-DATF/ to/from the high memory bank |  |  |

| Т     | Т    | DAT8/DATF/ to/from the high memory bank                                              |  |  |

| Table 3-3. | Description | of Transfer | Types |

|------------|-------------|-------------|-------|

|------------|-------------|-------------|-------|

#### 3.4.2 Write Mode

A write cycle is initiated when MWTC/ is asserted true, assuming that BMPRO is false (memory is not protected) and BDSEL/ is true (the board is selected).

The following signals then go true: CI (initiating the internal timing for the cycle), CI/ (holding off refresh cycles), XACK/ (an acknowledge), WEL/ and/or WEH/ (write enable signals to the memory chips, depending on the transfer type – WEL/ if the transfer is to the low bank and WEH if the transfer is to the high bank, or both true if the transfer involves both banks), RASn (the row address strobe for the row n determined from AD11 and HALF/FULL), and  $R/\overline{C}$  (causing the memory chip row address on the address lines to be placed on MA0-MA7 and then to be strobed into the selected row of memory chips).

At approximately 40ns,  $R/\overline{C}$  goes false (L), causing the column addresses on the address lines to be placed on MA0-MA7. At approximately 80ns, CAS0/-CAS1/ go true and the column addresses on MA0-MA7 are strobed into the memory chips. Data on the data lines is then written into the selected row and bank(s) of memory chips.

Parity bits (LPAR/ and HPAR/) are generated from the incoming data and are strobed into memory with the data as described above. Optionally (for test purposes), off-board parity bits (PAR1/ and PAR2/ on the P2 connector) may be strobed into memory in the same way (if so, W43, W47 and W48 must be jumpered and ONBRD must be set false).

See Figure 3-1 for write cycle timing signals.

530 **- 0**02A

| Parameter           | Minimum<br>(NSEC) | Maximum<br>(NSEC) | Description                             | Remarks                 |

|---------------------|-------------------|-------------------|-----------------------------------------|-------------------------|

| t <sub>AH</sub>     | 50                |                   | Address hold time                       |                         |

| <sup>t</sup> AS     | 50                |                   | Address setup to command                | From data to<br>command |

| <sup>t</sup> CMD    | 375               |                   | Command width                           |                         |

| tCS                 | 175               |                   | Command separation                      |                         |

| <sup>t</sup> DHW    | 0                 |                   | Write data hold time                    |                         |

| t <sub>DS</sub>     | 50                |                   | Write data setup to command             | Normal write            |

| t <sub>RD</sub>     | 550               |                   | Refresh delay time                      |                         |

| * <sup>t</sup> XACK |                   | 350               | Command to transfer<br>acknowledge time |                         |

| <sup>t</sup> XAH    |                   | 65                | Acknowledge turnoff<br>delay            |                         |

\*When an asynchronous refresh cycle occurs,  ${}^{t}RD$  is added to this parameter.

### 3.4.3 Read Mode

A read cycle is initiated when MRDC/ is asserted true, assuming BMPRO is false (memory is not protected) and BDSEL/ is true (the board is selected).

The following signals then go true: CI (initiating the internal timing for the cycle), CI/ (holding off refresh cycles), XACK/ (an acknowledge), RASn (the row address strobe for the row n determined from AD11 and HALF/FULL), and  $R/\overline{C}$  (causing the memory chip row address on the address lines to be placed on MA0-MA7 and then to be strobed into the selected row of memory chips).

At approximately 40ns,  $R/\overline{C}$  goes false (L), causing the column addresses on the address lines to be placed on MA0-MA7. At approximately 80ns, CAS0/-CAS1/ go true and the column addresses on MA0-MA7 are strobed into the memory chips.

At approximately 280ns, LATCH/ goes true and the data from the selected row of memory chips is latched at 2R and 2U (octal D-type latches at the outputs of the memory chips). Depending on the type of transfer, the data then becomes available on the Multibus data lines DAT0/-DAT7/ or DAT8/-DATF/ or both (RDSEL/ and RDATOE/ enable/disable the output from the latches and LOE/ and HOE/ enable/disable the data onto the Multibus according to the type of transfer).

The parity bits (LPAR0/ and HPAR0/) are enabled onto the output lines of the memory chips in the same way, but are not latched with the data but rather routed to the parity generators/checkers along with the data to determine if there are parity errors. The parity error flags, LERR and HERR, are then routed to the parity error I/O port, along with AD11 and HALF/FULL (which determine the row of chips), and are latched there at approximately 320ns. If any of the interrupt lines have been jumpered (W35-W42) and a parity error occurs, an interrupt will be issued and the processor may read the parity-related data by issuing an I/O read command, which enables the data onto the Multibus data lines DAT0/-3/. (Note: The interrupt should then be cleared by issuing an I/O write command to the parity error I/O port.)

See Figure 3-2 for read cycle timing signals.

530 - 003

| Parameter           | Minimum<br>(NSEC) | Maximum<br>(NSEC) | Description                          | Remarks |

|---------------------|-------------------|-------------------|--------------------------------------|---------|

| <sup>t</sup> ACC    |                   | 350               | Access time to read<br>data          |         |

| <sup>t</sup> DHR    | 0                 |                   | Read data hold time                  |         |

| t <sub>ID</sub>     | 0                 | 50                | Inhibit delay                        |         |

| tIH                 | 150               |                   | Inhibit hold time<br>command         |         |

| tIPW                | 100               |                   | Inhibit pulse width                  |         |

| t <sub>IS</sub>     | 0                 |                   | Inhibit setup to command             |         |

| t <sub>RD</sub>     |                   | 550               | Refresh delay time                   |         |

| * <sup>t</sup> XACK |                   | 350               | Command to transfer acknowledge time |         |

| <sup>t</sup> XAH    |                   | 65                | Acknowledge turnoff<br>delay         |         |

\*When an asynchronous refresh cycle occurs, <sup>t</sup>RD is added to this parameter.

### 3.4.4 Refresh Mode

The iSBC 012B memory board uses dynamic RAM memory chips which have a retention period of 2 milliseconds. Therefore each location must be refreshed every 2 milliseconds. This is accomplished by refreshing an entire row of locations every 15.6 microseconds.

Refreshes are normally initiated by the on-board pulse generator (2N), which generates a pulse every 15.6 milliseconds. This pulse is the signal ONBRDRQ.

When ONBRDRQ goes true, COUNT and REFREQ/ go true. COUNT causes the counter (5AA) for the row addresses generated for refresh cycles to increment; REFREQ/ inhibits read or write cycles.

Approximately 20ns after the pulse, REFADR/ goes true. This enables the row address generated for the refresh cycle onto MAO-MA7. At the same time that REFADR/ goes true, AEN/ goes false. This keeps the memory row and column addresses off MAO-MA7.

Approximately 50ns after the pulse, REF/ goes true, initiating the timing for the cycle and causing RAS0/-RAS3/ to go true. The row addresses are then strobed into the four rows of memory chips. This initiates a "RAS-only" refresh cycle for every memory chip on the board.

Approximately 220ns after REF/ goes true (approximately 270ns after the refresh pulse), CLRREF/ goes true, causing REFREQ/ to go false. Approximately 50ns later (approximately 320ns after the pulse), REF/ goes false.

Normally the refresh pulse is generated on board. There is optional facility (for test purposes) for generating pulses off board. For generating off-board refresh requests, either (1) W44 should be connected and ONBRDREF (P2-10) should be set false, or (2) W45 should be connected. In either case (1 or 2), the off-board request should be brought in on OFBRDRQ (P2-40).

### 3.5 SPECIAL OPERATING FEATURES

### 3.5.1 Parity Generation and Checking

On-board parity is generated for each byte written to memory. When a byte is read from memory, the parity bit, stored with the data in the associated bank, is checked against the data, and an error flag is used to reflect any discrepancy. An optional feature (for test purposes) allows parity bits to be brought in from off the board.

For more detail, read Section 3.4.2 (Write Mode) and Section 3.4.3 (Read Mode).

### 3.5.2 Powerfail Memory Protection

The memory protection circuitry is designed to prevent memory cycles from occurring during battery backup in periods of uncertain power. This is an optional feature.

Memory protection is initiated off board when MPRO/ is asserted true (MPRO/ is on the optional P2 connector). When MPRO/ goes true, BMPRO goes true when CLRREF/ goes true (this may be during a memory cycle or a refresh cycle). BMPRO then inhibits memory cycles until MPRO/ goes false and, at the end of a refresh cycle, CLRREF/ goes false. iSBC 012B Technical Manual 112748

#### **SECTION 4**

# THEORY OF OPERATION

## 4.1 INTRODUCTION

This section contains the theory of operation for the iSBC 012B memory board. It includes:

- 1. A description of standard logic symbols

- 2. Pin assignments and truth tables for the IC devices used on the board

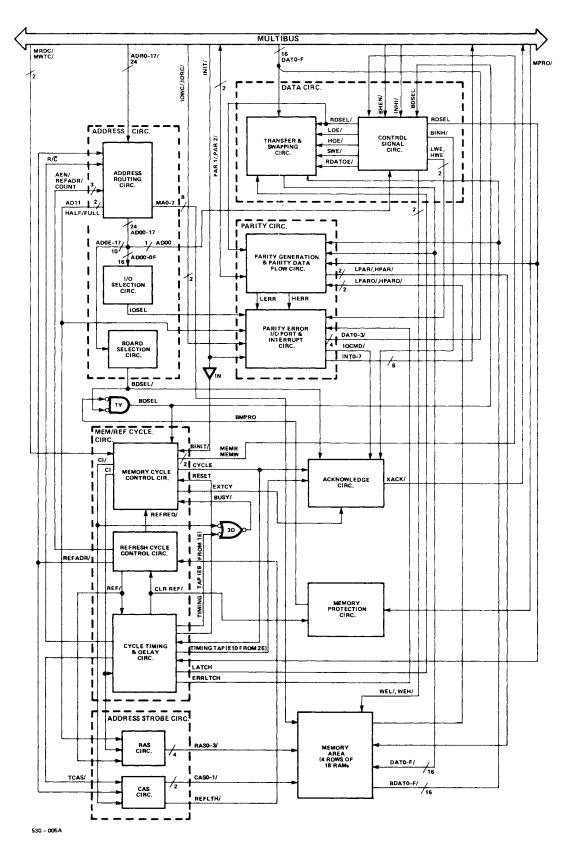

- 3. An overall description of the iSBC 012B circuitry, along with a diagram of the major blocks of circuitry on the board

- 4. A detailed description of the major blocks of circuitry.

#### 4.2 STANDARD LOGIC SYMBOLS

#### 4.2.1 Electrical Criteria

A circle (bubble) at the input or output of a gate indicates a low-going signal, or one which is active when low. The absence of a circle indicates a high-going signal, or one which is active when high.

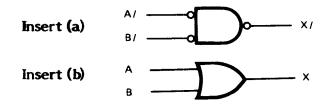

The logic symbols are generally drawn in such a way that the inputs required to produce a given output are explicit. Looking at Insert (a) below, the desired output at X/ is a low-going signal. A/ and B/ must both be low to produce this output. An alternative way of showing this relationship is given in Insert (b). The truth table for each symbol is the same, as shown in Insert (c).

| Insert (c) _ | A | В | × |

|--------------|---|---|---|

|              | L | L | L |

|              | L | н | н |

|              | н | L | н |

|              | н | н | н |

|              |   |   |   |

In the first case (Insert **a**), a low-going output is expected, and two low inputs are required to produce it. In the second case (Insert **b**), a high-going output is expected, and either one of two high-going inputs will produce it.

When edge-sensitive devices are shown, a circle on the clock, or other triggering input, indicates a negative-going edge that can be the leading edge of a negative pulse or the trailing edge of a positive pulse. If no circle is shown on the clock input, then the device is a positive-edge-triggered device, triggered by the leading edge of a positive pulse or the trailing edge of a negative pulse.

#### 4.2.2 Logical Criteria

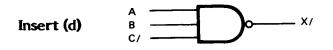

A slash following a signal name (WRITE/) signifies a negative logic or a low true signal. Looking at Insert (d), three high inputs are required to enable this gate. Input C/, which is an active low signal, inhibits the output when it is active and enables the output when it is inactive.

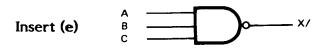

No slash following a signal name (BSEL) indicates a signal which is active when high. Insert (e) shows how the inverse of C/, C (active high) is used to enable an output.

When the signal matches the input (i.e., slash to circle, no slash to no circle), an enable function may be assumed. When the signal does not match the input (i.e., no slash to circle, slash to no circle), an inhibit function may be assumed. The four possible combinations are summarized in Table 4-1.

| Electrical Properties |                                                    |                                                    |  |  |  |  |  |  |  |  |

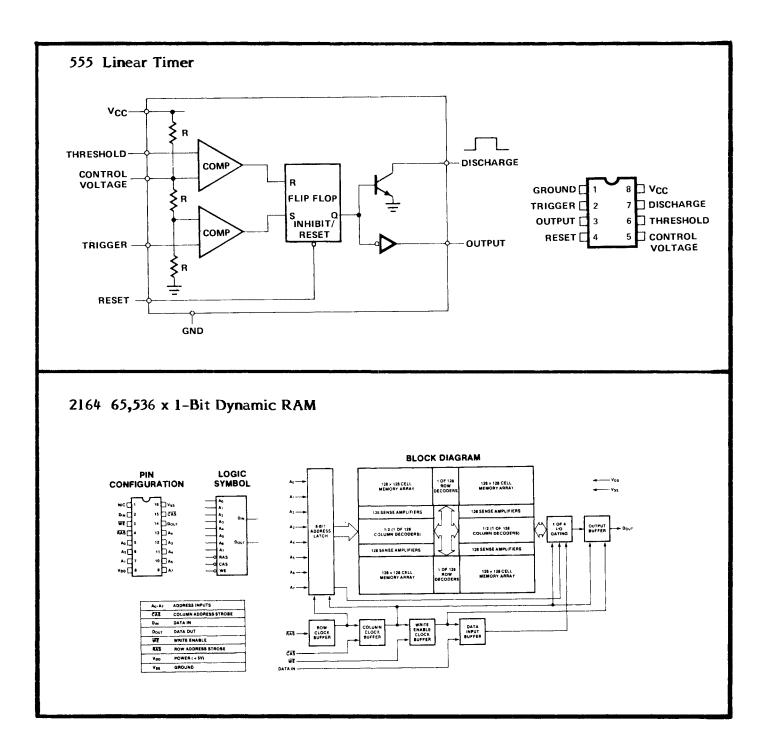

|-----------------------|----------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|--|