# JAMES B. JOHNSON STEVE KASSEL

# The Multibus Design Guidebook

Structures, Architectures, and Applications

# McGraw-Hill Book Company

New York St. Louis San Francisco Auckland Bogotá Hamburg Johannesburg London Madrid Mexico Montreal New Delhi Panama Paris. São Paulo Singapore Sydney Tokyo Toronto Library of Congress Cataloging in Publication Data

Johnson, James B. The multibus design guidebook.

Includes bibliographical references and index.

I. Microcomputers—Buses. 2. Computer architecture.

I. Kassel, Steve. II. Title.

TK7895.B87J63

1984

621.3819'535

83-16258

ISBN 0-07-032599-5

Copyright © 1984 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

234567890 DOC/DOC 8987654

# ISBN 0-07-032599-5

The editors for this book were Roy Mogilanski and Janet B. Davis, the designer was Riverside Graphics, and the production supervisor was Thomas G. Kowalczyk. It was set in Caledonia by University Graphics, Inc.

Printed and bound by R. R. Donnelley & Sons Company.

Multibus is a registered trademark of Intel Corporation.

Photographs, tables, and figures are used courtesy of Intel Corporation, Santa Clara, California. This book is dedicated to our parents, who furnished us guidance and gave us the educational opportunities to pursue our careers, and to our wives, Nancy and Nancy, who provided support and understanding during the development of this book.

# Contents

|        | PREFACE                                                        |                                                                 |    |

|--------|----------------------------------------------------------------|-----------------------------------------------------------------|----|

|        | ACKNOWLEDGMENTS                                                |                                                                 |    |

|        |                                                                |                                                                 |    |

| PART 1 | THE MULTIBUS FAMILY OF BUS STRUCTURES                          |                                                                 |    |

|        | 1                                                              | INTRODUCTION                                                    | 3  |

|        | 1.1                                                            | Objectives and Goals of Microprocessor-Based System<br>Buses, 3 |    |

|        |                                                                | 1.1.1 Do You Need a System Bus? 4                               |    |

|        | 1.2                                                            | Picking Your Multibus Family Structures, 4                      |    |

|        |                                                                | 1.2.1 Support of a Wide Range of System Architectures, 6        |    |

|        |                                                                | 1.2.2 A Conceptually Simple Structure, 14                       |    |

|        |                                                                | 1.2.3 A Structure That Can Incorporate New VLSI Quickly, 18     |    |

|        |                                                                | 1.2.4 A Reliable, Cost-Effective Structure, 21                  |    |

|        |                                                                | 1.2.5 A Well-Defined, Documented, and Controlled Standard, 23   |    |

|        | 1.3 Brief History of the IEEE-796/Multibus and its Extensions, |                                                                 |    |

|        |                                                                | 24                                                              |    |

|        | 2                                                              | THE MULTIBUS SYSTEM BUS                                         | 27 |

|        | 2.1                                                            | Notation, 27                                                    |    |

|        | 2.2                                                            | Logical Description of the Multibus System Bus, 28              |    |

|        |                                                                | 2.2.1 Bus Devices, 29                                           |    |

|        | 2.3                                                            | Bus Signal Definitions and Operation Overview, 33               |    |

|        |                                                                | 2.3.1 Address, Inhibit, and Data Lines, 33                      |    |

|        |                                                                | 2.3.2 Control Lines, 38                                         |    |

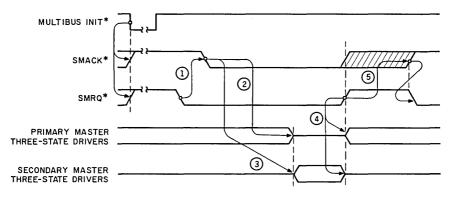

|        |                                                                | 2.3.3 A Data Read Operation, 43                                 |    |

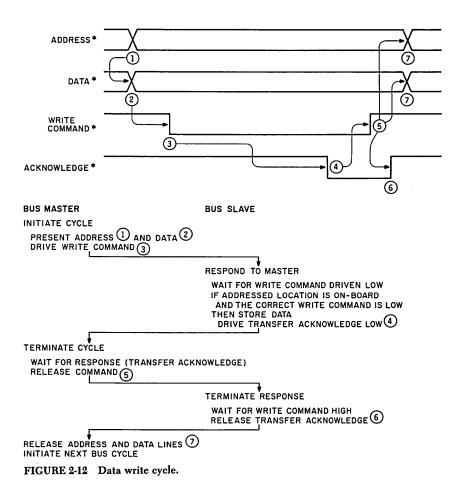

|        |                                                                | 2.3.4 A Data Write Operation, 44                                |    |

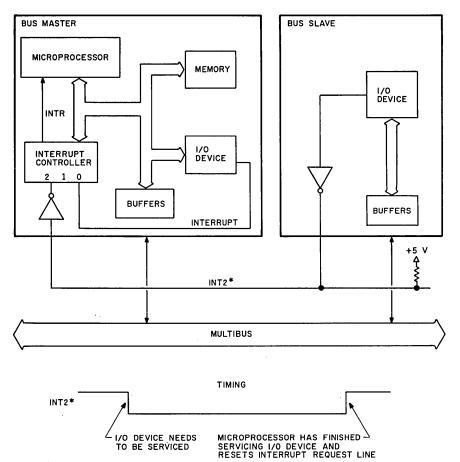

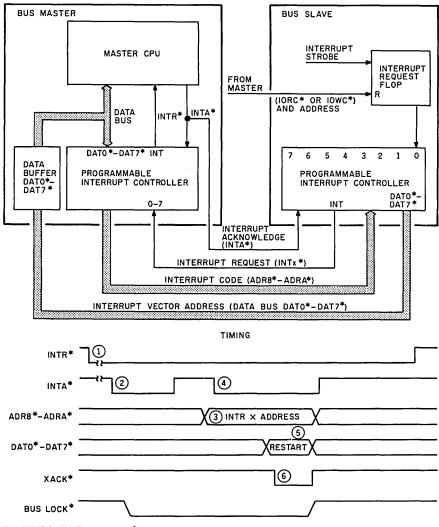

|        |                                                                | 2.3.5 Interrupt Lines, 46                                       |    |

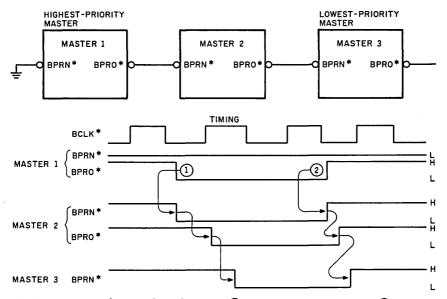

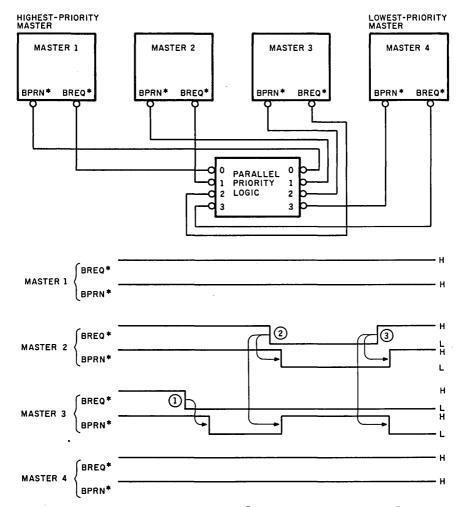

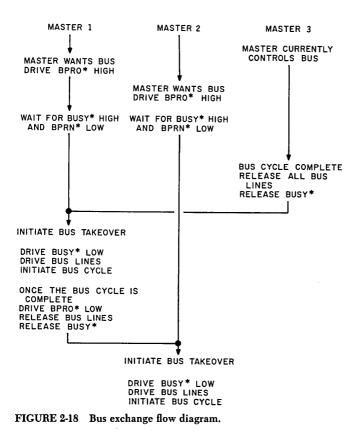

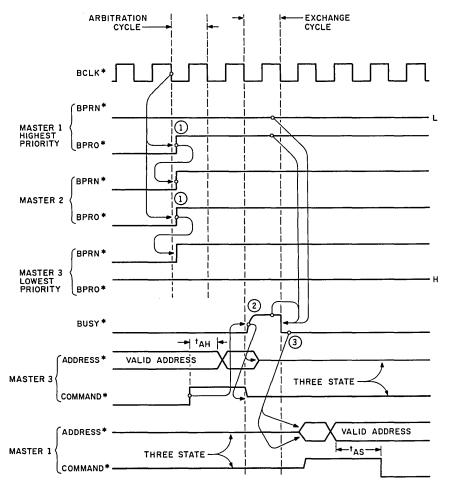

|        |                                                                | 2.3.6 Bus Arbitration and Exchange, 50                          | ,  |

|        |                                                                | 2.3.7 Bus Exchange, 55                                          |    |

vii

# 2.4 Detailed Electrical Description, 56

- 2.4.1 Logical State and Electrical Level Relations, 57

- 2.4.2 Signal Line Characteristics, 57

- 2.4.3 Bus Power Specification, 58

- 2.4.4 Temperature and Humidity Limits, 59

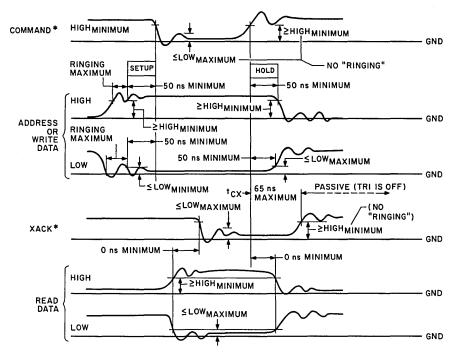

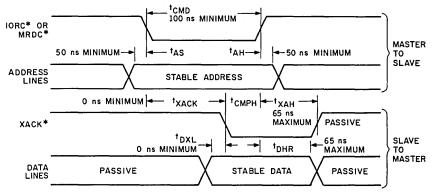

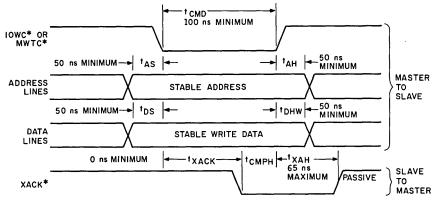

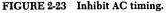

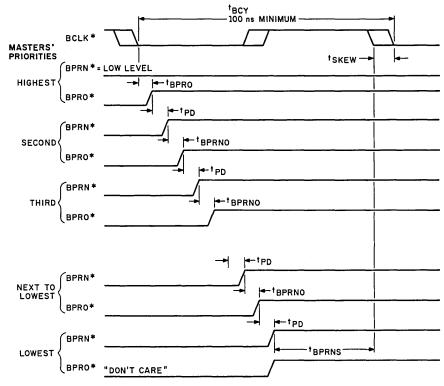

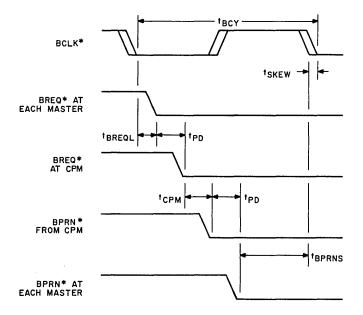

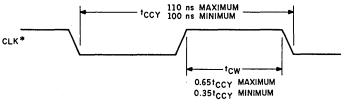

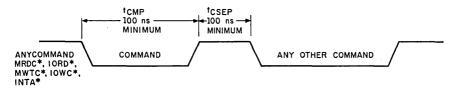

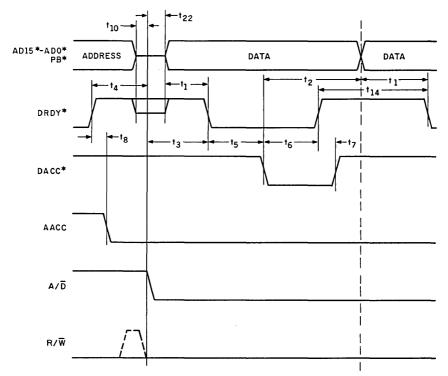

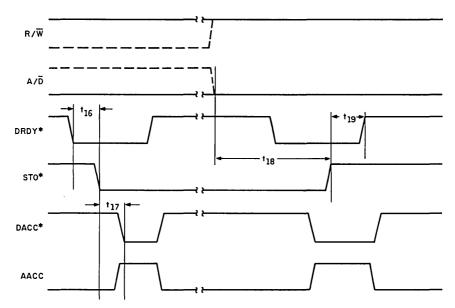

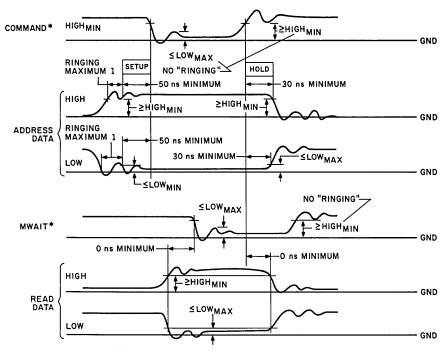

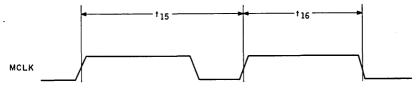

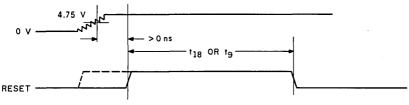

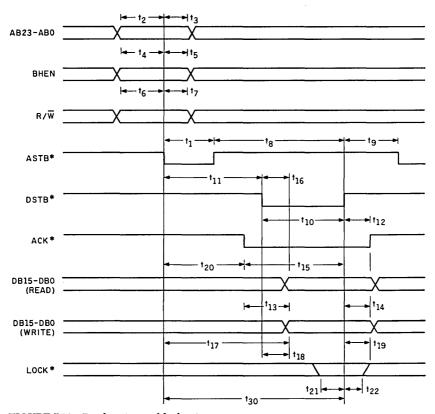

- 2.4.5 Bus Timing, 59

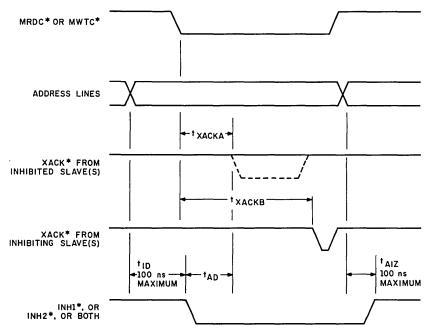

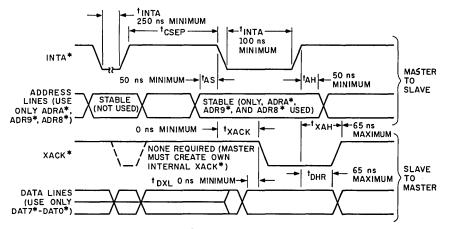

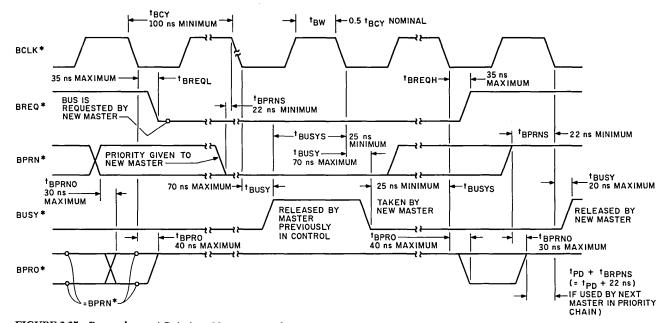

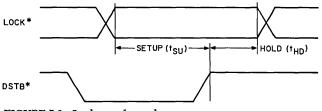

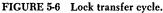

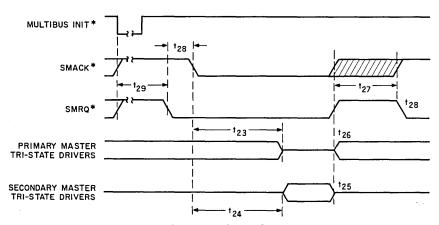

- 2.4.6 Bus Control Exchange Timing, 66

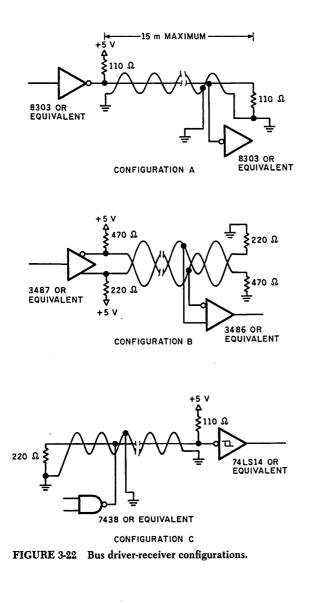

- 2.4.7 Receivers, Drivers and Terminations, 71

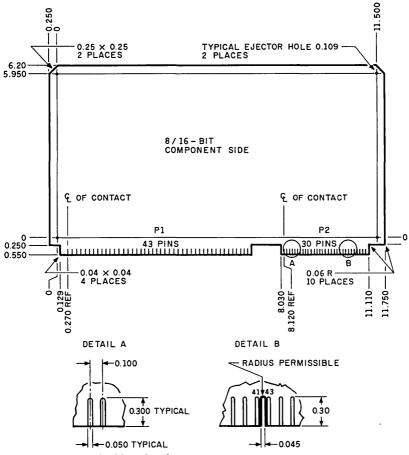

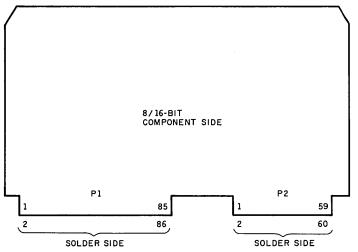

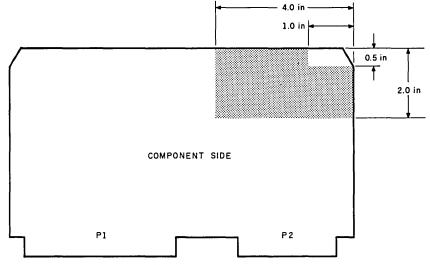

# 2.5 Mechanical Considerations, 72

- 2.5.1 Board-to-Board Relations, 72

- 2.5.2 Pin Assignments, 73

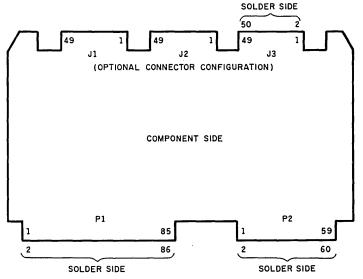

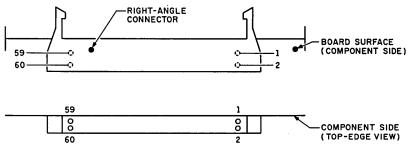

- 2.5.3 Connector-Naming and Pin-Numbering Standards, 73

- 2.5.4 Standard Outline of the PCB, 75

# 2.6 Levels of Compliance, 75

- 2.6.1 Variable Elements of Capability, 76

- 2.6.2 Masters and Slaves, 77

- 2.6.3 Compliance-Level Notation, 78

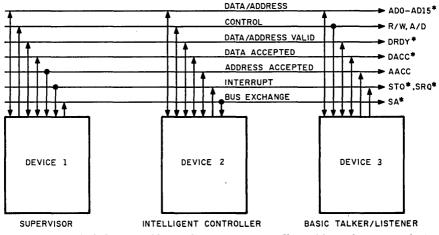

- 3 MULTICHANNEL BUS

- 3.1 Why the Multichannel Bus is Required, 80

# 3.2 Logical Description of the Multichannel Bus, 82

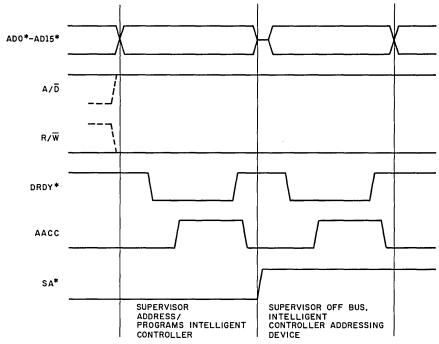

- 3.2.1 Bus States, 84

- 3.2.2 Bus Devices, 85

- 3.3 Bus Signal Definitions, 86

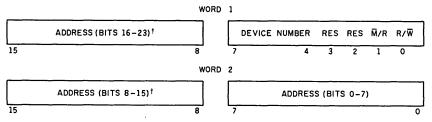

- 3.3.1 Address-Data, 86

- 3.3.2 Control, 87

- 3.3.3 Bus Interrupt Lines, 90

- 3.3.4 Parity, 92

- 3.3.5 Reset\*, 92

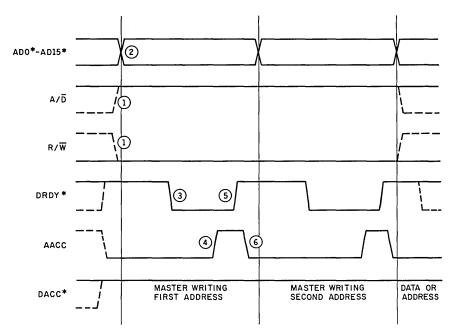

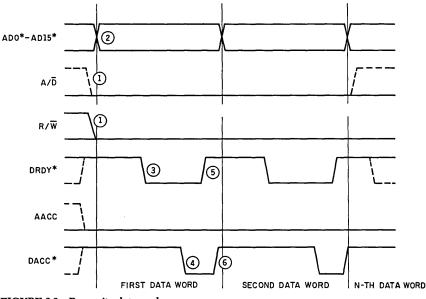

## **3.4 Bus Transfer Operations**, 93

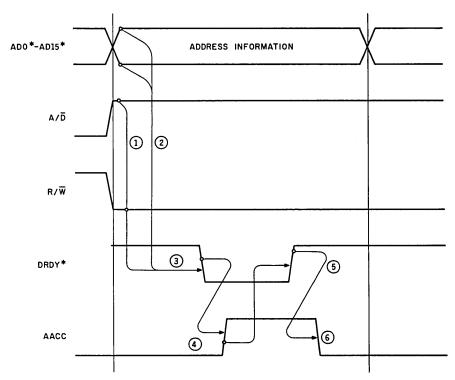

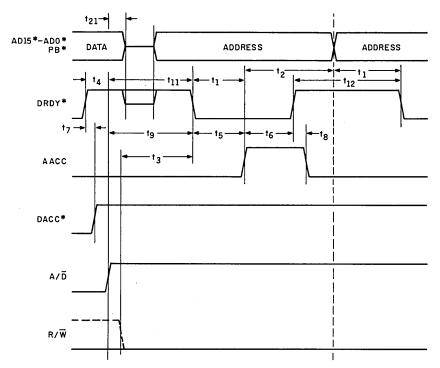

- 3.4.1 Address Cycle, 93

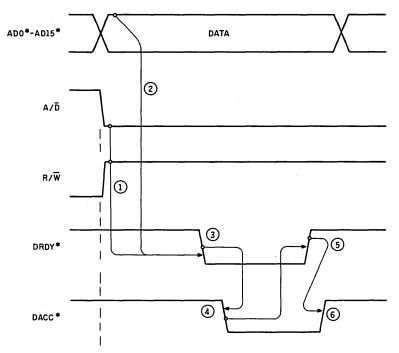

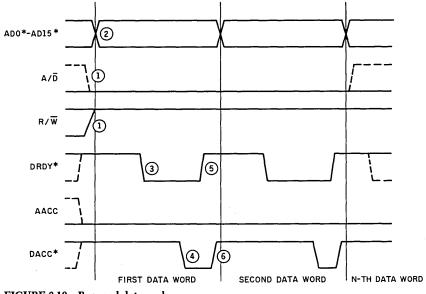

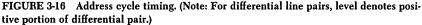

- 3.4.2 Data Cycles, 95

- 3.4.3 Transfer Cycle, 97

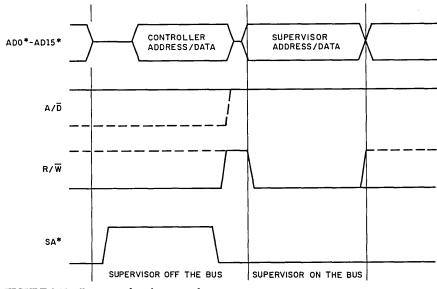

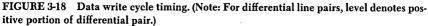

- 3.4.4 Control Arbitration and Exchange, 98

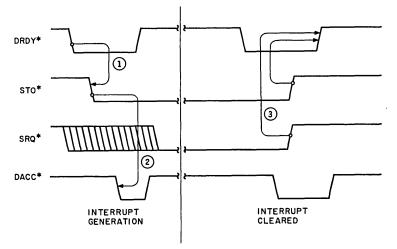

- 3.4.5 Interrupt Handling, 99

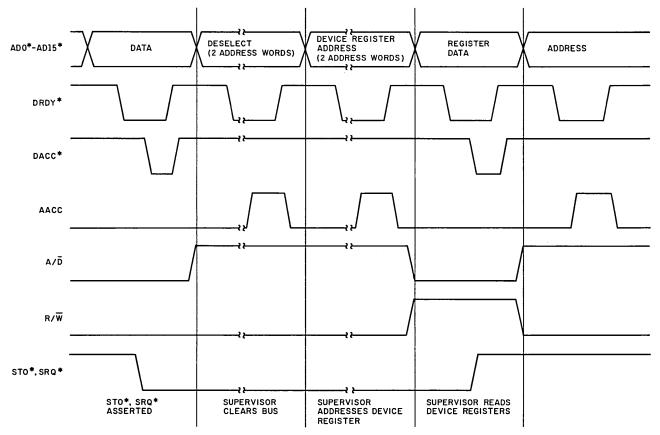

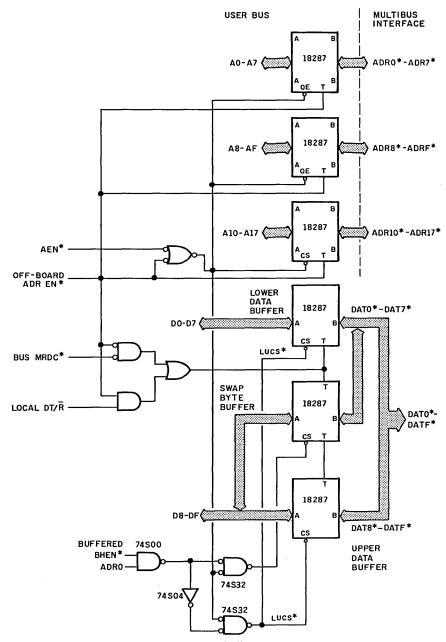

# 3.5 Programming Information, 100

- 3.5.1 Register Addressing, 100

- 3.5.2 Multichannel Register Definition, 101

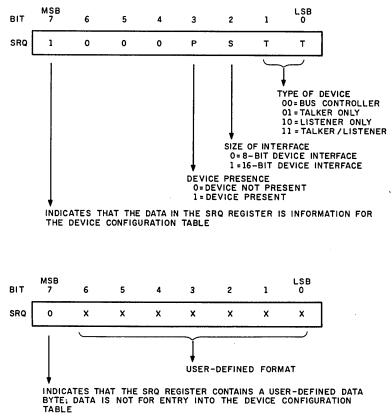

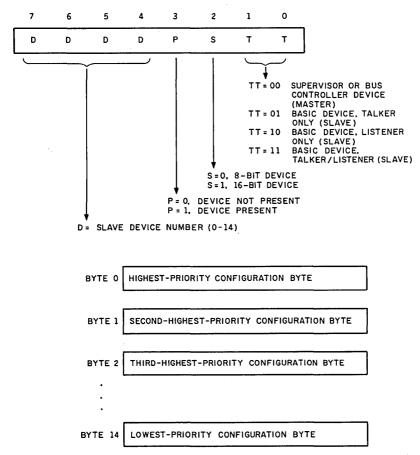

- 3.5.3 Device Polling, 103

- 3.5.4 Bus Exchange Programming, 104

# 3.6 Electrical Specification, 104

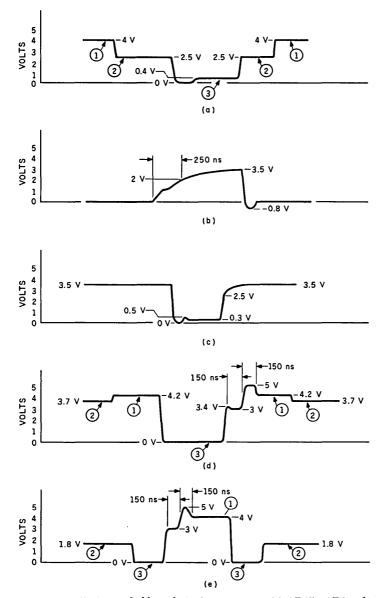

- 3.6.1 Logical State and Electrical Level Relations, 106

- 3.6.2 Signal Line Characteristics, 106

- 3.6.3 Bus Power Specification, 108

- 3.6.4 Environment, 108

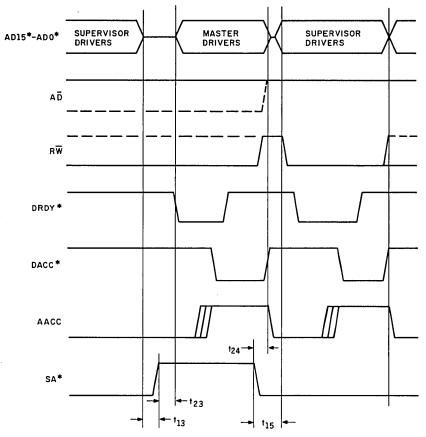

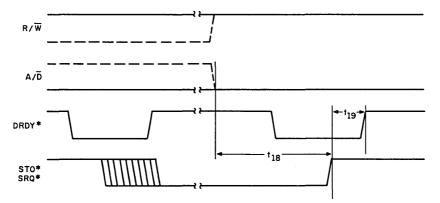

- 3.6.5 Bus Timing, 108

- 3.6.6 Receivers, Drivers, and Terminations, 115

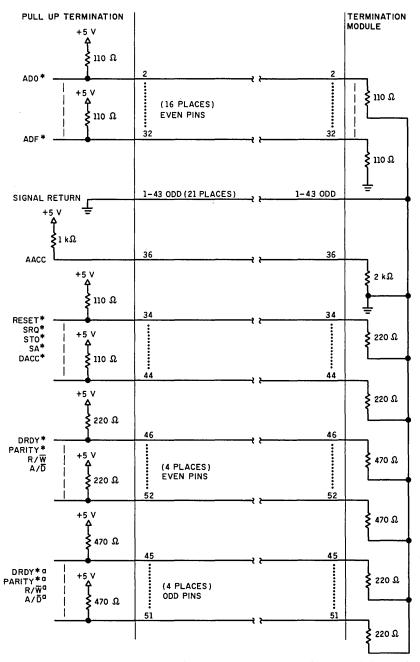

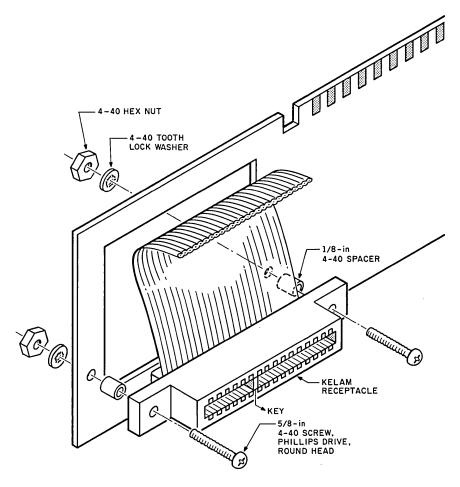

# 3.7 Mechanical Considerations, 116

- 3.7.1 Cable Specification, 116

- 3.7.2 Connector-Receptacle Specification, 119

- 3.7.3 Multichannel Bus Pin Assignments, 119

- 3.7.4 Bus Termination, 120

- **3.8 Levels of Compliance**, 120

- 3.8.1 Variable Elements of Capability, 120

- 3.8.2 Compliance-Level Notation, 122

- 3.9 Summary, 123

- 4 ISBX I/O BUS

- 4.1 Why the ISBX Bus is Required, 124

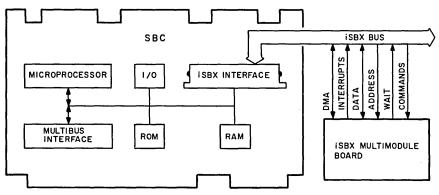

- 4.2 Logical Description of the ISBX Bus, 125

- 4.2.1 Bus Devices, 126

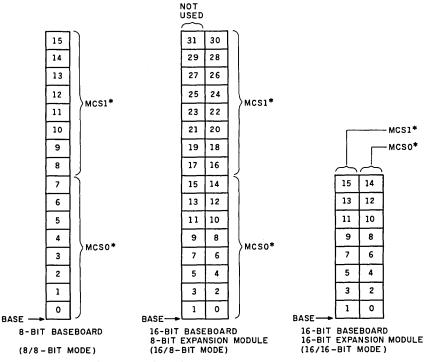

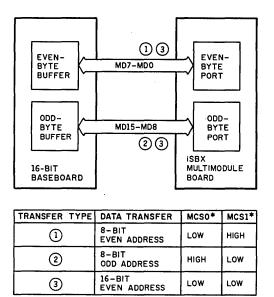

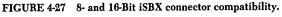

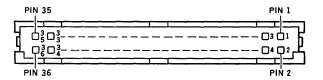

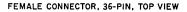

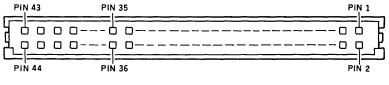

- 4.2.2 8- and 16-Bit Compatibility; Bus Device Notation, 129

# 4.3 Bus Signal Definitions, 129

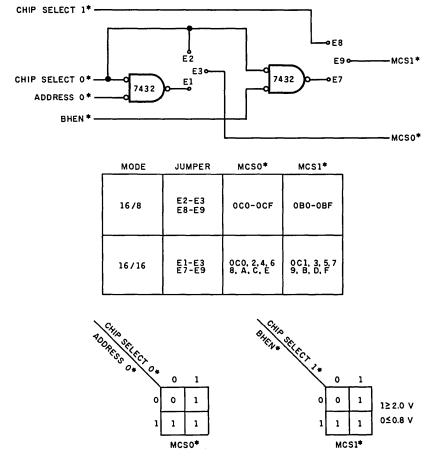

- 4.3.1 Address and Chip Select Lines, 129

- 4.3.2 Data Lines, 133

- 4.3.3 Control Lines, 134

- 4.3.4 Direct Memory Access, 137

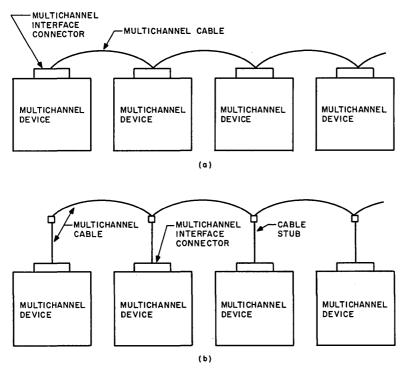

- 4.3.5 Miscellaneous Lines, 138

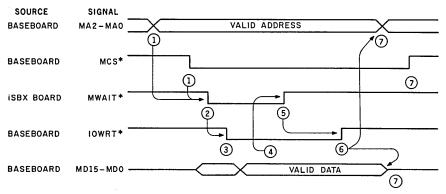

# 4.4 Bus Operation Overview, 139

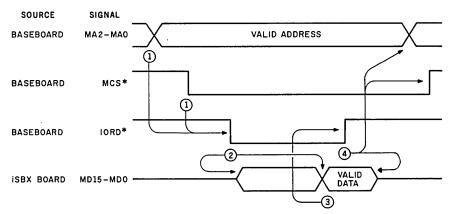

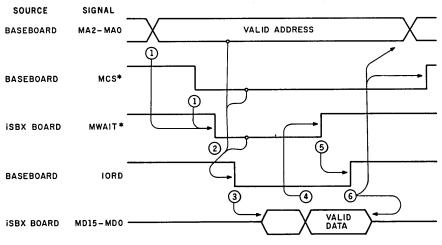

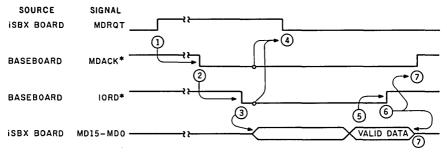

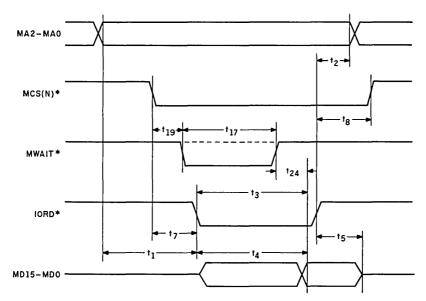

- 4.4.1 I/O Read Operations, 139

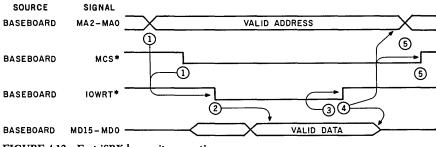

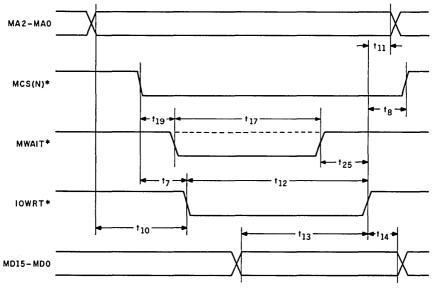

- 4.4.2 I/O Write Operations, 141

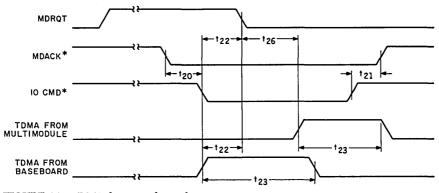

- 4.4.3 Direct Memory Access, Operations, 143

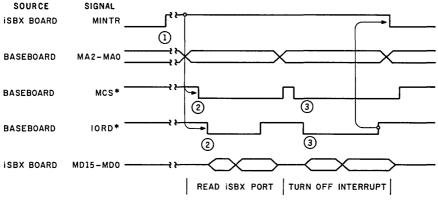

- 4.4.4 Interrupt Operations, 145

# 4.5 Detailed Electrical Description, 146

- 4.5.1 Logical State and Electrical Level Relations, 146

- 4.5.2 Signal Line Characteristics, 147

- 4.5.3 Bus Power Specification, 147

- 4.5.4 Temperature and Humidity Limits, 148

- 4.5.5 Storage, 149

- 4.5.6 Bus Timing, 149

- 4.5.7 Receivers, Drivers, and DC Specifications, 153

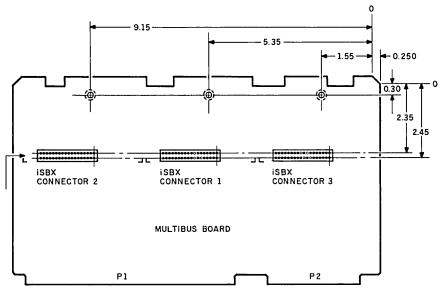

- 4.6 Baseboard Layout Considerations, 153

# 4.7 Mechanical Considerations, 155

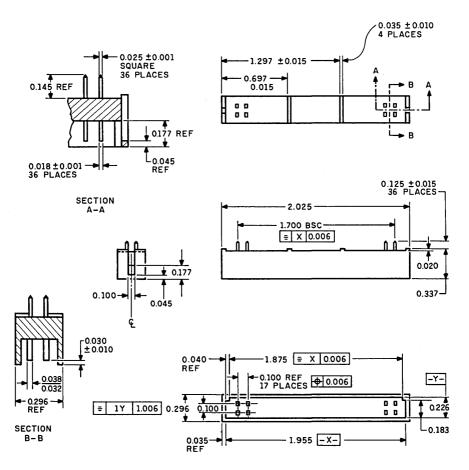

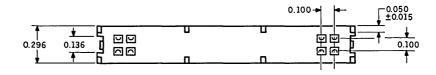

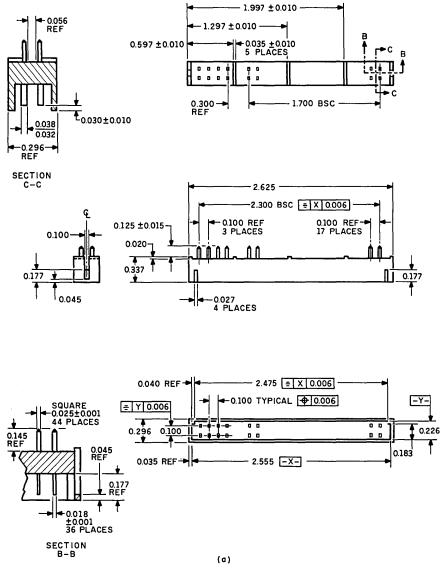

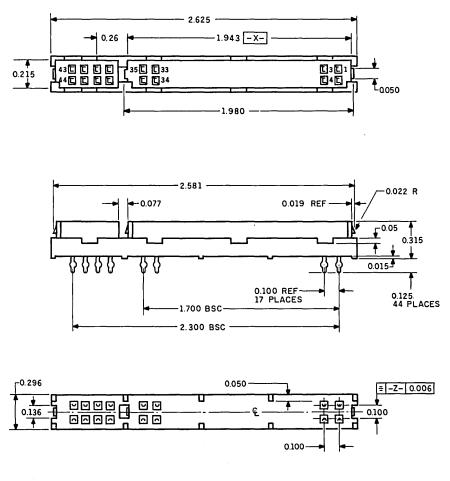

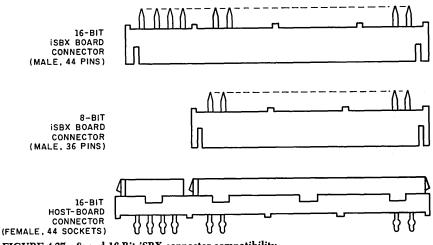

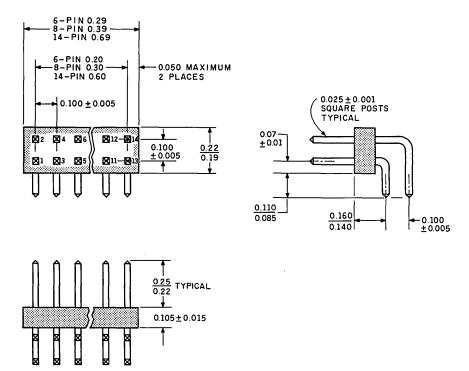

- 4.7.1 iSBX Connector, 155

- 4.7.2 Pin Assignments, 156

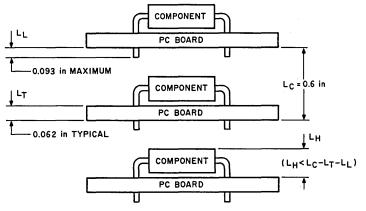

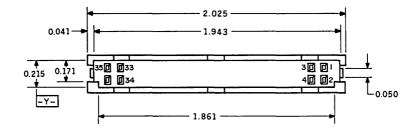

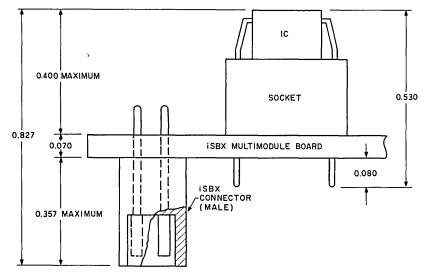

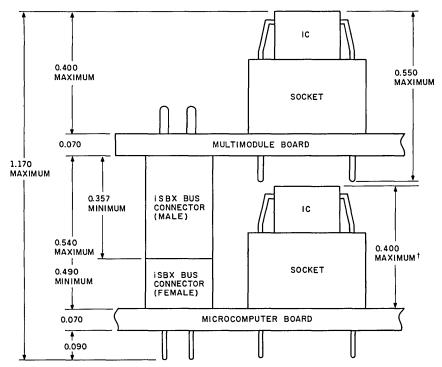

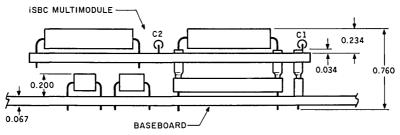

- 4.7.3 iSBX Multimodule Board Height Requirements, 156

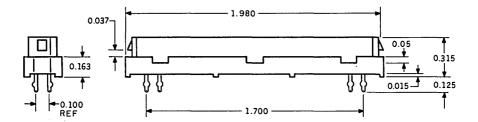

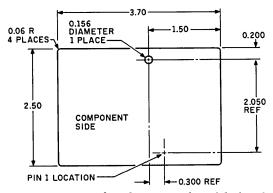

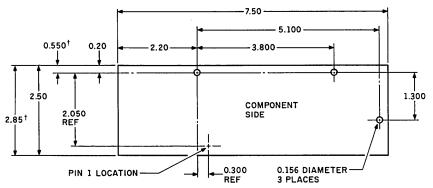

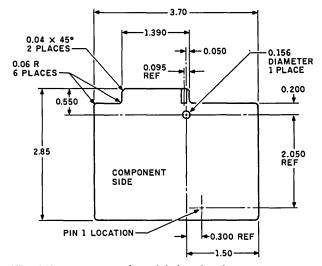

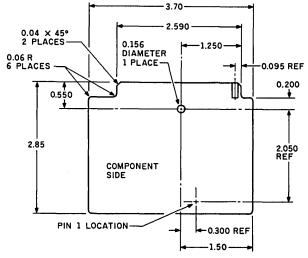

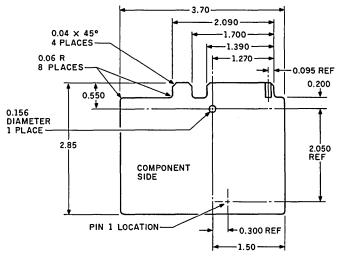

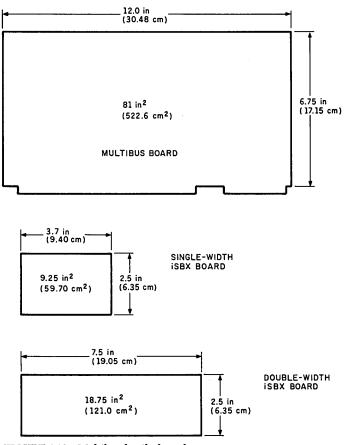

- 4.7.4 iSBX Multimodule Board Outlines, 161

- 4.7.5 iSBX Multimodule Board User I/O Connector Outlines, 161

# 4.8 Levels of Compliance, 162

- 4.8.1 Variable Elements of Capability, 166

- 4.8.2 Baseboards and iSBX Multimodule Boards, 167

- 4.8.3 Compliance-Level Notation, 167

- 5 ILBX BUS

- 5.1 Why the iLBX Bus is Required, 169

# 5.2 Logical Description of the iLBX Bus, 171

- 5.2.1 Bus Devices, 172

- 5.3 Bus Signal Definition, 175

- 5.3.1 Address Lines, 175

- 5.3.2 Data Lines, 176

- 5.3.3 Transfer Parity, 177

- 5.3.4 Control Status Lines, 177

- 5.3.5 Command Lines, 178

- 5.3.6 Bus Access Control Lines, 181

# 5.4 Bus Operation Overview, 184

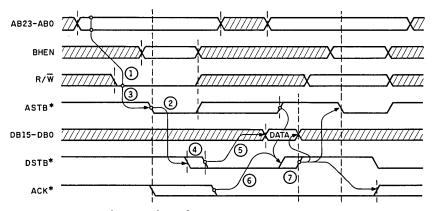

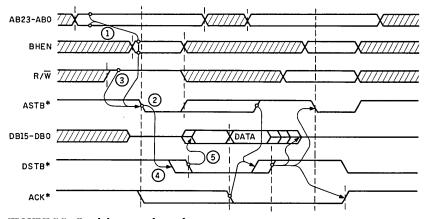

- 5.4.1 Write Data Operation, 184

- 5.4.2 Read Data Operation, 186

- 5.4.3 Bus Time-Out Operation, 188

- 5.4.4 Bus Exchange Operation, 189

# 5.5 Detailed Electrical Description, 190

- 5.5.1 Logical State and Electrical Level Relations, 190

- 5.5.2 Signal Characteristics, 191

- 5.5.3 Bus Power Specification, 192

- 5.5.4 Temperature and Humidity Limits, 192

- 5.5.5 Bus Timing, 192

- 5.5.6 Receivers, Drivers, and DC Specifications, 197

# 5.6 Mechanical Considerations, 198

- 5.6.1 Bus Connector Considerations, 198

- 5.6.2 Form Factor Considerations, 199

# 5.7 Levels of Compliance, 204

- 5.7.1 Variable Elements of Compatibility, 206

- 5.7.2 Compliance-Level Notation, 207

- 5.8 Summary, 208

6.1

# PART 2 THE MULTIBUS FAMILY ARCHITECTURES

# 6 SINGLE-BOARD COMPUTERS

- Definition of a Single-Board Computer, 211

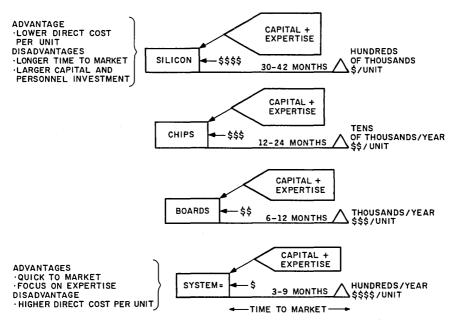

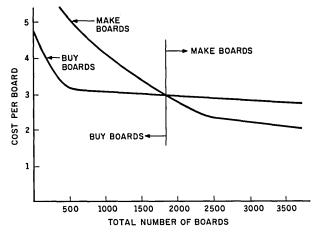

- 6.1.1 Trends in and Motivations for Using an SBC, 216

- 6.1.2 SBCs: What Level of Integration Should You Buy? 219

# 6.2 SBC Architectures, 221

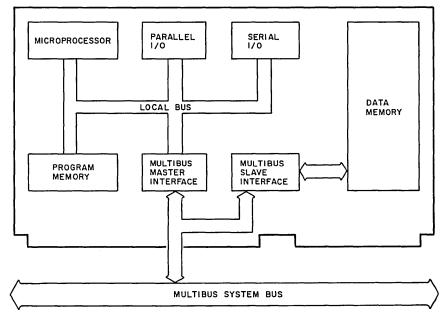

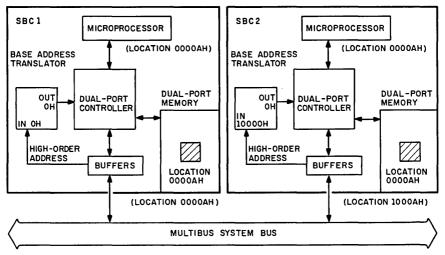

- 6.2.1 First-Generation Architecture, 222

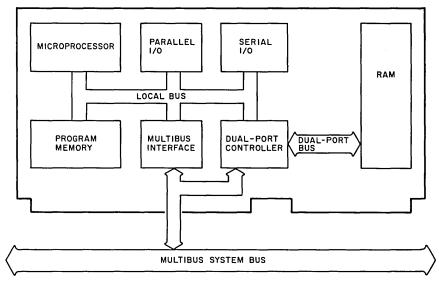

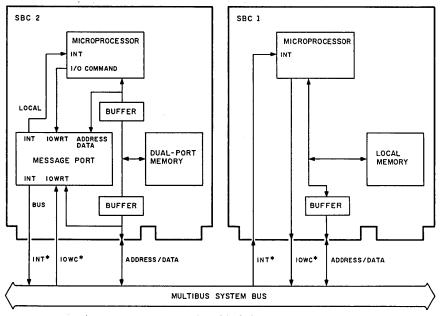

- 6.2.2 Second-Generation Architecture-Dual-Port Memory, 224

- 6.2.3 I/O Expansion, 227

- 6.2.4 Memory Expansion, 230

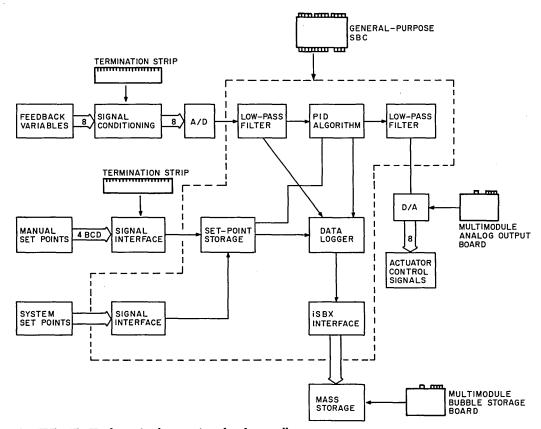

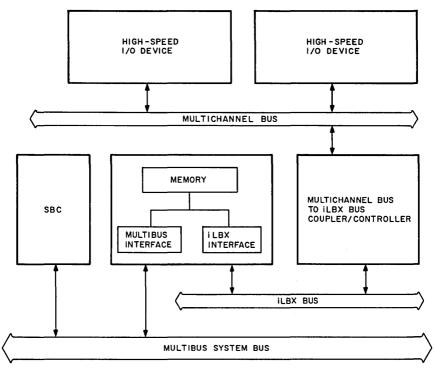

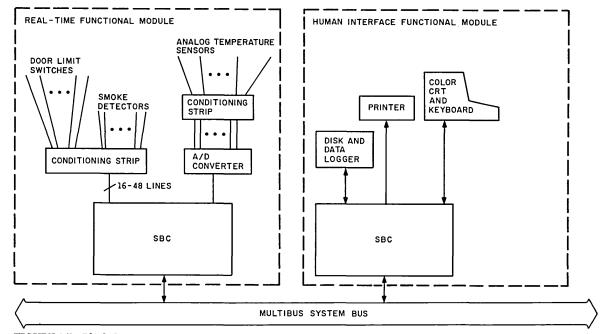

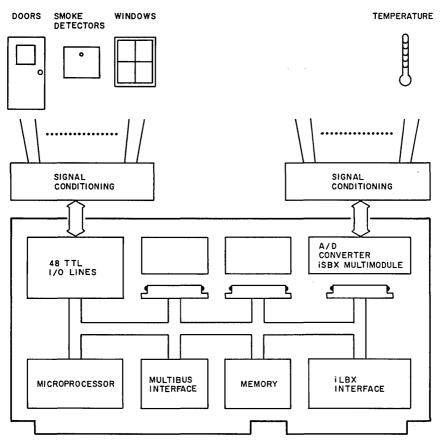

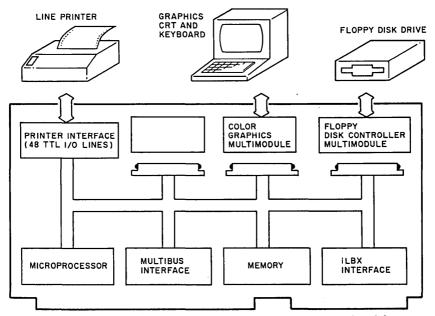

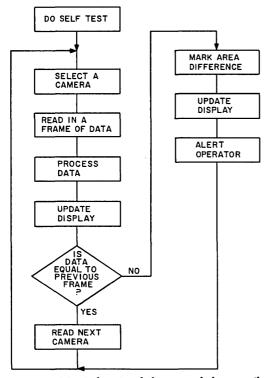

- 6.3 A Simple Design Using SBCs, 232

- 6.4 Summary, 235

# 7 MULTIPROCESSING WITH MICROPROCESSORS

- 7.1 Definition of a Multiple-Processor System, 238

- 7.2 What is a Multiprocessor Computer? 244

238

209

# 7.3 Motivation for Multiprocessing, 245

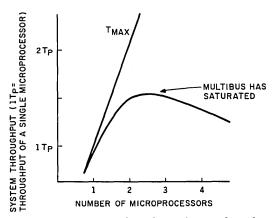

- 7.3.1 Throughput, 246

- 7.3.2 Reliability and Availability, 249

- 7.3.3 Flexibility, 250

- 7.3.4 VLSI Revolution, 251

- 7.3.5 Software Is Still a Problem, 251

# 7.4 Multiprocessor Architectures on the Multibus Structure,

- 251

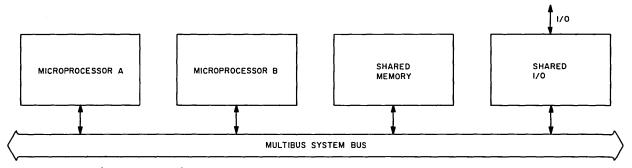

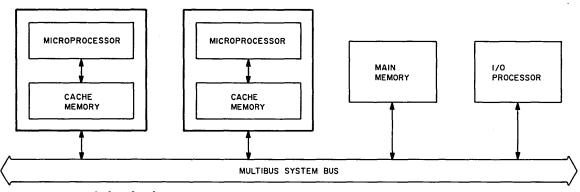

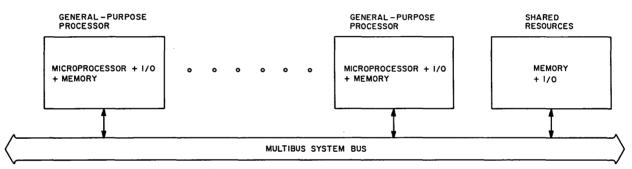

- 7.4.1 A Simple Multiprocessor Architecture, 253

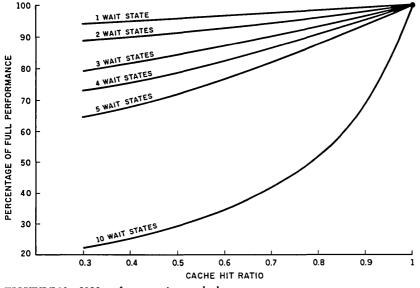

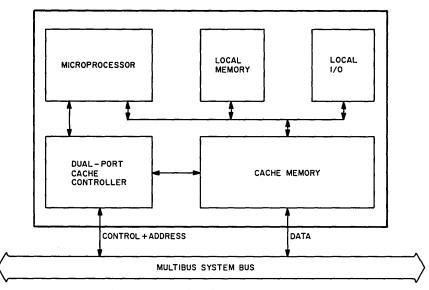

- 7.4.2 A Cached Memory Architecture, 253

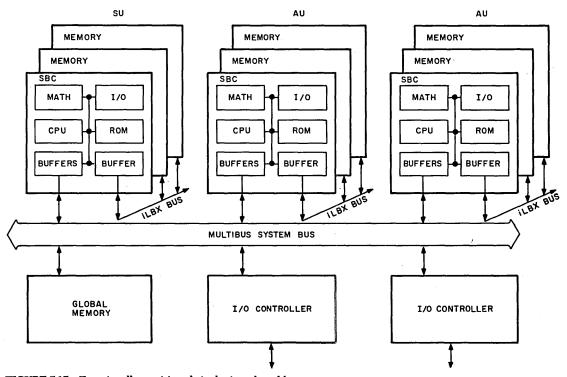

- 7.4.3 A Functional Partitioned Multiprocessor Architecture, 257

- 7.5 System Bus Requirements for Multiprocessor Systems, 261

- 7.5.1 Shared System Resources, 261

- 7.5.2 An Interprocessor Signaling Mechanism, 261

- 7.5.3 An Efficient Bus-Arbitration Scheme, 262

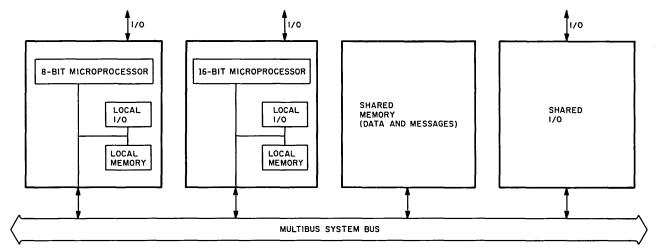

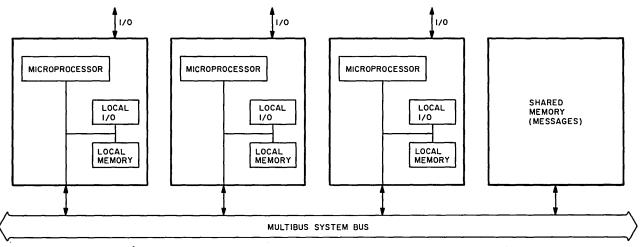

7.6 Three Multiprocessor Implementations, 262

- 7.6.1 Single Time-Sharing Bus System, 263

- 7.6.2 Single Time-Sharing Bus System with Cache, 266

- 7.6.3 Functionally Partitioned Single Time-Sharing Bus System, 269

- 7.7 Summary, 271

References, 272

### 8 MULTICOMPUTING WITH MICROPROCESSORS

8.1 Definition of a Multicomputing System, 273

# 8.2 Motivation for Multicomputing, 277

- 8.2.1 Increased Throughput and Reduced Response Time, 278

- 8.2.2 Module Design and Design Simplicity, 280

- 8.2.3 Flexibility and Modular Expansion, 282

- 8.2.4 Incorporating New VLSI Quickly with Standard Interfaces, 282

# 8.3 Multicomputing Architectures with the Multibus Family, 283

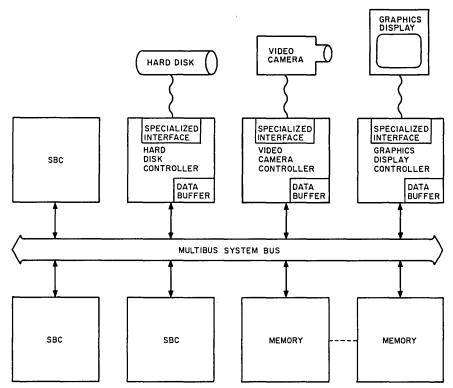

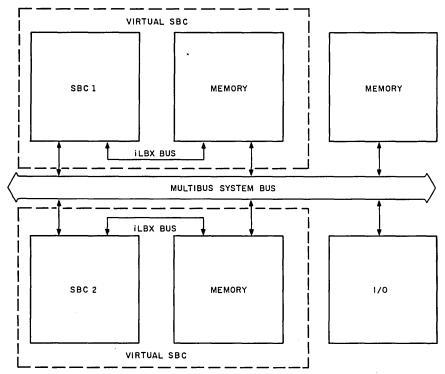

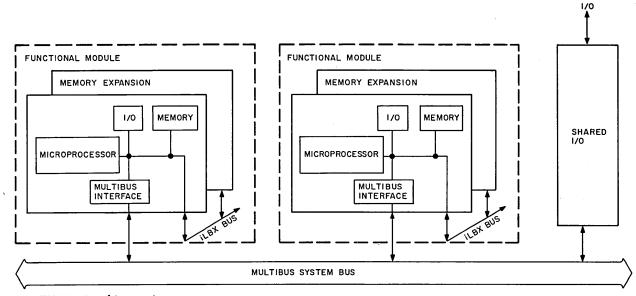

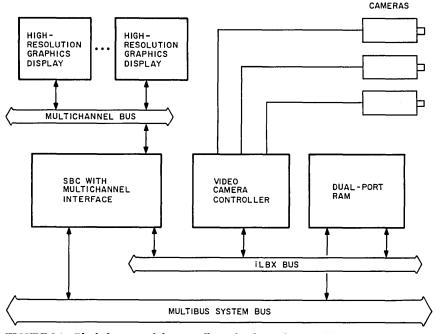

8.3.1 How to Use a System Bus in a Multicomputing Architecture, 286

# 8.4 A Simple Multicomputing System Example, 288

- 8.4.1 Designing the System, 289

- 8.4.2 Adding High Speed I/O, 295

- 8.5 Summary, 297

- References 298

### PART 3 MULTIBUS FAMILY APPLICATIONS

# 9 SYSTEM DESIGN GUIDELINES

# 9.1 Building Multibus-Based Systems, 301

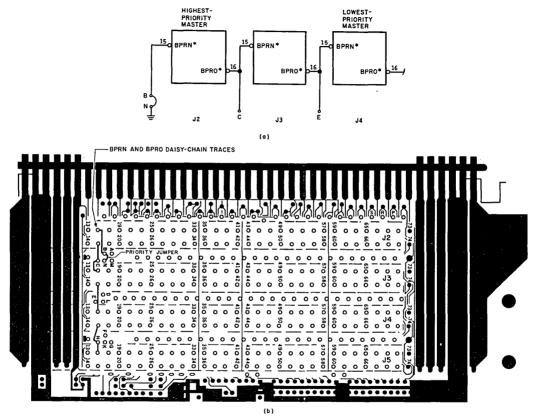

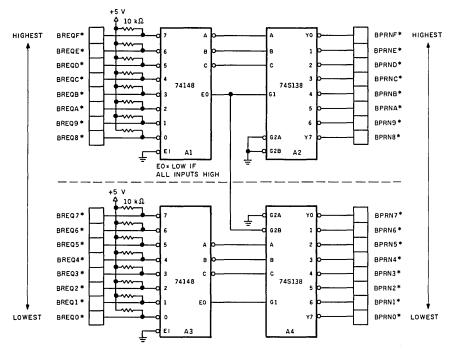

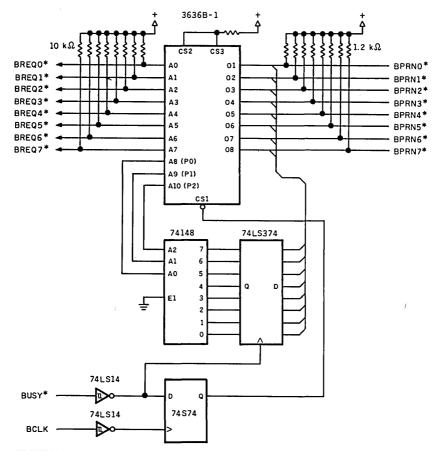

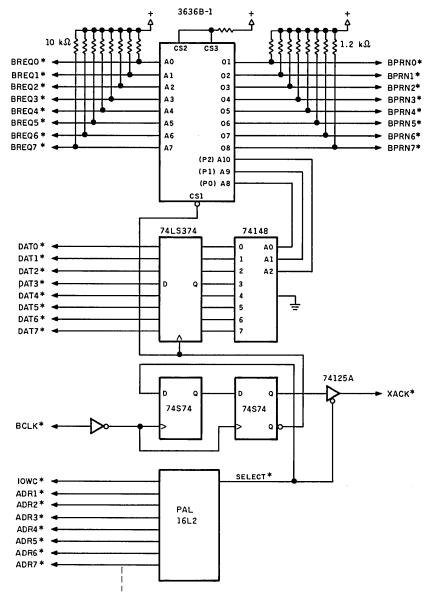

9.1.1 Bus Arbitration Techniques, 302

9.1.2 Memory Configuration and Addressing, 309

# 273

299

- 9.1.3 Interrupt Configuration, 313

- 9.1.4 Time-Out, 314

- 9.1.5 Bus Clocks, 315

- 9.1.6 Levels of Compliance, 315

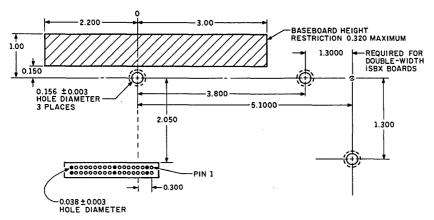

- 9.1.7 Mechanical Considerations, 316

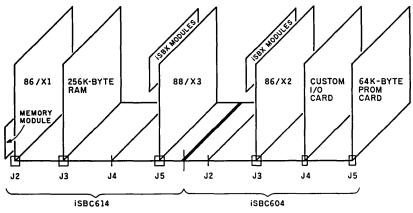

# 9.2 Building Systems with ISBX Multimodules, 319

- 9.2.1 Addressing, 319

- 9.2.2 Interrupts, 320

- 9.2.3 DMA, 320

- 9.2.4 Levels of Compliance, 320

- 9.2.5 Mechanical Considerations, 321

# 9.3 Building Systems with the Multichannel Bus, 322

- 9.3.1 Device Considerations, 323

- 9.3.2 Cable and Termination Considerations, 326

- 9.3.3 Levels of Compliance, 329

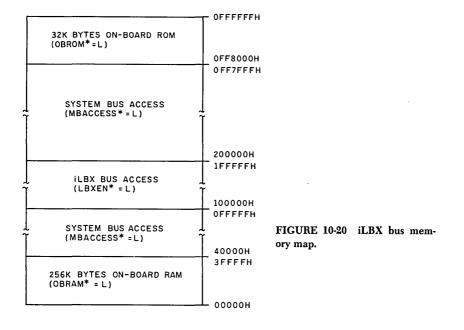

# 9.4 Building Systems with the ILBX Bus, 331

- 9.4.1 Address Space, 332

- 9.4.2 Secondary Master, 332

- 9.4.3 Acknowledge Timing, 333

- 9.4.4 Levels of Compliance, 334

- 9.4.5 Mechanical Considerations, 335

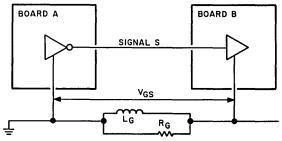

# 9.5 Reducing Multibus System Noise, 336

- 9.5.1 Signal-to-Signal Coupling, 337

- 9.5.2 Ground Shifts, 339

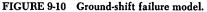

- 9.5.3 Signal Ringing, 341

- 9.5.4 Noise Reduction Summary, 342

- 9.6 System Configuration Example, 343

# 10 BOARD DESIGN GUIDELINES

- 10.1 General Design Guidelines, 349

- 10.1.1 Electrical Considerations, 349

- 10.1.2 Thermal Considerations, 352

- 10.1.3 Mechanical Considerations, 353

- 10.2 General Bus Interface Design Guidelines, 356

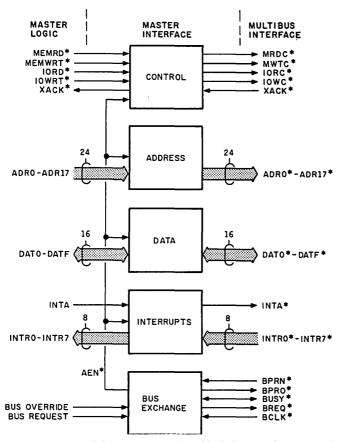

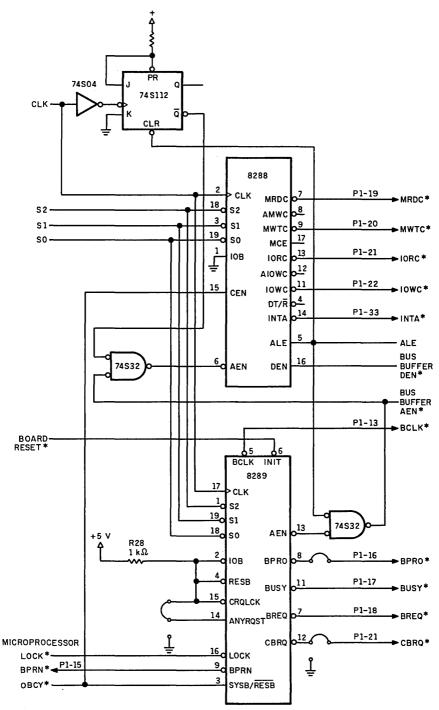

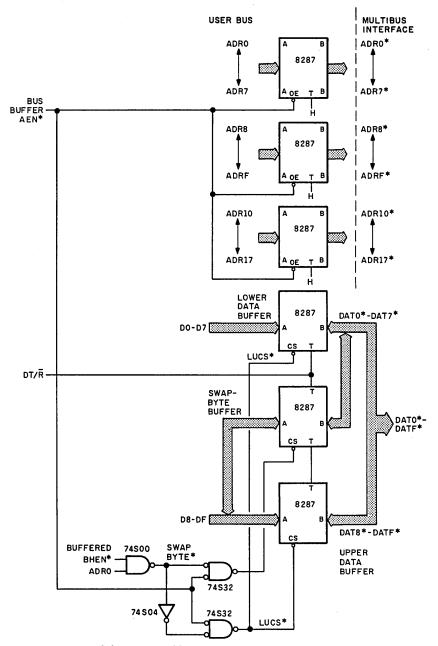

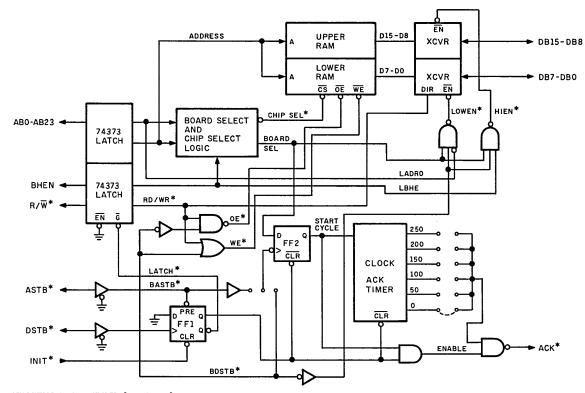

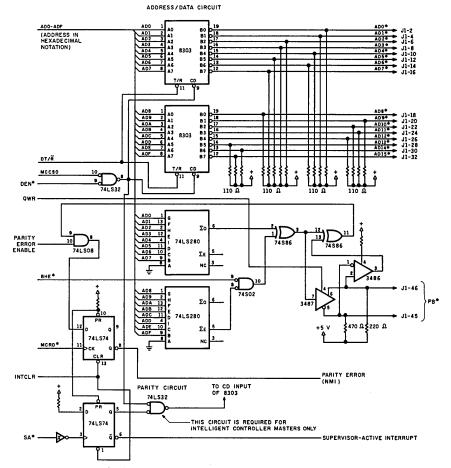

- 10.2.1 Multibus Master Interface, 356

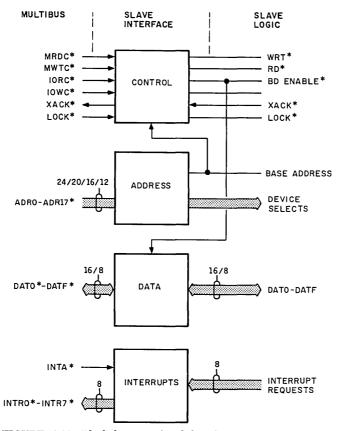

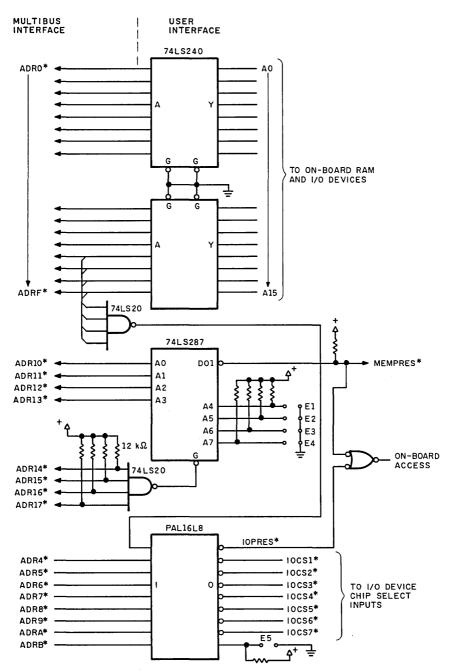

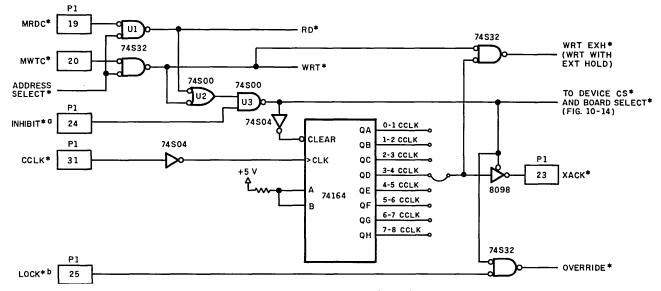

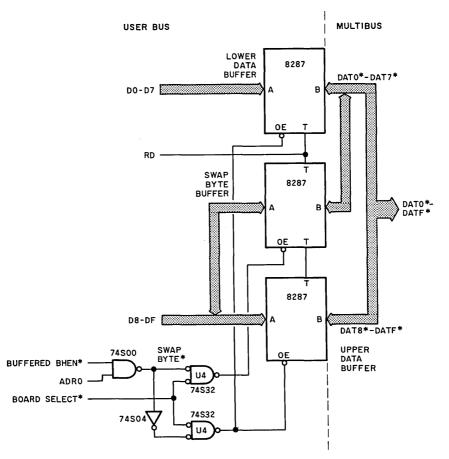

- 10.2.2 Multibus Slave Interface, 364

- 10.2.3 iSBX Multimodule Interface, 373

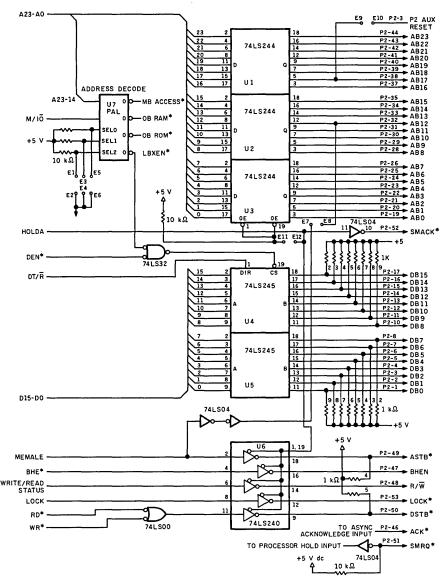

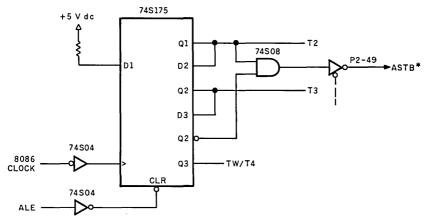

- 10.2.4 iLBX Master Interface, 376

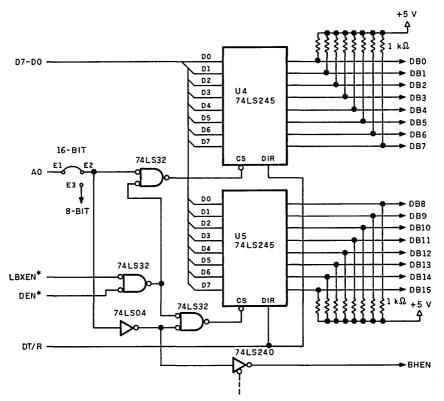

- 10.2.5 iLBX Slave Interface, 382

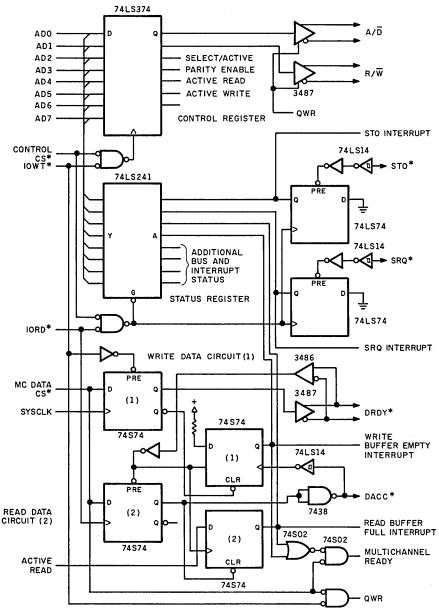

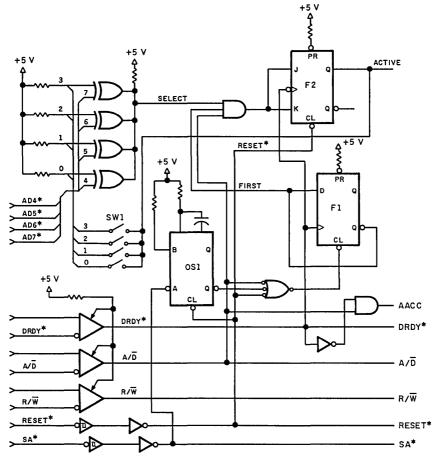

- 10.2.6 Multichannel Master Interface, 385

- 10.2.7 Multichannel Slave Interface, 390

# 10.3 Special Interface Guidelines, 394

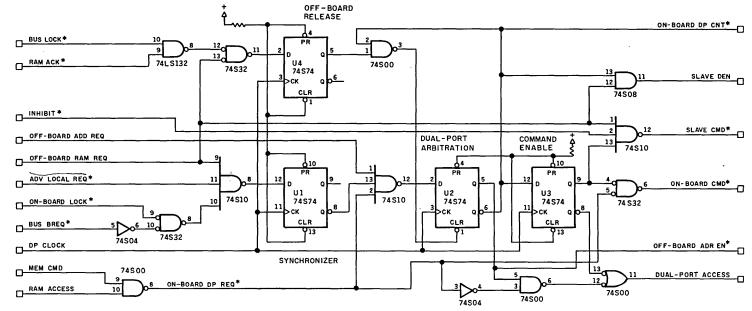

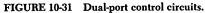

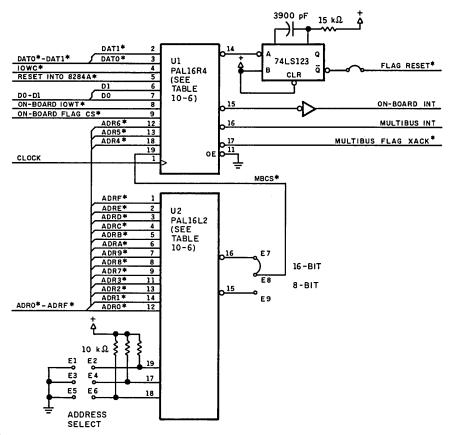

- 10.3.1 Dual-Port Memory Interface, 395

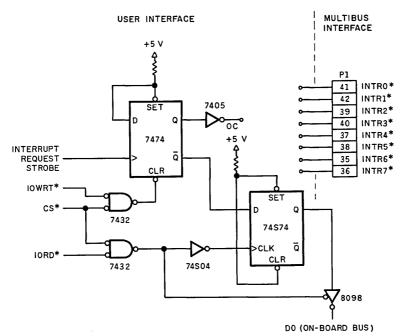

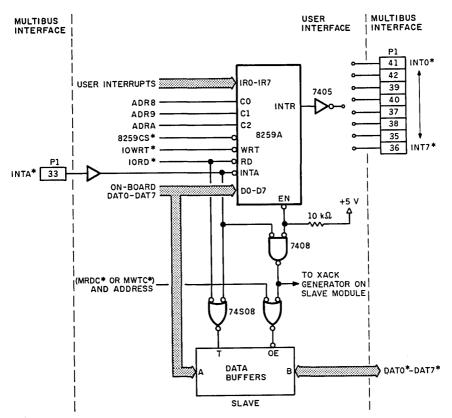

- 10.3.2 Interprocessor Communication Port, 398

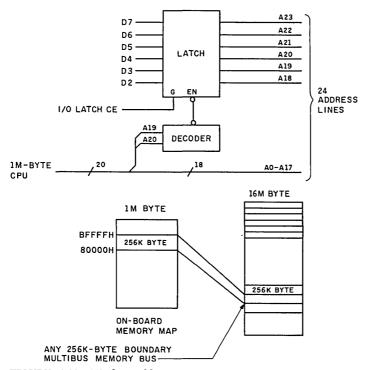

- 10.3.3 16M-byte Addressing, 401

- 10.3.4 Standard I/O Addresses, 404

| 10.4 | Multibus System Bus Backplane Design, 405 |                                             |  |  |

|------|-------------------------------------------|---------------------------------------------|--|--|

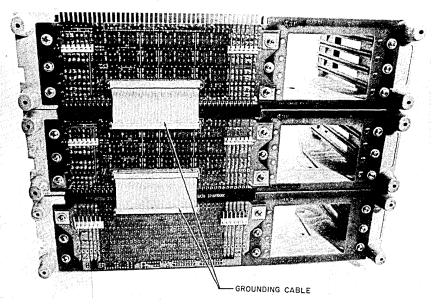

|      | 10.4.1                                    | Backplane Layout Considerations, 405        |  |  |

|      | 10.4.2                                    | Parallel-Priority Arbitration Examples, 408 |  |  |

| 10.5 | Summary, 414                              |                                             |  |  |

|      | Rəfərəncəs, 414                           |                                             |  |  |

# APPENDIX: LIST OF ABBREVIATIONS

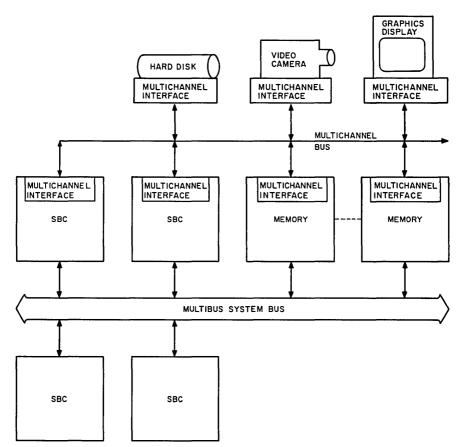

INDEX

# Preface

The Multibus/IEEE-796 is a commercial-quality industry-standard bus structure for use in microprocessor-based systems. Additionally, three separate buses have been developed to complement and extend the capabilities of the Multibus structure. Together these four structures form the Multibus family of structures. The Multibus family consists of the Multibus system bus, which is the center of all Multibus-based systems; the iSBX bus, a low-cost local (on-board) input-output expansion bus; the Multichannel bus, a very high speed cable bus designed to move blocks of data between peripherals and intelligent subsystems and Multibus-based systems; and the iLBX bus, a high-speed memory execution bus that allows a microprocessor on a single-board computer to expand its local memory using multiple boards.

This book provides the reader with a basic understanding of the structures, architectures, and detailed hardware designs of the various modules that can be used in association with the Multibus system bus, the iSBX local input-output bus, the Multichannel high-speed cable bus, and the iLBX local execution bus. It describes these various bus structures using simple concepts, and then builds on them until the reader understands the different architectures that can be constructed. The book, which is intended for board- and system-level hardware design and evaluation engineers and their managers, is essential for anyone involved with Multibus-based products. It provides detailed bus interface information and also serves as a quick reference for those designing Multibus-based systems. The text is supported by a wealth of examples and illustrations.

The book is divided into three parts: (1) structures, in which the electrical and mechanical specifications of the Multibus family members are described; (2) architectures, in which the different architectures are described that can be built on and around the Multibus family members; and (3) applications, in which hardware design examples are given for interfacing modules to the various Multibus family members. The structures section reviews each of the different Multibus family structures. First the structures are described conceptually; then the functions and the electrical and mechanical specifications of the bus are described in detail.

The Multibus family of structures supports a wide spectrum of system architectures, from simple, low-cost uniprocessing systems to sophisticated, distributed multiple-processor systems yielding high throughput. The architectures section considers the benefits and trade-offs of each of these different architectures in detail. Examples of several types of systems, including uniprocessing, multicomputing, and multiprocessing systems, are used to explain the major architectural approaches, interconnection schemes, and related hardware and software trade-offs. Other topics covered include an overview of system design issues and some discussion of highly reliable computers.

The applications section gives the reader examples of various interface circuits for the Multibus family structures. Each example provides enough detail to make it possible to actually implement the module or interface. This section also provides evaluation criteria for purchasing Multibus-compatible products.

> James B. Johnson Steve Kassel

# Acknowledgments

We wish to acknowledge the help of many colleagues at Intel's OEM Microcomputer Operations group (Hillsboro, Oregon) over the years during which most of these ideas, specifications, and applications were formulated and refined. The special efforts of Clark Allsworth, who provided constructive criticism of the early manuscript, have been most helpful. The final manuscript also has benefited greatly from the careful reading and comments of Craig Kinnie and Mary Slamp. The assistance of the engineering staff of Intel Corporation—especially Phil Drain, Pete MacWilliams, John Deignan, Scott Tetrick, and Ron Dilbeck—is also acknowledged.

# The Multibus Family of Bus Structures

# Introduction

This chapter provides a basic framework for evaluating microprocessor system buses and offers a little history of some of the most popular of such buses: the Multibus/IEEE-796 system bus and its extensions: the iSBX bus, the iLBX bus, and the Multichannel bus.<sup>1</sup> Basic system architectures of the Multibus/IEEE-796 family will also be defined.

# 1.1 OBJECTIVES AND GOALS OF MICROPROCESSOR-BASED SYSTEM BUSES

The system bus is the foundation of any computer system; it will influence the flexibility, cost, performance, and reliability of the system for its entire operating life. Advances in very large scale integration (VLSI) technology result in increased system complexity. The system bus, as a result, is recognized as the primary architectural resource, and it can frequently be the limiting factor in performance, reliability, and modularity. The most basic portion of a system bus is the bus structure, which defines all the signals and how the various system components interact with each other. These signals run along the backplane, where they can be supplied to the interface modules. A typical bus structure defines the word length, data types, and address length, as well as data transfer protocols such as memory reads, input-output (I/O) writes, and direct memory accesses (DMA). It will also specify some type of intermodule signaling such as interrupts, as well as a protocol to exchange control of the bus to various bus modules.

<sup>1</sup>Multibus, iSBX, iLBX, and Multichannel are trademarks of Intel Corporation, Santa Clara, California.

# 1.1.1 Do You Need a System Bus?

Not all users need a bus-oriented system. Such a system is generally more flexible, easier to upgrade, and easier to implement, but it is more expensive, module for module, than a specialized system. This expense is due to the greater component count required to meet the bus interface specification. Typically, a bus specification requires that each signal line be buffered. That can result in excess drive capacity, since most system designs use only a small fraction of the allowable receivers permitted on a signal. The buffers also require additional area on the board and increase power consumption. The additional parts increase the component cost, assembly time, and test time, which results in increased manufacturing cost.

In applications with lesser volume it will generally be found that the added cost of using standard bus design methodologies will be favorably offset by lower development costs during the shorter development time. In many instances, complete systems can be configured with off-the-shelf board-level products. In applications in which some custom design is required, standard bus design methodology is still applicable. The system design can be divided into two parts: the custom boards and the standard boards. The customized portion of the system can be completed with less expenditure of time and money because the system bus interface is already designed. The entire system development cost is lower because part of the system uses standard products. Busoriented systems also have a greater degree of configuration flexibility because different modules can be mixed and matched to produce a particular product or version. Products can easily be configured to meet the exact need of the end user.

Another important aspect of using standard bus-oriented systems is the ability to buffer a system design from the rapid technological changes in VLSI components. If a design needs more speed, it can be upgraded by plugging in a new bus-compatible module that uses a faster microprocessor or faster memory. Even using new technology such as converting a current design which used an 8-bit microprocessor to a 16-bit microprocesor would be permitted if the module met the bus interface requirements.

In summary, in applications that have very high volume, such as terminals or low-cost test equipment, it will be found that the use of a standard bus system adds undesirable cost to the end product. Systems that are dominated by manufacturing costs and do not need a great deal of configuration flexibility should use specialized configurations to avoid the costs of unnecessary parts and interconnections. On the other hand, systems that are dominated by development costs or need configuration flexibility should use a system bus scheme.

# **1.2** PICKING YOUR MULTIBUS FAMILY STRUCTURES

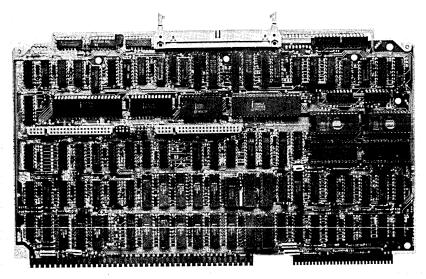

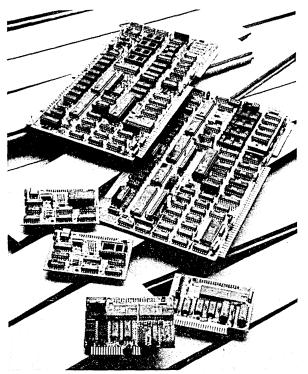

The Multibus system bus is a commercial quality bus for use in microprocessorbased systems. Some Multibus boards are shown in Fig. 1-1. The Multibus struc-

FIGURE 1-1 Multibus compatible boards.

ture provides all the necessary signals for easy system expansion with additional memory, I/O, or microprocessor modules. The Multibus system architecture has been developed to expand beyond the capabilities of the basic system bus structure with three new bus structures. They are (1) the iSBX bus, a low-cost local (on-board) I/O expansion bus, (2) the Multichannel bus, a high-speed path for block data transfers between a Multibus-based system and peripherals or other remote computer systems and (3) the iLBX bus, a high-speed memory-only execution bus that makes it possible to expand the local memory of a microprocessor on a single-board computer (SBC) by using multiple boards.

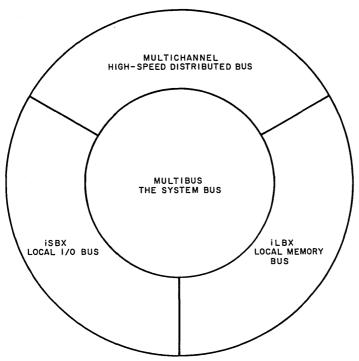

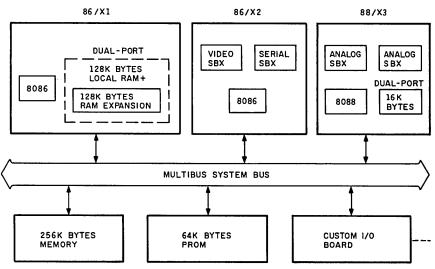

These three extensions—the iSBX bus, the Multichannel bus, and the iLBX bus—were developed to optimize a particular aspect of the basic Multibus system. The Multibus system bus, along with its three extensions, comprises the Multibus family (Fig. 1-2). The three extensions complement the Multibus system bus, which permits a system designer to make the best cost-performance trade-offs during the system design. The Multibus family provides a complete set of system building blocks for use in a wide variety of system architectures.

Picking the right system bus for a specific application is a very important and difficult task. When different system bus structures are evaluated, the following objectives need to be considered:

FIGURE 1-2 The Multibus family.

- Support of a wide range of system architectures

- A conceptually simple structure

- A structure that can quickly incorporate new VLSI

- A reliable, cost-effective structure

- A well-defined, documented, and controlled standard

Each of the above objectives will be discussed to provide a basis for understanding its effect on system design. Then the Multibus family will be examined in light of all the objectives.

# 1.2.1 Support of a Wide Range of System Architectures

The bus structures provide the groundwork for the system hardware architecture; they must support many different architectures ranging from simple, single-master monolithic designs to complex multiple-processing, locally distributed designs. These different system architectures are briefly defined, and their effects on the bus structures are explored. (In Chaps. 6 to 8 the different architectures are explored in more detail.)

# SINGLE-PROCESSOR ARCHITECTURE

A system with single-microprocessor architecture can have only one user-reprogrammable microprocessor. Although the system can have other bus masters with microprocessors, such as peripheral controllers, on them, these microprocessors are dedicated to particular tasks and cannot be reprogrammed—they simply replace logic and do it more cost-effectively. Two types of single-microprocessor architectures will be discussed. The first is a very traditional approach used by most of the basic minicomputer and microprocessor systems; the second is an evolution of the first that is driven by the effects of VLSI technology.

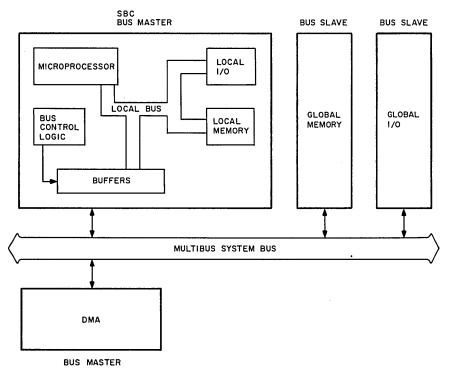

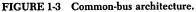

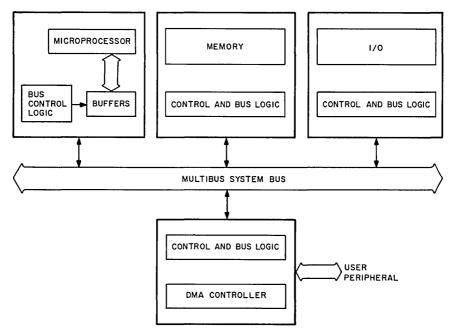

The most straightforward microprocessor system bus architecture is a splitbus or common-bus architecture, in which both the microprocessor and the system have equal access to the memory and other system resources. Examination of Fig. 1-3 reveals four basic blocks: the SBC unit, the global memory unit, the global I/O unit, and the DMA unit. The microprocessor unit is responsible for

# 8 THE MULTIBUS FAMILY OF BUS STRUCTURES

all execution of code, all communication in the system, and most of the lowspeed I/O tasks, and it can control the system bus (a bus master). The memory unit holds or stores all system data and program execution code and can respond only to bus commands; it is a bus slave. The I/O unit is responsible for interfacing to all the low-speed I/O in the system and is a bus slave; it interfaces to such devices as printers, control lines on machines, and front panels of boxes. The fourth block is the DMA unit; it handles all high-speed I/O devices such as disks, graphics stations, and video cameras without the aid of the microprocessor. This block's main task is to transmit high-speed data between the system peripherals and the system memory unit. The DMA unit is a bus master and can control the system bus. The microprocessor unit initializes the DMA unit for each block of data transfer, and then the DMA unit sustains independent activity. The microprocessor unit tells the DMA unit the direction of the data flow and where to put or get the data in system memory. Once the block transfer is complete, the DMA unit notifies the microprocessor unit via an interrupt.

The common-bus approach is very popular in minicomputer designs and early microprocessor systems. It was used in the first systems based on the Multibus system bus and in many personal computers such as the Apple II<sup>2</sup> and the TRS-80.<sup>3</sup> The microprocessor uses the system bus to execute out of the memory and to perform all I/O operations. In this configuration, the system bus is used as an execution bus. The advantages of this approach are simplicity and architectural consistency, which means that all system resources are accessible from the system bus and are made global; there are no resources in the system that only one of the bus masters can access. As an example, the microprocessor and disk controller can access all of the memory; that is, the memory is made global. System capacity is easily expanded by installing new modules. The limitations of the common-bus system are (1) the high utilization of the system bus required by most new microprocessors, which leaves no system bus bandwidth for other system activities such as DMA, and (2) the slow throughput, which is due to both arbitration time to gain control of the system bus and the extra delays of the multiple layers of buffers used to get to and from the system bus. The addition of another DMA device could slow the system down if the system bus cannot support all the bus master's memory bandwidth needs.

# SINGLE-BOARD COMPUTERS

The 1970s produced VLSI technology, which increased the performance and capabilities of silicon devices and at the same time reduced the number of devices and cost to implement complex functions. It became possible to inte-

<sup>&</sup>lt;sup>2</sup>Apple II is a trademark of Apple Corporation, Cupertino, California.

<sup>&</sup>lt;sup>3</sup>TRS-80 is a trademark of Radio Shack Division of Tandy Corporation, Fort Worth, Texas.

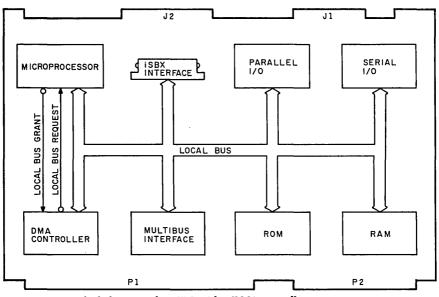

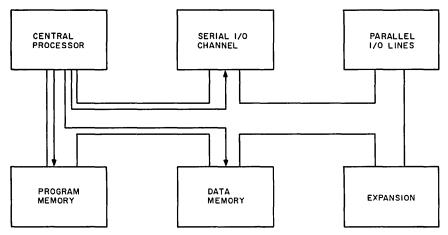

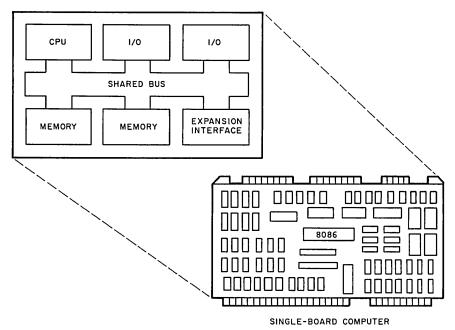

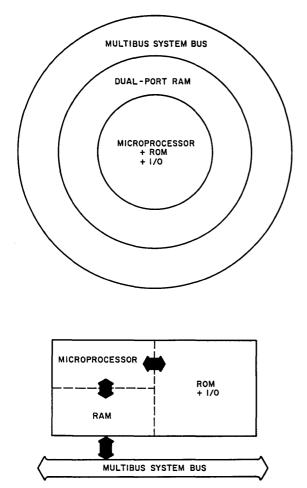

grate on a single circuit board all of the basic elements of the common-bus computer architecture. This resulted in the first SBC. (Figure 1-4 is a block diagram of an SBC, and Fig. 1-5 shows the implementation.) A typical SBC in the 1970s consisted of the generation of the system clock, read and write memory (RAM), real-only memory (ROM), I/O ports and drivers, serial communications interface, and bus control logic and drivers. The SBC is really a selfcontained computer system which offers an inexpensive, yet expandable, way to computerize a product with minimal engineering effort.

The key advance that VLSI technology provided was reduction of device count that in turn reduced the amount of printed-circuit board (PCB) area required to support system functions. An example is the serial communications area: the 8251 programmable communications interface chip reduced the serial communication interface logic from 30 in<sup>2</sup> (193.56 cm<sup>2</sup>) to less than 4 in<sup>2</sup> (25.8 cm<sup>2</sup>). Similiar VLSI advances in devices that implement other system functions permitted the first SBC to be built. The trend in Multibus-compatible SBCs is toward enhancement of existing features as well as the addition of new ones. These trends can be seen in Heurikon Corporation's MLZ-91A SBC, which

FIGURE 1-4 Block diagram of a single-board computer.

FIGURE 1-5 Single-board computer.

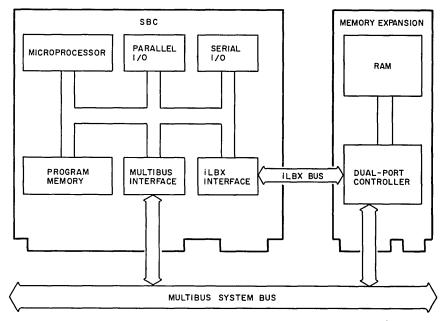

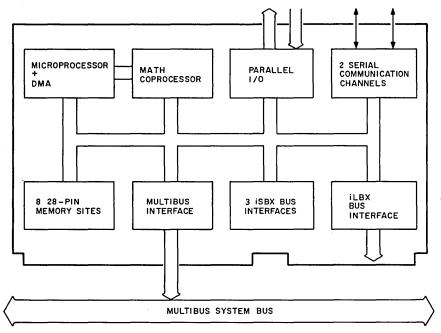

includes a 4-MHz Z80A<sup>4</sup> microprocessor, 64K bytes of RAM, DMA controller, a double-density floppy disk drive controller, hard disk and tape interfaces, and hardware mathematics support. Another example of the enhancement of features on an SBC is Intel Corporation's iSBC 86/30, which includes an 8-MHz 8086 microprocessor, 128K bytes of dual-ported RAM, four 28-pin sites, 24 parallel I/O lines, an RS-232 serial port, two iSBX connectors for inexpensive I/O expansion and high-speed mathematics support via an 8087 coprocessor.

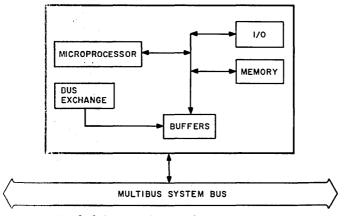

The architecture of an SBC is designed to permit access of local resources (memory and I/O on the SBC) by the local microprocessor without accessing the system bus. Local resources are accessible only by the local microprocessor; no other system bus device can access them. The microprocessor operates fastest when using local resources because it does not have to arbitrate for the system bus and the design can be optimized for a particular implementation. This is particularly useful in multiple-processing applications, since all the SBCs can perform true parallel processing when executing out their local resources. The potential disadvantage is that system consistency is lost. Another master in the system, such as a disk controller, cannot access the local resources.

# MULTICOMPUTING AND MULTIPROCESSING

The VLSI explosion has continued to reduce the cost of a microprocessor to such a low level that applying multiple microprocessors to meet system performance requirements has become an attractive and viable option. Using multiple micro-

<sup>4</sup>Z80A is a trademark of Zilog Corporation, Cupertino, California.

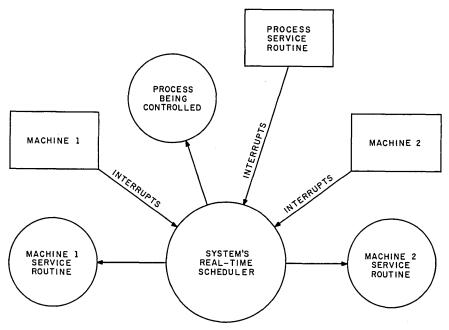

processors in a system design not only enhances system performance and throughput but also improves system reliability and system real-time response. Instead of doing one task at a time, a microprocessor-based system can increase throughput because the work is divided among a number of microprocessors. Another way of improving performance is by reducing the number of individual tasks any given microprocessor must handle. The time a new request for service will wait is thereby reduced, and so is the real-time response of the system.

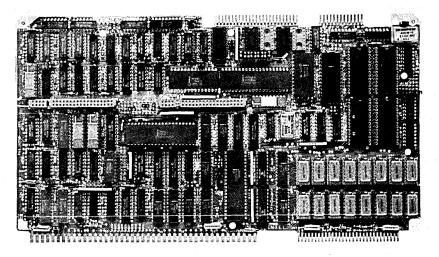

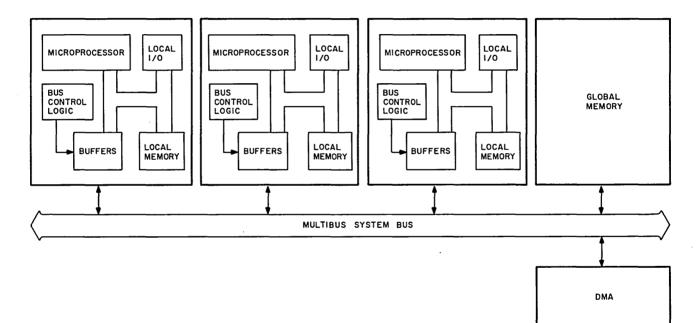

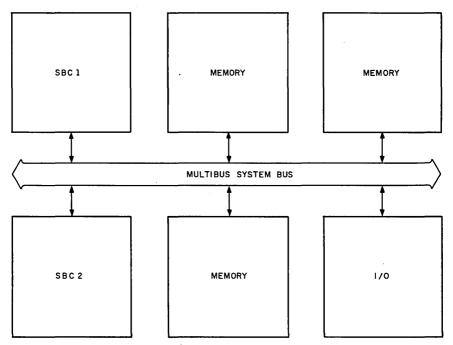

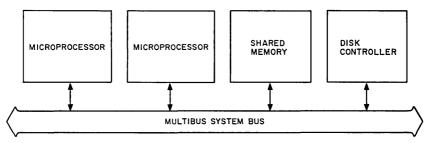

A simple definition of multicomputing is the use of multiple microprocessors that are capable of independent instruction execution and are able to communicate with each other over some local interconnection mechanism. The system is statically partitioned in that each microprocessor does a predetermined task. The processing units can be heterogeneous or homogeneous. A multicomputing system may have some shared resources, but that is not a requirement. The key is that the processing units' tasks are independent and require little interunit communication. A basic multicomputing configuration is shown in Fig. 1-6.

Using SBCs in a multicomputing system moves the bus activity from the system bus to the SBCs' local bus; this reduces the bandwidth needed on the system bus. The local execution of a program on an SBC becomes very important in multicomputing applications, since the different SBCs can execute their programs without using the Multibus system bus as long as all their code is located in local memory. Thus, providing true parallel processing with all microprocessors operating independently is possible with SBCs. The reduced system bus demand permits additional microprocessors (SBCs) to be added to the system and thereby increases overall system throughput.

FIGURE 1-6 A heterogeneous multicomputing configuration.

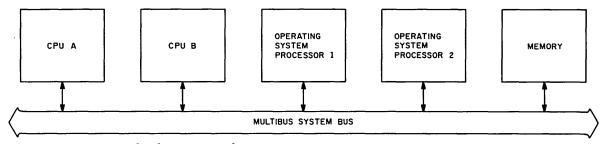

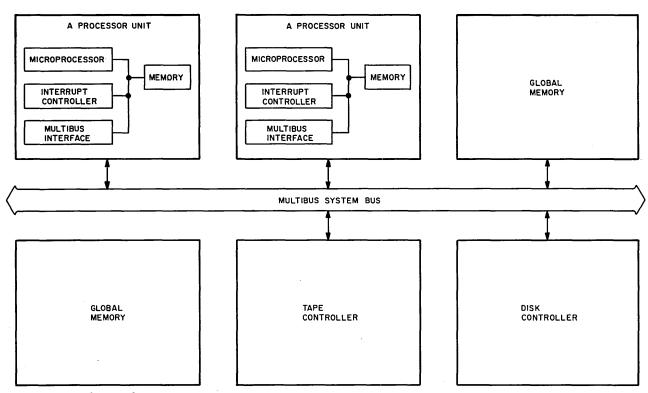

Similar to multicomputing is multiprocessing, which is defined as the use of multiple homogeneous microprocessors that are capable of independent instruction execution, are able to communicate with each other over some interconnection mechanism, and have shared memory and I/O. All the microprocessors in the system have exactly the same available resources. The coupling between the processing units is much tighter. The System is dynamically partitioned in that each microprocessor is assigned a task on a next-available-microprocessor basis. This must be done in such a way that the process is invisible to the user code being executed. A basic multiprocessor configuration is shown in Fig. 1-7.

In a common-bus architecture, adding more microprocessors to the system, as in multiprocessing systems, eventually causes the system bus to become saturated. When microprocessors are added to an already saturated system bus, each microprocessor must wait longer to gain access to the system bus, so the performance of each of the modules decreases. The net effect is lower total system throughput. A well-planned multiple microprocessor system bus structure will allow new microprocessors to be added to the system in a modular fashion. When new system functions, such as more peripherals, are added to the system, more processing power can be applied to handle them without affecting existing processor performance. This is a result of having extra system bus bandwidth as in the case of a multiprocessor system (needed to support another microprocessor executing on the system bus), or, in a multicomputing system, having enough bandwidth to support the communication and data transfer needs of the additional microprocessor. In addition, the bus structure must provide a communication path for microprocessors to signal each other.

Multiprocessing and multicomputing are supported on the Multibus system bus. Two to sixteen microprocessors (bus masters) are supported on the same system bus. Each of these microprocessors can be homogeneous or heterogeneous: one an 8-bit, another a 16-bit, one running at 1 MHz, and another at 16 MHz. Another aspect of heterogeneity is that the resources available to each microprocessor are different. The Multibus system bus also provides an arbitration and bus control exchange method that guarantees that a bus master can access the system without another master obtaining it, and it provides several reliable communication methods between bus masters through common resources such as memory and I/O.

Advances in semiconductor technology have driven the cost of microprocessors down to the point at which peripherals are the most expensive resources in the system. To design for maximum efficiency and economy, the designer must keep the expensive peripherals highly utilized. It is possible to do so only if multiple microprocessors are using the peripherals. The point can best be seen with an example. A system with an 8-in hard disk, a floppy disk, 512K bytes of RAM, and a single-user operating system running on one central processing unit (CPU) costs from \$5000 to \$10,000. The peripherals (the hard and floppy disks) and the packaging (the box, power supply, and cables) represent over 80 percent of the system cost. Adding a second microprocessor and a multiuser oper-

FIGURE 1-7 A multiprocessor configuration.

ating system to the system could roughly result in doubling throughput with only a 5-percent cost increase.

# 1.2.2 A Conceptually Simple Structure

A system bus structure must be easy to learn and use, and at the same time it must be flexible in order to support a wide range of applications. Documentation is a very important aspect of "easy to use"; it must be well structured to help the user understand the bus system. It must be broken down to give the user a step-by-step building-block approach to learning the system bus structure. Application examples of how to use the bus also are very helpful. They can give the user practical experience with the bus structure without having to actually build a prototype. An experienced board designer should be able to understand a new structure in a few hours and design a simple board within a few days after reading the bus specifications.

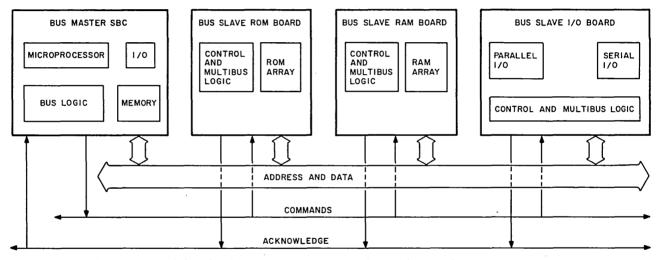

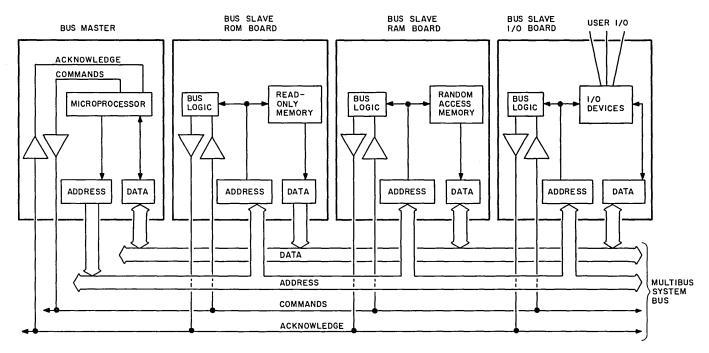

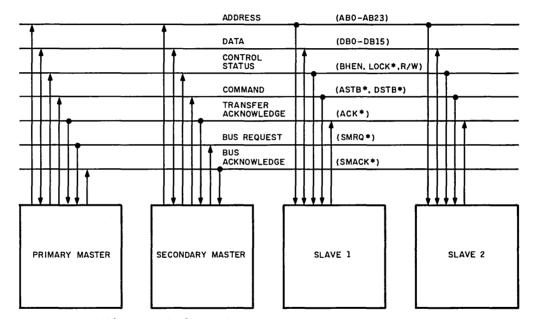

The Multibus system bus is an asynchronous parallel bus which can be divided into five signal categories: a 24-line address bus, a 16-line bidirectional data bus, eight multilevel interrupt lines, control and timing lines, and power distribution lines. The system bus operates on a master-slave principle. Figure 1-8 shows a typical bus master and some typical bus slaves. The bus master controls the system bus and starts all operations. Bus slaves respond to commands put on the system bus by the bus master. The bus master is interlocked to the bus slave module in that the bus master first issues a command and then must wait for an acknowledgment from the receiving bus slave module before continuing. This interlocking mechanism permits bus slave modules of different speeds to be on the same system bus, since each individual bus slave controls the amount of time it waits before responding with the acknowledgment.

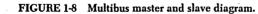

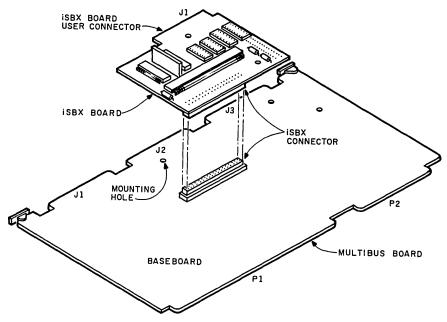

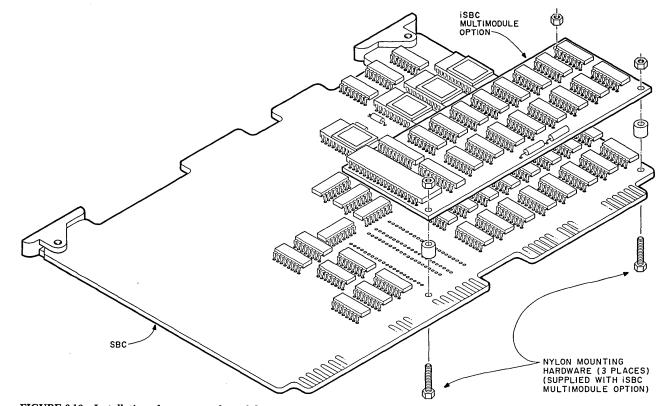

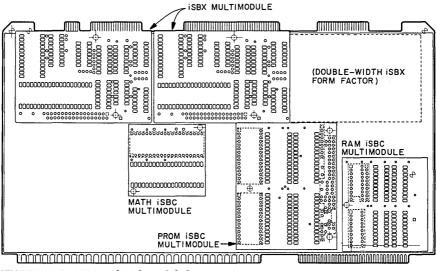

The iSBX concept allows the designer to inexpensively customize standard cost-effective Multibus-compatible boards (or any other board) with particular I/O features. This is done with small  $(2.85 \times 3.7 \text{ in}; 7.24 \times 9.4 \text{ cm})$  I/O modules called iSBX Multimodule boards. They are specialized I/O boards which plug piggyback style onto a variety of baseboards (Fig. 1-9) and thereby provide very low cost local I/O functional expansion. The concept is optimized around VLSI technology and small increments of I/O expansion. The iSBX boards are connected to the baseboard's local bus via the iSBX bus interface, and they convert the iSBX bus signals to a defined I/O function. The iSBX Multimodule boards enable the user to configure exactly the capabilities required for the system, which keeps both system size and cost at minimum levels. Since the I/O expansion is local, no system bus bandwidth is required.

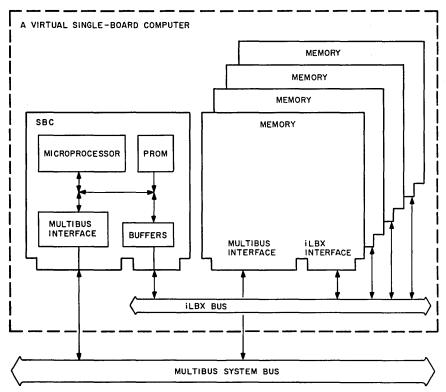

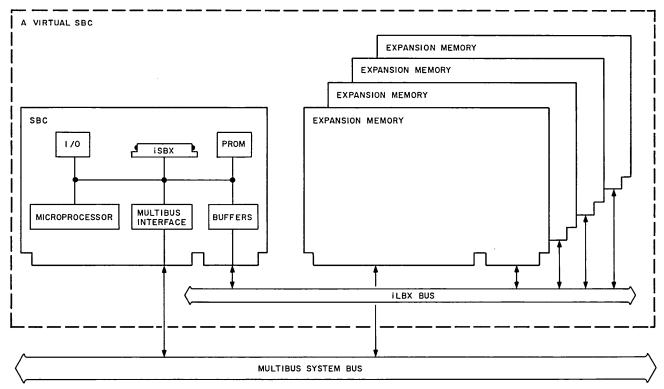

By providing a standard high-speed, tightly coupled connection between the microprocessor and its memory on another board, the iLBX bus permits the expansion of an SBC's local memory in a modular manner (without using the Multibus system bus) beyond what can fit on an SBC. The iLBX bus is opti-

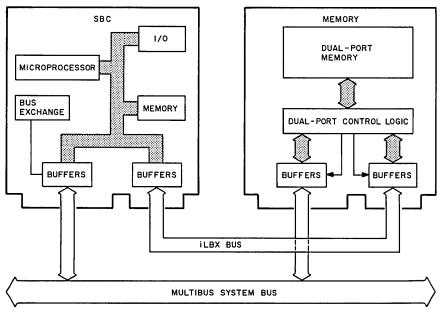

â

FIGURE 1-9 The iSBX Multimodule board concept.

mized for high-speed memory access. It supports two types of data transfer: a noninterlocked mode for maximum performance and an interlocked mode to support slower memory modules. The bus structure is built upon the master-slave principle, whereby the bus master (the SBC) places address and commands on the bus and the slave board (the memory module) decodes and acts on the command. This private bus between the microprocessor and the memory frees the Multibus system bus for DMA or other bus master traffic. Figure 1-10 is a block diagram of an SBC and a memory board connected via the iLBX bus.

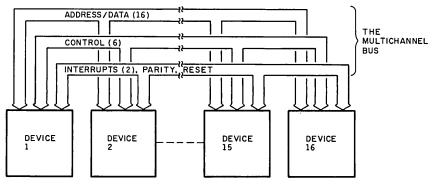

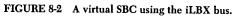

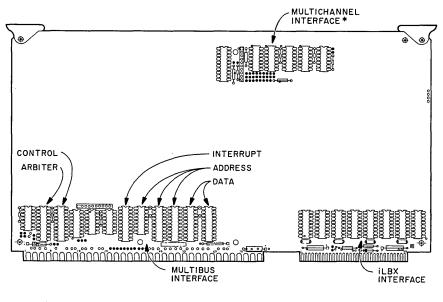

The Multichannel bus provides a standard high-speed (8M bytes per second) block-oriented gateway into and out of a Multibus-based system. By utilizing a standard interface, the bus allows multiple heterogeneous devices such as different high-speed I/O and memory modules to be connected together. Figure 1-11 is a simplified block diagram of a Multichannel system. The bus structure is an asynchronous parallel bus built upon the master-slave principle with interlocked 8- and 16-bit data transfers. The Multichannel bus has the ability to link together up to 16 devices that are distributed over a distance of up to 50 ft (15 m) via a twisted pair flat ribbon cable. It has addressing capability of up to 16M bytes of memory and 16M bytes of I/O space on each bus device. Figure 1-12 shows Intel's iSBC 589, a high-speed intelligent DMA controller, which connects the Multibus system bus to the Multichannel bus. The 60-pin connector on the top of the board is the Multichannel bus connector.

Another important feature of both the Multibus structure and the Multi-

channel bus is the ability to put multiple master modules on the same bus for multiprocessing configurations. A method is defined to transfer control of the bus between master modules, and it guarantees that only one bus master controls the bus at a given time. Both buses also support priority interrupts. This capability permits bus modules to request interruption of normal activity and have a special event serviced by the master microprocessor.

FIGURE 1-10 The iLBX memory expansion bus concept.

FIGURE 1-11 The Multichannel bus block diagram.

FIGURE 1-12 Multibus board with a multichannel interface.

# 1.2.3 A Structure That Can Incorporate New VLSI Quickly

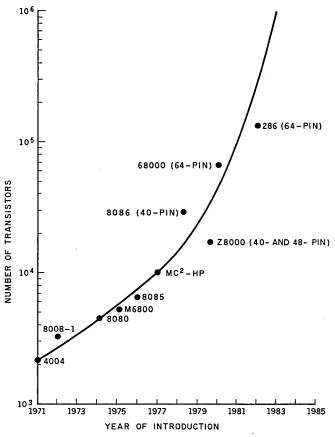

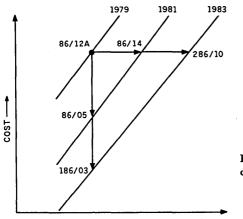

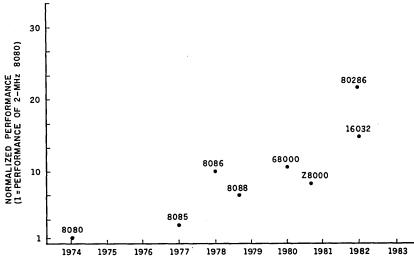

Advances in VLSI technology have resulted in performance and complexity doubling every 2 to 3 years (Fig. 1-13). As an example, Intel Corporation's 8008 microprocessor, introduced in 1972, had a 30- $\mu$ s average instruction execution time and was able to address a maximum of 16K bytes of memory. In 1982, Intel introduced the iAPX 80286 microprocessor, which has an average instruction time of less than 1  $\mu$ s and is capable of addressing a maximum of 16M bytes of memory. This technology explosion presents the system designer with the opportunity to design systems that have lower cost, higher performance, increased density, and greater reliability. But it also means quick obsolescence for systems that are not designed to permit the incorporation of future generations of VLSI components. The system designer has the challenge of creating competitive systems that can easily assimilate successive generations of VLSI technology.

Historically, new VLSI components required new system designs, especially for new microprocessors. Designers would implement new system boxes each time a new microprocessor was introduced, which meant completely new memory, I/O, and microprocessor board designs. The new designs were dedicated to supporting only a few functions with very basic and limited I/O. There was very little flexibility in the design to handle future VLSI technology or new peripherals without a major redesign. It became clear that a universal system box was needed; it would permit the use of previously designed memory and peripheral modules. From this exercise came the Multibus system bus, the first standard microprocessor system bus, and its family members: the iSBX bus, the Multichannel bus, and the iLBX bus.

In this age of rapid technological change, the use of standard system structures helps designers to quickly incorporate new VLSI technology into both new and old designs. They do so by tying the new VLSI devices to solid universal interfaces which are the gateway to all system resources such as memory and peripherals. The system must be developed in a functionally partitioned manner. Each of the functional units may be designed with the best technology available for that particular task and to interface to the system bus standard. When future generations of VLSI devices permit it, a superior replacement functional unit can be designed provided it meets the interface standard. Since the interface remains unchanged, the new unit can replace the old one and minimize the impact it has on the other functional units in the system.

FIGURE 1-13 Chart of VLSI density versus time.

Success in adapting future VLSI devices to microprocessor-based systems is measured by the effectiveness of the system's organization in alleviating the highly irregular structures of past and present microprocessors. The key lies in so defining the system bus structure that it is decoupled from any particular VLSI device. It must be architecture-independent; that is, it must be flexible enough to support many different families of VLSI devices. It should not have special signals that only one device supports. However, the interface must be similar to typical VLSI component interfaces to minimize the extra transistortransistor logic (TTL) required to convert the component interface to the universal interface. The board designer can design the VLSI device to the universal bus interface provided the new device has the ability to communicate quickly and easily with the rest of the system.

As an example, let us examine a three-board system: a CPU board based on a 5-MHz Z80,<sup>5</sup> a memory board, and a disk controller board. Assume that in the next design, a new CPU board is needed to get higher performance. The system designer needs to have the freedom to build an 8-MHz 80286-based CPU board. A properly defined bus structure would permit this new microprocessor board, which operates 10 times faster, to replace the old microprocessor board without affecting the rest of the system. The memory and disk controller boards would not have to be modified or replaced.

Another goal of a bus structure must be longevity. One way to achieve longevity is to support many different types of microprocessors and other VLSI devices over a 10- to 15-year lifespan. This requires that the bus structure support generic microprocessor attributes such as memory address space, I/O address space, some form of mutual exclusion, interrupts, different widths of address and data lines, and multiple-bus master-control capability. The bus must also be independent of microprocessor, memory, and I/O device speed.

The Multibus system bus provides a very basic set of generic functions which support a wide range of microprocessor families. Two data path widths permit the use of both 8- and 16-bit microprocessors. That includes a very wide range of 8-bit microprocessors such as 8080, Z80, 6800, and 8088. In the 16-bit world, there are Multibus-based SBCs with 8-MHz 80286s, 8-MHz 68000s, and 8-MHz Z8000s. Addressing is flexible; it permits the choice of 64K bytes, 1M byte, or 16M bytes of memory address space. Separate I/O address space, which can be either a 256K- or a 65K-byte location, is also supported.

In applications in which the microprocessor requires more bandwidth from the system bus than it can deliver, the iLBX bus provides an alternative. Microprocessor memory bandwidth needs have increased at a greater rate than memory subsystems have. The system bus which connects the two modules together can easily become the bottleneck. One solution is to use two buses in the system:

<sup>&</sup>lt;sup>5</sup>Z80 is a trademark of Zilog Corporation, Cupertino, California.

one bus for execution (which must be very tightly coupled to the microprocessor-memory subsystem pair) and a second bus for system communication and data movement. The iLBX bus provides this tightly coupled connection. The iLBX bus expands the local memory of the SBC, saving system bus bandwidth and supporting multicomputing architectures that require multiple SBCs with more memory than can fit on a single board.

# 1.2.4 A Reliable, Cost-Effective Structure

The most important aspects of a bus structure's basic cost are the form factor and interface costs. The cost of a module is generally proportional to module area. For a given area of PCB there is a minimum established cost; it is the cost of a two-layer PCB plus the system bus interface and some minimal circuitry. The complexity of implementing the system bus interface is proportional to the board area occupied. Smaller form factors cannot support extensive system bus features because of the additional circuitry required. The bus interface logic should occupy only 10 to 20 percent of the PCB area. Thus, in applications with minimal computer requirements a bus standard with a small board area should be chosen. Ideally, the form factor would support just enough components to accomplish the task at hand and future upgrades. The boards should be small enough for easy and inexpensive replacement in the field. That also makes repairs simple and fast.

If the form factor is too small, designers may run into problems in implementing reasonable functions in the system on a single board. Often the designer must resort to numerous board-to-board interconnections. Small board size may result in a greater than 20 percent board area to implement the bus interface. That leaves less space to implement the required function. A larger board has more area for interface logic, which in turn makes room for more complex functions to be supported. For applications which require a lot of computer power it is necessary to choose a bus standard with a larger form factor. The upper limit of the board size is typically limited by power-to-ground and signal-noise considerations. A standard Multibus board can safely handle 30 to 40 W of 5-V power. The limiting factor is the voltage drop across the P1 connection, which becomes too large. It subtracts from the voltage margin of the components on the board, which reduces the reliability of the board. Other factors that limit board size are (1) the envelope of the enclosure in which the board is used and (2) the warpage of the board, which can become severe.

The Multibus system bus provides solutions to a wide range of microprocessor-based systems. The form factor is small enough to be cost-effective in lowdensity designs and large enough to support a wide range of functions on a single board. At the low end, the VLSI support has reduced the bus interface logic to 10 percent of the board area. The Multibus system bus is also modular, which permits low-end designs to implement only part of the total bus capability and yet still operate with other Multibus boards. This leaves most of the board area available to accomplish the function of the design on a low-density two-layer circuit board. At the high end, a single Multibus board can accommodate a basic computer system consisting of a 16-bit microprocessor, nine interrupts, 24 parallel I/O lines, an RS-232 serial channel, 128K bytes of ROM capacity, and 512K bytes of RAM.

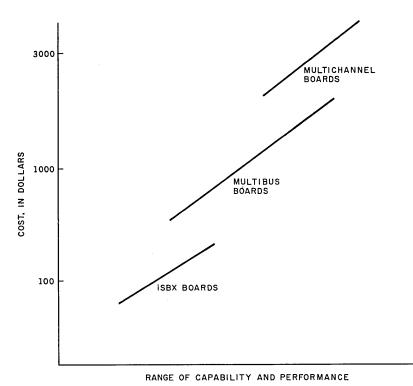

There are three options for I/O expansion: a Multibus module, an iSBX Multimodule board, and a Multichannel module, each with a different cost, performance, and capability range (Fig. 1-14). The iSBX Multimodule board provides the lowest-cost expansion for small increments of local I/O capacity. The iSBX Multimodule board is small (10.5 in<sup>2</sup>; 26.7 cm<sup>2</sup>), which keeps costs low. The interface was so designed that very little or no interface logic is required on the iSBX Multimodule board, so almost all the PCB area (typically >90 percent) can be used to implement the desired I/O function. An example of an iSBX Multimodule board is a serial communication module which has one or two complete serial channels. A Multibus module provides more flexibility and capacity, as well as global accessibility, but at a higher cost because of the

FIGURE 1-14 Multibus family I/O expansion flexibility.

greater PCB area (81 in<sup>2</sup>; 522.6 cm<sup>2</sup>) and the greater bus interface cost of implementing more complex functions. An example of a Multibus I/O board is a communication module with eight complete serial channels and a microprocessor with memory. The maximum data rates into and out of the board are limited by the Multibus lines (about 1M bytes per second). If more bandwidth is required, the Multichannel bus can be used; it provides up to 8M bytes per second transfer rates.

## 1.2.5 A Well-Defined, Documented, and Controlled Standard

The bus structure must be very well defined so multiple-board designers can design boards that will operate together on the system bus. Each signal must be documented and explained so clearly that there is no room for user misinterpretation. This includes signal definition, timing and loading requirements, and application examples. The signals in the system must cross a multiplicity of physical interfaces between the microprocessor and memory or I/O, including the system bus. Careful consideration must be given to these interfaces—solder connections, wire-wrap connections, and plug-in card connections—if they are to meet long-term-reliability goals. In addition, there must be limits on the physical dimensions of the system bus modules to permit construction of economical packaging systems to house the modules. All of this must be properly documented in a publicly available specification.

The specification must be properly controlled by an accepted authority in the industry. This controlling body has the responsibility to maintain and make updates and extensions to the bus specification. The changes and extensions must be so implemented that they support all old designs that met the earlier specification. The adoption of standards results in connectability, portability, and interchangeability of the different products designed to meet that standard. This protects the investment in many of the board designs when the boards are used in newer and more powerful systems. A custom I/O board can be used in two or three generations of systems, which saves time and development expense. This is a very important aspect of the evolution of a system bus to a solid and reliable foundation for system designs for years to come.

Developed standardized industrial buses used to build a microprocessorbased system provide a proven, reliable foundation. They are implemented by experienced designers who take into account very important electrical attributes, such as bus length, ground-plane effects, line reflections, ringing, noise coupling, signal skew, and connector reliability, that could easily be overlooked in a new bus design. Also, standardized industrial buses have been thoroughly tested and have demonstrated long-term reliability in field applications.

The Multibus/IEEE-796 bus set the standard for what a well-defined bus structure should be. It was first defined by Intel in the Multibus specification and later refined by the Institute of Electrical and Electronics Engineers (IEEE), Standards Committee in the form of the IEEE-796 bus standard. The iSBX bus is following a similar path. The initial definition, by Intel, was later updated by the IEEE Standards Committee in the form of the IEEE-P959 standard. Both specifications were written to define all operations completely; no user interpretation is required. In 1984, just 9 years after the introduction of the Multibus system bus, more than 120 different vendors were making more than 2000 compatible products. After only 3 years following the introduction of the iSBX bus, six vendors were making 35 different iSBX-compatible products. This is an indication of the popularity and quality of the specifications. The IEEE standardization efforts on both the IEEE-796 and IEEE-P959 will help assure the user community that the compatibility and high commercial quality of these buses will be maintained. The result is bus-compatible products from different manufacturers that will operate together reliably. The Multichannel and iLBX buses also have controlling specifications available to the general public. They were written with the same basic goals of the Multibus and iSBX specifications and will most likely follow the same standardization path.

The Multibus system bus and its other family members are very popular, and buyer's guides for them are available. The *Multibus Buyers Guide* is published semiannually by Ironoak Company (La Jolla, California). The *Buyers Guide* lists all the Multibus-family-compatible board-level products currently available. This publication provides the system designer, original equipment manufacturer (OEM) integrators, and manufacturers with a survey of the entire market.

The Multibus family of structures has been the basis of many designs in many different applications and environments from controlling bank teller machines to controlling steel mills. During the first 5 years of Multibus availability, more than 100,000 systems were shipped. This training ground has resulted in a proven and reliable bus structure.

#### **1.3** BRIEF HISTORY OF THE IEEE-796/MULTIBUS AND ITS EXTENSIONS

The Multibus system bus was originally developed at Intel Corporation in 1975 by the company's microprocessor systems group. The first product in which the new standard system bus was used was the group's Microcomputer Development System, the Intellec 800,<sup>6</sup> which provided design engineers with the software and hardware tools needed to implement microprocessor-based designs. The system architecture was a simple split-bus approach (Fig. 1-15). In addition to using the development system to implement their projects, some customers built custom boards and incorporated all of the boards into their own boxes. Intel Corporation then distributed the Multibus system bus specification to give

<sup>&</sup>lt;sup>6</sup>Intellec is a trademark of Intel Corporation, Santa Clara, California.

FIGURE 1-15 Split-bus architecture.

other vendors the basis for building Multibus-compatible products. The original Multibus structure supported only 8-bit transfers and 16 address lines.

Intel perceived the need for board-level solutions. In 1976 it provided the first commercially available SBC, the iSBC 80/10, that integrated on a single PCB a microprocessor, memory, and I/O. This new iSBC product line was based on the Multibus system bus, and it was the first Multibus-compatible board with a complete microprocessor system on a single board. The product line was very successful, and hundreds of competitive and complementary products followed from Intel Corporation and other vendors. All these products were compatible with the commercial-quality Multibus because of the effective documentation of the Multibus specification, which was made available by Intel Corporation and later by the IEEE Standards Committee with the IEEE-796 bus specification.

In 1977 the first silicon support for the bus was developed. Intel's 8218 and 8219 bipolar Multibus system bus controller for MCS-80 and MCS-85 families reduced the PCB area required to support the bus exchange logic and command generation from 5 in<sup>2</sup> (32.26 cm<sup>2</sup>) to 1 in<sup>2</sup> (6.45 cm<sup>2</sup>), which reduced the dollar cost of the Multibus interface. These chips contain all the control logic required by a bus master to interface with other masters on the Multibus system bus and share memory and I/O. They permit any designer to implement the bus

exchange logic and command generation with a proven, reliable method and thereby reduce the possibility of design errors. The bus structure was extended in 1978 to dynamically support both 8- and 16-bit devices. The Multibus system bus became the first microprocessor bus to permit both 8- and 16-bit devices to communicate with each other over the system bus. These evolutionary extensions made it possible for the Multibus system bus to support a new generation of 16-bit microprocessors and increased the useful lifespan of the bus as an industry standard.

In 1978 the Task 796 Working Group of the IEEE Computer Society's Microprocessor Standards Committee was set up to standardize the Multibus system bus. The 796 bus specification has its roots in Intel's Multibus system bus. Intel's specification was reviewed and refined by representatives from many different companies throughout the industry. During the standardization task some minor bus modifications were incorporated and improvements in documentation were made. One of the modifications was to extend the address bus to support 16M bytes by providing 24 address lines. The IEEE Standards Committee serves as a single point of control, which ensures that the specification of the bus will not change. A solid specification which does not change assures that products built by different vendors will be compatible. And, finally, the IEEE Standards Committee puts the specification into the public domain. The standardization work was completed in December 1982.

The iSBX bus was originally developed at Intel in 1979 by the OEM Microcomputer Systems Operation (OMO) group in Hillsboro, Oregon, to extend the SBC architecture with low-cost local I/O expansion. The concept was accepted immediately, and multiple vendors started producing iSBX Multimodule-compatible boards. In 1982 the IEEE Computer Society's Microprocessor Standards Committee was formed to standardize the iSBX bus. The Multichannel and iLBX buses were developed by Intel Corporation in 1982 by the OMO group.

# The Multibus System Bus

This chapter provides the basis for a conceptual understanding of the Multibus system bus. Included in it are the logical description of the functions of the bus and a detailed look at the electrical and mechanical specifications. The information in it was based on the Intel Multibus Specification (9800683-03) dated April 1981 and the Microcomputer System Bus Standard (796 bus) dated October 1980. It is recommended that anyone designing on the Multibus system bus obtain the latest versions of those specifications from Intel Corporation.

### 2.1 NOTATION

In this section, as well as throughout the book, a consistent notation for signals has been followed, and the memory read command (MRDC) will be used to explain it. The terms "true-false" and "one-zero" can be ambiguous and will be avoided. We will use the terms "electrical high (H)" and "low (L)." A slash or an asterisk following the signal name, as in MRDC\*, indicates that the signal is active-low. For example,

$MRDC* = MRDC = MRDC = \overline{MRDC} = asserted at 0 V$

Table 2-1 further explains the notation used in this book.

During the Multibus system bus standardization work by the IEEE Standards Committee, which produced the IEEE-796 bus specification, two basic notation standards were used. They differed from those of the original bus specification by Intel in two ways: (1) the change from the slash (/) to denote an active-low signal to an asterisk (\*) and (2) the use of decimal instead of hexadecimal notation. For example, in the original Multibus specification DAT0/ to DATF/ represented the 16 data lines; in the new IEEE-796 specification DAT0\* to

| Signal<br>name | Definition      |                                             |                   |                              |

|----------------|-----------------|---------------------------------------------|-------------------|------------------------------|

|                | Label           | Electrical                                  | Logical           | State                        |

| IORC           | H High<br>L Low |                                             | 1 True<br>0 False | Active, asserted<br>Inactive |

| IORC*          | L Low<br>H High | $\leq +0.8 \text{ V}$ $\geq +2.0 \text{ V}$ | 1 True<br>0 False | Active, asserted<br>Inactive |

TABLE 2-1

Notation Summary

DAT15\* is used to represent them. In the original IEEE-796 specification hexadecimal notation was used, and it is to be converted to decimal notation over a 5-year period. By 1987 decimal notation must be used in all IEEE-796-compatible documentation. This chapter uses the notation of the IEEE-796 specification, which is hexadecimal, and an asterisk (\*) to indicate an active-low signal. The other specifications in this book use decimal and asterisk notation. Readers will encounter the variant forms of notation on some figures and tables, and should be aware of their meaning and validity.

Also, these numeric conventions will be followed: to indicate decimal notation, (1) the letter D will follow the number (e.g., 120D) or (2) a number without any following letter will be assumed to be decimal. Binary numbers will be followed by the letter B (e.g., 10001110B), and hexadecimal numbers will be followed by the letter H (e.g., 10BDH).

#### 2.2 LOGICAL DESCRIPTION OF THE MULTIBUS SYSTEM BUS

The Multibus system bus is a commercial-quality bus used in microprocessorbased systems. The bus supports both 8- and 16-bit data paths in the same system, and it can be configured to support up to 16M bytes of memory address space and 64K bytes of I/O address space. Multiple masters are supported with up to 16 bus masters. The basic command protocol of the bus is asynchronous (the bus masters and bus slaves can operate with independent clocks) and interlocked, and all bus cycles require a positive acknowledgment from the bus slave before the bus master can continue. The maximum bus transfer rate is 5 megawords per second.

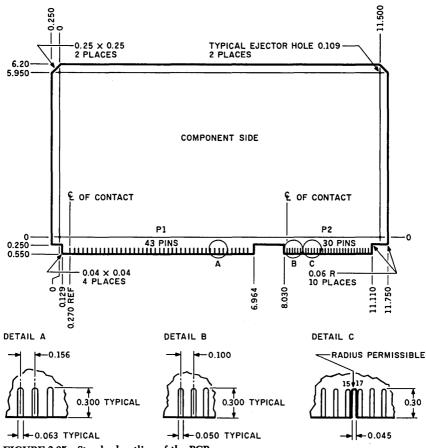

A Multibus-compatible board measures  $6.75 \times 12.00$  in  $(17.5 \times 30.48 \text{ cm})$ . The Multibus interface consists of two edge card connectors, P1 and P2. The P1 connector has 86 pins and handles the regulated +5-, +12-, and -12-V power, the 8- and 16-bit data bus, 20 bits of addressing (1M byte), the bus control lines, and the bus arbitration lines. The P2 connector has 60 pins and is used for the upper four address lines (16M bytes) and the iLBX bus. The iLBX bus is a high-speed memory execution bus used to expand the local memory capacity of an SBC without using the Multibus system bus. The iLBX bus is discussed in more detail in Chap. 5.

# 2.2.1 Bus Devices

There are three basic types of elements that interface with the Multibus system bus: bus masters, bus slaves, and bus hybrid modules.

#### **BUS MASTERS**

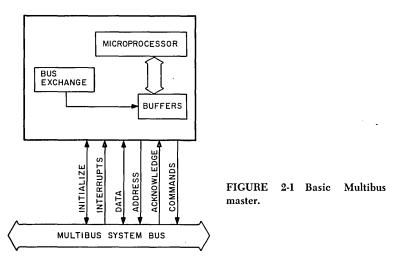

A bus master is any module that can control the bus and initiate data transfers. The Multibus system bus supports up to 16 bus masters on the same system bus. Control of the bus is passed from one bus master to another through its bus exchange logic. Any one of these 16 bus masters can make a data transfer by (1) requesting control of the bus through its bus exchange logic, (2) aquiring the bus once it is granted access, and (3) driving the command and address lines to perform data transfers. Figure 2-1 is a block diagram of a basic bus master, which consists of a microprocessor, bus exchange logic, and data-address buffers. A more complex master, a typical SBC bus master, is shown in Fig. 2-2. The SBC also includes its own memory and I/O logic. Typical bus masters are CPU modules, SBC modules, disk controller modules, and DMA controllers. All bus masters either process or move data in the system.

#### **BUS SLAVES**

A bus slave is any module that can respond to bus commands generated by a bus master. It can control only three parts of the bus: (1) the interrupt lines when generating interrupts, (2) the data lines when performing a read command, and (3) the acknowledge line. Bus slaves simply decode the address and command information on the system bus and perform the requested operation and acknowledge the master once the operation is completed. Memory and I/O expansion modules are examples of typical bus slaves; they are low-cost vehicles that extend the system capabilities by providing data storage or I/O capability to the system. Some bus slaves are shown in Fig. 2-3.

FIGURE 2-2 Block diagram of a typical SBC bus master.

#### HYBRID MODULES

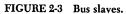

A hybrid module has all the attributes of a bus master and most of the attributes of a bus slave on one module. Like a bus master, it can control the bus, and it has resources that can be used by other bus masters. The latter make it look like a bus slave to the other bus masters. Figure 2-4 shows two hybrid modules. The first one is an SBC with dual-port memory, which is memory which can be accessed by the microprocessor on that module, as if it were a private resource, and by another bus master via the Multibus system bus. The dual-port memory is both a local resource, which can be accessed by the local microprocessor without using the system bus, and a global resource, which is accessible to all bus masters. The second hybrid is a simple combination of a memory module and a bus master on one board. Each of the functions, however, is logically independent.

Hybrid modules are an outgrowth of the VLSI explosion; today an entire system can be built on one Multibus board. Some examples of hybrid modules are intelligent communication boards such as Interphase Corporation's LNC5180 Local Area Network Controller and SBCs such as Intel's iSBC<sup>1</sup> 86/ 30 board and National Semiconductor's BLC<sup>2</sup> 80/30 board. These boards are considered hybrid modules because they have (1) the ability to control the bus through their bus exchange logic and (2) the RAM that can be accessed from the system bus through their dual-port control logic.

<sup>1</sup>iSBC is a trademark of Intel Corporation, Santa Clara, California.

<sup>2</sup>BLC is a trademark of National Semiconductor Corporation, Santa Clara, California.

1

<u>د</u>

-

FIGURE 2-4 Hybrid Multibus modules.

-

# 2.3 BUS SIGNAL DEFINITIONS AND OPERATION OVERVIEW

In this section the signals that make up the bus are described, and basic Multibus operations are discussed. The Multibus system is composed of 90 signal lines that can be broken into several classes: address (25 bus lines), inhibit (2), data (16), control (9), interrupts (9), bus exchange (5), and power (24). The different classes are explained in the following sections.

# 2.3.1 Address, Inhibit, and Data Lines

The address, inhibit, and data lines can be broken down into four groups:

| Class        | Signal       | Function                                                    |  |

|--------------|--------------|-------------------------------------------------------------|--|

| Address      | ADR0*-ADR17* | Address lines (0–9, A–F, 10–<br>17) in hexadecimal notation |  |

| Byte control | BHEN*        | Byte high enable                                            |  |

| Inhibit      | INH1+-INH2+  | Inhibit 1 and 2                                             |  |

| Data         | DAT0*-DATF*  | Data lines 0 to F in hexadecimal notation                   |  |

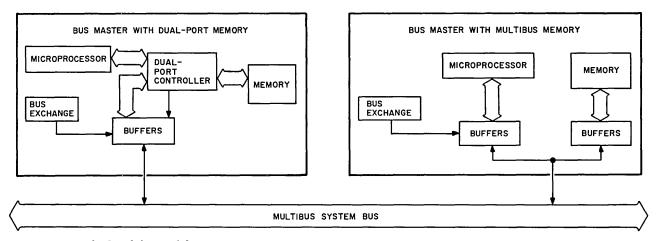

# ADDRESS

The 24 address lines ADR0\* to ADR17\* carry the binary address of the memory location or I/O device that the bus master is referencing. ADR0\* is the least significant bit of the address. The bus master indicates to the bus slaves which type of address (memory or I/O) is on the address lines by using the appropriate command line. The IORC\* and IOWC\* commands are used for I/O port accesses, and the MRDC\* and MWTC\* commands are used for memory accesses. The Multibus system bus supports many address ranges—three for memory modules and two for I/O modules. The three memory address ranges are those that address 16M bytes, those that address 1M byte, and those that address 64K bytes. The I/O address ranges are those that address 256 devices' addresses and those that address 64 kilodevices' addresses (see Fig. 2-5). These various ranges are discussed in Sec. 2.6. Different ranges are needed to support various microprocessors. The 8080 microprocessor can address only 64K bytes of memory and 256 I/O devices, whereas Intel's iAPX 80286 microprocessor can address 16M bytes of memory and 64K bytes of I/O devices.

All signals on the Multibus system bus are negative true; that is, the active state is low, and they are terminated with a pull-up resistor. These termination resistors cause all signals which are not driven to be in the inactive (high) state. If a bus slave looks at the address bus and no bus master is driving it, the bus slave reads an address of 000000H. This permits a memory board (a bus slave) to decode all 24 address bits and still respond to a microprocessor that can generate only 16 address bits. In this case all the nondriven address lines will be in the inactive state. (ADRX\* = high, so the upper eight address lines ADR10\*

FIGURE 2-5 Multibus address line usage.

to ADR17\* will be decoded as TTL low.) Thus if an 8080 microprocessor were to generate a memory read command of location 1000H (hexadecimal), the address on the system bus as seen by the memory board would be 001000H. The microprocessor module would drive ADR0\* to ADRF\*, and the termination resistor would drive ADR10\* to ADR17\*.

### BYTE HIGH ENABLE

Byte high enable (BHEN\*) is used to select the upper byte (DAT8\* to DATF\*) of a 16-bit word. BHEN\* is used only in 16-bit systems. It is an extension of the address bus that supports 8-bit-byte operations on 16-bit words.

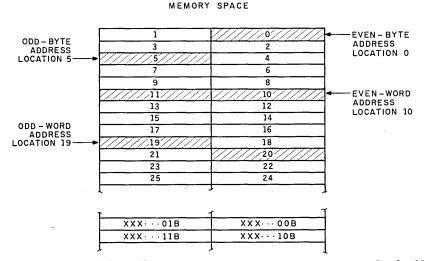

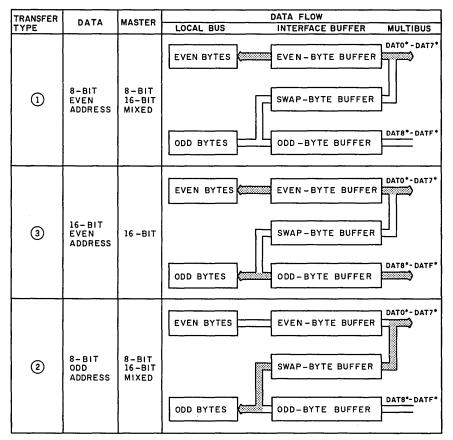

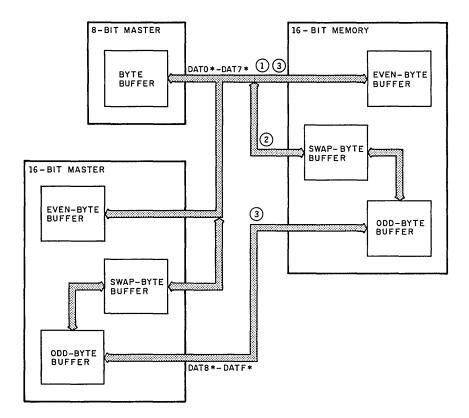

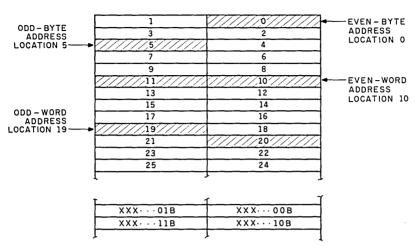

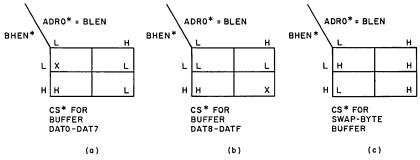

The Multibus structure supports both byte and word addressing (see Fig. 2-6). A byte location is the smallest addressable unit of storage. There are two types of byte address locations: an even-byte address (ADR0\* = high) and an odd-byte address (ADR0\* = low). Two consecutive byte locations form a word. The Multibus structure can transfer a word only if the first byte location of the word is an even address (ADR0\* = high). If the first byte location of the word is an odd address (ADR0\* = low), the bus master must perform two byte accesses and assemble the word.

A bus master accesses a byte on the system bus by placing the binary address (even or odd) on the address lines and driving BHEN\* = high (inactive). Access

to a word location is gained by placing the binary address on the address lines with ADR0\* = high (an even address) and BHEN\* = low (active). Again, word access on odd-address boundaries must be divided into two byte bus accesses, and the bus master must reassemble the word. This is summarized below:

|             | BHEN* = low | BHEN* = high     |

|-------------|-------------|------------------|

| ADR0 = low  | Reserved    | Odd-byte access  |

| ADR0 = high | Word access | Even-byte access |

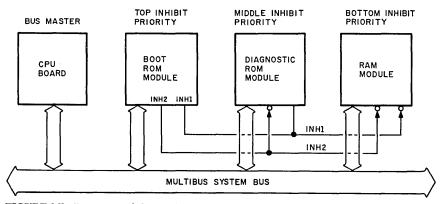

#### INHIBIT

Inhibit INH1\* and INH2\* is used by a bus slave to hold off another bus slave's bus activity. This permits a bus slave (the inhibiting slave) to turn off another bus slave (the inhibited slave). The inhibit lines can be used during a memory read or memory write operation. The inhibit signal is generated by the inhibiting bus slave based on the bus address lines. If the address is in its address range, an inhibit signal is activated. Then the inhibited bus slave will disable all its drivers from the system bus (data and acknowledge) and may perform the operation internally (locally to the module). The inhibiting bus slave must not return its acknowledge until 1.5  $\mu$ s after the command is generated. This long

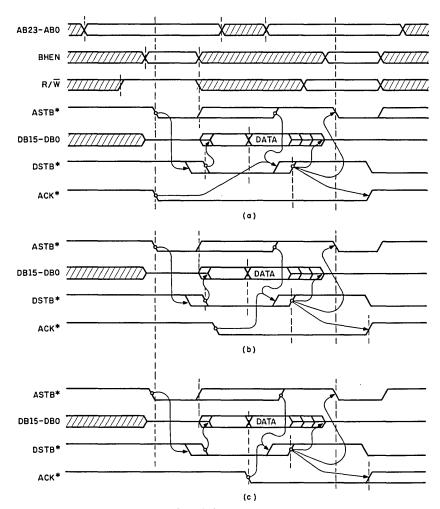

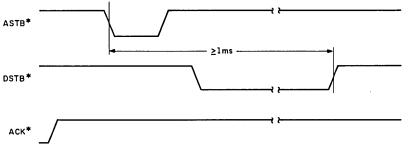

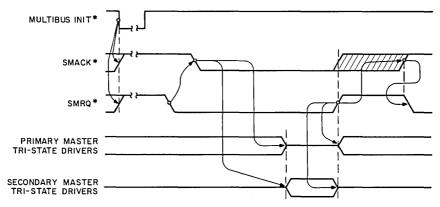

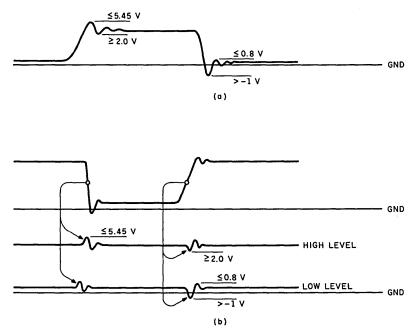

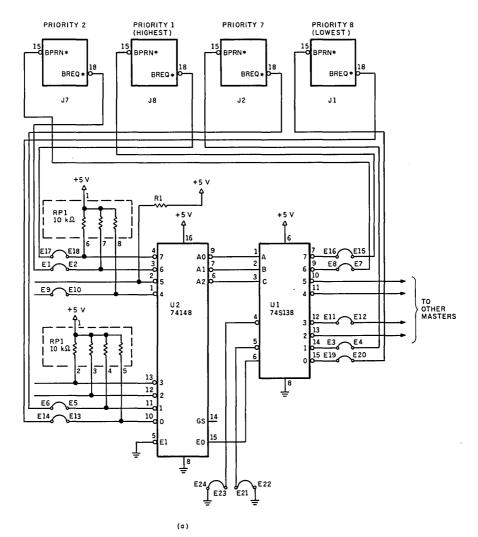

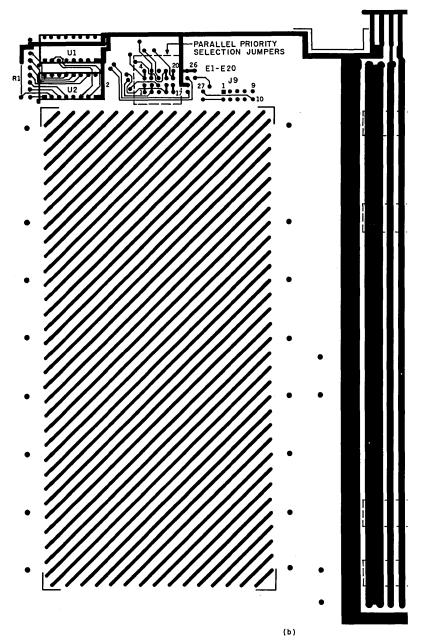

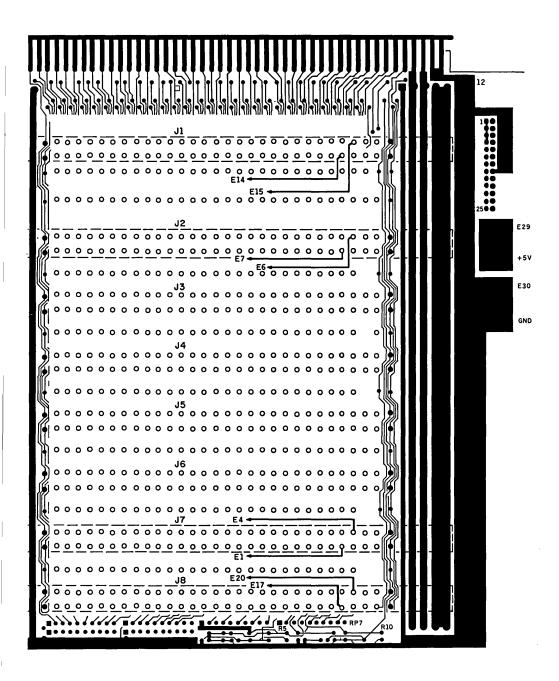

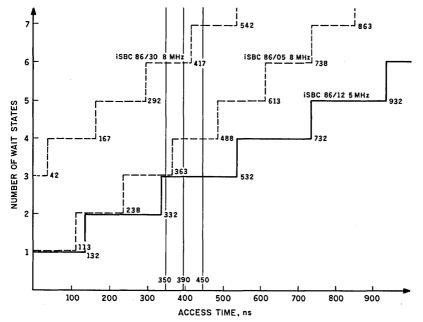

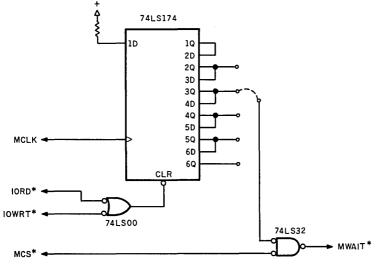

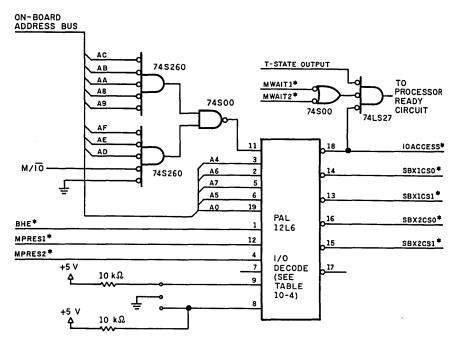

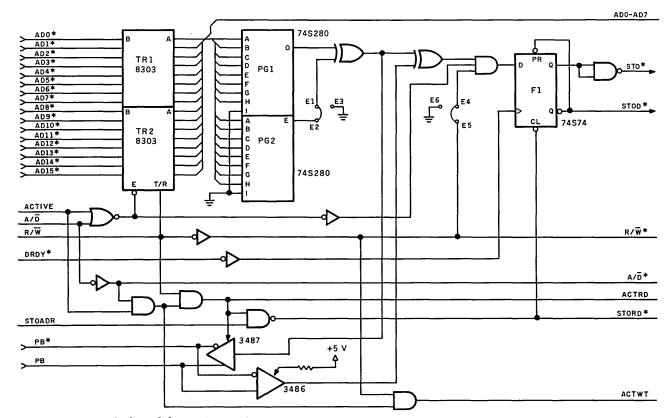

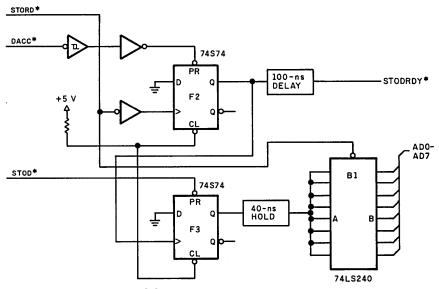

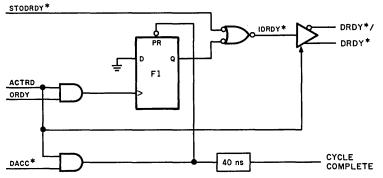

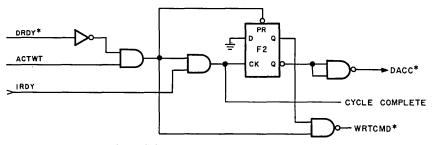

FIGURE 2-6 Multibus address memory mapping. (Note: Bus master must break oddword address access into two byte accesses and reform the word.) bus cycle is required to give all inhibited bus slaves enough time to return to a normal state, since an internal operation may have occurred.