FIELD ENGINEERING TECHNICAL MANUAL

SPD<sup>TM</sup> 10/20

STORED PROGRAM DISPLAY

FS 002

"This document contains information proprietary to INCOTERM Corporation and is delivered on the express condition that it is not to be disclosed, reproduced in whole or in part, or used for manufacture for anyone other than INCOTERM Corporation without its written consent, and that no right is granted to disclose or so use any information obtained in said document. This restriction does not limit the right to use information obtained from another source. "

SPDIM

Copyright C 1971 by INCOTERM Corporation, Marlboro, Mass.

# TABLE OF CONTENTS

| Chapter |      |           |                                             | Page |

|---------|------|-----------|---------------------------------------------|------|

| LIST    | OF 1 | ILLUSTRA  | TIONS                                       | ix   |

| LIST    | OF   | TABLES    |                                             | xi   |

| I       | INTF | RODUCTIC  | DN                                          | 1-1  |

|         | 1.1  | Scope     |                                             | 1-1  |

|         | 1.2  | General   | Specifications                              | 1-1  |

|         | 1.3  | Configur  | ation                                       | 1-1  |

|         |      | 1.3.1     | Minimum Configurations                      | 1-2  |

|         |      | 1.3.2     | Units Available for Expanded Configurations | 1-2  |

|         | 1.4  | Reference | ce Documents                                | 1-3  |

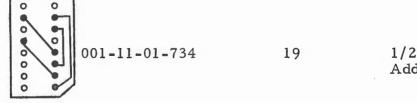

| II      | INST | ALLATIC   | N                                           | 2-1  |

|         | 2.1  | Visual In | nspection                                   | 2-1  |

|         | 2.2  | Configur  | ation Chart                                 | 2-3  |

|         | 2.3  | Site Pre  | paration                                    | 2-10 |

|         | 2.4  | Installat | ion                                         | 2-10 |

|         |      | 2.4.1     | Cabling of Product 005, Model 00010         | 2-10 |

|         |      | 2.4.2     | Cabling of Product 005, Model 00011         | 2-13 |

|         |      | 2.4.3     | Cabling of Product 005, Model 00014         | 2-13 |

| III     | OPE  | RATION    |                                             | 3-1  |

|         | 3.1  | General   | Information                                 | 3-1  |

|         | 3.2  | Keyboar   | d                                           | 3-1  |

|         |      | 3.2.1     | Introduction                                | 3-1  |

|         |      | 3. 2. 2   | Key Functions                               | 3-2  |

|         |      | 3.2.3     | Indicator Functions                         | 3-6  |

|         | 3.3  | Initial T | urn On and Check Out                        | 3-6  |

|         |      | 3.3.1     | Initial Turn On Procedures and Indications  | 3-6  |

|         |      | 3.3.2     | Programmed Operation                        | 3-7  |

| IV      | SYST | TEM DES   | CRIPTION                                    | 4-1  |

|         | 4.1  | Introduc  | tion                                        | 4-1  |

|         | 4.2  | System 1  | Functional Description                      | 4-1  |

# TABLE OF CONTENTS (Cont.)

| Chapter |     |         |                                   | Page |

|---------|-----|---------|-----------------------------------|------|

|         |     | 4.2.1   | General Information               | 4-1  |

|         |     | 4.2.2   | Terminal Processing Unit          | 4-3  |

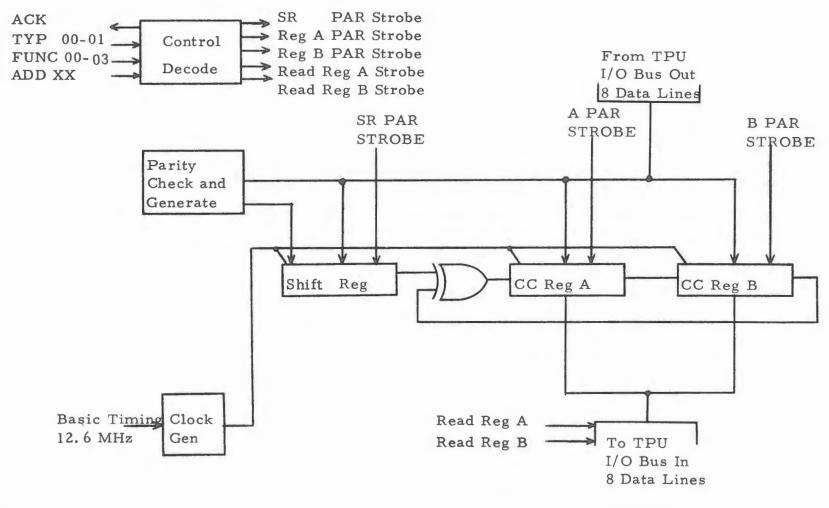

|         |     | 4.2.3   | Interface Control                 | 4-6  |

|         | 4.3 | Address | sing and Instruction Formats      | 4-7  |

|         |     | 4.3.1   | Introduction                      | 4-7  |

|         |     | 4.3.2   | Hexadecimal Notation              | 4-8  |

|         |     | 4.3.3   | Word Formats                      | 4-9  |

|         |     | 4.3.4   | Instruction Classes               | 4-10 |

|         |     | 4.3.5   | Effective Address Calculation     | 4-11 |

|         |     | 4.3.6   | Basic System Timing and Data Flow | 4-14 |

| v       | THE | ORY OF  | OPERATION                         | 5-1  |

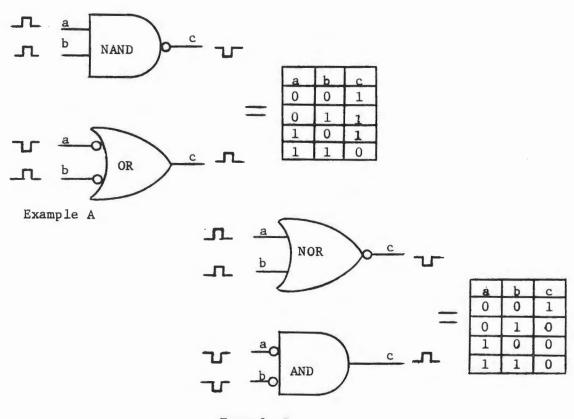

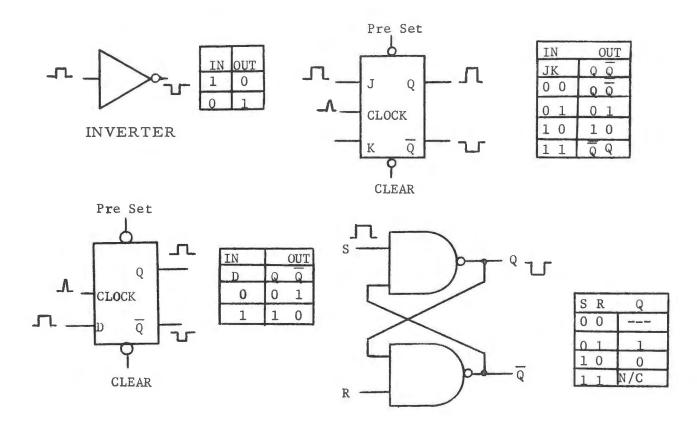

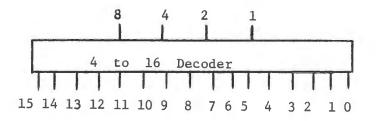

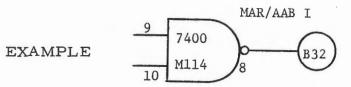

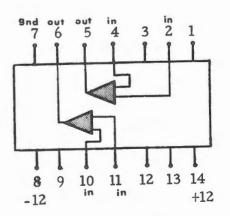

|         | 5.1 | Logic U | Jtilized                          | 5-1  |

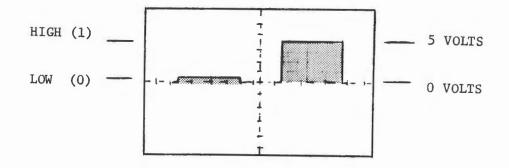

|         |     | 5.1.1   | Logic Levels                      | 5-1  |

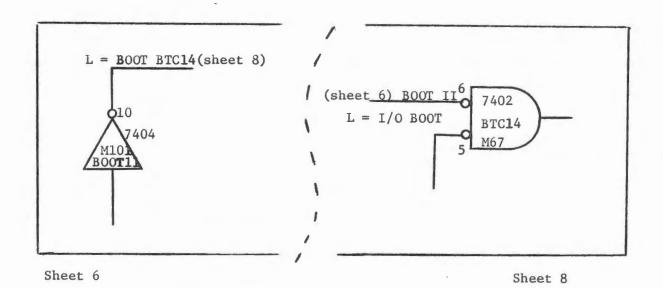

|         |     | 5.1.2   | Schematic Interpretation          | 5-5  |

|         | 5.2 | Data Fl | ow Electronics                    | 5-8  |

|         |     | 5.2.1   | Introduction                      | 5-8  |

|         |     | 5.2.2   | General Discussion of Data Flow   | 5-9  |

|         |     | 5.2.3   | Bus System                        | 5-12 |

|         |     | 5.2.4   | Memory Address Register           | 5-12 |

|         |     | 5.2.5   | Arithmetic Unit Adder             | 5-13 |

|         |     | 5.2.6   | Arithmetic Unit Bus               | 5-13 |

|         | \$  | 5.2.7   | Auxiliary Arithmetic Unit         | 5-13 |

|         |     | 5.2.8   | Character Register                | 5-15 |

|         |     | 5.2.9   | Line Register                     | 5-16 |

|         |     | 5.2.10  | Accumulator Register              | 5-16 |

|         |     | 5.2.11  | Condition Store Register          | 5-17 |

|         |     | 5.2.12  | Program Counter Register          | 5-17 |

|         |     | 5.2.13  | Test Comparator                   | 5-18 |

|         |     | 5.2.14  | Bus Enable Decoders for the MDR   | 5-18 |

|         |     | 5.2.15  | Memory Data Register              | 5-19 |

|         |     | 5.2.16  | Memory Data Bus Drivers           | 5-20 |

# TABLE OF CONTENTS (Cont.)

| Chapter |     |         |                                                            | Page |

|---------|-----|---------|------------------------------------------------------------|------|

|         |     | 5.2.17  | Exclusive-Or Unit                                          | 5-20 |

|         |     | 5.2.18  | TPU Register-Clock Drivers                                 | 5-21 |

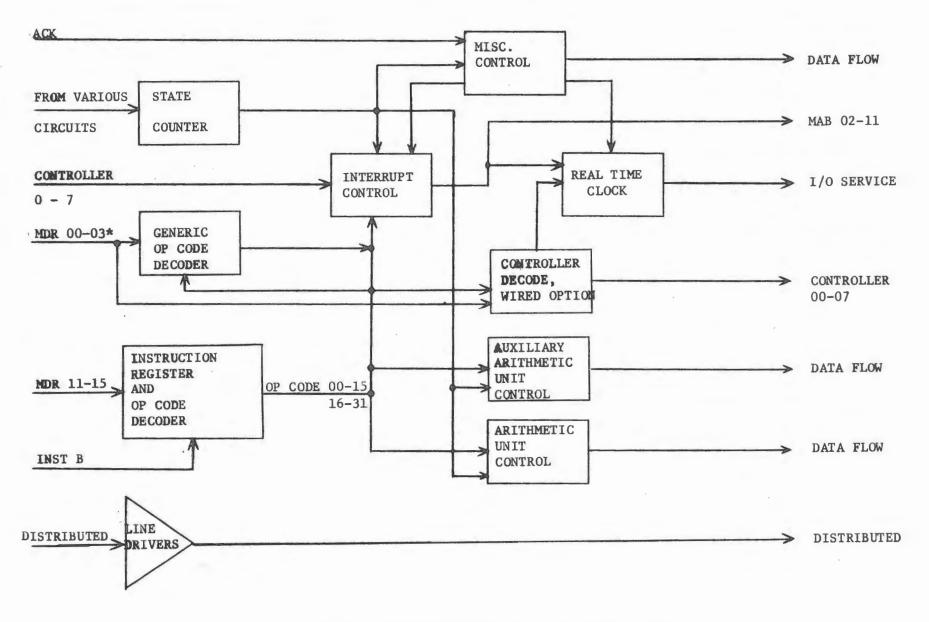

|         | 5.3 | Data Co | ntrol Electronics                                          | 5-21 |

|         |     | 5.3.1   | General Information                                        | 5-21 |

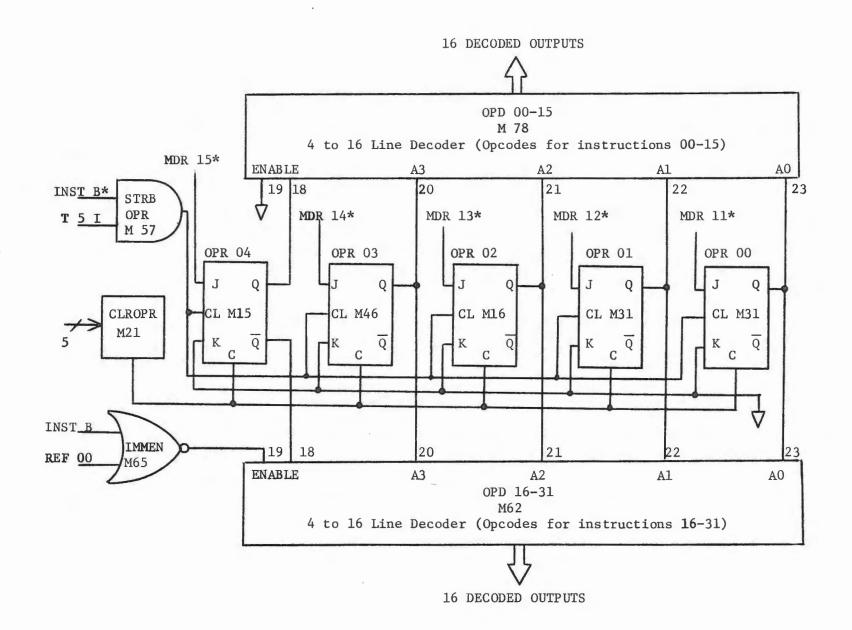

|         |     | 5.3.2   | Instruction Register and Decoder                           | 5-25 |

|         |     | 5.3.3   | Generic Opcode Decoder                                     | 5-26 |

|         |     | 5.3.4   | Miscellaneous Control Functions                            | 5-27 |

|         |     | 5.3.5   | State Counter                                              | 5-35 |

|         |     | 5.3.6   | Auxiliary Arithmetic Unit                                  | 5-39 |

|         |     | 5.3.7   | Arithmetic Unit Control                                    | 5-43 |

|         |     | 5.3.8   | Real Time Clock Module                                     | 5-45 |

|         |     | 5.3.9   | Interrupt Controls                                         | 5-46 |

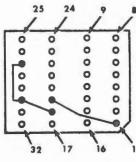

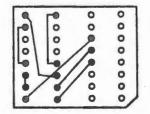

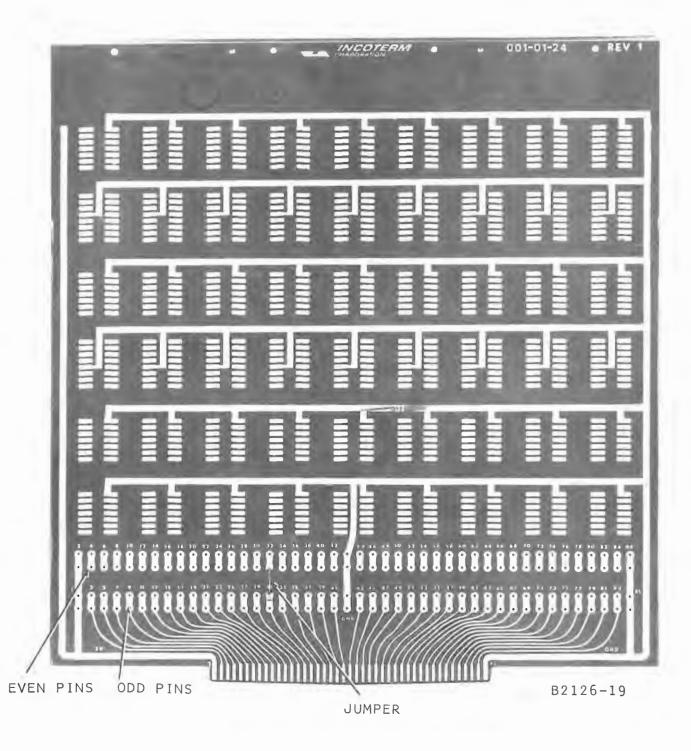

|         |     | 5.3.10  | Controller Decoder and Wired Option Matrix                 | 5-48 |

|         |     | 5.3.11  | Control Line Drivers                                       | 5-49 |

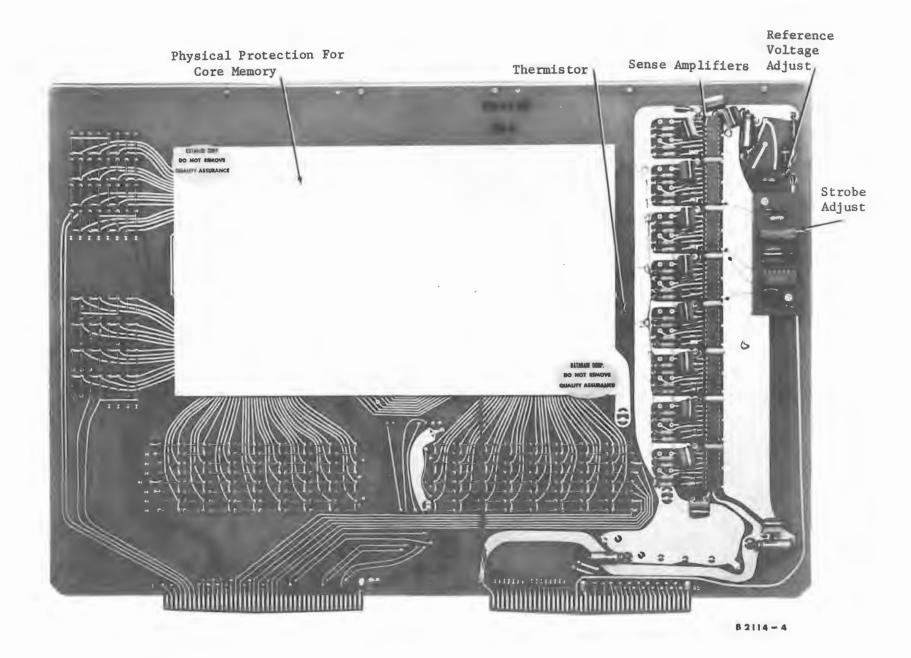

|         | 5.4 | Memory  | Electronics                                                | 5-49 |

|         |     | 5.4.1   | Introduction                                               | 5-49 |

|         |     | 5.4.2   | General Discussion of Memory<br>Organization and Operation | 5-49 |

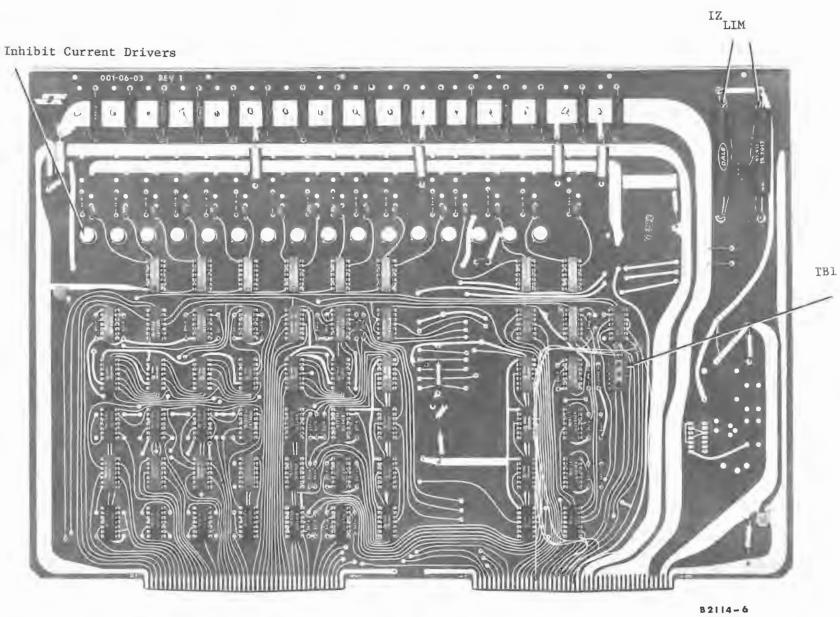

|         |     | 5.4.3   | X and Y Drivers and Associated Logic                       | 5-54 |

|         |     | 5.4.4   | Inhibit Logic and Drivers                                  | 5-57 |

|         |     | 5.4.5   | Memory Stack Sense Electronics                             | 5-58 |

|         |     | 5.4.6   | Memory Sense Logic                                         | 5-60 |

|         | 5.5 | Timing  | and Refresh Electronics                                    | 5-61 |

|         |     | 5.5.1   | Introduction                                               | 5-61 |

|         |     | 5.5.2   | 20-Phase Clock Timing Unit                                 | 5-64 |

|         |     | 5.5.3   | Control, Start and Last Line Control                       | 5-65 |

|         |     | 5.5.4   | Line Computation Logic                                     | 5-66 |

|         |     | 5.5.5   | Character Code Translator                                  | 5-66 |

|         |     | 5.5.6   | Refresh Video Circuit                                      | 5-67 |

|         |     | 5.5.7   | Read-Only-Memory and Input Logic                           | 5-68 |

|         |     | 5.5.8   | ROM Data Buffer                                            | 5-70 |

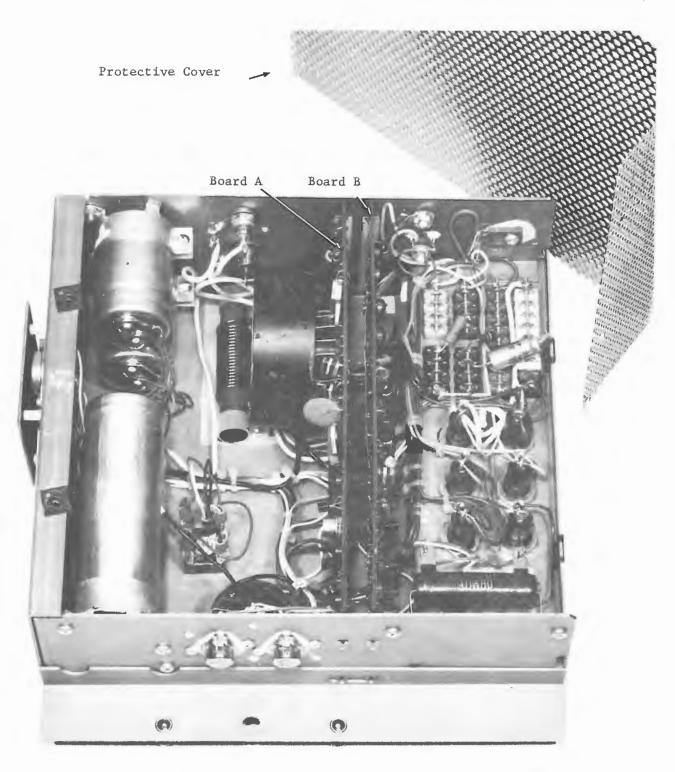

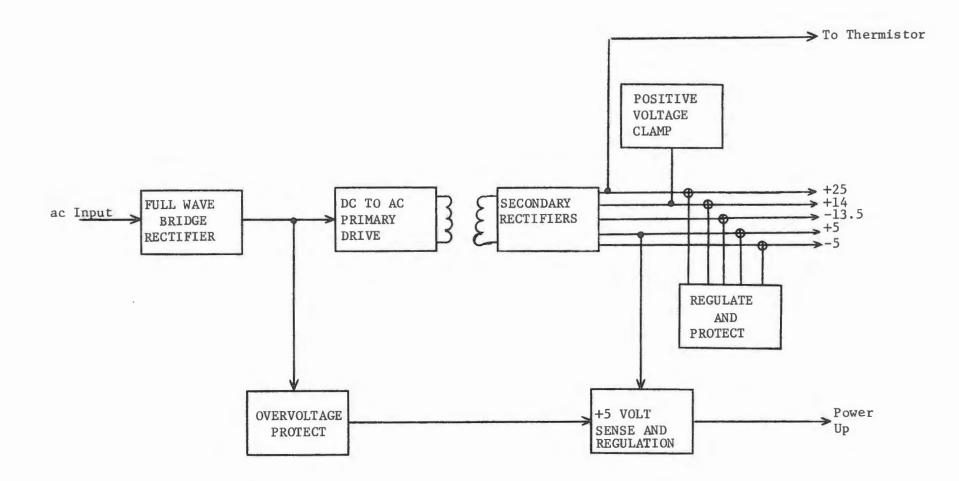

|         | 5.6 | High Ef | ficiency Power Supply                                      | 5-71 |

|         |     | 5.6.1   | Operation                                                  | 5-74 |

| Chapter |      |          |                                                      | Page |

|---------|------|----------|------------------------------------------------------|------|

|         |      | 5.6.2    | Operation                                            | 5-74 |

|         |      | 5.6.3    | Regulation                                           | 5-74 |

|         |      | 5.6.4    | Typical Checks                                       | 5-75 |

|         | 5.7  | Line Lo  | ock Oscillator                                       | 5-76 |

| VI      | INPU | JT/OUTI  | PUT INTERFACE CONTROL                                | 6-1  |

|         | 6.1  | Input/C  | Output System                                        | 6-1  |

|         | 6.2  | Keyboa   | rd                                                   | 6-1  |

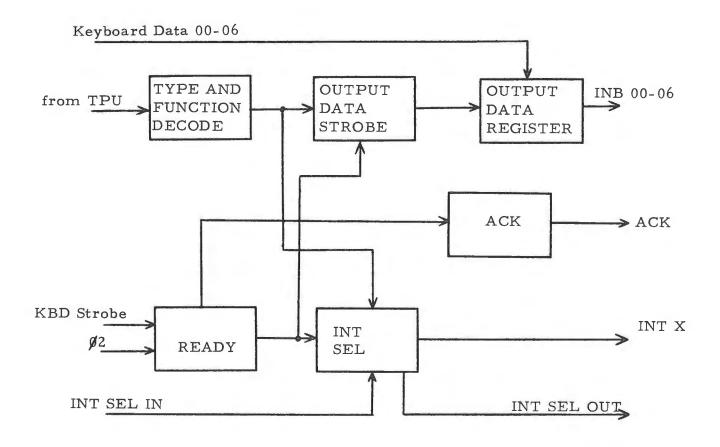

|         | 6.3  | Keyboa   | rd Controller                                        | 6-5  |

|         |      | 6.3.1    | Introduction                                         | 6-5  |

|         |      | 6.3.2    | Input/Output Data                                    | 6-5  |

|         |      | 6.3.3    | Control Logic                                        | 6-9  |

|         | 6.4  | Asynch   | ronous Controller                                    | 6-11 |

|         |      | 6.4.1    | General                                              | 6-11 |

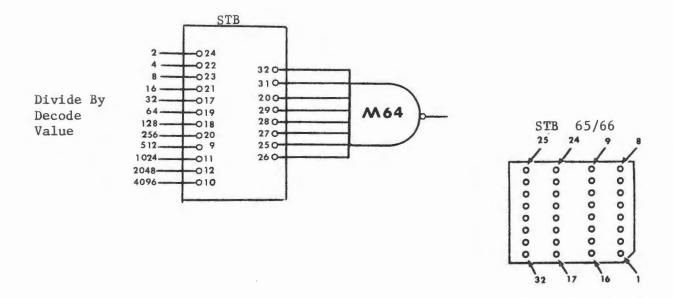

|         |      | 6.4.2    | Timing Circuits                                      | 6-20 |

|         |      | 6.4.3    | Input/Output Commands                                | 6-21 |

|         |      | 6.4.4    | Write Mode                                           | 6-22 |

|         |      | 6.4.5    | Read Mode                                            | 6-23 |

|         |      | 6.4.6    | Boot Mode                                            | 6-24 |

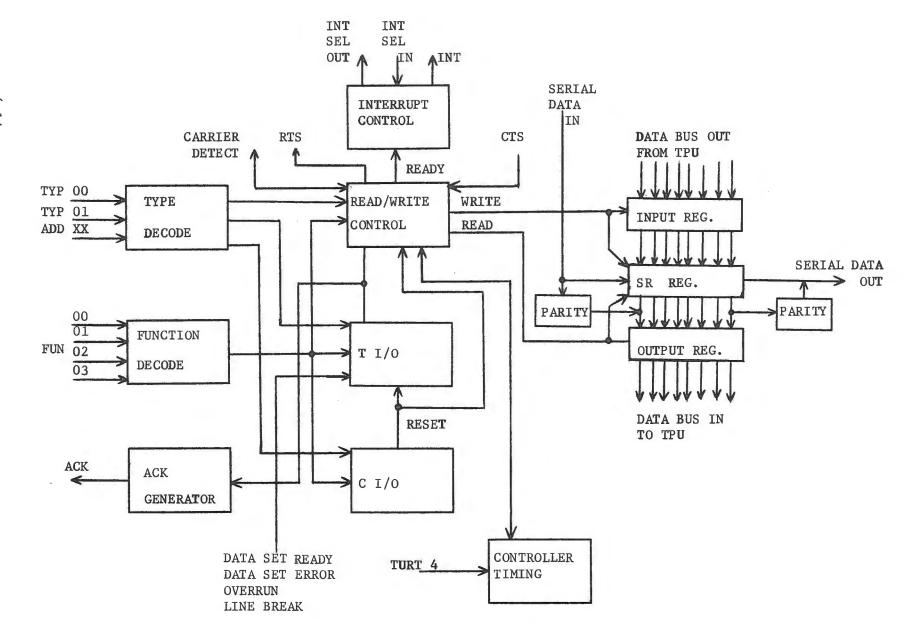

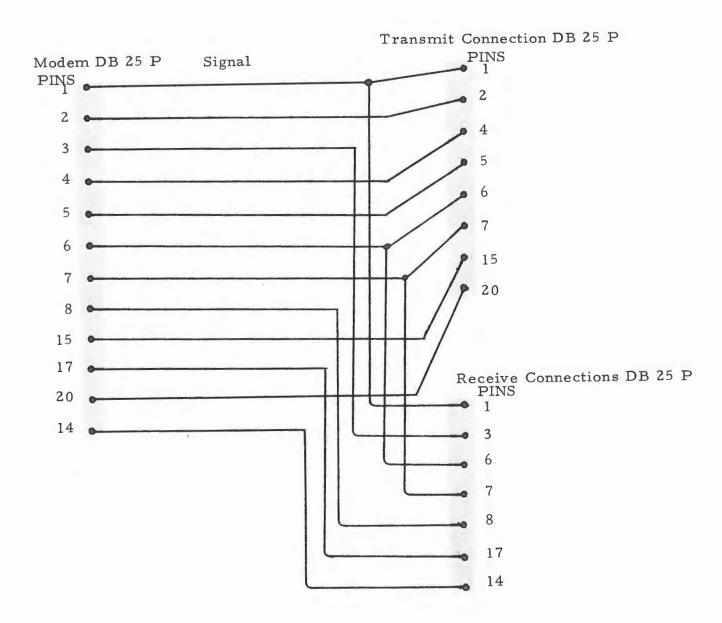

|         | 6.5  | Synchro  | onous Controller                                     | 6-24 |

|         |      | 6.5.1    | General                                              | 6-24 |

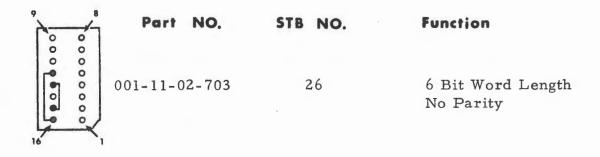

|         |      | 6.5.2    | Circuit Options                                      | 6-24 |

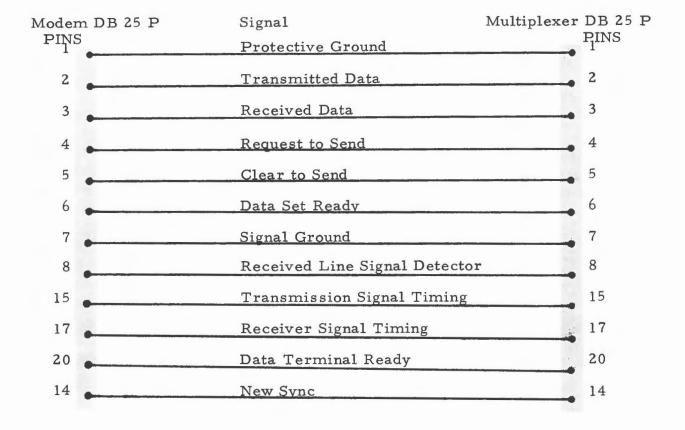

|         |      | 6.5.3    | TPU Control and Modem Interface                      | 6-26 |

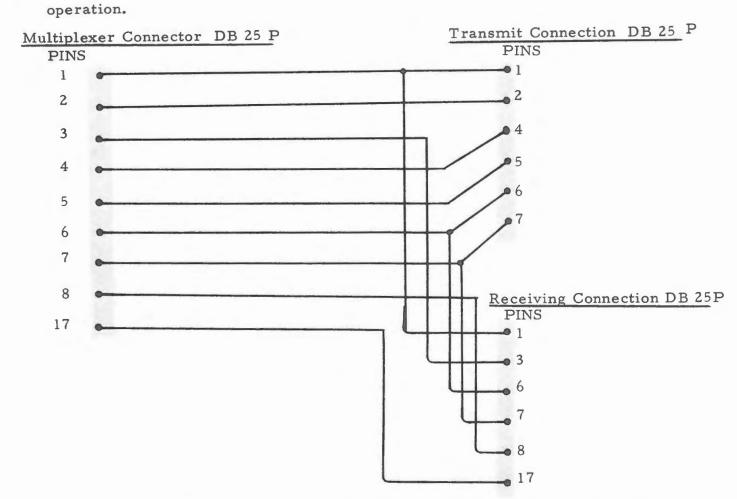

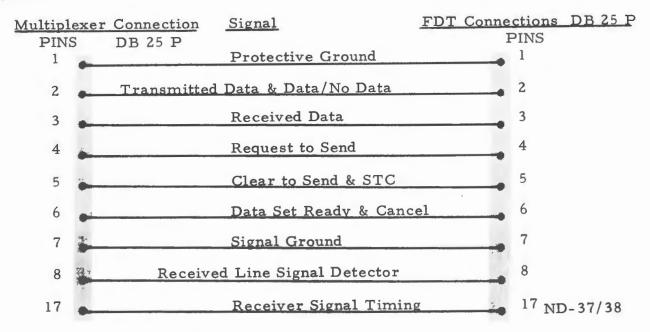

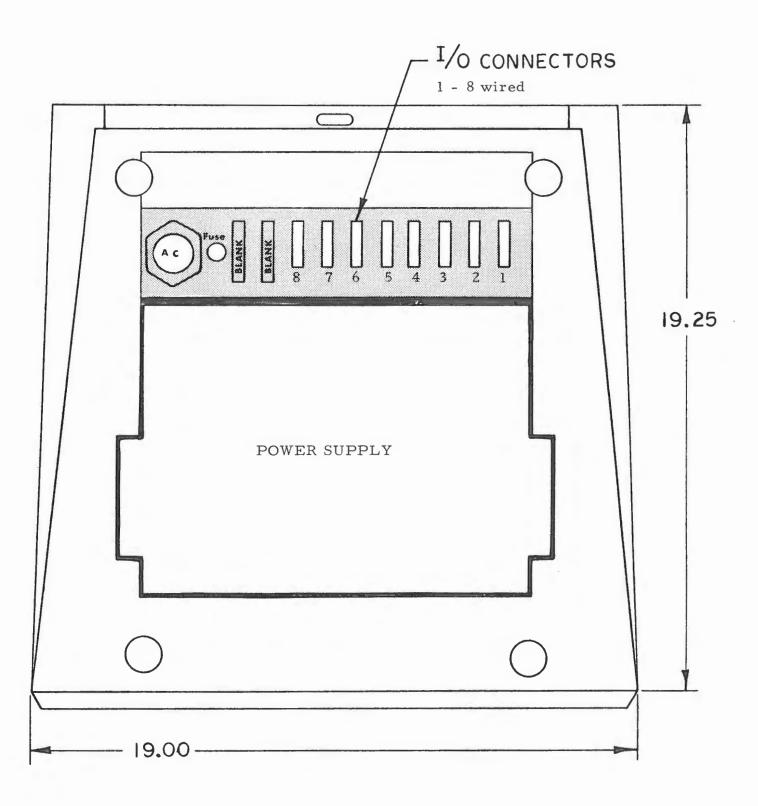

|         |      | 6.5.4    | Multiplexer Operation with Synchronous<br>Controller | 6-27 |

|         |      | 6.5.5    | Synchronous Operation in BOOT Mode                   | 6-27 |

|         |      | 6.5.6    | Basic Operation                                      | 6-28 |

|         | 6.6  | Split Sc | creen Controller                                     | 6-29 |

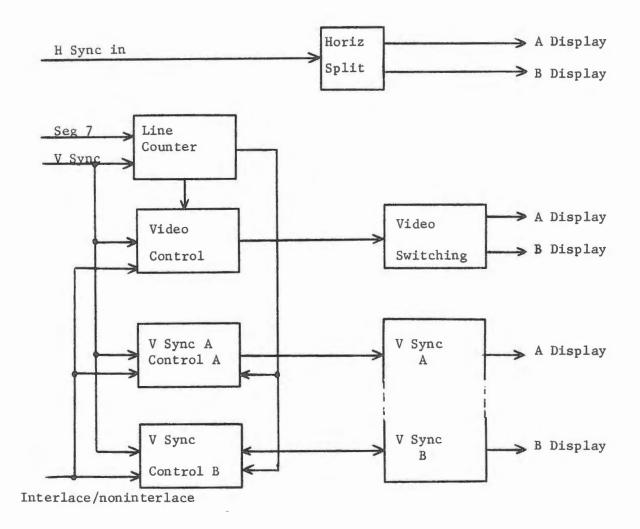

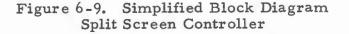

|         |      | 6.6.1    | Operation                                            | 6-33 |

|         | 6.7  | Boot Co  | ontroller                                            | 6-34 |

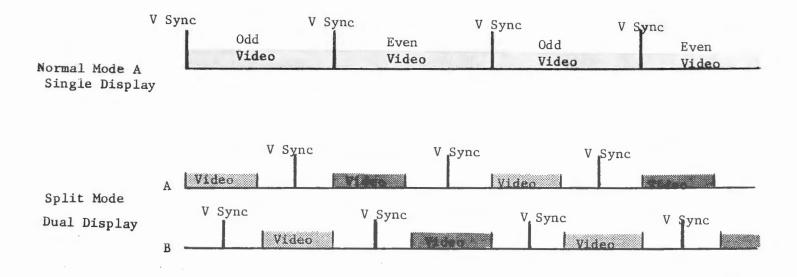

|         |      | 6.7.1    | Introduction                                         | 6-34 |

|         |      | 6.7.2    | Remote Load Sequence                                 | 6-34 |

|         |      | 6.7.3    | Boot Controller Circuitry                            | 6-35 |

# TABLE OF CONTENTS (Cont.)

| Chapter  |                                                | Page |

|----------|------------------------------------------------|------|

| VII      |                                                | 7-1  |

| 7.1      | General                                        | 7-1  |

| 7.2      | Field Substitution                             | 7-1  |

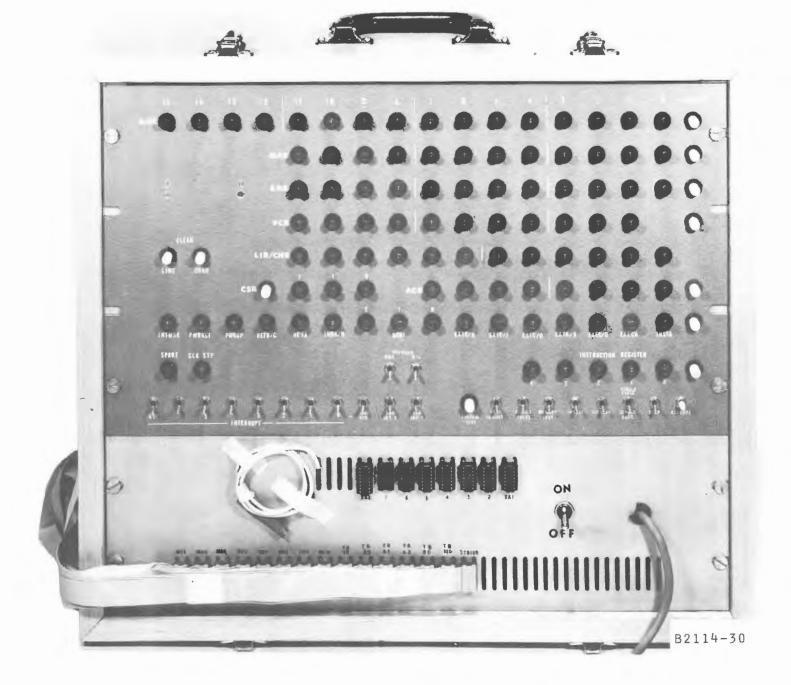

| 7.3      | Test Console                                   | 7-9  |

|          | 7.3.1 Wiring Procedure                         | 7-11 |

|          | 7.3.2 Detailed Explanation of Control Switches | 7-17 |

| 7.4      | Test Points Not Console Tested                 | 7-20 |

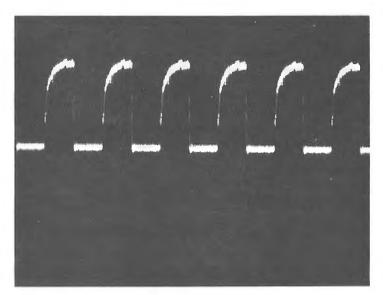

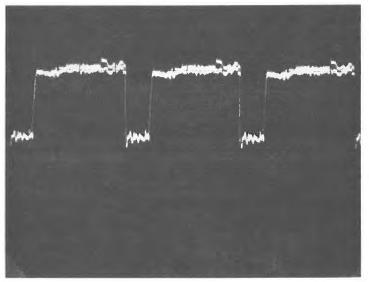

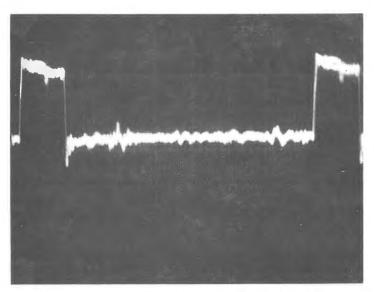

| 7.5      | Waveforms                                      | 7-27 |

| 7.6      | CRT Adjustments                                | 7-33 |

| APPENDIX | A-SIGNAL MNEMONICS                             | A-1  |

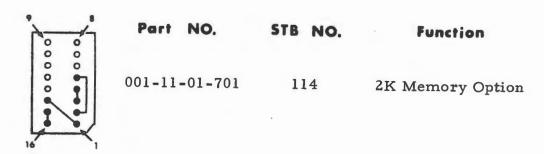

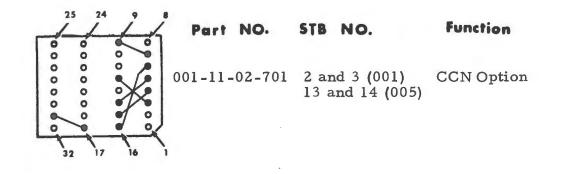

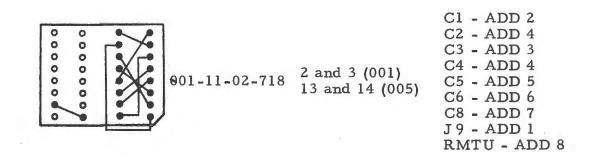

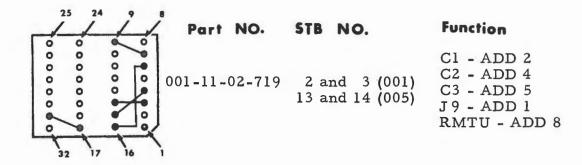

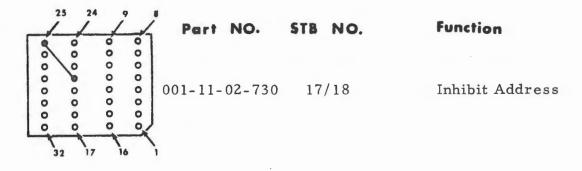

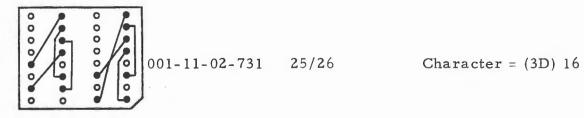

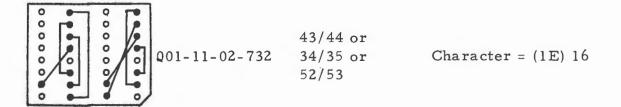

| APPENDIX | B-OPTION BLOCKS                                | B-1  |

| APPENDIX | C-MISCELLANEOUS CABLE DATA                     | C-1  |

# LIST OF ILLUSTRATIONS

| -5<br>-6<br>-2<br>-3<br>-4 |

|----------------------------|

| -2<br>-3<br>-4             |

| -3<br>-4                   |

| -4                         |

|                            |

| -5                         |

|                            |

| -6                         |

| -7                         |

| -11                        |

| -12                        |

| -13                        |

| -3                         |

| -2                         |

| -4                         |

| -12                        |

| -13                        |

| -17                        |

| -2                         |

| -10                        |

| -11                        |

| -22                        |

| -23                        |

| 5-24                       |

| 5-50                       |

| 5-51                       |

| 5-52                       |

| 5-55                       |

| 5-59                       |

|                            |

1

$\mathbf{i}\mathbf{x}$

# LIST OF ILLUSTRATIONS (Cont.)

| Figure |                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------|------|

| 5-12   | Refresh Module Timing Unit                                                           | 5-62 |

| 5-13   | Simplified Block Diagram Refresh Module<br>Refresh Module Timing Unit                | 5-63 |

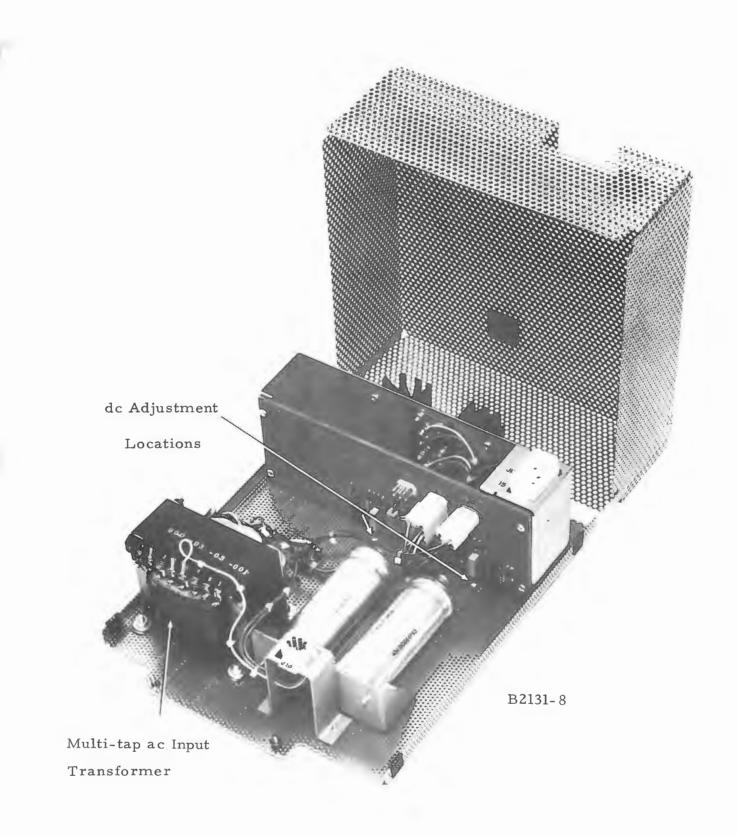

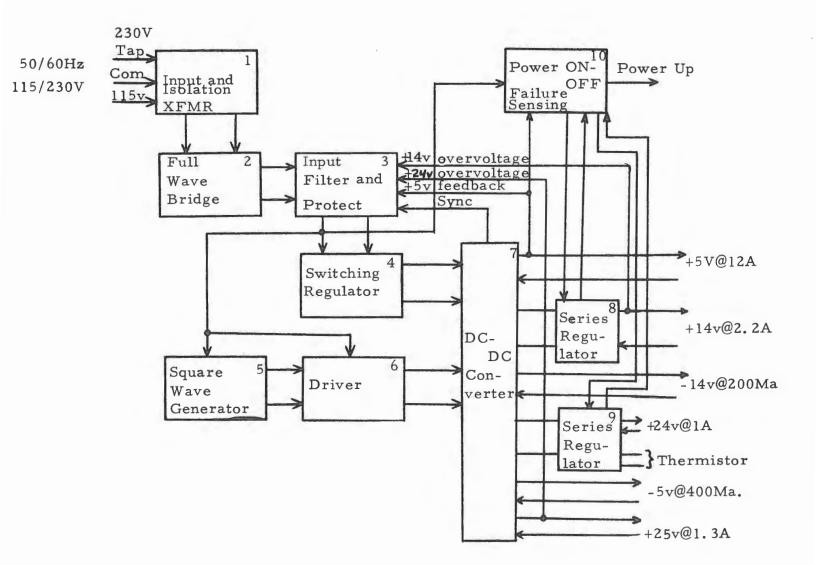

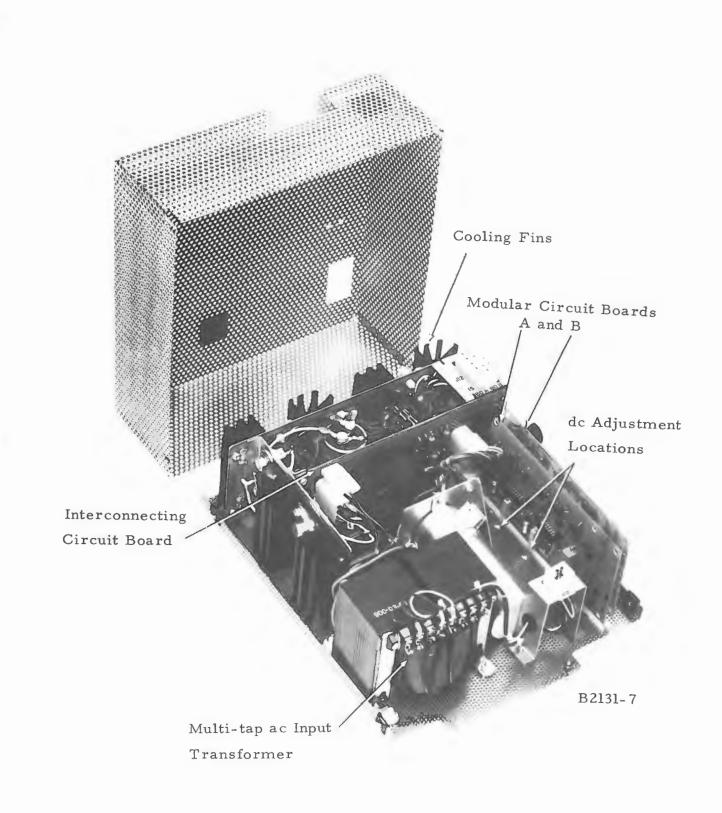

| 5-14   | Internal View Power Supply                                                           | 5-72 |

| 5-15   | Simplified Block Diagram Power Supply                                                | 5-73 |

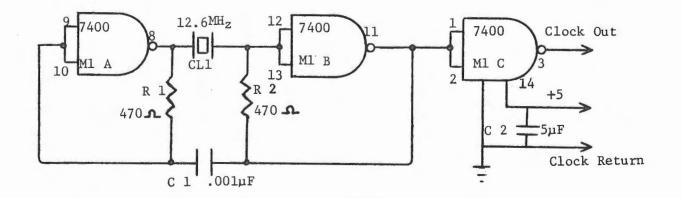

| 5-16   | Line Lock Oscillator Schematic                                                       | 5-76 |

| 6-1    | Code Chart, 1090-C Keyboard                                                          | 6-2  |

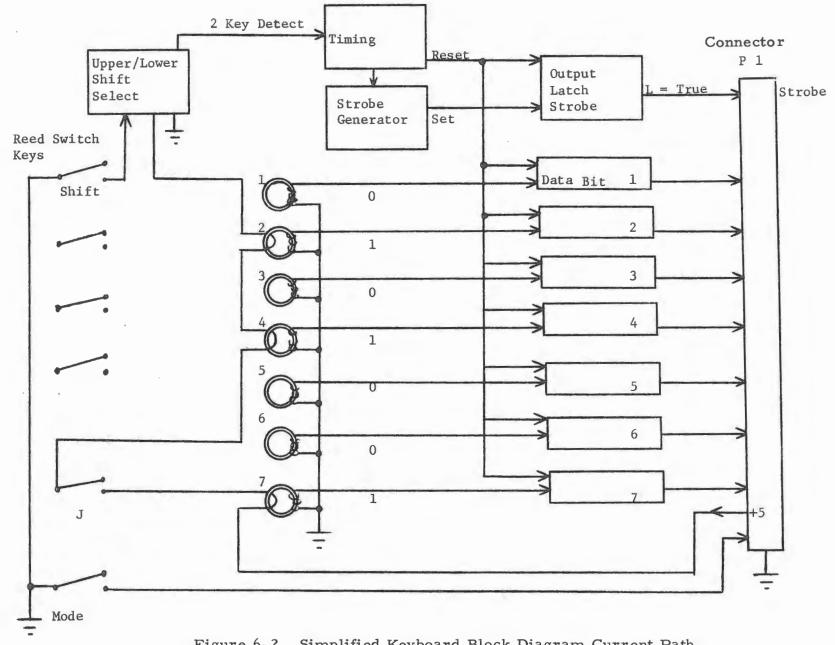

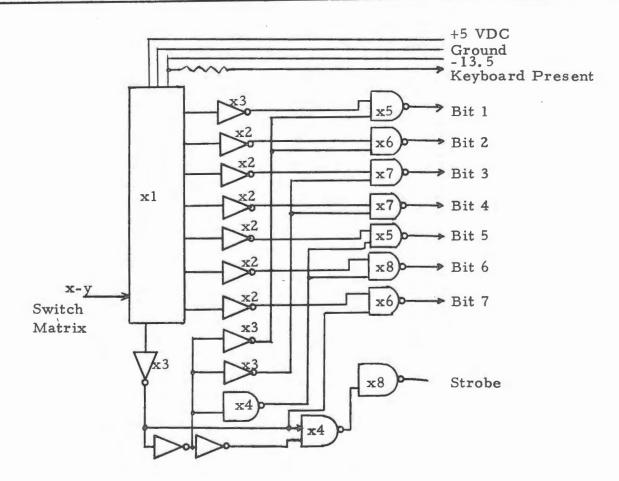

| 6-2    | Simplified Keyboard Block Diagram Current Path<br>Illustrated for J Key              | 6-3  |

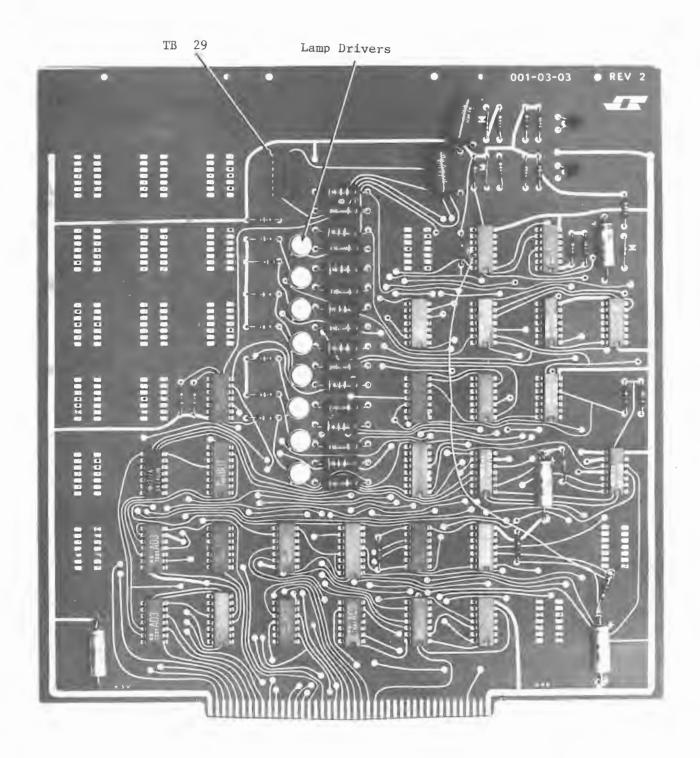

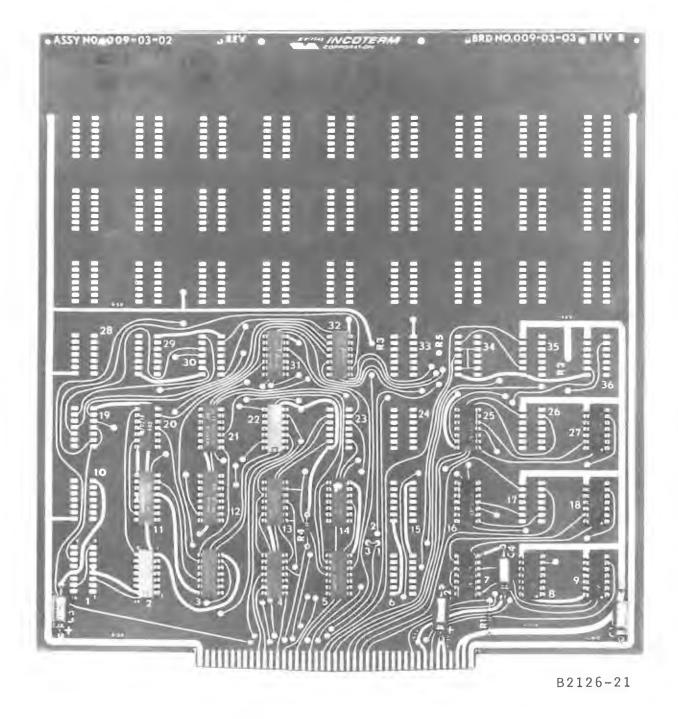

| 6-3    | Keyboard Controller                                                                  | 6-6  |

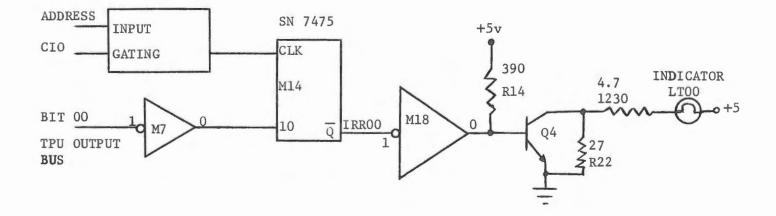

| 6-4    | Typical Keyboard Lamp Driver Circuit                                                 | 6-7  |

| 6-5    | Asynchronous Controller                                                              | 6-12 |

| 6-6    | Block Diagram Asynchronous Controller                                                | 6-14 |

| 6-7    | Synchronous Controller                                                               | 6-25 |

| 6-8    | Split Screen Controller                                                              | 6-30 |

| 6-9    | Simplified Block Diagram Split Screen Controller                                     | 6-31 |

| 6-10   | Split Screen Timing                                                                  | 6-32 |

| 6-11   | Simplified Diagram Boot Controller                                                   | 6-36 |

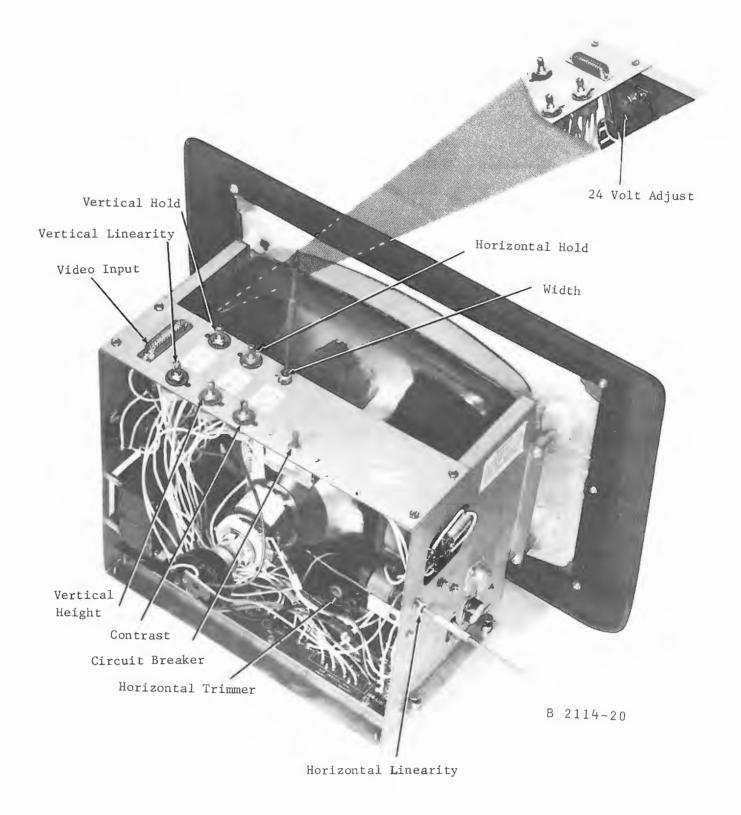

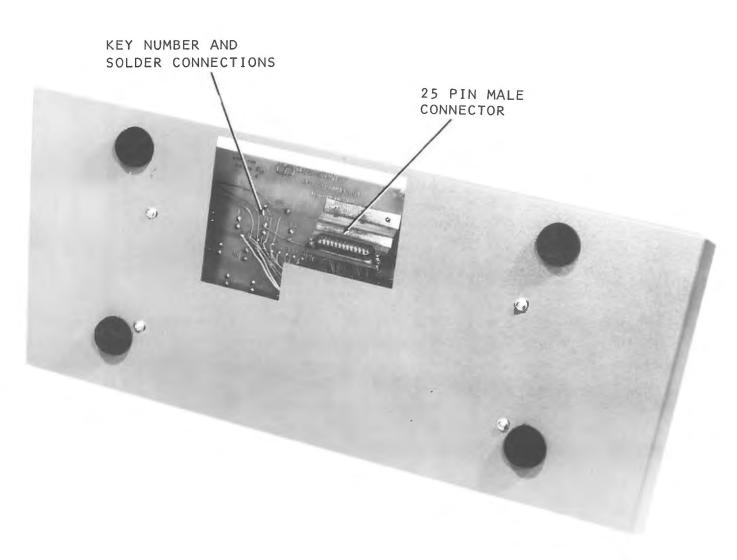

| 7-1    | Bottom View of Terminal Illustrating Voltage Test<br>Points and Adjustment Locations | 7-6  |

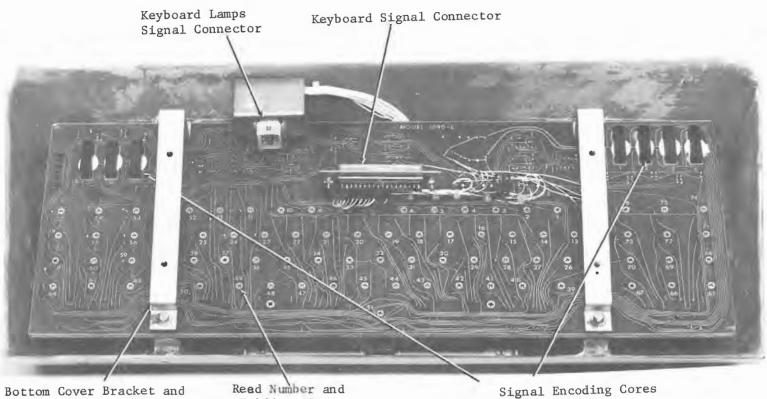

| 7-2    | Keyboard Bottom View                                                                 | 7-8  |

| 7-3    | INCOTERM Test Console                                                                | 7-10 |

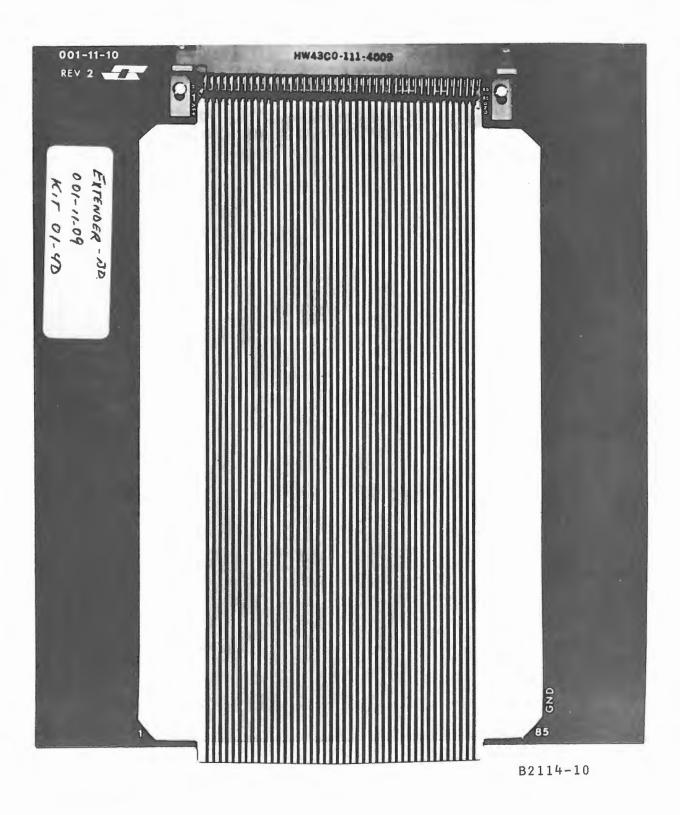

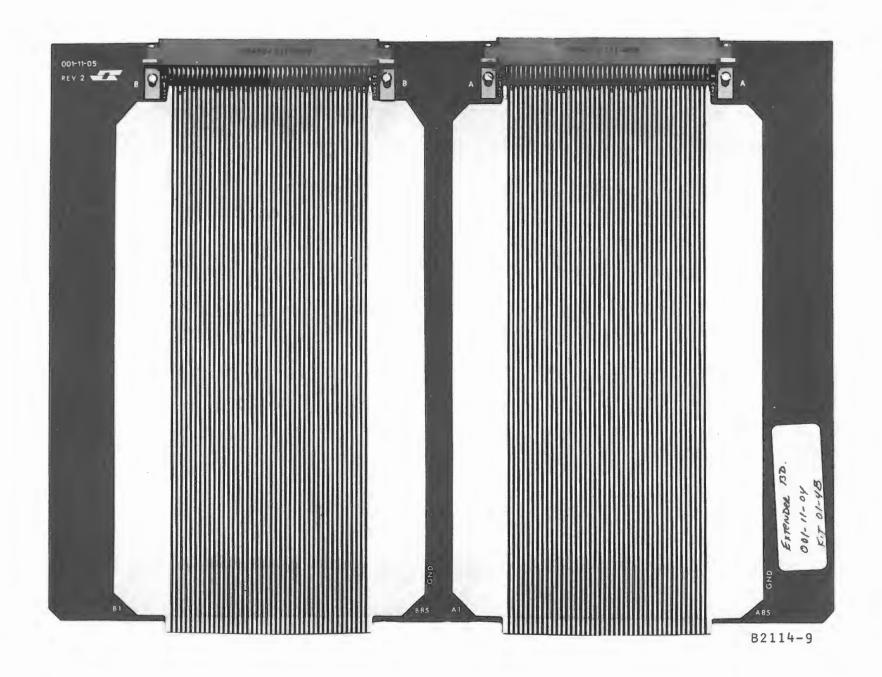

| 7-4    | Controller Circuit Board Extender                                                    | 7-12 |

| 7-5    | Computer Circuit Board Extender                                                      | 7-13 |

| 7-6    | T. V. Monitor Adjustments                                                            | 7-34 |

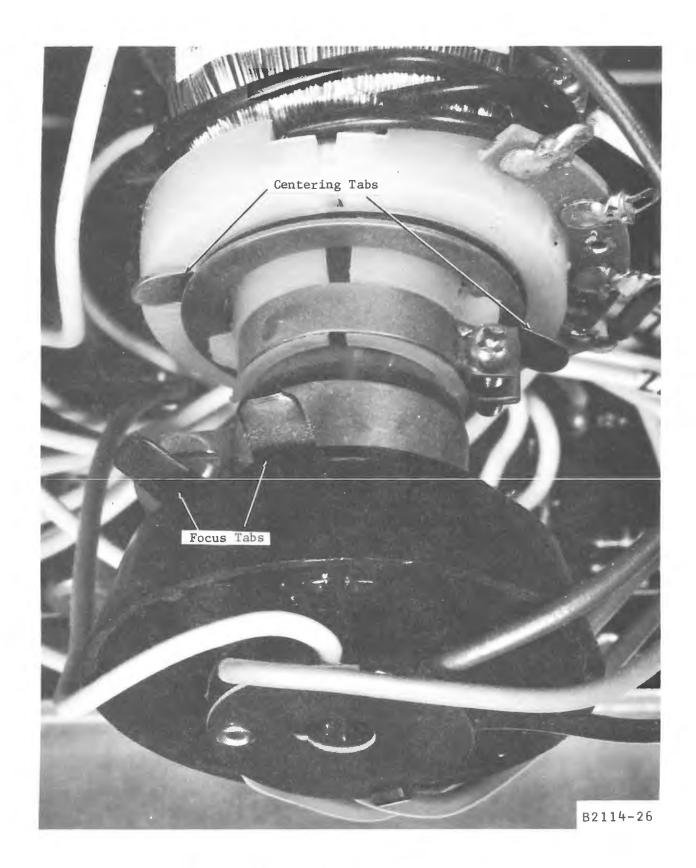

| 7-7    | Cathode Ray Tube Adjustments                                                         | 7-35 |

# LIST OF TABLES

| Table |                                                              | Page |

|-------|--------------------------------------------------------------|------|

| 1-1   | SPD 10/20 TPU Specifications                                 | 1-3  |

| 1-2   | SPD Product Physical and Electrical Data                     | 1-4  |

| 2-1   | Configuration Chart                                          | 2-8  |

| 4-1   | SPD 10/20 Controllers, Related Function and External Devices | 4-7  |

| 4-2   | Decimal, Binary and Hexadecimal Equivalents                  | 4-8  |

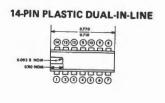

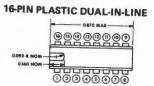

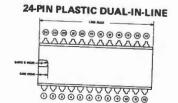

| 5-1   | Integrated Circuit Reference Table                           | 5-3  |

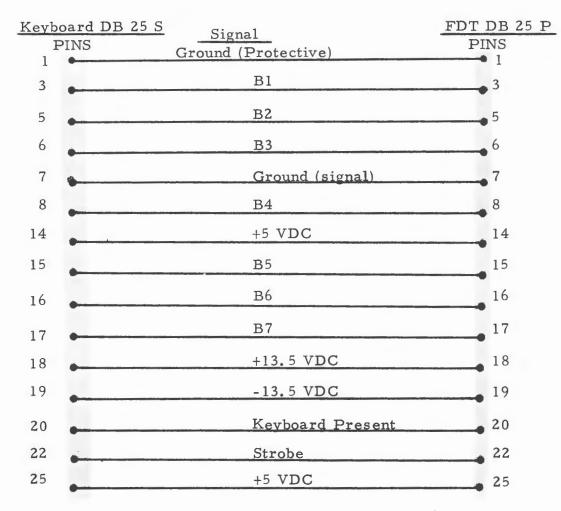

| 6-1   | Keyboard Connectors                                          | 6-4  |

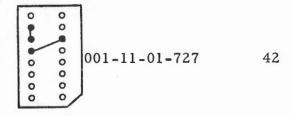

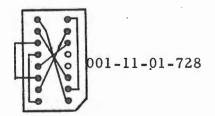

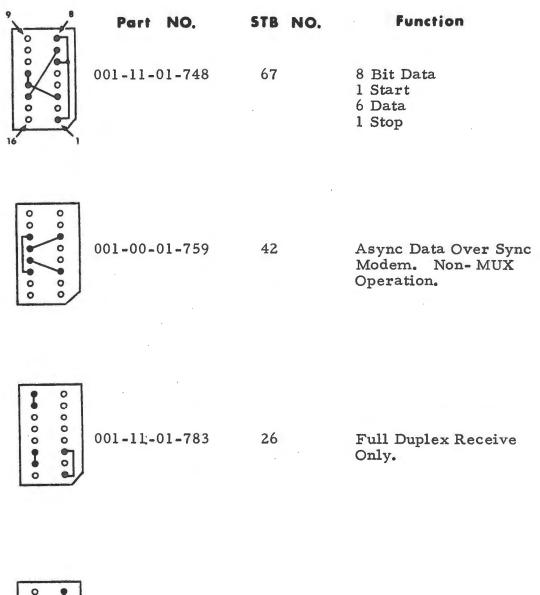

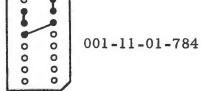

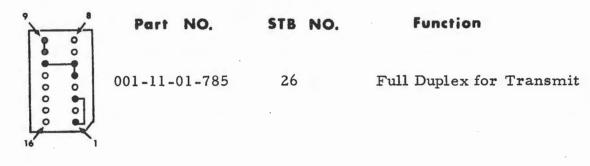

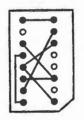

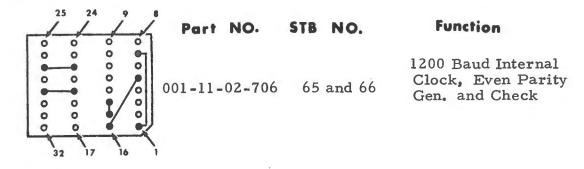

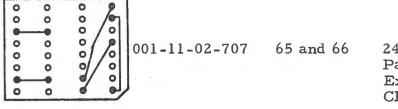

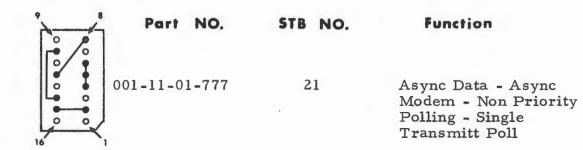

| 6-2   | Asynchronous Controller Option Blocks                        | 6-15 |

| 7-1   | Field Problem Identification                                 | 7-2  |

| 7-2   | Test Point Wiring From TPU to Console                        | 7-14 |

| 7-3   | Test Points Not Console Tested                               | 7-21 |

ι

(c)

## FOREWORD

This manual provides the installation, theory of operation and maintenance procedures for the SPD<sup>IM</sup> -10/20 stored Program Display Terminal. Field repair is accomplished by on-site replacement of a faulty module. Module repair is performed offsite by a technical staff with appropriate test equipment. An understanding of the theory provided in this manual and a familiarization with the logic diagrams provided in support document FS 003 will provide the required background for technical proficiency in both areas of SPD 10/20 maintenance.

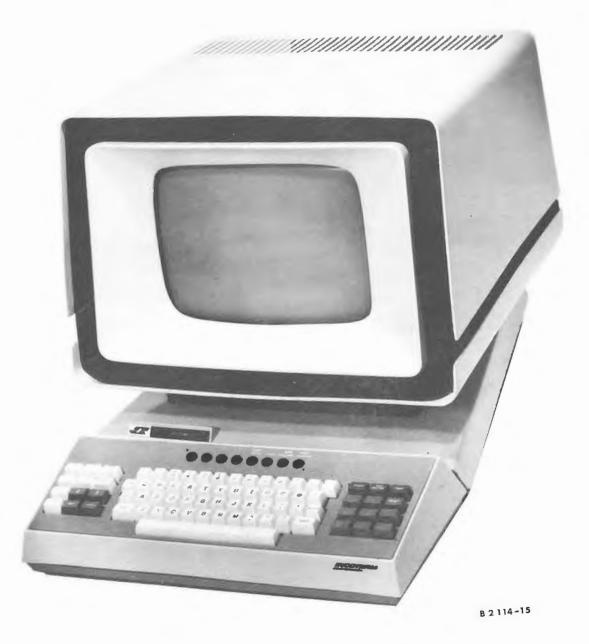

SPD 10/20 Stored Program Display Terminal

## CHAPTER I

#### INTRODUCTION

#### 1.1 SCOPE

The purpose of this manual is to provide Field Engineers with preliminary data concerning the SPD 10/20 Stored Program Display Terminal. Two levels of information are required within the Field Service organization. First, the Field Repair philosophy dictates repair by replacement of assemblies and subassemblies; and, secondly, Depot repair requires replacement of components in assemblies and subassemblies returned from the field. This manual is organized to fulfill both levels of maintenance.

## 1.2 GENERAL SPECIFICATIONS

The SPD 10/20 is a CRT display containing a stored-program computer. The built in computer allows the terminal to be programmed and optimized for any specific application. It also allows the terminal to operate in any network, with or without a central computer. Table 1-1 contains the operating specifications for the SPD 10/20 Display Terminal. Table 1-2 provides both physical and electrical data for the Display Terminal and associated products.

## 1.3 CONFIGURATION

The SPD 10/20 is designed for maximum production standardization such that the product baseline is manufactured and stocked as an off-the-shelf item. The terminal computing circuitry, Display CRT, input output wiring, and housing are included in the baseline configuration. When a customer's order is placed, any required additional hardware is easily included. Configuration deviations are caused by each customer's definition of the type of data environment the Terminal will be exposed to. At this point, modular I/O interface circuitry is added with little or no change necessary to the manufactured terminal.

## 1.3.1 Minimum Configurations

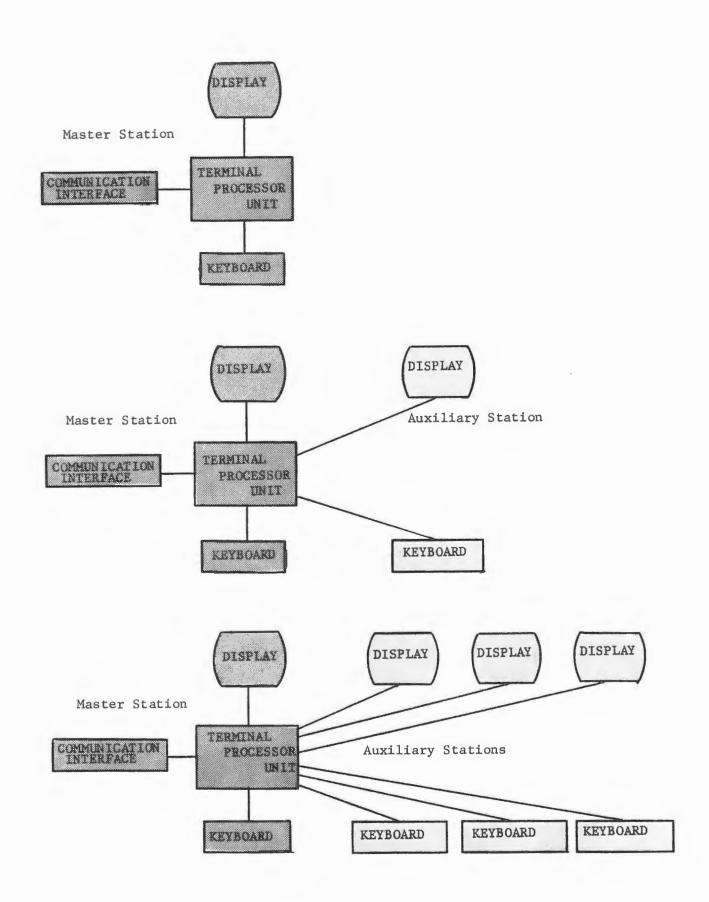

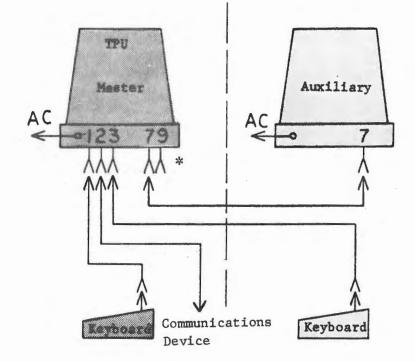

Minimum unit configuration relative to the SPD 10/20 product line is comprised of three terminal utilizations, illustrated in Figure 1-1. First, the basic terminal contains the terminal processor (computer), display, keyboard and half duplex communications interface. The second adds a remote display and keyboard manufactured as an auxiliary unit to the basic terminal. The auxiliary is identical in appearance to the basic unit, but does not have a computer or I/O circuitry. The basic terminal, in this case, becomes a master; the auxiliary is a slave that shares the basic terminal computer. The third is a further extension of the second, which results in two additional input and display stations operating as slaves to the master terminal.

## 1.3.2 Units Available for Expanded Configurations

As an enhancement to the versatility of the SPD 10/20 Display Terminal, INCOTERM has developed a complete family of SPD products. The following paragraphs briefly describe each product. Figure 1-2 illustrates the present SPD product line.

# SPD<sup>TM</sup>L Program Loader

The SPD-L Program Loader is used to load data into the TPU from punched paper tape. The loader, a portable device, contains its own control electronics and does not require an I/O interface controller. Data is entered into the TPU by bootstrapping the tape data to the I/O data bus, which is directly accessed at connector 9 on the TPU connector panel. This mode of operation is initiated at the loader. It is possible to load from tape via TPU command.

## Table 1-1. SPD 10/20 Terminal Processing Unit (TPU) Specifications

| Type:                           | Parallel binary, byte oriented                                                                        |

|---------------------------------|-------------------------------------------------------------------------------------------------------|

| Addressing:                     | Single address with indirect addressing                                                               |

| Data Word Length:               | 8-bit byte, 12-bit special word                                                                       |

| Memory Word Length:             | 16 bits, 2 bytes                                                                                      |

| Arithmetic Code:                | Two's complement                                                                                      |

| Internal Memory:                | Magnetic core with 2048 16-bit words                                                                  |

| Memory Cycle:<br>Machine Speed: | <ol> <li>6 microseconds</li> <li>Add: 3.2 microseconds</li> <li>Subtract: 3.2 microseconds</li> </ol> |

| Standard I/O Lines:             | 8-bit input bus<br>8-bit output bus<br>10-bit control bus<br>8 interrupt lines                        |

# SPD<sup>TM</sup> -M Terminal Multiplexer Unit

The SPD-M provides the capability of interfacing a maximum of 16 terminals to a single modem. When in use, the Multiplexer monitors the communications line and provides ordered transmissions. The Multiplexer can also be cascaded to provide additional terminals with data.

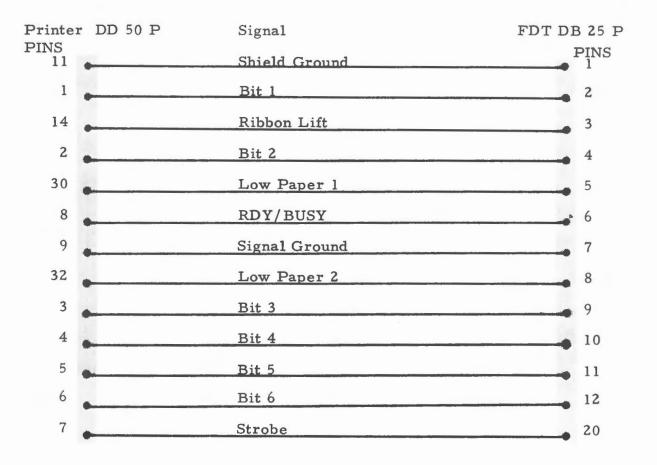

# SPD<sup>TM</sup> - P Printer

The SPD-P is a hard copy output device which prints out messages sent to it by SPD 10/20 Terminals. The Printer contains its own multiplexer and can interface with up to 16 SPD 10/20 Terminals. The hard copy form is edge sprocketed measuring up to 14-7/8 inches in width and 11 inches in length. The forms can provide multiple copies. Data input to the Printer conforms to the American Standard Code for Information Interchange (ASCII).

## 1.4 REFERENCE DOCUMENTS

SPD 10/20 programming instructions are found in the Programmer's Reference Manual. Operating functions for specific programs are found in

| Unit Type            | Size in<br>Inches<br>(HxWxD)                 | Weight<br>in<br>Lbs. | Maximum Cable<br>Length<br>in Feet                                  | Power<br>in Watts | Voltage & Frequency                 |

|----------------------|----------------------------------------------|----------------------|---------------------------------------------------------------------|-------------------|-------------------------------------|

| SPD 10/20            | 18x18.5x19                                   | 48                   | 50 - Modem<br>300 - Multiplexer<br>1000 - Multiplexer<br>(OPTIONAL) | 180               | 117V <u>+</u> 10%, 60 <u>+</u> 1 Hz |

| KEYBOARD             | 3.2x19x8.1                                   | 7                    | 10 - SPD 10/20                                                      | POWER             | ED FROM SPD 10/20                   |

| PRINTER              | 12x31x26<br>(Desk)<br>36x31x26<br>(Pedestal) | 90                   | 300 - SPD 10/20<br>1000 - SPD 10/20<br>(OPTIONAL)                   | 450               | 110 to 125V, 60 <u>+</u> 0.5 Hz     |

| MULTIPLEXER          | 9.5x17x14                                    | 30                   | 50 - Modem<br>300 - SPD 10/20<br>1000 - SPD 10/20<br>(OPTIONAL)     | 120               | 117V <u>+</u> 10%, 60 <u>+</u> 1 Hz |

| PROGRAM LOADER       | 5x12x7                                       | 10                   | 10 - SPD 10/20                                                      | POWER             | RED FROM SPD 10/20                  |

| AUXILIARY<br>DISPLAY | 18x18-1/2x19                                 | 40                   | 10 - SPD 10/20                                                      | 60                | 117V <u>+</u> 10%, 60 <u>+</u> 1 Hz |

Table 1-2. SPD Product Physical and Electrical Data

Figure 1-1. Minimum Terminal Configurations

SPD-P Printer

SPD-M Multiplexer

SPD -L Program Loader

Figure 1-2. SPD Product Line

the Operator's Brochure. Integrated circuit descriptions are found in Texas Instrument Catalog CC-201R and supplement CC-301. Technical data for the SPD Peripheral line is presented in the INCOTERM Peripheral Products Technical Manual.

1

#### CHAPTER II

#### INSTALLATION

#### 2.1 VISUAL INSPECTION

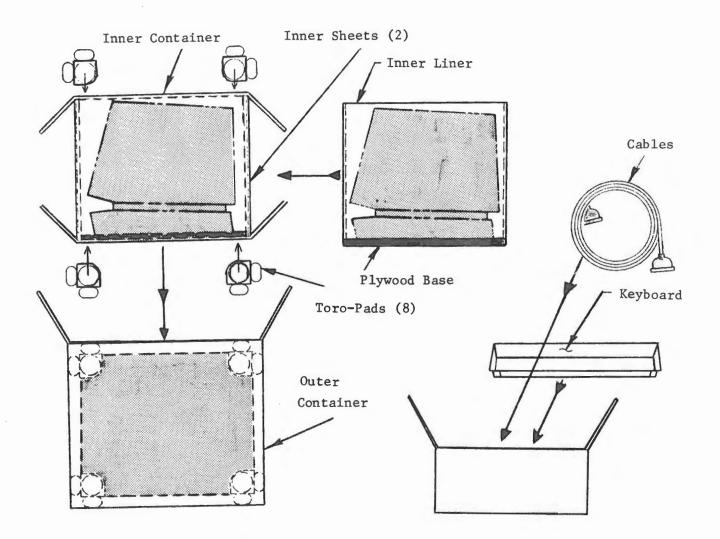

Prior to unpacking, check the shipping container for signs of damage in shipment such as crushed or torn areas. Packing at the factory consists of placing the Terminal on a plywood base which prevents lateral movement during shipment. The Terminal is then placed in a cardboard container which serves as an inner container. The inner container is restricted from moving within the outer container by edgemounted shock absorbers. See Figure 2-1 for packaging layout.

As illustrated in Figure 2-1, the Keyboard and associated cables are packed in a separate smaller container. Shipping weight of the Terminal is approximately 60 pounds. Shipping weight of the Keyboard and cables is approximately 10 pounds.

In the event that damage in shipment has occurred or the items received are not those listed on the Equipment Summary, promptly contact:

> James Mahoney INCOTERM Corp. Phone: 617-481-2000

A visual examination of the contents can be made while removing the Terminal from the shipping container. Check for any indication of damage in shipment, such as cracked outer housing, broken CRT, damaged cables, pins, loose or bent hardware, etc. Remove the plywood base and outer housing from the Terminal to facilitate visual inspection of the bottom and inside of the Terminal.

Figure 2-1. Factory Packing

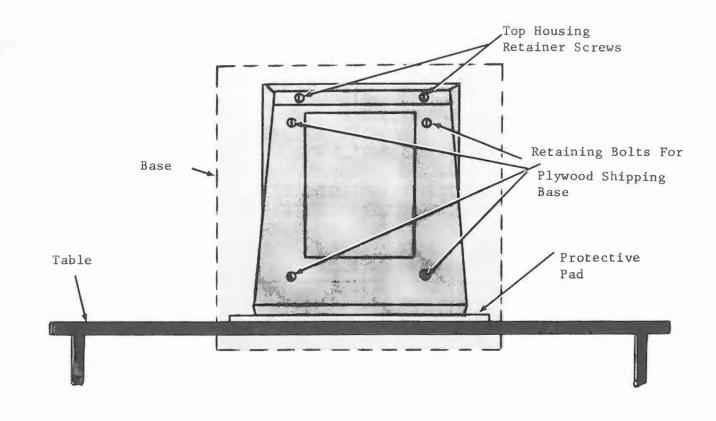

Removal of the outer housing is accomplished as follows. (See figure 2-2.)

- (a) Place Monitor protective pad on table and rest Terminal face down on the pad.

- (b) Remove plywood base by removing four retaining bolts.

- (c) Rotate the two lock-down screws located under the rear edge of the Terminal.

Figure 2-2. Removal of Plywood Base

# (d) Return the Terminal to its proper position and lift outer housing up and away from Terminal.

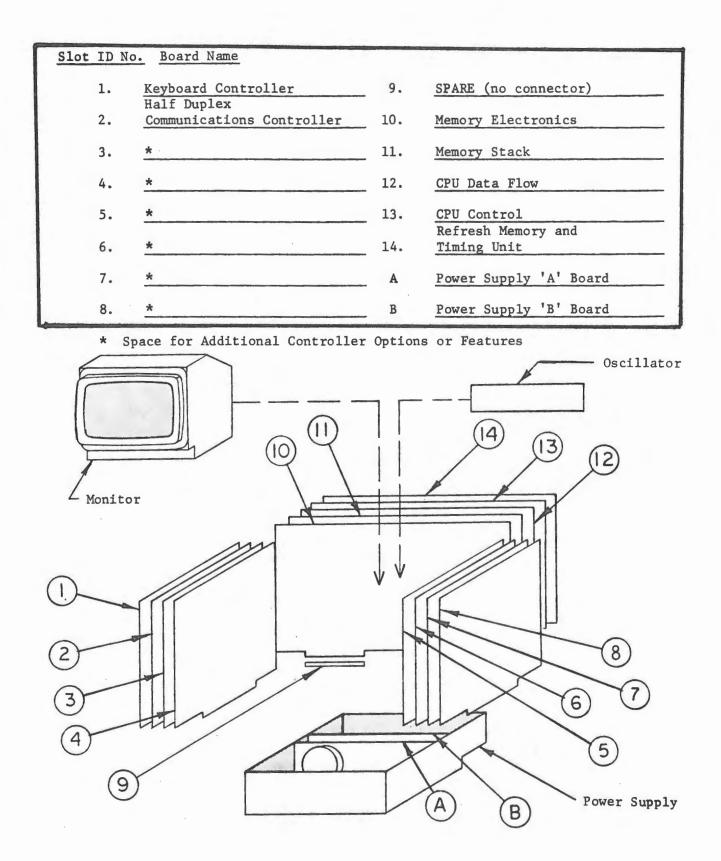

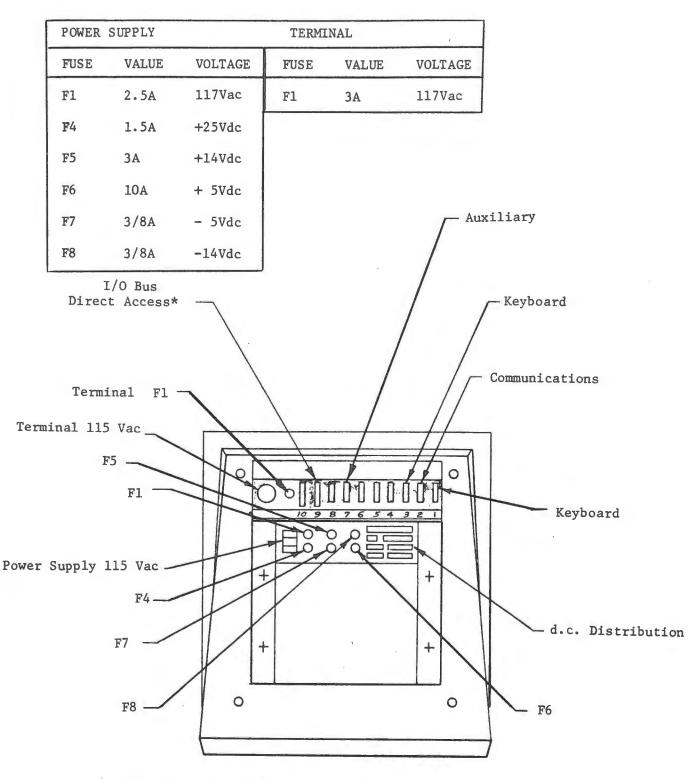

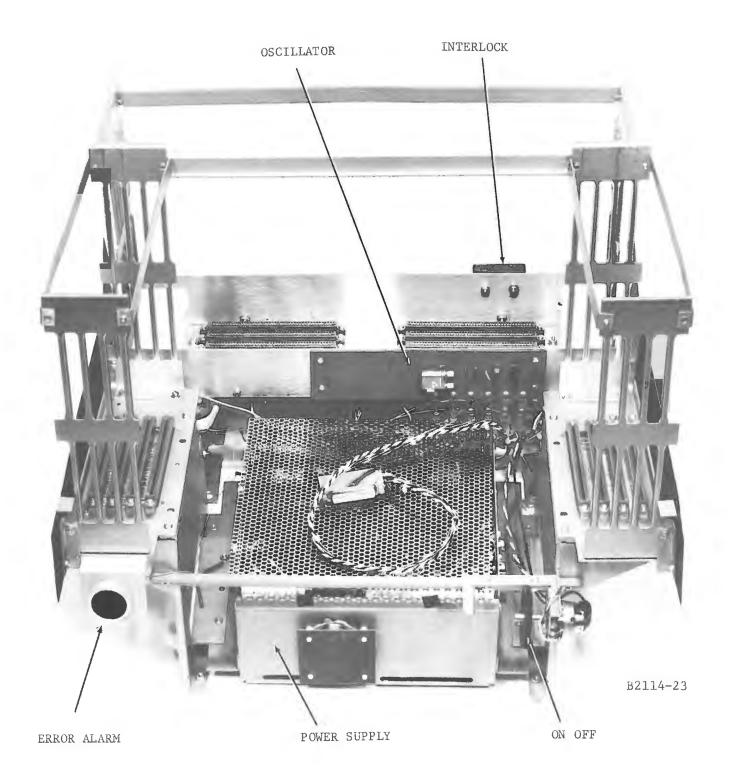

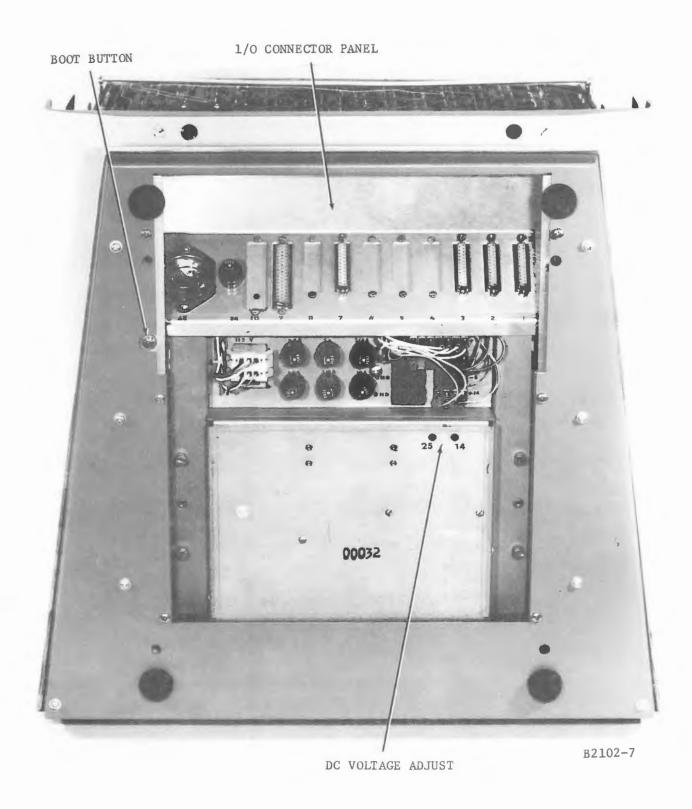

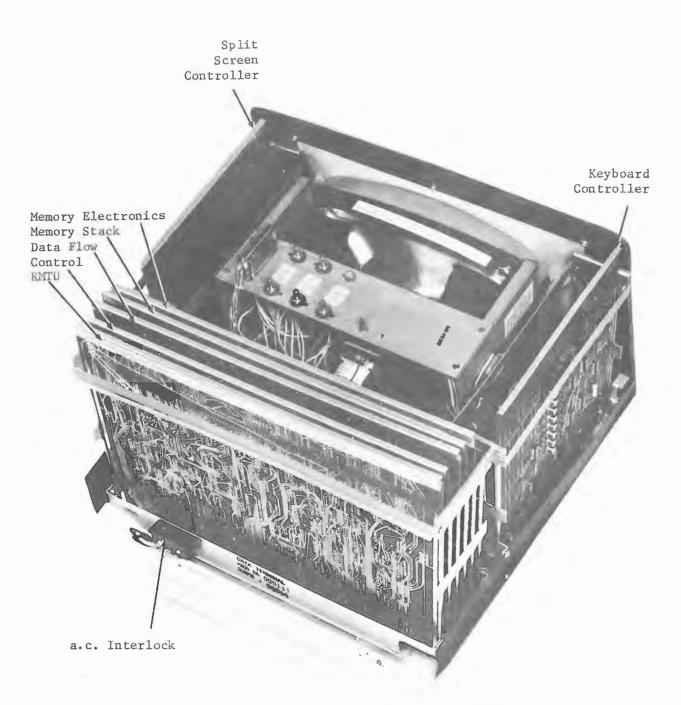

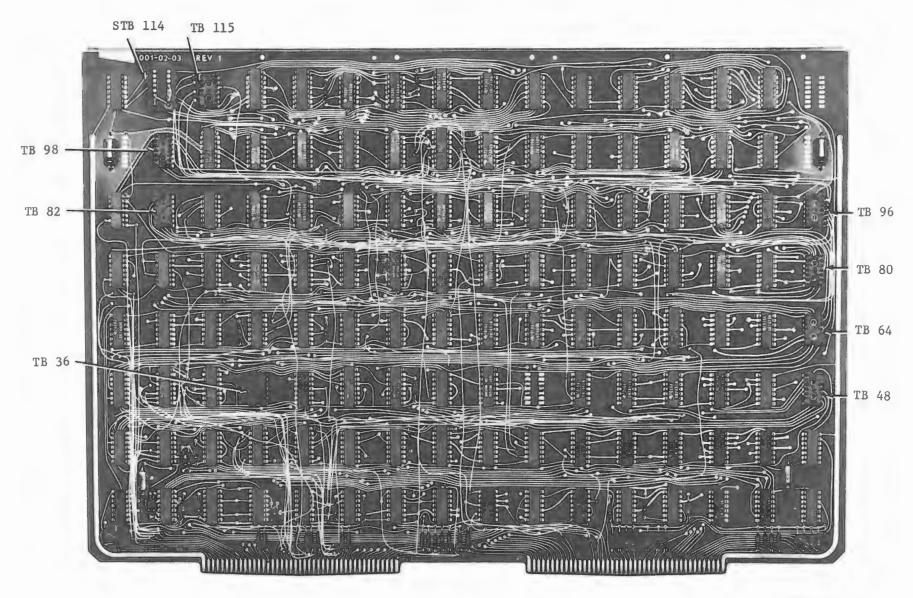

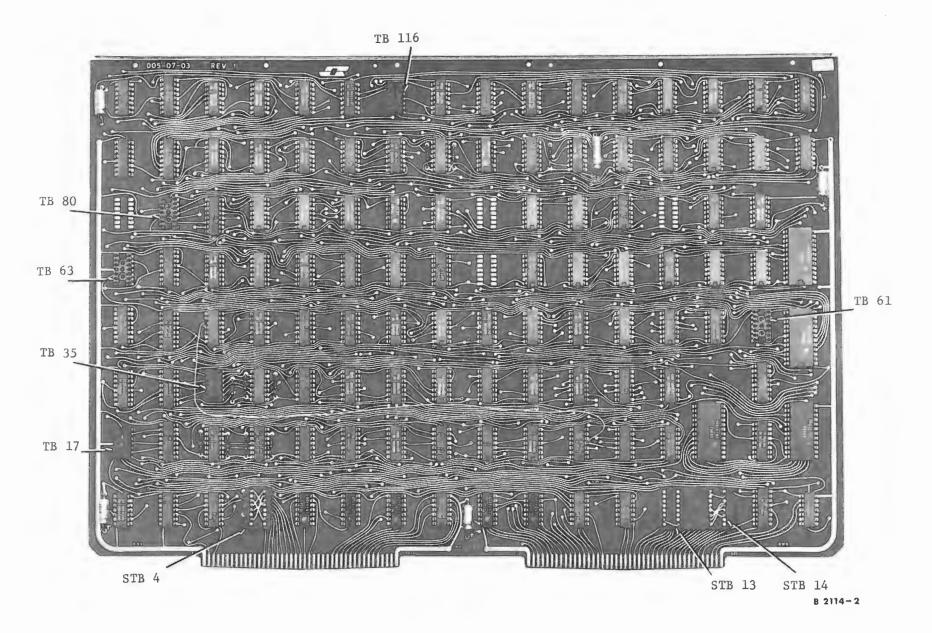

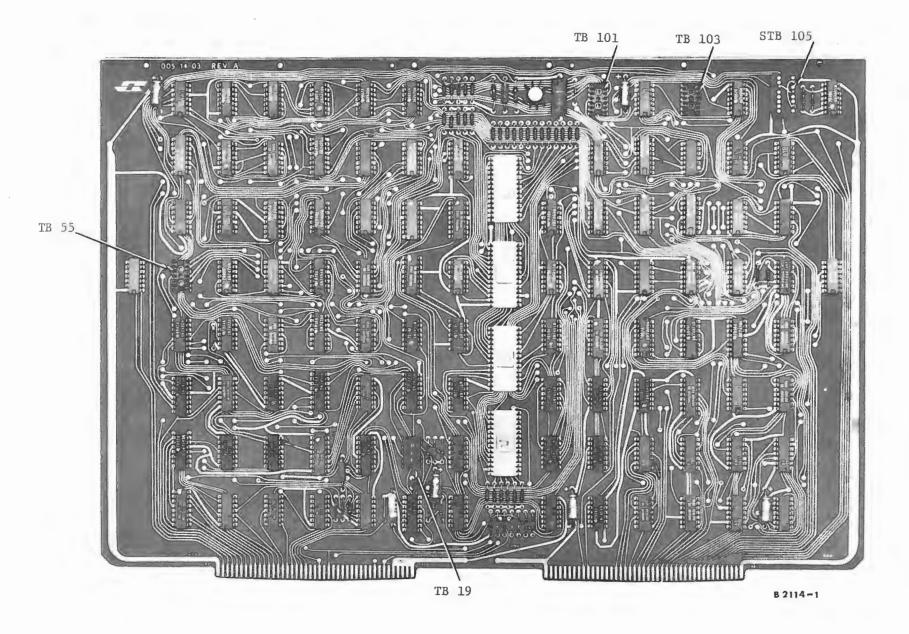

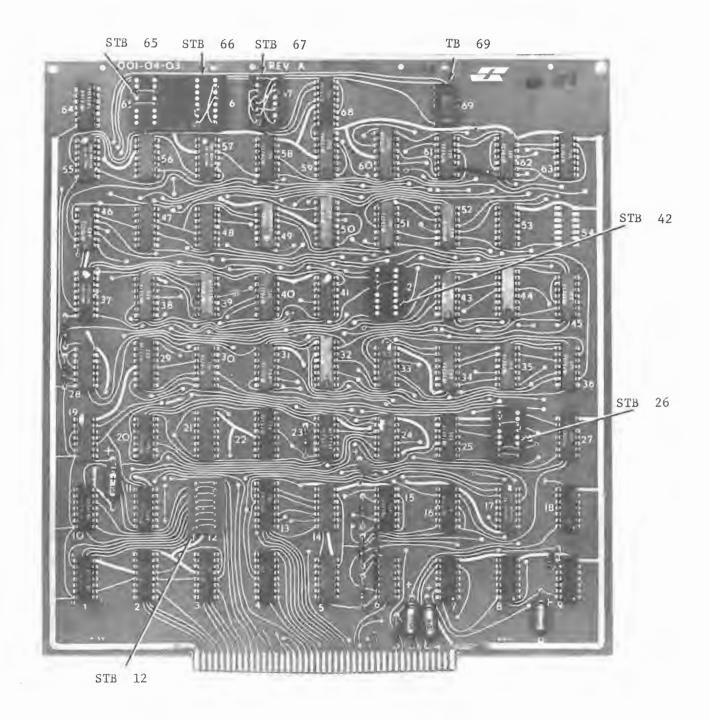

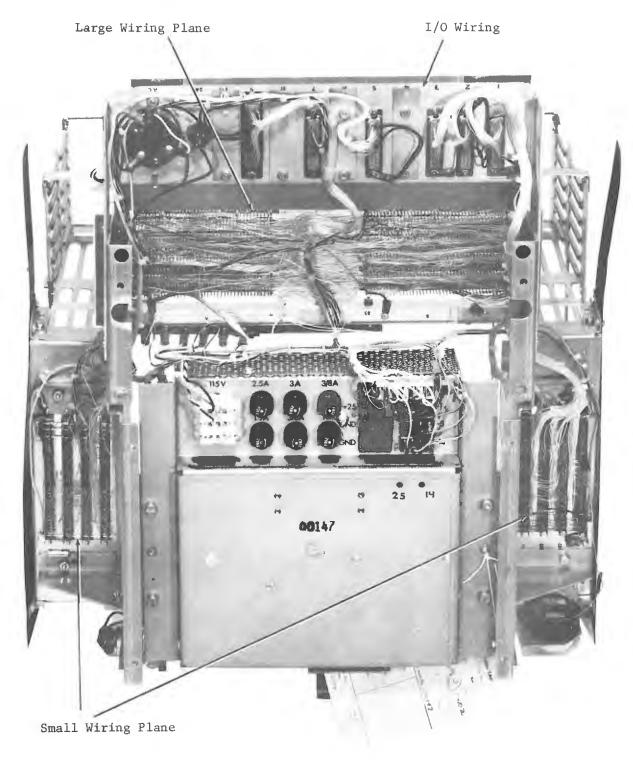

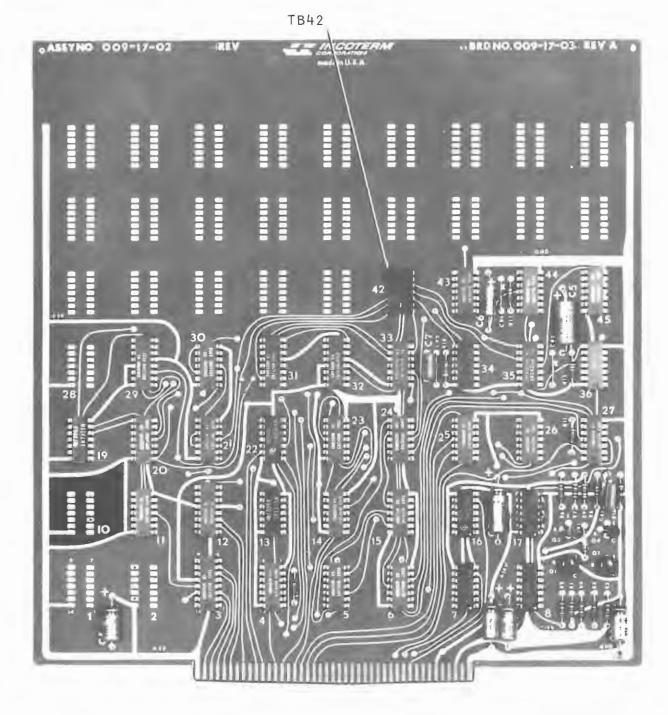

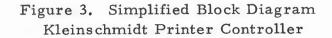

While the top cover is off, check the circuit boards to see if they are properly aligned and plugged in, as vibration in shipment could cause board loosening. See Figure 2-3 for circuit board identification and location. Check the connectors and fuses that are accessible from the bottom of the Terminal. See Figure 2-4 for identification and location. Replace top cover by reversing the removal procedure. Figure 2-5 and 2-6 provide actual views relating to construction and location of the TPU and associated components.

## 2.2 CONFIGURATION CHART

Table 2-1, along with the visual inspection and shipping memo (Figure 2-7), provide a check list to verify that for the given product, model and serial number, the required boards have been supplied. This table will be expanded as future products, models and options are developed.

Figure 2-3. Circuit Board Identification and Location

\* Will commonly be used for Program Loading.

Figure 2-5. TPU Wired Chassis with Power Supply

Figure 2-6. Bottom View Actual Photo

| N |  |

|---|--|

| 1 |  |

| 8 |  |

# Table 2-1. Configuration Chart

| Board | C                             | ircuit Board Allo             | ocation per Product           | and Model Number              |                               |

|-------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| Slot  | 005/00010                     | 006/00011                     | 005/00012                     | 006/00013                     | 005/00014                     |

| 1.    | Keyboard<br>001-03-03         | Keyboard<br>001-03-03         | Keyboard<br>001-03-03         | Keyboard<br>001-03-03         | Keyboard<br>001-03-03         |

| 2.    | Sync<br>001-08-03             | Sync<br>001-08-03             |                               |                               | Sync<br>001-08-03             |

| 3.    | Keyboard<br>001-03-03         | Keyboard<br>001-03-03         |                               |                               |                               |

| 4.    |                               |                               |                               |                               |                               |

| 5.    |                               |                               |                               |                               |                               |

| 6.    |                               |                               |                               |                               |                               |

| 7.    | Split Screen<br>001-15-03     | Split Screen<br>001-15-03     | Jumper                        | Jumper                        | Jumper                        |

| 8.    |                               |                               |                               |                               |                               |

| 9.    | <b>4</b>                      |                               | NO CONNECTION                 |                               |                               |

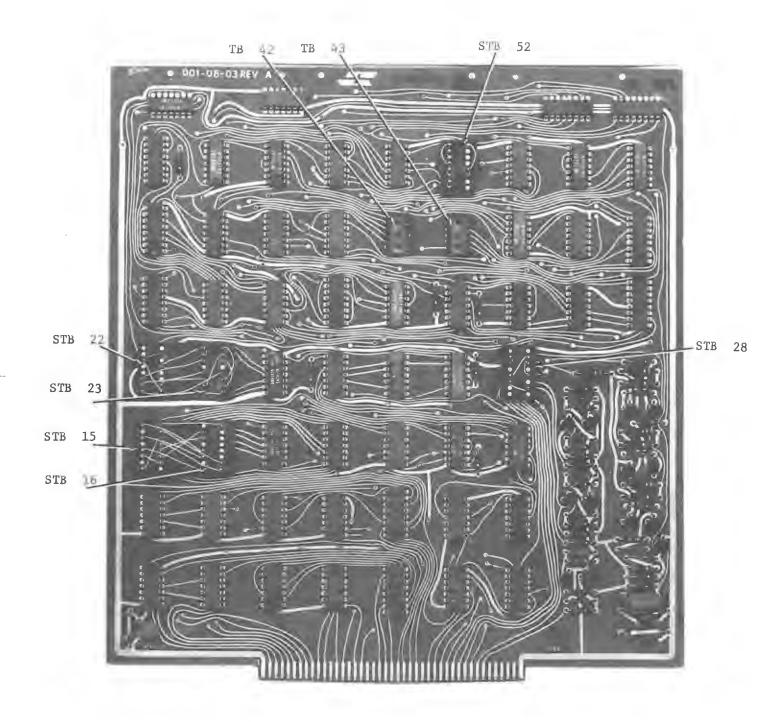

| 10.   | Memory Elec.<br>001-06-03     | Memory Elec.<br>006-06-03     | Memory Elec.<br>001-06-03     | Memory Elec.<br>006-06-03     | Memory Elec.<br>001-06-03     |

| 11.   | Memory<br>Stack 2K            |

| 12.   | TPU Data<br>Flow<br>001-02-03 | TPU Data<br>Flow<br>006-02-03 | TPU Data<br>Flow<br>001-02-03 | TPU Data<br>Flow<br>006-02-03 | TPU Data<br>Flow<br>001-02-03 |

| Board                                                 | Circuit Board Allocation per Product and Model Number |                                                   |                                                   |                                                   |                                                               |  |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------|--|--|--|--|--|

| Slot                                                  | 005/00010                                             | 006/00011                                         | 005/00012                                         | 006/00013                                         | 005/00014                                                     |  |  |  |  |  |

| 13.                                                   | TPU Control<br>005-07-03                              | TPU Control<br>005-07-03                          | TPU Control<br>005-07-03                          | TPU Control<br>005-07-03                          | TPU Contro<br>005-07-03                                       |  |  |  |  |  |

| 14. Refresh<br>Module and<br>Timing Unit<br>005-14-03 |                                                       | Refresh<br>Module and<br>Timing Unit<br>005-14-03 | Refresh<br>Module and<br>Timing Unit<br>005-14-03 | Refresh<br>Module and<br>Timing Unit<br>005-14-03 | Refresh<br>Module and<br>Timing Unit<br>005-14-03<br>(Custom) |  |  |  |  |  |

| With<br>AUX                                           | x                                                     | х                                                 |                                                   |                                                   |                                                               |  |  |  |  |  |

| Without<br>AUX                                        |                                                       |                                                   | x                                                 | х                                                 | х                                                             |  |  |  |  |  |

Table 2-1. Configuration Chart (Cont)

#### NOTE

Board etch number is listed in Table 2-1 because there is a difference between Product 005 and 006 art work. The Table makes the different boards clear. Also be aware that the number etched on a given board relates to the artwork and is not a circuit board part number. The part number is provided on the Equipment Summary. Figure 2-7 is an example of the Shipping Memo which is packed with each system. As stated previously, this data is available at installation time. The data identifies the particular Terminal and should be retained for future reference.

## 2.3 SITE PREPARATION

Site preparation is not a critical factor with the SPD 10/20 Terminal. Verify that the site contains a 115 VAC, 60 Hz, 3 wire (hot, common and ground) connector and a cable for connecting the Terminal to the selected communications device, such as a modem. This cable is supplied by INCOTERM at the customer's request.

## 2.4 INSTALLATION

On-site installation of the SPD 10/20 Terminal requires connecting the cables to the rear of the Terminal, and to external equipment. As indicated in Table 2-1, these instructions are directed toward initial Product Installation.

## 2.4.1 Cabling of Product 005, Model 00010

The SPD 10/20 Terminal, Model 00010 configuration consists of a Master Terminal and an Auxiliary Terminal. Each Terminal has a Keyboard Controller, Video Display and Keyboard input unit; however, both Terminals share a single Processor that is contained in the Master unit. Figure 2-8 is a cabling diagram for the Model 00010.

The following instructions define the cable connections required to install an SPD 10/20 Terminal in the Product 005, Model 00010 configuration. Throughout the entire cabling procedure observe proper cable dressing for professional final appearance. Secure each cable with connector hood securing screws. Proceed as follows to install the cabling.

- (a) Position the INCOTERM equipment on the desk or table designated by the customer.

- (b) Position a Keyboard in front of the Master Display and connect the Keyboard cable (male end) to the Display rear connector number 1. Route the female end under the

SHIPPING MEMO NO. 11114

HAYES MEMORIAL DRIVE, MARLBOROUGH, MASS. 01752 617-481-2000 TELEX 84-8402

SHIP TO FRIENDSHIP ARPORT Baltimore, Rayland Hold for Mick-up by Jack Colburn Star Incoterm Corporation

| PURCHASE ORDER NO. SALES C |                  |       | SALES            | DRDER NO. DATED                    |                             | DEFECTED MAT'L. REPORT NO. |                                                               |                           |       |

|----------------------------|------------------|-------|------------------|------------------------------------|-----------------------------|----------------------------|---------------------------------------------------------------|---------------------------|-------|

| DATE                       | OF SHIPPER SHIP  | NOT   | LATER THAN       | TRANSPORTATION CHARGES             | SHIPPED VIA<br>Air Freight  |                            | WEIGHT                                                        | DATE SHIPPE               | . BY  |

| ITEM                       | QUANTITY ORDERED | $\ge$ | QUANTITY SHIPPED |                                    | DESCRIPTION                 |                            |                                                               | UNIT COST                 | TOTAL |

| 1.                         |                  |       | 2                | SPD 10/20 Data Te<br>Serial #'s 13 |                             |                            |                                                               |                           |       |

| 2.                         |                  |       | 2                | Keyboards Model<br>Serial #'s 173  | L #2-70 <b>2</b><br>3 & 108 |                            |                                                               |                           |       |

| 4                          |                  |       | 2                | Keyboard Cables                    |                             |                            |                                                               |                           |       |

| 4.                         |                  |       | 2                | Power Cords                        |                             |                            |                                                               |                           |       |

| 5.                         |                  |       | 1                | Paper Tape Reader<br>Serial #117   | r. Model #3-701             |                            |                                                               |                           |       |

| 6.                         | ·                |       | 1                | Paper Tape Cable                   |                             |                            |                                                               |                           |       |

|                            |                  |       |                  | NOTE: Supplied b                   | by Marketing for            | DEMO                       |                                                               |                           |       |

|                            |                  |       |                  |                                    |                             |                            |                                                               |                           |       |

|                            |                  |       |                  |                                    |                             |                            |                                                               |                           |       |

|                            |                  |       | ·                |                                    |                             | TRANS<br>INSPEC<br>PACKA   | MATERIAL<br>PORTATION<br>CTION CHAF<br>GING CHAF<br>MISC. CHA | I CHARGES<br>RGES<br>RGES |       |

| F                          | igure 2-7.       | S     | ample Shippin    | ng Memo                            |                             | TOTAL                      | DEBIT                                                         |                           |       |

THIS IS NOT A PURCHASE ORDER

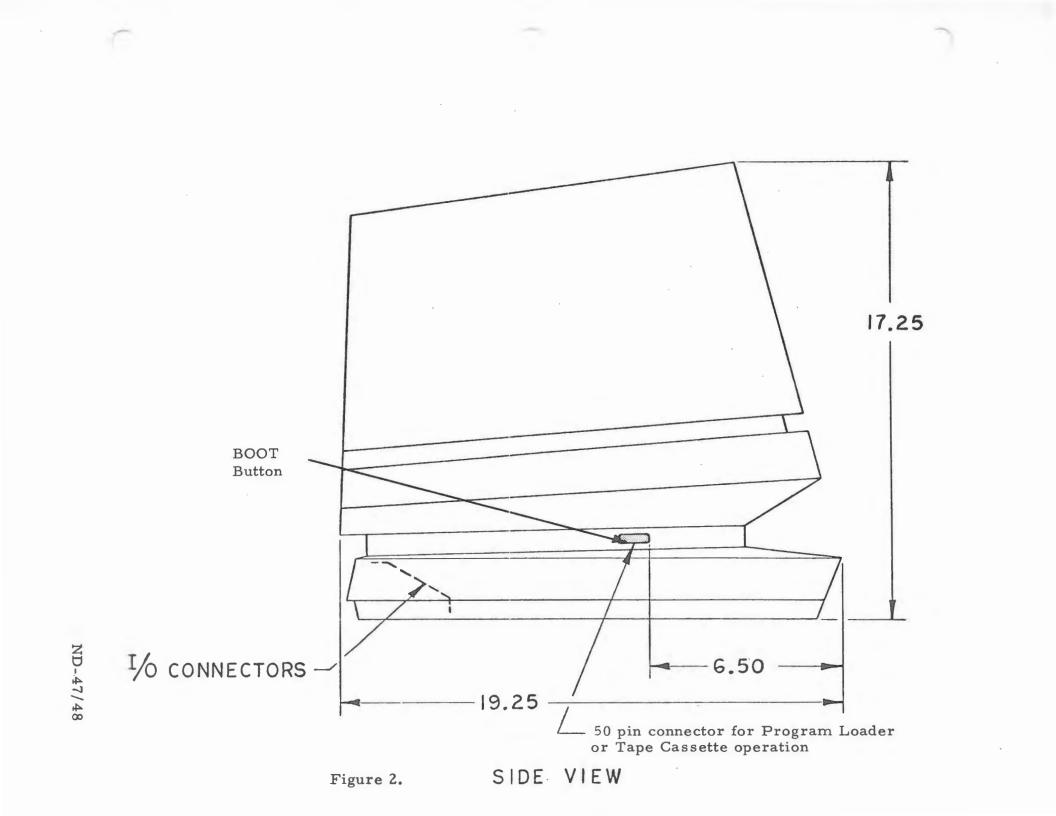

\*Connector Number 9 is Wired Directly to the I/O Bus and is Generally Used for Program Loading.

Figure 2-8. Cabling Diagram for Model 00010

Master Display then to the Keyboard. Also on the Keyboard end, locate the white 9-pin nylon plug and connect it to the nylon connector (this provides power to the Master Keyboard lamps).

- (c) Position a Keyboard in front of the Auxiliary Display and connect the Keyboard cable (male end) to rear connector number 3 of the Master Display. Route the female end under the Auxiliary Display, then connect it to the Keyboard. Also on the Keyboard end, locate the white 9-pin nylon plug and connect it to the nylon connector (this provides power to the Auxiliary Keyboard lamps).

- (d) Connect Auxiliary Display connector number 7 to Master Display connector number 7, utilizing the double female cable provided.

- (e) Connector number 2 is dedicated to communications I/O operations. Connect the cable to the specified communications device.

- (f) Connector number 9 is wired to accept Program Loader inputs. If the Loader is used, connect 50-pin female connector from the Loader unit to connector number 9.

- (g) Tighten any loose cabling hardware and check interlock switch for proper engagement with actuating arm.

- (h) Check customer ac line for proper voltage and ground.

- (i) Attach twist lock ac line cords to both displays.

- (j) Plug line cords into outlet.

#### 2.4.2 Cabling of Product 006, Model 00011

As derived from Table 2-1, the circuit board complement in this model is identical to the 00010 model. The prime difference is the connector pin compatibility on the Memory Electronics and Data Flow Boards, which are not interchangeable between models. This difference is of no importance during installation. Refer to Figure 2-8 and follow the cabling instructions in paragraph 2.5.1.

## 2.4.3 Cabling of Product 005, Model 00014

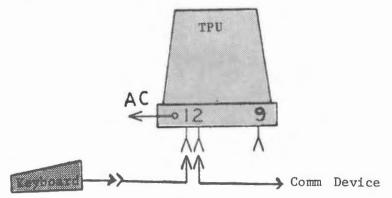

Unlike Models 00010 and 00012, the Model 00014 is not configured to operate with the auxiliary capability. Installation cabling is illustrated in Figure 2-9.

Figure 2-9. Cabling Diagram for Model 00014

Proceed as follows to install the cabling.

(a) Position the INCOTERM equipment on the desk or table designated by the customer.

2-13

- (b) Position the Keyboard in front of the Terminal and connect the Keyboard cable male end to the Display rear connector number 1. Route the female end under the Display then to the Keyboard. Also on the Keyboard end, locate the white 9-pin nylon plug and connect it to the nylon connector (this provides power to the Keyboard lamps).

- (c) Connector number 2 is dedicated to communications I/O operations. Connect the cable to specified communications device.

- (d) Connector number 9 is wired to accept Program Loader inputs. If the Loader is used, connect 50-pin female connector from the Loader unit to connector number 9.

- (e) Tighten any loose cabling hardware and check interlock switch for proper engagement with actuating arm.

- (f) Check customer ac line for proper voltage and ground.

- (g) Attach twist-lock ac line cord to Display.

- (h) Plug line cord into outlet.

# CHAPTER III

#### OPERATION

## 3.1 GENERAL INFORMATION

A Power On switch and a keyboard are the only controls required to operate the SPD 10/20 Display Terminal. The Power On switch is located on the under side of the display at the front right. It is a rotary switch that is also used to adjust the brightness of the display screen.

The keyboard contains the keys, controls and indicators necessary to operate and monitor the display. It is connected to the display with a ten-foot cable that allows convenience in positioning the keyboard. The operator uses the keyboard to input data to the Terminal Processor Unit via an I/O interface called a Keyboard Controller. The formatting of input data and operation of the special function keys are predetermined by the stored software program.

## 3.2 KEYBOARD

## 3.2.1 Introduction

The stored software program determines the functions that the operator can enable via the keyboard. The programs vary with customer applications so that it is not possible to describe a standard keyboard configuration. The keyboard described is for a specific application but it can be considered typical for this discussion.

## 3.2.2 Key Functions

All keyboards conform to a single physical layout (see Figure 3-1). The center section consists of four rows of keys and a space bar. The bottom row contains 12 keys and the other three rows contain 13 keys each. Twelve function keys are located on each side of the center section. Unused keys are not engraved.

The center section of the keyboard contains the alphanumeric keys and is arranged essentially the same as a standard electric typewriter keyboard. The alphabet is used in upper case only. The SHIFT key has no effect on these characters. Other keys in this group have both upper and lower case characters. They must be used in conjunction with the SHIFT key to obtain the upper case character. When a key is depressed, the character engraved on its top is displayed on the CRT at the cursor location.

The special keys are described below.

### DATA CONTROL KEYS

- MSG Requests a waiting processor message when MSG WAITING indi-WAITING cator is lit. When this key is depressed, the keyboard is locked until completion of message.

- TRANS Causes the message displayed on the CRT, starting from the START OF ENTRY symbol ▷ and continuing forward to the cursor, to be transmitted to the processor. If there are multiple ▷ symbols displayed, transmission begins at the nearest ▷ to the left of the cursor. If no ▷ symbols are displayed, transmission begins at line 1, character 1 position. Keyboard is locked until message transmission is completed.

- RESET Causes the keyboard to unlock and should be used with discretion to prevent interruption of message transmission and receipt.

- PRINT Causes the message displayed on the CRT, starting from the symbol and continuing forward to the cursor, to be printed on the locally attached output printer. If there are multiple ▷ symbols displayed, printing begins at the nearest ▷ symbol to the left of the cursor. If no ▷ symbols are displayed, printing begins at the home position. Keyboard is locked until printing is completed.

- TABInserts a TAB STOP character in the memory position occupiedSETby the cursor. The cursor will automatically move one positionto the right, after tab is set.

B2114-18

Figure 3-1. Typical Keyboard Arrangement

3-3

#### EDITING KEYS

Editing keys are used to make changes in the text message prior to transmission. The cursor must be at the character position where the action is to be taken; viz., deleted, inserted or erased.

ERASE Erases and enters spaces in all character positions including END the cursor position to the end of the display. DISPLAY

ERASE Erases and enters spaces in all character positions from and in-END cluding the cursor position to the end of that line. LINE

IN DISPL DELETE IN LINE Uppercase (depress SHIFT key) operation of this key causes all characters in the display to the right of the cursor to move left one position. The original character at the cursor position is deleted and a space is inserted into the last character position of the display. This key is pressed once for each character deleted.

> Lowercase operation of this key causes the characters in the line to the right of the cursor to shift left one position. The original character at the cursor position is deleted and a space is inserted into the last character position in the cursor line. This key is pressed once for each character to be deleted.

IN DISPL Uppercase (depress SHIFT key) operation of this key causes all INSERT the characters in the display from and including the cursor position to move right one position. A space is inserted in the cursor position and if a character is moved out of the last position of the display, it is discarded.

> Lowercase operation of this key causes all the characters in the line from and including the cursor positions to move right one position. A space is inserted in the cursor position and if a character is moved out of the last position of the line it is discarded.

Warning: When a space or character is inserted in the cursor position, causing an overflow in the display, the last character(s) will be discarded.

CHAR Causes the character at the cursor position to be deleted, insert-ERASE ing a space in lieu of the character. The cursor will not move.

## CURSOR CONTROL KEYS

The cursor symbol **M** is always present and indicates where the next keyboard or processor generated character will appear. These keys are nondestructive. If the key is pressed momentarily, it causes the cursor to move forward one position. If the key is held down, the function is repeated at a rate of approximately 10 cycles per second. If the cursor is at the last character position in a line, it will step to the first position of the next line. If the cursor is in the 64th position of the line 30 (line 15 if dual display), it will move to position one of the first line.

If the key is pressed momentarily, it causes the cursor to move backward one position. If the key is held down, the function is repeated at a rate of approximately 10 cycles per second. If the cursor is at the first character position in a line, it will step to the last character position of the previous line. If the cursor is in the first position of line 1, it will move to the last position of line 30 (line 15 if dual display).

If the key is pressed momentarily, it causes the cursor to move up one line in the same character position. If the key is held depressed, the function is repeated at a rate of approximately 10 cycles per second. If the cursor is in the top line, it will step to the bottom line, maintaining the same character position.

If the key is pressed momentarily, it causes the cursor to move down one line in the same character position. If the key is held depressed, the function is repeated at a rate of approximately 10 cycles per second. If the cursor is in the bottom line, it will step to the top line, maintaining its character position.

CURSOR Causes the cursor to move to the first character position on the display (upper left-hand corner). HOME

#### SPECIAL KEYS

START Depress prior to entering input. Causes the start of entry sym-OF bol  $\triangleright$ , to be displayed on the CRT. When the message is completed, ENTRY all data from the  $\triangleright$  to the cursor is transmitted.

- TAB This special cursor-positioning key moves the cursor forward until a special character, set by the TAB SET key, is detected. The cursor will stop either one space beyond the tab character or at the end of the display if no tab character is found.

- SPACE Pressing this cursor positioning bar places a space in the current cursor position and moves the cursor one character position to the right. If the cursor is in the last position in a line, it moves to the first character position in the next line.

- RETURN Occupies the position normally occupied by the carriage return key on the standard electric typewriter keyboard. Pressing this key causes the cursor to move to the first character position in the next line.

SHIFT This key places the keyboard in the uppercase mode. Depression LOCK of this key causes the SHIFT LOCK indicator light to turn on. A subsequent depression of the SHIFT LOCK key returns the keyboard to the normal mode and turns off the SHIFT LOCK indicator light.

Also used in conjunction with DELETE and INSERT IN DISPLAY (see Editing Keys).

### 3.2.3 Indicator Functions

Eight indicator lights are located on the keyboard. They are arranged in a row in the top center position. The indicators are program controlled and are not actuated by the keyboard electronics.

## STATUS INDICATOR LIGHTS

MSG When the processor has an unsolicited message for display, this WAITING light goes on. The indicator remains lit until the MSG WAITING key is depressed to request the message.

WAIT This indicator light comes on while a message is being transmitted to or received from the processor. In addition, the keyboard remains locked for the entire transmission time. The keyboard is locked whenever the TRANSMIT or PRINT key is depressed and remains locked until a valid text message or print complete signal is received. The processor can effect a keyboard lock by inserting a lock code in a message.

MSG Lights while text is being received and is automatically turned off INCOMPL when communications error checks are satisfied.

SHIFT This indicator lights when the SHIFT LOCK key is depressed and LOCK goes off when the SHIFT LOCK key is depressed a second time.

#### 3.3 INITIAL TURN ON AND CHECK OUT

## 3.3.1 Initial Turn On Procedures and Indications

After installation, activate the SPD 10/20 Terminal by turning on the rotary power switch. The CRT should illuminate approximately 30 seconds after the switch is turned on. The switch can be rotated to control the screen brightness. Screen illumination (raster) indicates that ac power is applied to the Terminal. Proper CRT operation is verified by horizontal and vertical synchronization of the raster.

Assuming that the Terminal contains a stored program, type a few characters on the keyboard. The characters and the cursor should be displayed on the CRT which confirms that the power supply is operating and the Terminal electronics appear normal. Exercise each alphanumeric key by depressing it twice in succession. Observe that the displayed data is in the form QQWWEE, etc. Erase the screen and type a few lines of text. Exercise the editing keys and other special function keys and observe the screen for proper operation. Exercising the keyboard in this way indicates normal operation of some of the Terminal circuitry; particularly, that contained on the Keyboard Controller board. If the installation contains an Auxiliary Terminal, exercising both keyboards checks out the Split Screen Controller as well.

The Communications Controller board is checked by connecting the Terminal to a communications device and performing a dynamic test. Confirm that the communications device and its associated cable are troublefree prior to testing.

## 3.3.2 Programmed Operation

If the initial turn-on indications and responses are satisfactory, final checkout is performed by operating the Terminal under control of the customer's software program.

The program can be loaded with the INCOTERM SPD-L Program Loader using the validated tape supplied with the Terminal. Refer to the SPD-L Program Loader Section in the Peripheral Manual for details of operation.

If problems are encountered during programmed operation or initial turn-on, refer to Chapter 6, Maintenance, and Chapter 5, Theory of Operation.

(

## CHAPTER IV

### SYSTEM DESCRIPTION

#### 4.1 INTRODUCTION

The SPD 10/20 is a complete unit that contains all the hardware necessary to perform as a remote alphanumeric and/or point-plot graphic display. It interfaces with all common communications equipment through standard modems. It also interfaces with the INCOTERM peripheral devices: SPD-L Program Loader, SPD-P Printer, SPD-M Multiplexer and the SPD-T Tape Cassette. These devices are briefly described in Chapter I. Detailed information can be obtained from the Peripheral Technical Manual associated with each device. System configuration varies with each application; however, a brief discussion of the three minimum configurations (single, dual and quad) is found in Chapter I.

## 4.2 SYSTEM FUNCTIONAL DESCRIPTION

### 4.2.1 General Information

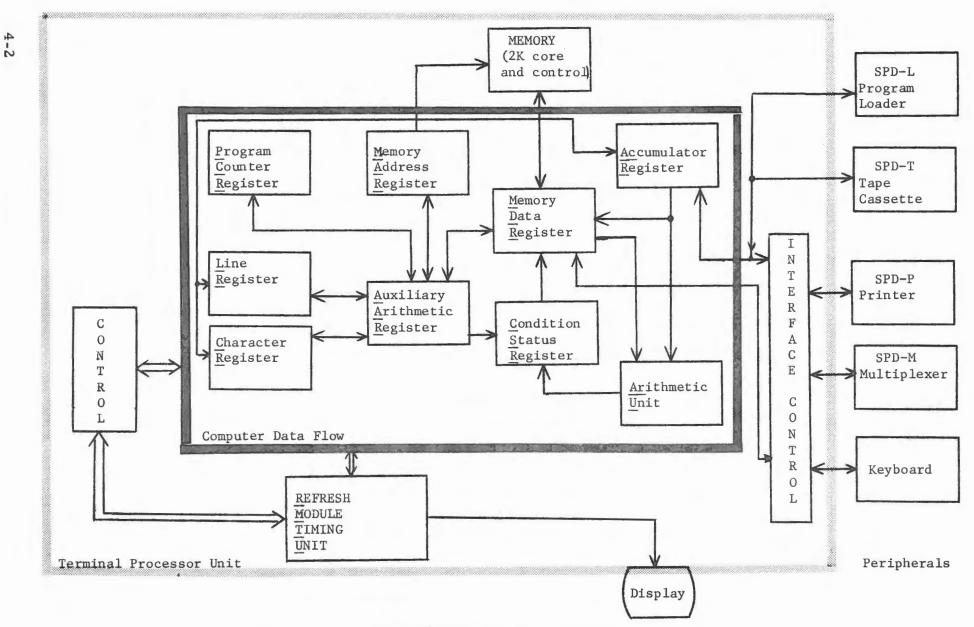

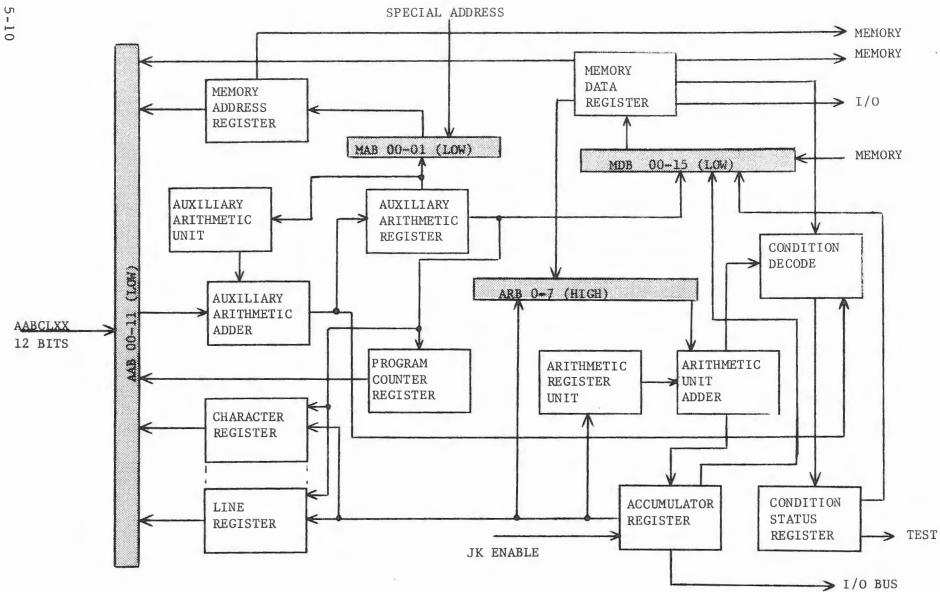

The SPD 10/20 Terminal consists of the Terminal Processing Unit (TPU), Interface Controllers, CRT Display Unit and Keyboard Unit. The keyboard is considered as part of the Terminal. Figure 4-1 is a simplified system block diagram.

The Terminal Processing Unit is physically constructed of five printed circuit boards which are identified as memory electronics, memory stack, data flow, control, and refresh module and timing. In Figure 4-1, both

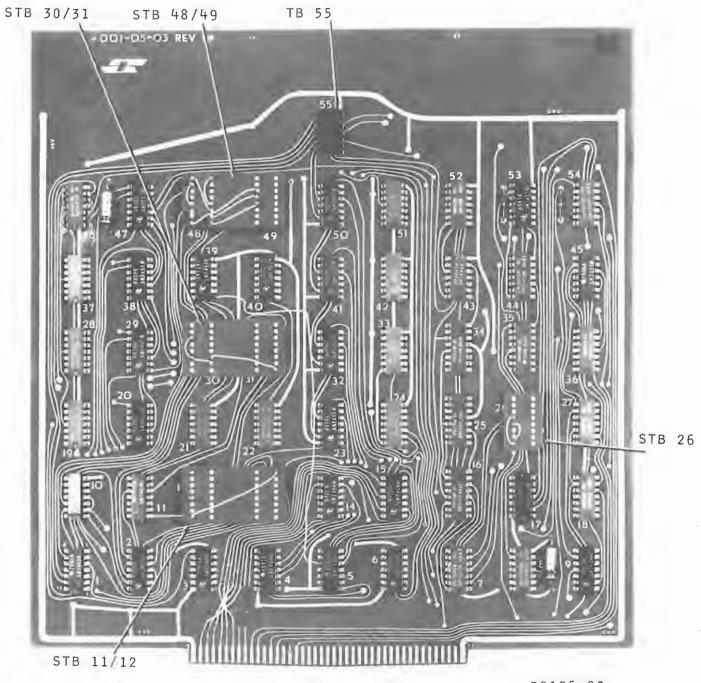

Figure 4-1. SPD 10/20 Stored Program Display System

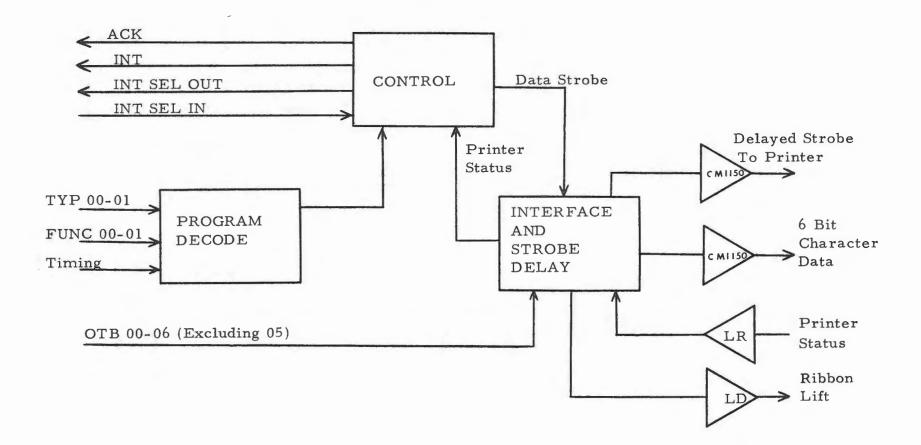

memory boards have been combined functionally; the Data Flow has been reduced to show the register detail in a system concept. The functional units that are contained on these boards have been identified to show the basic data flow and to introduce the reader to the terminology used in Chapter V, Theory of Operation. The illustration shows a Keyboard, SPD-P Printer, SPD-M multiplexer, SPD-LProgram Loader and SPD-T Tape Cassette connected to the Terminal. Each device except the SPD-L and SPD-T require a plug-in Controller to interface with the Terminal. Figure 4-2 shows the printed circuit board arrangement and identification.

## 4.2.2 Terminal Processing Unit

1

1. Computer Data Flow (See Figure 4-1)

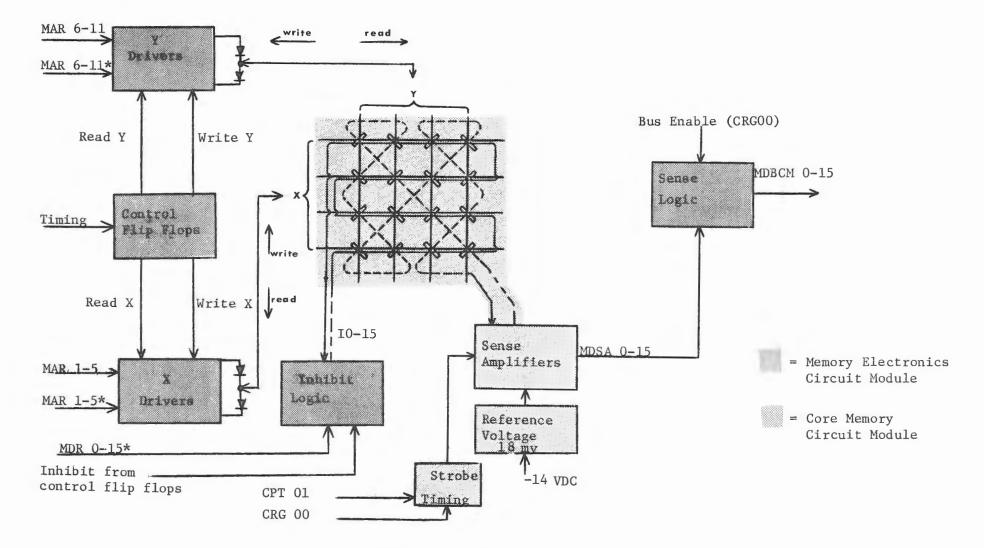

<u>Memory</u>: The SPD 10/20 utilizes a ferrite core coincident-current memory organized in a 3D-4 wire configuration. The memory capacity is 2048 words of 16 bit length (referred to as a 2K x 16 memory). Physically, each bit plane consists of a 64 x 32 core matrix. Sixteen planes are mounted on a circuit board in a 4 x 4 arrangement. The memory functional layout is discussed in paragraph 4.

Memory Data Register (MDR): A 16-bit register which buffers all data to and from the memory. The contents of this register are also available to the Display Subsystem.

<u>Memory Address Register (MAR)</u>: A 12-bit register which stores the address of the memory byte. Control of this register is also possible through the Display Subsystem.

Program Counter Register (PCR): A 12-bit register which contains the address of the next instruction to be executed. The least significant bit is always zero.

Accumulator (ACR): An 8-bit register which contains the data for the output bus and receives data from the input bus. It is also the primary arithmetic and logical register of the processor.

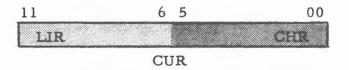

Cursor Register (CUR): A 12-bit register which controls the position of the cursor on the display. It can also be used in certain load, store, and arithmetic operations.

B2102-6

# Figure 4-2. Circuit Board Identification and Location

Character Register (CHR): The least significant six bits of the cursor register which represents the cursor location on a line.

Line Register (LIR): The most significant six bits of the cursor register which represents the number of the line on which the cursor is displayed.

Cursor Register Layout

Condition Status Register (CSR): This 3-bit register stores the status of all arithmetic operations.

| 02            | 01                       | 00 |                                              |  |

|---------------|--------------------------|----|----------------------------------------------|--|

| NG            | EQ                       | ·  | 0                                            |  |

| Negative (NG) |                          | 0  | nificant bit of the arith-<br>peration is 1. |  |

| Equal (EQ)    |                          |    | zero after an Arithme-<br>ry Arithmetic Unit |  |

| Carry Out (C) | Set on an o<br>ARU opera |    | condition from AAU or                        |  |

|               |                          |    | <i>c</i> • • • 1                             |  |

Arithmetic Unit (ARU): This 8-bit unit performs arithmetic and logic operations such as add, subtract, and, or.

Auxiliary Arithmetic Unit (AAU): This 12-bit unit provides capability for +1, +2, +4, -1 and comparison operations on a word basis.

Input Data Bus (IDB): This 8-bit bus consists of eight lines which transfer data from an I/O device to the accumulator (ACR).

Output Data Bus (ODB): This bus consists of eight lines which transfer data from the accumulator (ACR) to an I/O device.

Peripheral Address Bus (PAB): This bus transmits the address and function command for a selected peripheral directly to the device. Sixteen lines are used for the address and four bits are used to define the function to be performed by the peripheral device. The information is obtained as a decoded output from the Memory Data Register.

2. Control

The SPD 10/20 control electronics are contained on a single printed circuit board. Numerous control functions are provided by the interaction of system timing phases and extensive signal gating. A primary function is the decoding of the operation code and subsequent directing of the specified instruction. The State Counter and Real Time Clock are located on this board.

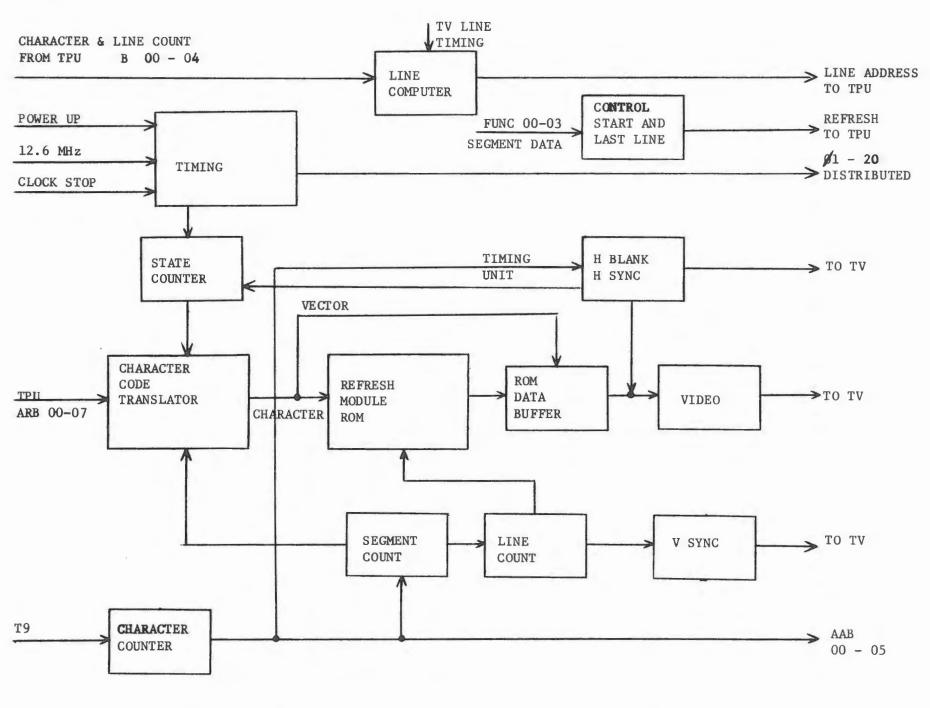

3. Refresh and Timing

The refresh and timing circuit board performs two major functions: one is the generation of a system timing chain; and the other is the processing and interfacing of data from the TPU to the CRT display. Circuits are provided to compute the CRT line number and character position on a line. The selected character is converted to a  $7 \times 10$  dot matrix by the read-only memory which modulates the CRT video circuit and displays the character on the screen. The displayed character is refreshed at a rate that prevents image flickering.

4. CRT Display Unit

The CRT display is a commercially purchased (Sylvania) TV monitor. It is completely self-contained and has a viewing area that measures 9-1/2 inches wide by 7 inches high. In a single SPD 10/20 configuration, the display format consists of 30 lines of 64 characters each. In a dual SPD 10/20 configuration, both screens display 15 lines of 64 characters each.

# 4.2.3 Interface Control

Each communications line and peripheral device driven by the SPD 10/20 requires an associated controller to provide the interface between the external device and the TPU. Four standard controllers are available. Each one is self-contained on a plug-in printed circuit board. The SPD 10/20 can accommodate a maximum of eight Controllers, all under TPU control. Table 4-1 lists the Controllers by type, function and external device controlled.

| Controller   | Function                                                                                                                                                                                          | External Device                                                                                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Keyboard     | ASCII interface with SPD 10/20<br>keyboard. (Two required for<br>auxiliary operation.)                                                                                                            | Keyboard                                                                                                                                        |

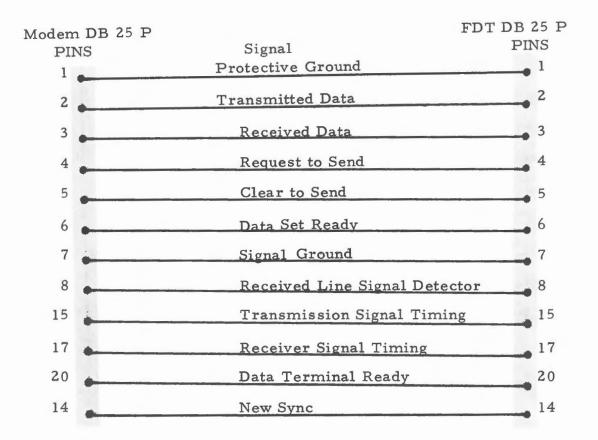

| Asynchronous | (EIA) Standard RS-232-C inter-<br>face for communicating with<br>standard line modems. One<br>controller for half duplex. Two<br>controllers for full duplex.<br>Operation is 50 to 2400 Baud.    | SPD-M Multi-<br>plexer, Data-<br>speed Service,<br>Teletype, TWX,<br>Telex, Honey-<br>well Data Sta-<br>tion, SPD-P<br>Printer,<br>Remote Load. |

| Synchronous  | (EIA) Standard RS-232-C inter-<br>face for communicating with<br>standard line modem. One con-<br>troller for half duplex. Two<br>controllers for full duplex.<br>Operation is 1200 to 4800 Baud. | Univac DCT<br>2000, IBM<br>2780, RCA<br>70/740, Data-<br>term, Remote<br>Load.                                                                  |

| Split Screen | Used with Auxiliary Display<br>to provide Master Display<br>time sharing.                                                                                                                         | SPD Auxiliary<br>Terminal.                                                                                                                      |

## Table 4-1. SPD 10/20 Controllers, Related Functions and External Devices

# 4.3 ADDRESSING AND INSTRUCTION FORMATS

## 4.3.1 Introduction

The purpose of this paragraph is to provide a fundamental discussion of the addressing and instruction formats used with the SPD 10/20 Terminal. Refer to the SPD 10/20 Programmers' Reference Manual for a detailed discussion of this subject plus a complete listing of instruction formats, operation codes and hexadecimal function codes.

## 4.3.2 Hexadecimal Notation

In programming the SPD 10/20, memory addresses and instruction codes are listed in the hexadecimal notation. It is a convenience, like shorthand, to express a code as four hexadecimal symbols rather than a string of 16 binary symbols (1's and 0's).

Any positional number system can be defined by its base (radix). The base is the number of unique symbols that can occupy a position in the number system. For example, the binary system has two symbols (base 2); the octal system has eight symbols (base 8); and the decimal system has ten symbols (base 10). The hexadecimal system has 16 symbols, so it is a base 16 system. The symbols are: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E and F (see Table 4-2).

|         |        | Hexadecimal |         |  |  |

|---------|--------|-------------|---------|--|--|

| Decimal | Binary | Symbol      | Spoken  |  |  |

| 0       | 0000   | 0           | Zero    |  |  |

| 1       | 0001   | 1           | One     |  |  |

| 2       | 0010   | 2           | Two     |  |  |

| 3       | 0011   | 3           | Three   |  |  |

| 4       | 0100   | 4           | Four    |  |  |

| 5       | 0101   | 5           | Five    |  |  |

| 6       | 0110   | 6           | Six     |  |  |

| 7       | 0111   | 7           | Seven   |  |  |

| 8       | 1000   | 8           | Eight   |  |  |

| 9       | 1001   | 9           | Nine    |  |  |

| 10      | 1010   | A           | Able    |  |  |

| 11      | 1011   | B           | Baker   |  |  |

| 12      | 1100   | C           | Charlie |  |  |

| 13      | 1101   | D           | Dog     |  |  |

| 14      | 1110   | E           | Easy    |  |  |

| 15      | 1111   | F           | Fox     |  |  |

Table 4-2. Decimal, Binary and Hexadecimal Equivalents

In converting from hexadecimal to decimal, the symbol represents both a coefficient and its position in the number (the exponent of the base). The exponent of the base (position) is determined by counting from right to left. For example, convert the hexadecimal number 4F2 to its decimal equivalent. Refer to Table 4-2 for the value of symbol F.

$$4F2 = 4(16^{2}) + F(16^{1}) + 2(16^{0})$$

$$= 4(256) + 15(16) + 2(1)$$

$$= 1024 + 240 + 2$$

$$= 1266$$

The Enable Interrupts (ENB) instruction is presented as an example of the convenience of coding in the hexadecimal system.

| 15  | 12     | 11  |      | 8 | 7 |    | 4   | 3   | 0   | Bit Number       |

|-----|--------|-----|------|---|---|----|-----|-----|-----|------------------|

| 1 1 | 00     | 0 0 | 0    | 0 | 0 | 0  | 0 0 | 0 1 | 1 0 | Binary Code      |

|     | С      |     | 0    |   |   |    | 0   |     | 6   | Hexadecimal Code |

| C   | harlie |     | Zero | ) |   | Ze | ero |     | Six |                  |

## 4.3.3 Word Formats

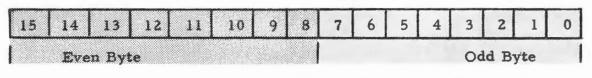

The SPD 10/20 addressing and instruction word is composed of an odd/ even byte pair, containing eight bits each. The word can be accessed by addressing either byte; however, for compatability, the address of the even byte should be used.

16 BIT WORD

There are three major instruction formats:

- 1. Non-memory reference

- 2. One word memory reference

- 3. Two word memory reference.

- 1. The non-memory reference instructions are a group of operations which contain their own data; therefore, they do not need to request data from memory. The non-memory reference data is made up of an op code and data which instructs the Terminal to operate on what is supplied in that data word.

- 2. The one word memory reference is an instruction in which a particular location in memory is fetched during the instruction cycle. If the resulting data is determined to be the effective data, the Terminal will operate on it during the execute cycle.

- 3. The two word memory reference only occurs when test jumps or test input-output is desired. The data is arranged such that the first word is used for operating instructions while the second contains address information.

# 4.3.4 Instruction Classes

The SPD 10/20 provides a repertoire of 58 instructions including:

- 16 data manipulation

11 cursor control

20 test and/or branch

6 input/output

4 miscellaneous

- 1. <u>Byte Class</u>: An op code instruction dictating action on the byte at the effective address. Actions are:

| Load    | Store | Add | Subtract |

|---------|-------|-----|----------|

| Compare | And   | Or  |          |

- 2. <u>Cursor Class</u>: The data in the cursor register (line and character taken together) can be loaded with the word at the effective address, stored at the effective address, or compared to the effective address.

- 3. <u>Increment Class</u>: The word at the effective address can be incremented by one, incremented by two, or decremented by one.

- 4. Jump Class: Provides for an unconditional jump to the effective word address or jump to a subroutine, in which case a return address is stored.

- 5. <u>Test Jump Class</u>: A test jump is two words long; the first contains operating data, the second contains address data. This instruction is conditional.

- 6. <u>Immediate Class</u>: The effective data is located in the odd byte of the instruction word.

- Input/Output Class: Provides device attention to I/O controllers and provides the necessary interface select and enabling data. Included in this class are Control, Read and Write with a conditional test for possible jump.

- 8. Operate Class: Enables a large majority of data movement within the Terminal's operating registers. Interface commands also form a part of this class.

## 4.3.5 Effective Address Calculation

An example of an effective address calculation is presented in this paragraph. The textual discussion is supported by diagrams of the instruction words.

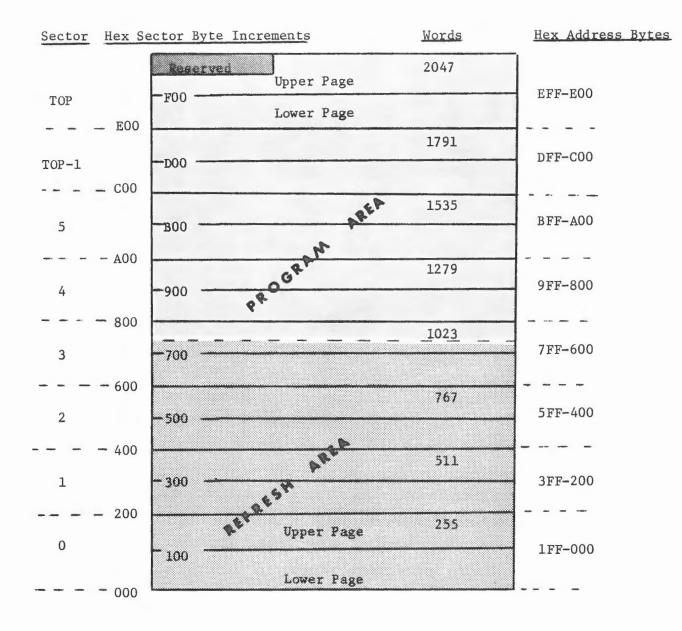

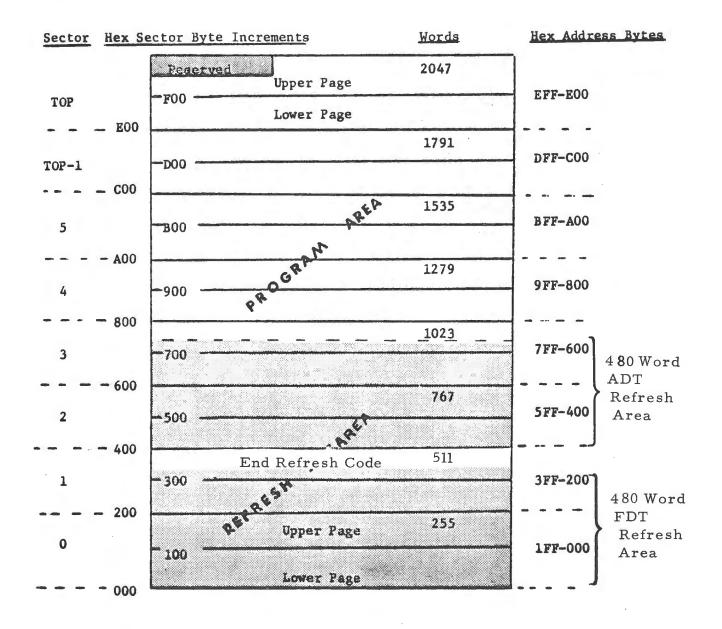

Prior to the discussion, it is necessary to explain the functional division of the core memory. Figure 4-3 shows the functional division of a memory bit-plane. Each plane contains 2048 locations (words). Information is transferred in and out of the memory as complete 16-bit words: that is, the identical core location in all 16 bit-planes. The memory is divided into eight sectors, each of which contains 256, 16-bit words or 512 bytes. Each sector is divided into an upper page and lower page of 128 words each. The highest numbered sector (7) is labeled TOP; sector 6 is labeled TOP-1. A 44 byte reserved area is contained in sector 7. Hex bytes 000 through 77F are reserved for refreshing displayed data. The remaining area is used for program storage.

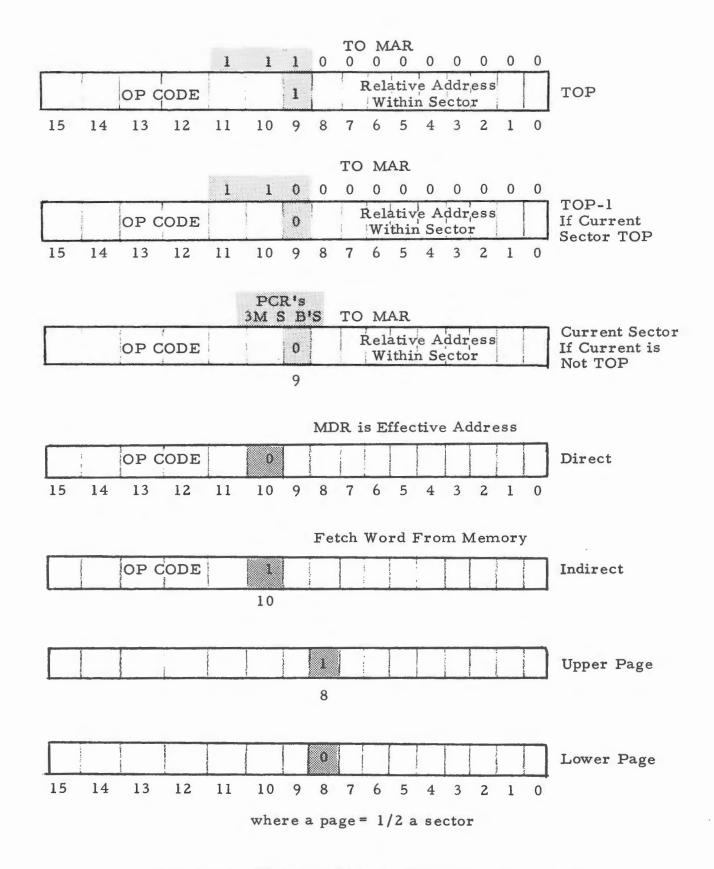

A discussion of a sample effective address calculation is presented below. The text is keyed to Figure 4-4 which shows the layout of the oneword memory reference instructions used in the operation. Bit identification is as follows:

| Bits 11 through 15: | Opcode                                                 |

|---------------------|--------------------------------------------------------|

| Bits 00 through 08: | Displacement (relative address)<br>with defined sector |

| Bit 10:             | Indirect addressing (0 = direct,<br>1 = indirect)      |

Figure 4-3. 2K Core Memory Layout

Figure 4-4. Effective Address Calculation Illustrated

| Bit 9: | Sector address<br>l = TOP sector<br>0 = Current sector if current sector<br>\$\neq\$TOP<br>0 = TOP-1 sector if current sector<br>= TOP |

|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| Bit 8: | Page identification (0 = Lower page,<br>1 = Upper page).                                                                               |

## Sample Effective Address Calculation (See Figure 4-4)

- 1. The sector bit (bit 9) is tested. If it is 1, the last sector of memory (TOP) has been referenced. The address of the top sector, linked with the instruction's displacement field, is loaded into the Memory Address Register (MAR). GO TO step (4).

- If the sector bit is not 1, test to see if the current sector is TOP. If so, the sector below TOP has been referenced (TOP-1). TOP-1 linked with the instruction's displacement field is loaded into the MAR. GO TO step (4).

- 3. If the current sector is not TOP, then the current sector has been referenced. Combine the sector bits of the Program Counter (PCR) with the instruction's displacement and load the result into the MAR. Note that the PCR still contains the address of the current instruction at this point.

- 4. The indirect bit (bit 10) is tested. If it is 0, there is no indirect addressing, and the MDR contains the true effective address. The instruction execute cycle is entered which uses this address. The least significant bit (LSB) of the effective address has been maintained for use in byte instructions.

- 5. Indirect addressing is indicated. The MAR is used to fetch an indirect address word from memory, which is loaded into the MDR. If the indirect bit (bit 15) of this word is 1, continue by a GO TO step (5). If it is 0, the MDR contains the true effective address. The instruction execution cycle is entered, which uses this address. The LSB of the effective address has been maintained for use in byte instructions.

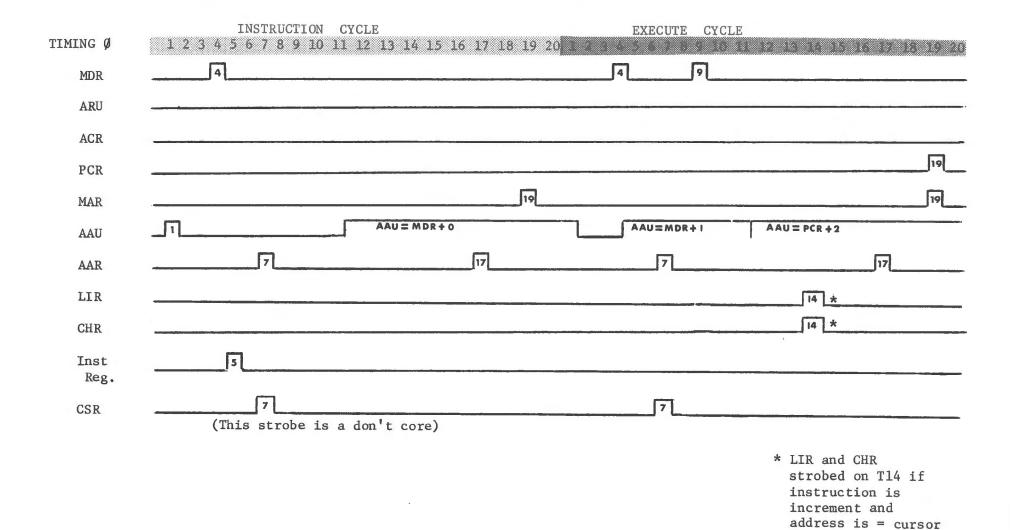

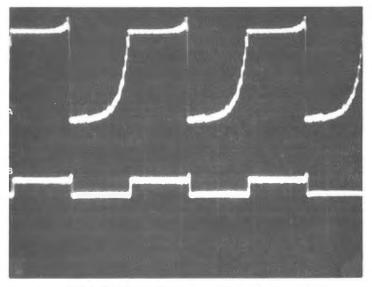

#### 4.3.6 Basic System Timing and Data Flow

The system timing is generated on the Refresh Module and Timing Unit circuit board. The system operates on two cycles, each of which is divided into 20 equal increments or timing phases. The instruction cycle is first, followed by the execute cycle. During the instruction cycle, an instruction is fetched during timing phases 1 through 10 and decoded during timing phases 11 through 20. During the execute cycle, the selected data is fetched during timing phases 1 through 10 and is operated on during timing phases 11 through 20.

The processing of a specific instruction (Increment and Store) is presented as a typical example of system activity with respect to timing. Obviously, each instruction requires a different data path within the TPU; however, some operations follow the same pattern, such as Memory Data Register strobe at time T4 and Program Counter Register update at time T19.

## Processing of Increment and Store Instruction

The purpose of an Increment and Store instruction is to retrieve data in a specific memory location, add 1 to it, and return it to the memory. Figure 4-5 is a timing diagram for this operation.

Activity starts at time T4 when a memory data word is strobed into the Memory Data Register (MDR). At the trailing edge of T5, the opcode portion is decoded and saved in the Instruction Register so that during the remainder of the operation the computer knows what it is supposed to do. The address portion of the word is taken from the MDR and after T11, enabled to the Auxiliary Arithmetic Unit (AAU) where zero is added to it, and it is loaded into the Auxiliary Arithmetic Register (AAR) at T17. At T19, the address is placed in the MAR, such that the MAR is pointed to the address which it is desired to increment. At this point, the instruction cycle has been performed and the execute cycle is entered.

Execute cycle time T4 enables the MAR Selected Data from the MDR to the Auxiliary Arithmetic Unit where it is incremented by one, and at T7, the result is placed in the Auxiliary Arithmetic Register. Also at T7 the CSR is set as required. At T9, the AAR data is placed in the MDR so that it can be written back into memory. The line and character are not important unless a cursor operation is involved. At this point, the data movement called for has been performed. All that remains is to up-date the Program Counter Register (PCR). After T11, the PCR is enabled to the Auxiliary Arithmetic Unit where a +2 is added to it (+2 because of byte orientation, two bytes per word). At T17, it is enabled to the Auxiliary Arithmetic Register. At T19 the PCR and MAR are updated, which finishes the operation.

Figure 4-5. System Timing Example, Increment and Store Instruction

.

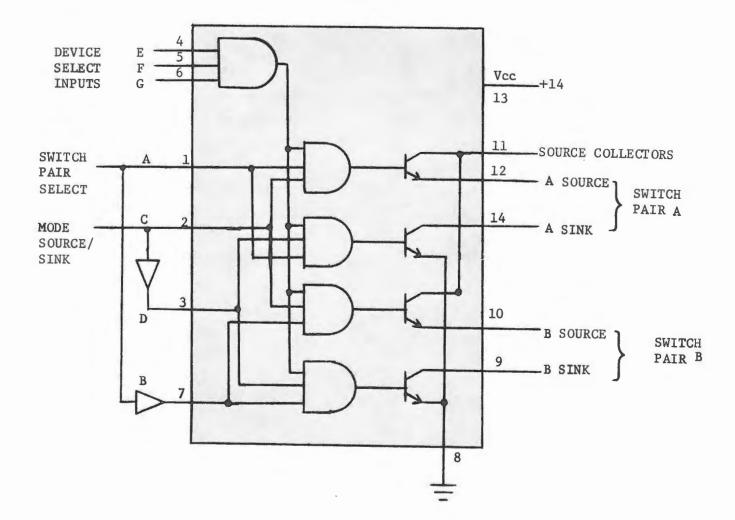

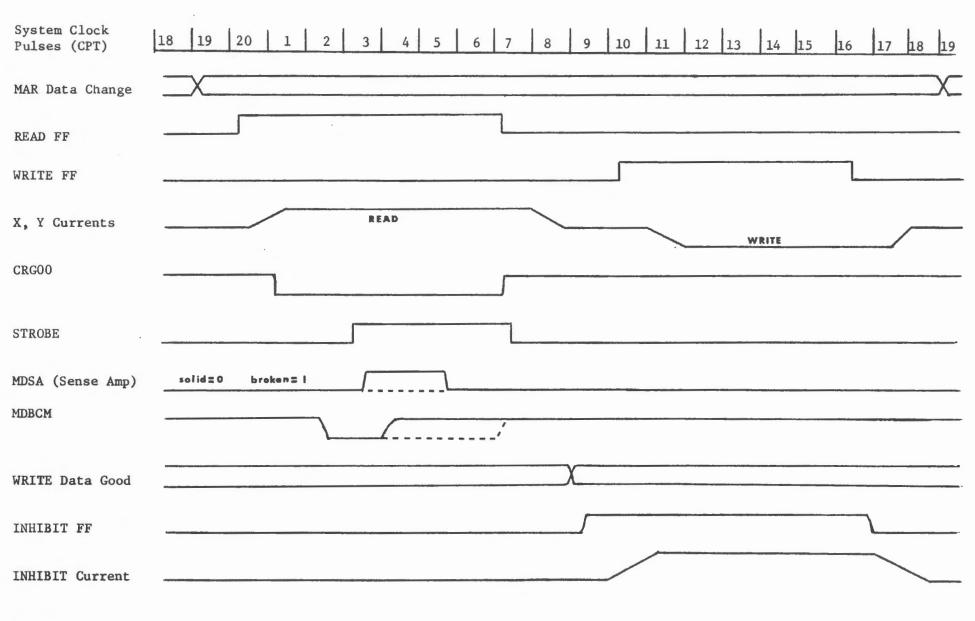

## CHAPTER V