GC30-3004-6 File No. S360/S370-09

IBM 3704, 3705-I, and 3705-II Communications Controllers Principles of Operation

Systems

# Preface

This reference publication contains the hardware operation and programming requirements of the IBM 3704 and the IBM 3705 Communications Controllers. The information applies to the IBM 3704, IBM 3705-I and 3705-II except where specifically noted.

The publication is intended for any user of a communications controller who is attempting to write or modify a 3704/3705 control program. The reader should have an understanding of basic data communication and a thorough knowledge of IBM System/360 and System/370 channel operations. The Introduction to the IBM 3704 and 3705-II Communications Controllers (GA27-3051) is a prerequisite publication. Related publications are the IBM 3705 Communications Controller Assembler Language manual (GC30-3003), the Synchronous Data Link Control General Information manual (GA27-3093), the Guide to Using the IBM 3704 Communications Controller Control Panel (GA27-3086), and the Guide to Using the IBM 3705 Communications Controller Control Panel (GA27-3087).

Other IBM publications concerning the communications controllers are identified and described in the *IBM System/* 370 Bibliography, GC20-0001.

This manual is divided into eleven chapters and three appendixes.

Chapter 1: Introduction

Provides a general description of the 3704, 3705-I, and 3705-II.

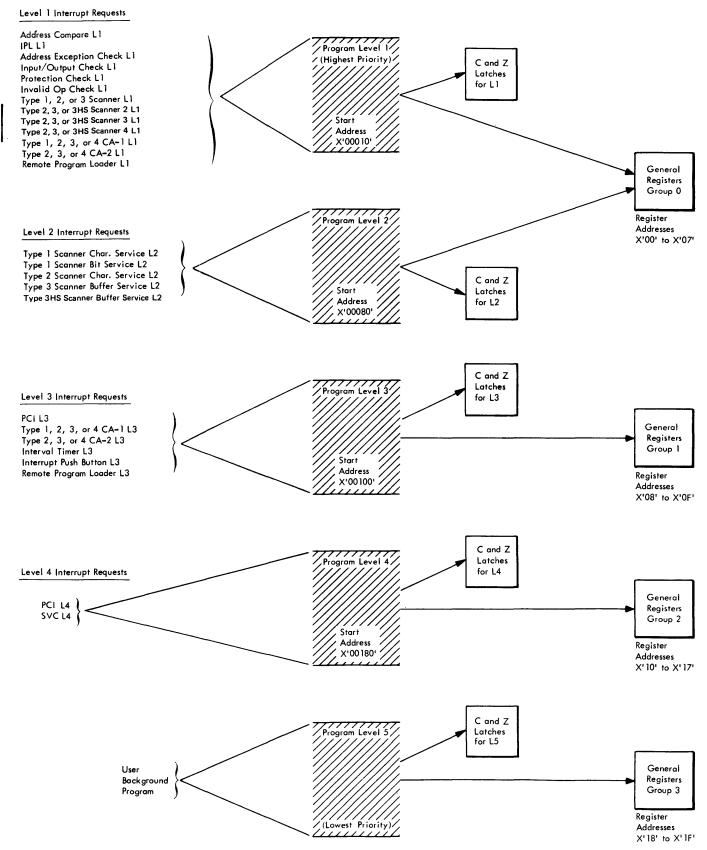

Chapter 2: System Structure Describes the registers, interrupt scheme, and levels of the control program.

Chapter 3: Storage and Line Addressing Describes the basic storage addressing procedure and the format for addressing the individual communication lines.

Chapter 4: Instruction Set Describes each of the 3704/3705 machine instructions with their format and condition codes.

Chapters 5 through 10: Describe the operation and programming requirements of the Central Control Unit, the Types 1, 2, 3, and 3HS Communication Scanners, and the Types 1, 2, 3, and 4 Channel Adapters.

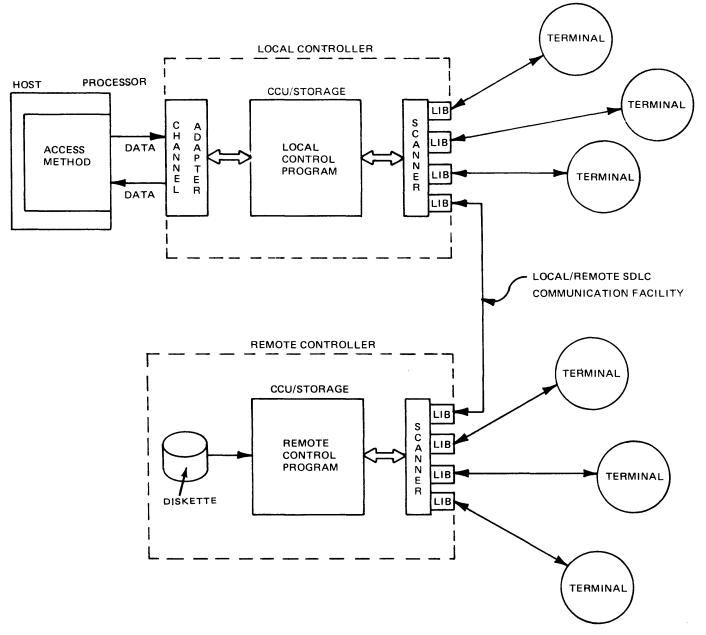

Chapter 11: Remote Communications Controller Describes the hardware and programming required to support a communications controller at a remote location.

The appendixes contain (A) External register functions, (B) Input/Output instruction bit definitions, and (C) Input/ Output instruction summary.

#### Seventh Edition (October 1979)

This is a major revision of and makes obsolete GC30-3004-5, and TNL GN30-3081. The Summary of Changes section describes the changes made in this edition.

Changes are periodically made to the information herein; before using this publication in connection with the operation of IBM systems or equipment consult the latest IBM System/370 Bibliography (GC20-0001) and associated Technical Newsletters, for the editions that are applicable and current.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Publications are not stocked at the address given below; requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Information Development, Department E02, P.O. Box 12195, Research Triangle Park, North Carolina, U.S.A. 27709. IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

# Contents

| Preface                                          |           |      |      |     |     |   |   |   |   |   |   |            |

|--------------------------------------------------|-----------|------|------|-----|-----|---|---|---|---|---|---|------------|

| Abbreviations                                    |           | •    | •    | •   | •   | • | • | • | · | • | • | vii        |

| Summary of Changes                               |           | •    | •    | •   | •   | • | • | • | · | · | · | ix         |

|                                                  |           |      |      |     |     |   |   |   |   |   |   |            |

| Chapter 1: Introduction .                        |           | •    | •    | •   | ·   |   |   |   |   |   | • | 1-1        |

| Host System Interface                            |           | •    | •    | •   | ·   | • |   |   | · |   | · | 1-1        |

| System Support Programs .                        |           | •    | •    | •   | •   |   |   | • | • | • | · | 1-1        |

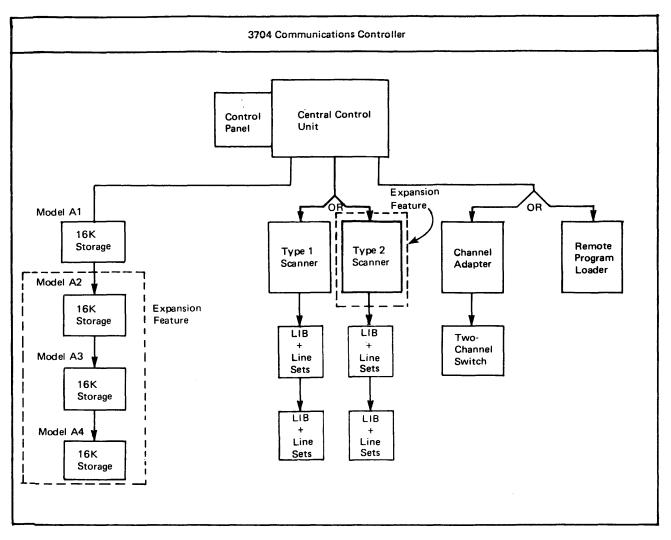

| 3704 Description                                 |           | •    | •    | •   | ·   | • | • | · | · | • | · | 1-1        |

| 3705 Description                                 |           |      | •    | •   | •   | • | • | • | • | · | · | 1-1        |

| Storage                                          |           |      | •    | •   | •   | • | • | • | · | ٠ | • | 1-4        |

| Central Control Unit                             |           |      | •    |     | •   | • | • | • | • | • | • | 1-4        |

| Adapters                                         |           | •    | •    | •   | •   | • | • | • | • | • | • | 1-4        |

| Channel Adapters                                 |           |      | •    |     | •   |   | • |   |   |   | • | 1-5        |

| Two-Channel Switch Fea                           | tu        | re   |      |     |     |   | • |   |   |   |   | 1-6        |

| Communication Scanners                           | S         |      |      |     |     |   |   |   |   |   |   | 1-6        |

| Attachment Bases                                 |           | •    |      |     |     |   |   |   |   |   |   | 1-12       |

| Line Interface Bases and Lin                     |           |      |      |     |     |   |   |   |   |   |   | 1-12       |

| Remote Communications Co                         |           |      |      |     |     |   |   |   |   |   |   | 1-12       |

| Remote Program Loader                            |           |      |      |     |     | : | • | : | : | : |   | 1-12       |

| SDLC                                             |           | •    | :    | •   | •   | : | • | • | : |   |   | 1-12       |

| General Programing Concept                       | ts        | •    | •    | •   | •   |   |   | • | : | : |   | 1-12       |

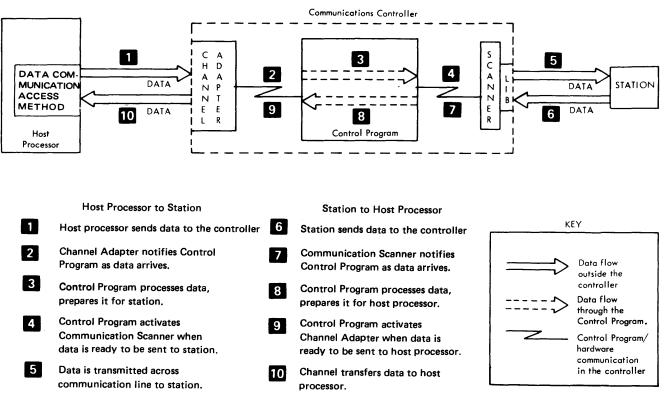

| System Data Flow                                 |           | •    | •    | •   | •   |   |   |   |   |   | • | 1-12       |

| System Data Flow Input/Output Instruction        |           | ·    | ·    | ·   | •   | · | · | • | · |   |   | 1-13       |

| Input/Output Instruction                         | ns        | ·    | ·    | •   | ·   | · | · | · | • | · | · | 1-13       |

|                                                  |           |      |      |     |     |   |   |   |   |   |   | <b>~</b> 1 |

| Chapter 2: System Structur                       |           |      |      |     |     | · | · | · | · | · | · | 2-1        |

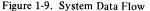

| Registers                                        |           | ·    | •    | ·   | ·   | • | • | · | • | · | · | 2-1        |

| General Registers                                |           | •    | •    | •   | •   | • | • |   | · | · | • | 2-1        |

| Instruction Address Regi                         |           |      |      |     |     |   |   |   |   |   |   | 2-1        |

| External Registers                               |           |      |      |     |     |   |   |   |   |   |   | 2-2        |

| Program Levels                                   |           |      |      |     |     |   |   |   |   |   |   | 2-2        |

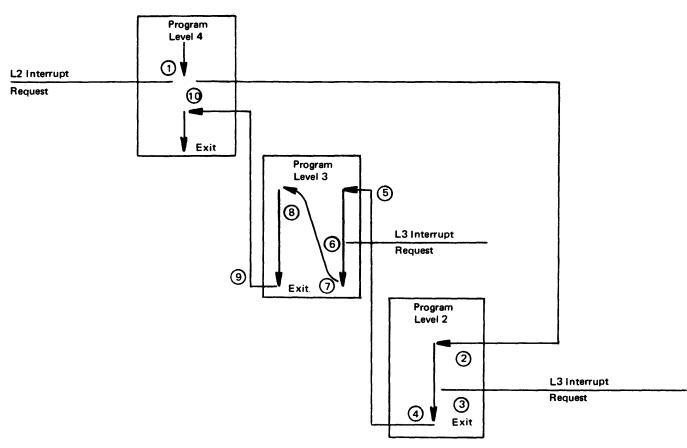

| Interrupts                                       |           |      |      |     |     |   |   |   |   |   |   | 2-2        |

|                                                  |           |      |      |     |     |   |   |   |   |   |   |            |

| Chapter 3: Storage and Line                      | e A       | ١dd  | ress | ing |     |   |   |   |   |   |   | 3-1        |

| Storage Addressing<br>Extended Addressing .      |           |      |      |     |     |   |   |   |   |   |   | 3-1        |

| Extended Addressing .                            |           |      |      |     |     |   |   |   |   |   |   | 3-1        |

| Interface Addressing                             |           |      |      |     |     |   |   |   |   |   |   | 3-2        |

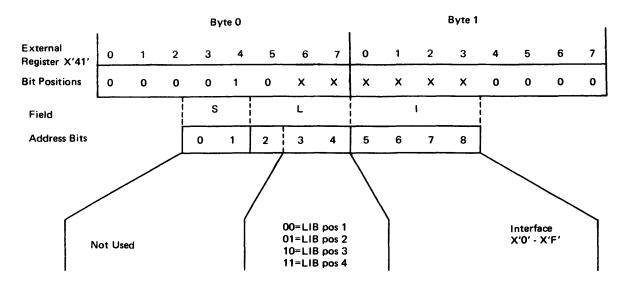

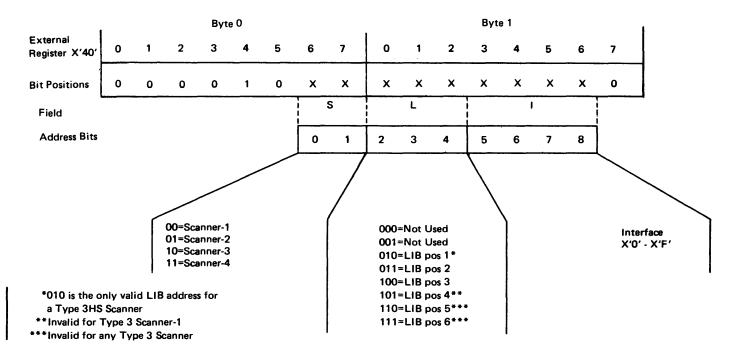

| LIB and Line Addressing .                        |           |      |      |     |     |   |   |   |   |   |   | 3-2        |

| 5                                                |           |      |      |     |     |   |   |   |   |   |   |            |

| Chapter 4: Instruction Set                       |           |      |      |     |     |   |   |   |   |   |   | 4-1        |

| Instruction Format                               |           |      |      |     |     |   |   |   |   | ÷ |   | 4-1        |

| Instruction Format<br>Instruction Operand Fields |           | ·    | •    | •   | :   |   | : |   | • | : |   | 4-1        |

| Immediate Operands                               |           | ·    | •    | •   | •   |   | : |   |   | : |   | 4-1        |

| Immediate Operands .<br>External Register Operar |           | ÷    | ·    | ·   | •   | · |   | · | · |   | · | 4-1        |

| General Register Operan                          | nus<br>de | ,    | ·    | ·   | ·   | · | · | ٠ | · | · | • | 4-1<br>4-1 |

| Europeian Register Operand                       | us        | •    | •    | •   | •   | · | • | • |   | · | · | 4-1<br>4-4 |

| Explicitly Addressed Op                          | era       | ınas | s in | 310 | rag | C | • | • | • | · | ٠ | • •        |

| Condition Latches                                |           | •    | ·    | •   | ·   | · | · | · | · | • | • | 4-5        |

| General Register Usage                           |           | ·    | •    | ·   | ·   | · | · | · | · | • | • | 4-5        |

| Instruction Descriptions .                       |           | •    | ·    | ·   | ·   | ٠ | · | · | ٠ | · | · | 4-5        |

|                                                  |           |      |      |     |     |   |   |   |   |   |   |            |

| Chapter 5: Central Control                       |           | nit  | ·    | •   | •   | · | · | • | • | · | • | 5-1        |

| CCU Registers                                    |           | •    | •    | •   | •   | • |   | • | • | • | · | 5-1        |

| CRC Register                                     |           | •    | •    |     |     |   |   |   |   |   |   | 5-1        |

| CRC Data Register                                |           |      |      |     |     |   |   |   |   |   |   | 5-1        |

| Display Register 1 (DR1)                         | )         |      |      |     |     |   |   |   |   |   |   | 5-1        |

| Display Register 2 (DR2                          |           |      |      |     |     |   |   |   |   |   |   | 5-1        |

| Lagging Address Register                         |           |      |      |     |     |   |   |   |   |   |   | 5-1        |

| Cycle Utilization Counte                         |           |      |      |     |     |   |   |   |   |   |   | 5-1        |

| Old-CRC Register                                 |           |      |      |     |     |   | · |   |   | • | ÷ | 5-2        |

| Operation Register (Op F                         |           |      | •    |     | :   | : | : | • | • | : | : | 5-2<br>5-2 |

| Stroage Address Register                         |           |      |      |     |     |   |   | · | · |   | • | 5-2        |

|                                                  |           |      |      |     | ·   | · | • | · | · | · | • | 5-2<br>5-2 |

| Temporary Address Regi                           | ste       | а (. |      | v   | •   | • | • | · | • | · | · | 5-2        |

| Setting/Resetting Interrupt Re                                 | eque  | ests      |     |      |   |   |   |   |   | • | 5-2        |

|----------------------------------------------------------------|-------|-----------|-----|------|---|---|---|---|---|---|------------|

| Determining the Cause of an I<br>Masking Program Level Priorit | nter  | rrup      | t   |      |   |   |   |   |   |   | 5-3        |

| Masking Program Level Priorit                                  | ies   |           |     |      |   |   |   |   |   |   | 5-3        |

| Storage Protect                                                |       |           |     |      |   |   |   |   |   |   | 5-3        |

| Interval Timer                                                 |       |           |     |      |   |   |   |   |   |   |            |

| Cyclic Redundancy Check (Cl                                    | RC)   |           |     |      |   |   |   |   |   |   | 5-6        |

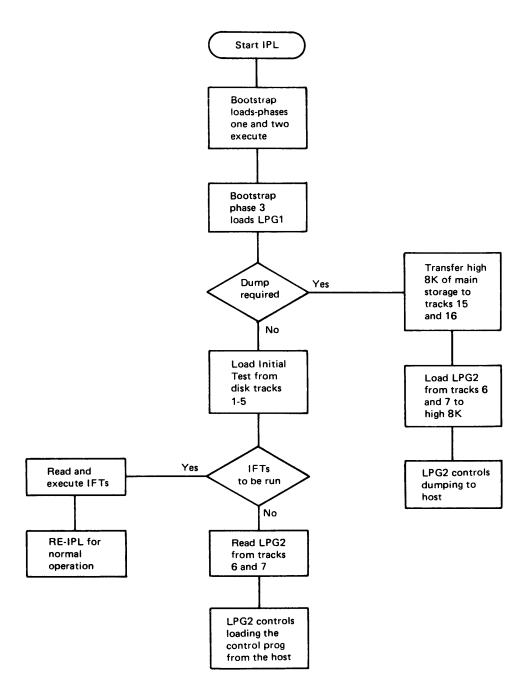

| Initial Program Load (IPL).<br>Check Conditions During I       |       |           |     |      |   |   |   |   |   |   | 5-6        |

| Check Conditions During I                                      | PL    |           |     |      |   |   |   |   |   |   | 5-8        |

| Input/Output Instructions.                                     |       |           |     |      |   |   |   |   |   |   |            |

| Input Instructions                                             |       | •         |     |      |   |   |   |   |   |   |            |

| Output Instructions                                            |       |           |     |      |   |   |   |   |   |   | 5-9        |

| CCU Checks                                                     |       |           |     |      |   |   |   |   |   |   | 5-10       |

| Program Checks                                                 |       |           |     |      |   |   |   |   |   |   | 5-10       |

|                                                                |       |           |     |      |   |   |   |   |   |   | 5-10       |

| Protection Exception .                                         | •     | ·         | •   | ·    | : |   | : |   |   |   | 5-11       |

| Invalid Op-Code Check .                                        | •     | •         | •   | :    | : | : |   |   |   |   | 5-11       |

|                                                                |       | :         |     |      |   |   |   |   |   |   |            |

|                                                                |       |           |     |      |   |   |   |   |   |   | 5-11       |

| CCU Diagnostic Facilities .                                    | ·     | ·         | ·   | ٠    | · | · | • | · | · | · | 5-12       |

| Chandra (. Truns 1 Communi                                     | - 41  | 6         |     |      |   |   |   |   |   |   | 6-1        |

| Chapter 6: Type 1 Communic                                     | catio | on 3      | car | inei |   | · | · | · |   |   | 6-1<br>6-1 |

| Operation and Data Flow .                                      | ·     | ·         |     |      |   |   |   |   | · | • |            |

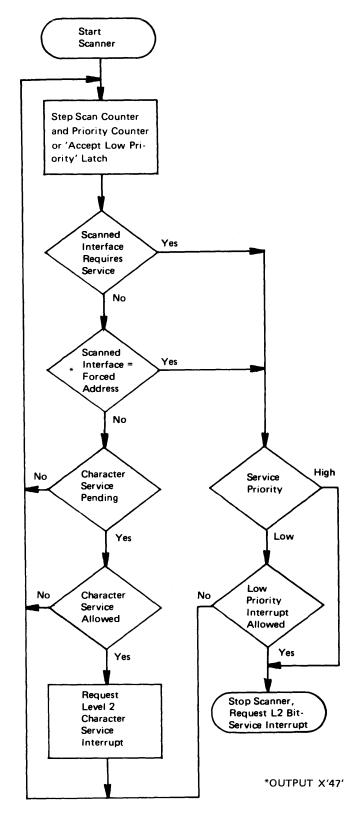

| Interface Scanning                                             | ·     | ·         | ·   | ·    | · | · | · | · | · | · | 6-2        |

| Bit Service Priority                                           |       |           |     |      |   |   | · | · | · | • | 6-2        |

| Interrupt Requests                                             | ·     | ·         | •   | ·    | · |   | · |   | • | · | 6-3        |

| Bit Service Interrupt Requ                                     | est   | ·         | •   | ·    | · | · | · | · | · | · | 6-3        |

| Character Service Interrup                                     | t Re  | que       | est | •    | • | · | ٠ | · | • | · | 6-3        |

| Scanner and Interface Initializ                                |       |           | •   | •    | · | • | • | • | · | • | 6-5        |

| Programming Considerations                                     |       |           |     |      |   |   |   |   |   |   | 6-5        |

| Interface Modes of Operation                                   | •     |           | •   | •    | • |   | • | • |   | • | 6-5        |

| Business Machine Clocks                                        |       | •         |     |      |   |   |   |   | • |   | 6-6        |

| Autocall Interface Operation                                   |       |           |     |      |   |   |   |   |   |   | 6-7        |

| Input/Output Instructions .                                    |       |           |     |      |   |   |   |   |   |   | 6-7        |

| Input Instructions                                             |       |           |     |      |   |   |   |   |   |   | 6-7        |

|                                                                |       |           |     |      |   |   |   |   |   |   | 6-8        |

| Error Indications                                              |       |           |     |      |   |   |   |   |   |   | 6-9        |

|                                                                |       |           |     |      |   |   |   |   |   |   | 6-9        |

| Interface Errors                                               |       |           |     |      |   |   |   |   |   |   | 6-9        |

| Diagnostic Functions                                           |       |           |     |      |   |   |   |   |   |   |            |

| Diagnostic Bit Service .                                       | •     |           |     |      | ÷ |   |   |   |   |   |            |

| Diagnostic Wrap Mode .                                         | •     |           |     |      |   |   | ÷ | ÷ |   |   |            |

| Modem Wrap Test                                                |       |           |     |      |   |   |   |   |   |   |            |

|                                                                | ·     | •         | •   | •    | · | · | · | · | • | • | 010        |

| Chapter 7. Type 2 Communi                                      | ati   | <b></b> 9 | oar | mor  |   |   |   |   |   |   | 7-1        |

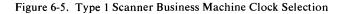

| Chapter 7: Type 2 Communic<br>Operation and Data Flow .        | air   | 511 0     | car | ne   |   | • | · | • | · | · | 7-1        |

| Type 2 Seemer Begisters                                        | •     | ·         | •   | •    | · | • | • | • | • | • | 7-1        |

| Type 2 Scanner Registers .<br>Local Storage                    | •     | •         | ·   | •    | • |   | · | · | · | • | 7 1        |

|                                                                | ·     | •         | ·   | •    | • | · | · | · | • | • | 7-1        |

| ICW Work Register .                                            | ·     | ·         | ·   | •    | · | · | · | · | · | • | 7-1        |

|                                                                |       |           | ·   | •    | · | · | · | · | • | · | 7-1        |

| Attachment Buffer Addres                                       | s R   | egisi     | ter | ·    | • | · | · | · | · | · | 7-2        |

| Display Register                                               | ·     | ·         | ·   | ·    | · | • | · | · | · | • | 7-2        |

| Type 2 Scanner Addressing                                      | ·     | ·         | •   | ·    | • | • | · | · | • | · | 7-3        |

| Scan Addressing                                                | •     | •         | •   | •    | • | • | · | • | • | • | 7-3        |

| Scan Counter                                                   | •     | •         | •   | •    | • | • | • |   | · | • | 7-3        |

| Upper Scan Limit                                               | •     | •         |     | •    | • |   | • |   | • | • | 7-3        |

| Address Substitution .                                         |       |           |     |      | • |   |   |   |   |   | 7-4        |

| Program Addressing                                             |       |           |     |      |   |   |   |   |   |   | 7-5        |

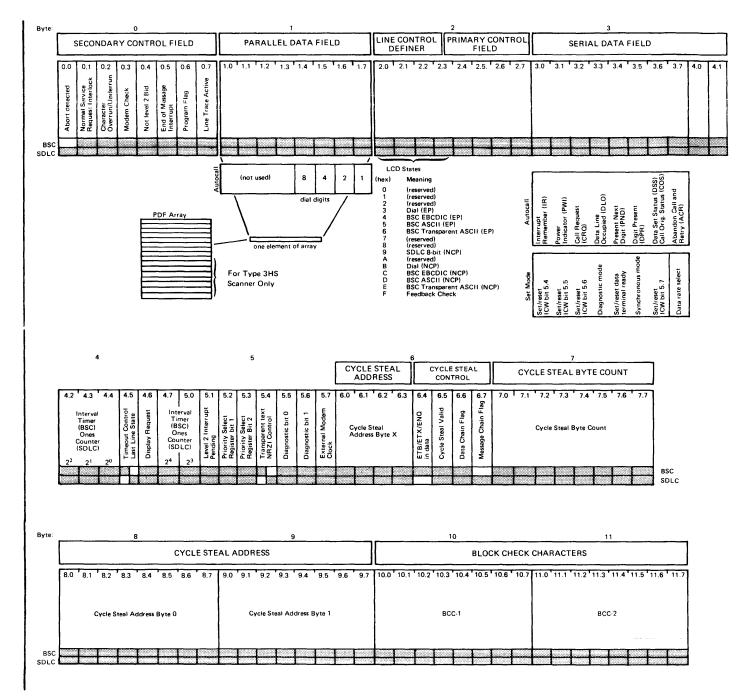

| Interface Control Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICW Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ICW Modification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Interface Control Word Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Line Control Definer (LCD) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Primary Control Field (PCF) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interface Mode Set-SDF Values .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Business Machine Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I/O Programming Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Program Level 1 (Error Routines)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

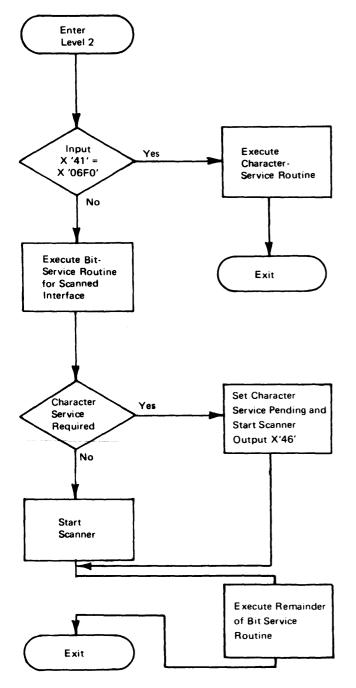

| Program Level 2 (Character Service)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |                                       | 7-15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |