# 2711<sup>1</sup>A EXTERNAL REFERENCE SPECIFICATION

# A-27114-90011-1 Rev A

# CONTENTS

| 1.  | SCOPE                                              |          |

|-----|----------------------------------------------------|----------|

| 2.  | GENERAL                                            |          |

|     | 2.1 Description                                    | .2-1     |

|     | 2.2 Environment                                    |          |

|     | 2.3 Installation                                   |          |

| 3.  | FRONTPLANE FUNCTIONAL DESCRIPTION                  |          |

| 5.  | 3.1 Physical Characteristics of Frontplane Signals |          |

|     | 3.1.1 Cable - differential version                 | -3 - 1   |

|     |                                                    |          |

|     | 3.1.2 Cable (single-ended version):                |          |

|     | 3.1.3 Drivers and Receivers                        |          |

|     | 3.1.4 Bi-directional bus                           |          |

|     | 3.2 Signal Definitions                             | .3-3     |

|     | 3.3 pin out                                        | .3-5     |

|     | 3.4 Logic sense on frontplane interface            | 3-18     |

|     | 3.5 Data Transfer                                  |          |

|     | 3.6 Frontplane Timing                              |          |

|     | 3.7 Back-to-Back 27114 Link                        |          |

|     | 3.7.2 Back-to-Back Data Transfer                   | 3-25     |

| 4.  | BACKPLANE CONTROL DESCRIPTION                      | $J_{-1}$ |

| 7.  | 4.1 Register Definitions                           |          |

|     | 4.1.1 Register descriptions:                       |          |

|     | 4.1.2 Card Identification                          |          |

|     |                                                    |          |

|     | 4.2 Data path pipeline                             |          |

|     | 4.2.1 FIFO and external latches                    |          |

|     | 4.2.2 State machine                                |          |

|     | 4.2.3 SRQ poll response and burst request          |          |

|     | 4.2.4 Backplane data handshaking                   |          |

|     | 4.2.5 Frontplane data handshaking                  | 4-11     |

|     | 4.3 Data Path Loopback                             | 4-11     |

|     | 4.3.1 Loopback without test hood                   | 4-12     |

|     | 4.3.2 Loopback with test hood                      |          |

|     | 4.4 Interrupts                                     |          |

|     | 4.5 Output to a Peripheral                         |          |

|     | 4.6 Data input from a Peripheral                   |          |

|     | 4.7 Dealing with the Data Path Pipeline            |          |

|     | 4.8 27114 to 27114 Connections - Software          |          |

| 5.  | PERFORMANCE ISSUES                                 |          |

| 2.  |                                                    |          |

|     | 5.1 Fundamental Limits to Performance              |          |

|     | 5.2 Frontplane Limits to Performance               |          |

|     | 5.2.1 Cable Length                                 |          |

|     | 5.3 Backplane Performance                          |          |

|     | 5.3.1 Data Bursting                                |          |

|     | 5.3.1.1 Burst Hardware Variation                   |          |

|     | 5.3.2 Interaction Between Backplane and Frontplane | .5-5     |

|     | 5.4 27114 to 27114 Performance                     | .5-6     |

| 6.  | PRELIMINARY PROGRAMMING INFORMATION                | .6-1     |

|     | 2.1 Description                                    | .6-1     |

|     | 2.2 Installation                                   |          |

| 2.3 | Driver features                                    |          |

### UPDATE HISTORY

Dec 12, 1985

\* The correct definition for backplane interface registers is given (in term of BPO, BP1, CBYT and CEND).

\* Frontplane pin A10 now is a safety ground pin and pin B10 is the test hood presence pin.

Feb 12, 1986

- \* Cable offering (single-ended: high and low true)/differential.

- \* General clean up of documentation

Apr 9, 1986

\* Extra information on group 0 polling

\* Information about series 550 is removed

\* More information on grounding and RFI performance

June 26, 1986

\* General clean up

Nov 7, 1986

\* General clean up

\* Clarify data handshake

Jan 14, 1986 \* General clean up

### 1. SCOPE

This External Reference Specification provides all the information required to instal? and operate the AFI (Asynchronous FIFO Interface) card. It details the pin out and function of the frontplane interface as well as the backplane interface in terms of register descriptions.

The intention of this document is to provide sufficient information such that drivers can be written for high level language users. This document does not provide full information on how the card operates internally or how programming is done at the user level. The 27114 IRS provides information on how the card operates internally. For user programming information, please refer to the appropriate driver's ERS.

Eventhough any well written ERS could provide enough information to guide how to use the described product, it is believed that the AFI card belongs to an exception group. This ERS alone probably would be sufficient to provide enough information for most intended use but wise users should also be intimately familiar with the hardware via the IRS and specially, the schematics, the granddaddy of all electrical documents.

It should be noted here that this is not an ERS for the AFI product but only an ERS for the AFI hardware. Attempt to interpret this otherwise could mislead to other confusion. A good example is the parity feature of the AFI card. While there are hardware circuits available on the AFI assembly to support the parity feature, the host channel adapter and device adapter driver/operating systems must also support it to claim that AFI product has the parity feature. The ERS for AFI product should be written after close examination of ERS's for both hardware and software products to see how and what kind of interactions could be expected.

As of this release, most of the performance testing has been done to verify that AFI actually could go as high as 5 Mbytes per sec for cables of length 3 to 12 m long. This figure may also be misleading if not carefully interpretted by the product ERS writer since other system factors could greatly affect it.

Throughout this document, temporary NOTEs will be used to describe unresolved issues as of the latest revision date. Please consult RND' R&D for latest information on those subjects.

## 2. GENERAL

2.1 Description

The 27114 card is an extended level 1 CIO card intended for fast parallel data transfer batween CIO channel and an external peripheral. It interfaces to user's equipment via a 16 data bit parallel bus. Two additional parity bits are also provided for suitable future application.

NOTE:

The 8 bit mode can be achieved by having the byte packing/unpacking done by the CIO channel adapter.

This bus can be configured either as differential or single-ended (separate in/out only). Pulsed asynchronous handshake is provided. The 27114A card can be used in any Spectrum host with CIO channel adapter.

The 27114 is used as a dedicated interface to a single peripheral device. It is not and cannot be made to be compatible to either HPIB, SCSI or IPI. The 27114 is designed to be compatible to most other HP's parallel cards.

2.2 Environment

POWER CONSUMPTION:

The 27114A card consumes about 2 A at +5 volts. The 2 sigma value is about 2.25 A.

FUSE:

The 27114A is shipped with a built-in fuse printed circuit trace. Under abnormal condition, this trace will burn out to protect the main power supply. After the abnormal cause is removed, part number 2110-0712 fuse (4 A) should be used to replace the built-in fuse. This part is available directly from CPC.

**OPERATING ENVIRONMENT:**

The 27114 is intended to be operated over the Hewlett-Packard CLASS B environmental specifications.

2.3 Installation

The 27114A card is a regular mode card as far as power consumption is concerned. It draws typically about 10 watts compared to the normal 12 watt allowance for regular CIO cards. The installation of this card in any CIO card cage does not require budgeting of power supply resource. Since the AFI responds to polling via its UAD line and its channel address is the same as the slot address, it can be guaranteed to function correctly in group 0 slots only. Note that other level 2 CIO cards have a programmable (via address teaching) channel address register which would pull on the appropriate data line (one of D0 through D7) when they respond to any poll, regardless what address (0 through 15) they are at (group 1 cards belong to address 8 to 15 but also responds to poll via D0 to D7).

Please refer to the appropriate channel adapter manual for further information. Section 4.2.3 gives some extra information on how group 0 polling is necessary for the AFI card.

The configuration switches (SW1 switch 1 through 8) must be set as follow:

SWITCH SW1:

Switches 1 through 6:

For standard cable length (3/12 meter differential, and 3 meter single-ended), set switches SW1 #1,#3,#5 to the ON position. SW1 #2,#4,#6 are don't cares.

The 25 m cable length is not recommended for single-ended cables due to excessive resistance of the common return current ground lines.

SW1 switches 7 and 8:

These two switches are used to program the parity bit in the ID (read) register (bit #11). The bit is read as 1 when switch 7 is closed and switch 8 is open. If switch 7 is open and switch 8 is closed, a 0 will be read. Note that the generation and checking of parity is not affected by the setting of these two switches.

ALTERNATE CABLE LENGTH RESISTOR VALUES:

When the 24 m length is selected, a different custom length cable can be used when resistors R5, R7 and R9 are installed with the desired values as recommended in section 3.6

LINE CONFIGURATION:

As shipped from the factory, all of the frontplane signals are differential and can be re-configured as single-ended (high true logic) as follow:

- \* Remove resistor network packs RP26, RP56 and RP406 from their DIP sockets. These (part # 1810-0338) should be saved if future re-conversion is anticipated.

- \* Install part number 1810-0906's in these sockets such that their pin 1 corresponds to pin 10 and 20 of each of the U26, U56 and U406 mentioned above (two -0906's per DIP socket).

- \* For low true single ended line configuration, install these 1810-0906 such that their pin 1 corresponds to pin 1 and 11 of the sockets U26, U56 and U406

- \* To convert back to differential lines, install the 1810-0338 resistor network DIPs in sockets U26, U56 and U406 such that their pin 1 corresponds to pin 2 of the sockets.

6 part number 1810-0906's are supplied with each 27114 card with single-ended cable option.

## CABLE INSTALLATION:

Each 27114A AFI card is shipped with either a differential cable (3 or 12 m long) or a single-ended cable (3 m long) depending on the option selected. The differential cable is ambidextrous and can be installed with either end plugged in to the 27114A card. The single-ended cable is labeled on both connectors. The connectors are labeled "High-true Periph. End" and "Low-true Periph. End". With the "High-true Periph. End" connected to the peripheral, the cable conforms to high-true application and vice-versa for the "Low-true Periph. End" connector.

It is recommended that the user effectively ground the cable at the peripheral end via a reliable, low resistance, broad surface connection between the exposed metal part ("Rook") and the nearest chassis. THE RADIO FREQUENCY INTERFERENCE CHARACTERISTIC OF THE TOTAL SYSTEM CAN BE SEVERELY DEGRADED IF THIS CONNECTION IS NOT MADE PROPERLY AND COULD LEAD TO POSSIBLE VIOLATIONS OF MOST LOCAL LAWS AND REGULATIONS. THE IMPORTANCE OF THIS CANNOT BE OVERSTATED HERE.

## 3. FRONTPLANE FUNCTIONAL DESCRIPTION

The frontplane is used to pass data back and forth between the IO card and the user's equipment. The frontplane is organized around 16 bits of data plus two parity bits (one for each byte). Status and control lines are also used to pass information (at a slower rate). An attention line can be used to interrupt the host processor for priority service.

3.1 Physical Characteristics of Frontplane Signals

3.1.1 Cable - differential version

The cable has 48 twisted pairs of 32 gauge wire wrapped in a combination of foil/braid shield and jacketed in standard HP jade gray PVC. The connectors on both 27114 ends of the cable are DIN 41650 type C headers (Eurocard connector).

Both ends behave in the same manner and can be installed either way. The wiring is made such that if the cable is used to connect two AFI cards, the positive output of a signal on one card is connected to the positive input of a matching signal on the other card (e.g. PCTL+ to PFLG+). This arrangement allows the same cable to be used for AFI to AFI connection.

RF shielding is done via the Rook to slot contact at the point the cable exits the CIO card cage and also via the clipping mechanism. Safety grounding is also provided via the rook to slot contact.

The cable assembly is mated to a male (pin) 96-position Eurocard connector on the 27114A card. A 1/2" wire-wrap connector (DIN header type R) is supplied as the matching connector at the user end. Only two lengths are provided: 3 m and 12 m. Custom made cables for other length can be ordered directly from the OEM supplier, DuPont Connector Systems. Its impedance is about 120 ohms. The resistance per foot is about 60 milliohms. Propagation delay in the cable is about 5 nanoseconds per meter.

3.1.2 Cable (single-ended version):

The single-ended cable is very similar to the differential cable. There are some differences however:

\* There are only 50 conductors. Two of which are for ground return.

\* If this cable is used to connect two AFI cards together, it will map the output of a signal to the opposite sense input of a matching signal on the other card. Connected as thus would complicate the use of this cable as AFI to AFI connection but provide a side benefit: only one cable is needed for both high and low true applications.

The cable is wired such that if installed in one direction, it will provide high true single-ended interface and low true

interface in the other direction. The cable is labeled on both connectors as stated in section 2.3.

Length longer than 3 m is not recommended unless the data rate is reduced substantially to maintain data integrity. Even then, the excessive length can cause the signal to be more susceptible to noise or become unreliable.

## NOTE:

Unless otherwise specified, all performance figures in this document are applicable only in the differential mode with the standard 3 m cable and with an zero delay user's interface (instantaneous PFLG timing with respect to PCTL).

The single-ended cable shares other common characteristics with the differential cables. Same technique of grounding and cable termination/ connectors are provided (mating wire-wrap connector included).

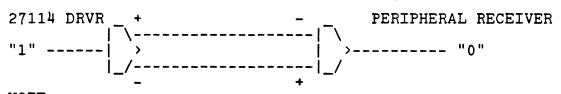

## 3.1.3 Drivers and Receivers

Drivers: MC3487 differential drivers which complies to RS-422 specs. The HP part number is 1820-2145.

Receivers: 26LS32B differential receivers. This is a higher speed/less skew/ more hysteresis 26LS32. These parts are designed to "receive" a "one" if left open. In differential mode, since there is a resistor across each input pair, the outputs cannot be guaranteed of any certain value if left disconnected. The HP part number is 1820-2830.

To configure the frontplane interface as single-ended lines, refer to section 2.3 (installation).

Even though these line drivers and receivers were designed to withstand the common mode voltage which may appear between the 27114A card and the user's equipment as specified per RS-422 specs, the card was not designed to interface to +12 volt open collector devices.

### 3.1.4 Bi-directional bus

There is no current plan to supply a bi-directional cable for the 27114 card. A possibility exists whereas the user can shorten corresponding inputs and outputs at the peripheral end to form a makeshift cable. Line reflections and impedance mismatch may deteriorate performance and thus this solution is not recommended unless data transfer rate is reduced substantially and experiments are done by the user to assure data integrity.

Notes on bi-directional bus contention: The users should take every precaution in determining which end is driving the bi-directional bus at any one point in time. If both ends are in the same talking/listening state, unsatisfactory results are is inevitable. The line drivers provided on the 27114 card are electrically protected against this abuse as stated by the RS-422 standard but abuses should be avoided if possible.

## 3.2 Signal Definitions

The following description is for the differential cable mode. It would also generally apply to the single-ended cable mode. Wherever differences occur, these will be pointed out. Note that the single-ended cable has only one conductor per signal and all signals share two common ground return lines.

In the differential cable, each pair of signal includes two conductors wound in a twisted manner to minimized induced noise and to keep line impedance within tolerance. Since each conductor in a pair swings in the opposite direction of the other one, they tend to cancel each other as far as the return current is concerned. This effectively makes the line less susceptible to length and induced noise.

<u>Output Data</u>: 16 twisted pairs. Each of these should be terminated with around 120 ohms at the user's end. For single ended lines, it is recommended that these are terminated with a 3.3 K ohm resistor connected to +5 volt source.

<u>Input Data</u>: 16 twisted pairs. Each of these is terminated on the 27114 with 120 ohm terminator (for both separate and common in-out bus configuration). When configured as single-ended lines, these inputs are terminated by a voltage divided connected between +5 and ground consisting of a 1500 ohm resistor (to +5) and a 3300 ohm resistor (to ground). The other line is biased internally on the card to a voltage around 1.5 volts.

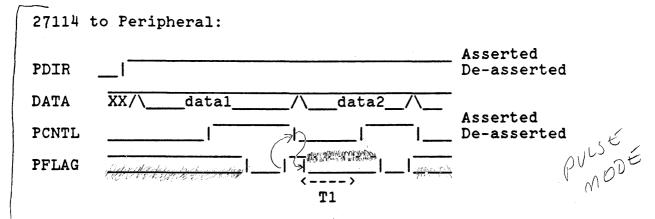

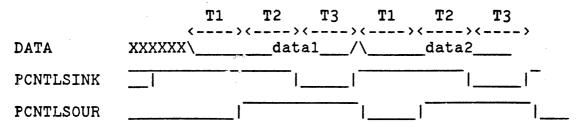

PCNTL: (sometime referred to as PCTL) It is asserted in a master relationship to the peripheral to indicate that either data is available or data can now be accepted. Set up time of data assertion prior to assertion of PCNTL is controlled by an RC time constant on board. This time is nominally 75 nsec. Recommended termination is 120 ohms at receiver. The asserted state is that of the pin labeled PCNTL+ at a high voltage with respect to PCNTL-. For high true single-ended lines, the PCNTL+ line is used.

This line can be preset or reset by careful manipulation of data output sequence to the card. Its state is available as a status bit in the 27114 status register. These manipulations are not accessible directly to the user above the driver's level.

**PFLAG**. It is asserted by the peripheral to acknowledge the acceptance of data or to indicate that valid data exists on the lines. Data must be valid at the same time as PFLAG is asserted on transfer from peripheral to 27114. Received by 26LS32B with 120 ohms across line. De-skewing of data received by the 27114 is done based on an RC time constant on the board. This is nominally about 75nsec. The asserted state is of the same sense as PCNTL. The state of this line can be read as a bit in the 27114A status register. However, this is not visible to the user above the driver's level.

<u>**PDIR:</u>** It is asserted by the 27114 indicating the direction of transfer. Transfer is to peripheral in case of PDIR = 1 (output/write). This state is indicated with PDIR+ high with respect to PDIR-.</u>

This line is asserted during output mode. The actual timing is driver's dependent but should not be changing between consecutive outputs or inputs.

**CONTROL**[2..0]: Three bits under program control. They are simply bits in a register on the card. 27114 asserts these and the peripheral watches them. They are set to all zero's in case of a clear of the card. The "zero" state is that of the pin labeled CTL?+ at a low voltage with respect to CTL?-. Program logic sense is the opposite of that seen on cable.

These lines can be reset or preset independently of each other and of other activities on the card. They should be maintained at the commanded levels (by user) regardless of other data input/output activities.

STATUS[2..0]: Three bits which are readable by a program as register bits. The STATUS[1..0] bits are updated with every /SYNC rising edge from the CIO backplane. The STATUS 2 line receiver's output is enabled only when DIR is false (data input); the corresponding status bit is valid only in this condition. Another way to look at this restriction is to consider that status 2 does not exist.

Received by 26LS32B terminated with 120 ohms. The sense is such that if STS?+ is at a high voltage with respect to STS?- the  $p_{0}^{(A)}$ , value read from the 27114 by a program will be a zero.

These lines are received and passed directly to the user and do not affect other activities on the 27114 card.

<u>ATTN:</u> Asynchronous interrupt line. When switched, it causes sense[arq] to be set. If software has enabled the card to pass ATTN on through as an ARQ interrupt, it will cause an interrupt to the channel adapter. If the interrupt in the channel adapter is enabled, it will cause an interrupt to a CPU. Received by 26LS32B and 120 ohms. This is an edge-triggering signal which activates only when the ATTN+ signal is changing from high to low level while ATTN- is changing in the other way around.

The interrupt action is sensed by CIO channel adapter and passed on to the host accordingly.

**TEST:** This is a special testing pin. When grounded, the data line drivers are enabled at all time, allowing the loopback of data with the test hood during diagnostic tests. The supplied

testhood grounds this input. Unless necessary, user should leave this pin untouched.

This line can also be detected as a bit in the 27114 status register. The presence of a test hood would ground this pin, resulting in a reading of 1. The status of this line is inaccessible to most user above driver's level.

Grounds: Two signal ground wires in the cable (two pairs). A drain wire is also provided. This wire is connected to the frame ground on the card.

3.3 pin out

Four wiring tables are presented here. The first one is for the frontplane connector. The second table is for the differential wire-wrap connector. The third and fourth tables are for single-ended wire-wrap connector pin outs.

The first one follows immediately as three tables. These three diagrams illustrate the assignment of pins versus signals for rows A, B and C of the frontplane connector.

Perhaps of more importance is the wire-wrap connector pin out diagram which follows the frontplane connector pin out diagram. As the 27114 cable is defined, most signal pairs are swapped in the cable, resulting in a slightly different wiring diagram.

A quick observation will reveal that the wire-wrap connector wiring diagram is an inverted image of that of the frontplane interface connector. This is very useful when one attempts to interconnect two 27114A cards to each other. In this case, only one cable assembly is required.

## FRONTPLANE CONNECTOR PIN OUT DIAGRAM - ROW A

| 27114<br>CONN.<br>OPIN NO.                                                                                                                                                                        | SIGNAL                                                                                                                                                                                                                                                                                                                                                                                               | WIRE<br>COLOR | SIGNAL<br>DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A13<br>A14<br>A15<br>A16<br>A17<br>A16<br>A17<br>A18<br>A19<br>A20<br>A21<br>A22<br>A23<br>A24<br>A25<br>A26<br>A27<br>A28 | RD0-         RPAR0-         RD1-         SPAR0+         RD2-         RPAR1+         RD3         SPAR1-         RD4-         SHIELD         RD5-         STS2+         RD6-         PFLG-         RD7-         STS0+         RD8+         STS1-         RD9+         GND         SD9-         PCTL-         RD11+         CTL0+         RD12+         CTL1+         RD13+         CTL2-         RD14+ |               | Data Bit 0, Low True, RECEIVE<br>Parity bit 0, Low True, RECEIVE<br>Data Bit 1, Low True, RECEIVE<br>Parity bit 0, High True, SEND<br>Data Bit 2, Low True, RECEIVE<br>Parity bit 1, High True, RECEIVE<br>Parity bit 1, Low True, RECEIVE<br>Parity bit 1, Low True, RECEIVE<br>Parity bit 1, Low True, RECEIVE<br>Frame ground<br>Data Bit 5, Low True, RECEIVE<br>Frame ground<br>Data Bit 5, Low True, RECEIVE<br>STATUS 2, High True, RECEIVE<br>Data Bit 6, Low True, RECEIVE<br>PFLAG, Low True, RECEIVE<br>STATUS 0, High True, RECEIVE<br>STATUS 1, Low True, RECEIVE<br>STATUS 1, Low True, RECEIVE<br>STATUS 1, Low True, RECEIVE<br>Data Bit 9, High True, RECEIVE<br>Data Bit 9, Low True, SEND<br>PCTL, Low True, SEND<br>Data Bit 11, High True, RECEIVE<br>CTRL 0, High True, RECEIVE<br>CTRL 1, High True, RECEIVE<br>CTRL 1, High True, RECEIVE<br>CTRL 2, Low True, SEND<br>Data Bit 13, High True, RECEIVE<br>CTRL 2, Low True, SEND<br>Data Bit 14, High True, RECEIVE |

| A31                                                                                                                                                                                               | ATTN+<br>RD15+<br>PDIR- *                                                                                                                                                                                                                                                                                                                                                                            |               | ATTN , High True, RECEIV<br>Data Bit 15, High True, RECEIVE<br>PDIR , Low True, SEND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

•

WIRECOLOR ("AMISTED WITH COLOR)

0-BK (BLACK) 1-BR (BROWN) 2-R (RG) 3-0 (ORANGE) 4-Y (YELOW) 5-6 (GREEN)

6-8 (BLUG)

7. GR (GRAY)

8-V (VIOLET)

9-W (WHITE)

X-BG (BE16E) OW= DEF WHITE

# 27114 ERS, Nov 7, 1986

# FRONTPLANE CONNECTOR PIN OUT DIAGRAM - ROW B

| 1     | 1      | 1                                                                                                              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                     |

|-------|--------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27114 | 1      | 1                                                                                                              |                                                                                                                                                                                                                                                                                                           |

|       | SIGNAL | WTRF                                                                                                           | SIGNAL                                                                                                                                                                                                                                                                                                    |

|       | NMEM.  | COLOR                                                                                                          | DEFINITION                                                                                                                                                                                                                                                                                                |

|       | 1      |                                                                                                                |                                                                                                                                                                                                                                                                                                           |

|       |        |                                                                                                                |                                                                                                                                                                                                                                                                                                           |

| B1    | SD0-   | $(1,1) \to (1,1)$                                                                                              | Data Bit 0, Low True, SEND                                                                                                                                                                                                                                                                                |

| B2    | RPARO+ |                                                                                                                | Parity bit 0, High True, RECEIV                                                                                                                                                                                                                                                                           |

| B3    | SD1-   |                                                                                                                | Parity bit 0, High True, RECEIV<br>Data Bit 1, Low True, SEND<br>Parity bit 0, Low True, SEND<br>Data Bit 2, High True, SEND<br>Parity bit 1, Low True, RECEIVE<br>Data Bit 3, Low True, SEND<br>Parity bit 1, High True, SEND<br>Data Bit 4, High True, SEND                                             |

| B4    | SPARO- | 2                                                                                                              | Parity bit 0, Low True, SEND                                                                                                                                                                                                                                                                              |

| B5    | SD2+   | 1                                                                                                              | Data Bit 2, High True, SEND                                                                                                                                                                                                                                                                               |

| B6    | RPAR1- |                                                                                                                | Parity bit 1, Low True, RECEIVE                                                                                                                                                                                                                                                                           |

| B7    | SD3-   |                                                                                                                | Data Bit 3, Low True, SEND                                                                                                                                                                                                                                                                                |

| B8    | SPAR1+ |                                                                                                                | Parity bit 1, High True, SEND                                                                                                                                                                                                                                                                             |

|       | SD4+   | · · ·                                                                                                          |                                                                                                                                                                                                                                                                                                           |

| B10   | TEST-  |                                                                                                                | Data line driver enable                                                                                                                                                                                                                                                                                   |

| B11   | IADE   | 1                                                                                                              |                                                                                                                                                                                                                                                                                                           |

| B12   | STS2-  |                                                                                                                | STATUS 2 , Low True, RECEIVE                                                                                                                                                                                                                                                                              |

| B13   | SD6+   |                                                                                                                | Data Bit5, Low True, SENDSTATUS 2, Low True, RECEIVEData Bit6, High True, SENDPFLAG, High True, RECEIVData Bit7, Low True, SENDSTATUS 0, Low True, RECEIVEData Bit8, High True, SENDSTATUS 1, High True, RECEIVData Bit10, Low True, RECEIVESignal GroundData Bit10, High True, SENDPCTL. High True, SEND |

| [B14  | PFLG+  |                                                                                                                | PFLAG , High True, RECEIV                                                                                                                                                                                                                                                                                 |

| B15   | SD7-   |                                                                                                                | Data Bit 7, Low True, SEND                                                                                                                                                                                                                                                                                |

| [B16  | STS0-  |                                                                                                                | STATUS 0 , Low True, RECEIVE                                                                                                                                                                                                                                                                              |

| B17   | SD8+   |                                                                                                                | Data Bit 8, High True, SEND                                                                                                                                                                                                                                                                               |

| B18   | STS1+  |                                                                                                                | STATUS 1 , High True, RECEIV                                                                                                                                                                                                                                                                              |

| B19   | RD10-  |                                                                                                                | Data Bit 10, Low True, RECEIVE                                                                                                                                                                                                                                                                            |

| B20   | GND    |                                                                                                                | Signal Ground                                                                                                                                                                                                                                                                                             |

| B21   | SD10+  |                                                                                                                | Data Bit 10, High True, SEND                                                                                                                                                                                                                                                                              |

|       |        |                                                                                                                |                                                                                                                                                                                                                                                                                                           |

| B23   | SD11+  |                                                                                                                | Data Bit 11, High True, SEND                                                                                                                                                                                                                                                                              |

| B24   | CTLO-  | 6                                                                                                              | CTRL 0 , Low True, SEND                                                                                                                                                                                                                                                                                   |

| B25   |        | 6                                                                                                              | Data Bit 12, High True, SEND                                                                                                                                                                                                                                                                              |

| B26   | CTL1-  | ie in the second se | CTRL 1 . Low True. SEND                                                                                                                                                                                                                                                                                   |

|       |        | $\tilde{c}$ .                                                                                                  | Data Bit 13, Low True, SEND                                                                                                                                                                                                                                                                               |

| B28   | CTL2+  | -                                                                                                              | CTRL 2 , High True, SEND                                                                                                                                                                                                                                                                                  |

| B29   | SD14+  |                                                                                                                | CTRL 2 , High True, SEND  <br>Data Bit 14, High True, SEND                                                                                                                                                                                                                                                |

| B30   | ATTN-  |                                                                                                                | ATTN , Low True, RECEIVE<br>Data Bit 15, Low True, SEND                                                                                                                                                                                                                                                   |

| B31   | SD15-  | $E = e^{-i\omega t}$                                                                                           | Data Bit 15, Low True, SEND                                                                                                                                                                                                                                                                               |

|       | PDIR+  | 1. A.                                                                      | PDIR , High True, SEND                                                                                                                                                                                                                                                                                    |

|       |        |                                                                                                                |                                                                                                                                                                                                                                                                                                           |

# FRONTPLANE CONNECTOR PIN OUT DIAGRAM - ROW C

-

## WIRE-WRAP CONNECTOR PIN OUT DIAGRAM - DIFFERENTIAL, ROW A

| and the second se |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27114<br> CONN.  SIG<br>OPIN NO.  NME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                | SIGNAL<br>DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A2       SPA         A3       SD1         A4       RPA         A5       SD2         A6       SPA         A7       SD3         A8       RPA         A9       SD4         A10       SH1         A11       SD5         A12       PD1         A13       SD6         A14       PCT         A15       SD7         A16       CTL         A17       SD8         A18       CTL         A19       SD9         A20       GND         A21       RD9         A22       PFL         A23       SD1         A24       STS         A25       SD1         A26       STS         A27       SD1         A28       ATT         A29       SD1         A30       CTL                                                       | R0-         -         P0+         -         R1+         -         R1-         -         ELD         -         ELD         -         ELD         -         ELD         -         O+         +         1-         +         0+         +         1-         +         1+         0+         2+         1+         3+         N-         4+         2+         5+ | Data Bit 0, Low True, SEND<br>Parity bit 0, Low True, SEND<br>Data Bit 1, Low True, SEND<br>Parity bit 0, High True, RECEIVE<br>Data Bit 2, Low True, SEND<br>Parity bit 1, High True, SEND<br>Parity bit 1, Low True, SEND<br>Data Bit 5, Low True, SEND<br>Data Bit 6, Low True, SEND<br>Data Bit 6, Low True, SEND<br>PCTL , Low True, SEND<br>Data Bit 7, Low True, SEND<br>Data Bit 7, Low True, SEND<br>Data Bit 8, High True, SEND<br>Data Bit 9, High True, SEND<br>Data Bit 9, High True, SEND<br>Signal Ground<br>Data Bit 9, Low True, RECEIVE<br>PFLAG , Low True, RECEIVE<br>PFLAG , Low True, RECEIVE<br>Data Bit 12, High True, SEND<br>STATUS 0 , High True, SEND<br>STATUS 1 , High True, SEND<br>ATTENTION , Low True, RECEIVE<br>Data Bit 13, High True, SEND<br>ATTENTION , Low True, SEND<br>ATTENTION , Low True, SEND<br>ATTENTION , Low True, SEND<br>STATUS 2 , High True, SEND<br>Data Bit 14, High True, SEND |

COLOR ("TWISTED WITH" COLOR)

- O-BK BLACK BROWN 1 - BR **F** (\*) 2- P ORANISE 3 - 0 yercow y- Y We and M 5.6

- RUSS 6 E

- VIDE 7 . 1

- 619ª 1 8- 6R

- 9- WH ي. موجع المراجع

- North Constant X-Bb

- ow

# WIRE-WRAP CONNECTOR PIN OUT DIAGRAM - DIFFERENTIAL, ROW B

| İC                                     |                                                                                                                | SIGNAL<br>NMEM.                                                                                                                | WIRE<br>COLOR | SIGNAL<br>DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BBBBBBBBBBBBBBBBBBBBBBBBBBBBBBBBBBBBBB | 23456789112345678901222222222222333                                                                            | RD1-<br>RPAR0-<br>RD2+<br>SPAR1-<br>RD3-<br>RPAR1+<br>RD4+<br>RD5-<br>PDIR-<br>RD6+<br>PCTL+<br>RD7-<br>CTL0-<br>RD8+<br>CTL1+ |               | Data Bit 0, Low True, RECEIVE<br>Parity bit 0, High True, SEND<br>Data Bit 1, Low True, RECEIVE<br>Parity bit 0, Low True, RECEIVE<br>Data Bit 2, High True, RECEIVE<br>Parity bit 1, Low True, SEND<br>Data Bit 3, Low True, RECEIVE<br>Parity bit 1, High True, RECEIVE<br>Data Bit 5, Low True, RECEIVE<br>Data Bit 5, Low True, RECEIVE<br>DIRECTION , Low True, SEND<br>Data Bit 6, High True, RECEIVE<br>PCTL , High True, RECEIVE<br>CONTROL 0 , Low True, SEND<br>Data Bit 8, High True, RECEIVE<br>CONTROL 1 , High True, RECEIVE<br>CONTROL 1 , High True, SEND<br>Data Bit 10, Low True, SEND<br>Data Bit 10, Low True, SEND<br>Data Bit 10, Low True, RECEIVE<br>CONTROL 1 , High True, RECEIVE<br>CONTROL 1 , High True, RECEIVE<br>STATUS 0 , Low True, RECEIVE<br>Data Bit 10, High True, RECEIVE<br>Data Bit 11, High True, RECEIVE<br>Data Bit 12, High True, RECEIVE<br>Data Bit 13, Low True, RECEIVE<br>Data Bit 14, High True, RECEIVE<br>Data Bit 15, Low True, RECEIVE<br>Data Bit 14, High True, RECEIVE<br>Data Bit 15, Low True, RECEIVE |

|                                        |                                                                                                                |                                                                                                                                | COLOR (TWISTE | D WITH " COLOR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1                                      | - BR $- R H$ $- O H$ $- V H$ $- B H$ $- H$ $- H$ $- H$ | 3LACK<br>BROWN<br>RED<br>DRANGE<br>MANGE<br>MANGE<br>RAN<br>INTE<br>NOLET                                                      |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8 -<br>9 -                             | GR 6<br>W (1)<br>R(F)                                                                                          | RAV<br>IMTE                                                                                                                    |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# WIRE-WRAP CONNECTOR PIN OUT DIAGRAM - DIFFERENTIAL, ROW C

| 27114       VIRE       SIGNAL         CONN.       SIGNAL       WIRE       SIGNAL         PIN NO.       NMEM.       COLOR       DEFINITION         C1       SD0+       Data Bit 0, High True, SEND         C2       RD0+       Data Bit 0, High True, RECEIVE         C3       SD1+       Data Bit 1, High True, SEND         C4       RD1+       Data Bit 1, High True, RECEIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C2RD0+Data Bit0, High True, RECEIVEC3SD1+Data Bit1, High True, SEND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CONN. SIGNA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C5ISD2+Data Bit 2, High True, SENDC6RD2-Data Bit 2, Low True, RECEIVEC7SD3+Data Bit 3, High True, SENDC8RD3+Data Bit 3, High True, RECEIVEC9SD4+Data Bit 4, High True, RECEIVEC10RD4-Data Bit 4, Low True, RECEIVEC11SD5+Data Bit 5, High True, SENDC12RD5+Data Bit 6, High True, SENDC13SD6+Data Bit 6, Low True, RECEIVEC14RD6-Data Bit 7, High True, SENDC15SD7+Data Bit 8, Low True, RECEIVEC17SD8-Data Bit 8, Low True, SENDC18RD8-Data Bit 9, Low True, SENDC20SD10+Data Bit 10, High True, SENDC21RD9+Data Bit 11, Low True, RECEIVEC22SD1-Data Bit 11, Low True, RECEIVEC23SD1-Data Bit 12, Low True, SENDC24RD1-Data Bit 12, Low True, SENDC25SD12-Data Bit 13, Low True, SENDC26RD12-Data Bit 14, Low True, SENDC27SD13-Data Bit 13, Low True, SENDC28RD13+Data Bit 14, Low True, SENDC28RD13+Data Bit 14, Low True, SENDC30RD14+Data Bit 14, Low True, SENDC31SD15-Data Bit 15, Low True, RECEIVEC31SD15-Data Bit 15, Low True, RECEIVEC31SD15+Data Bit 15, High True, RECEIVE | C2       RD0+         C3       SD1+         C4       RD1+         C5       SD2+         C6       RD2-         C7       SD3+         C8       RD3+         C9       SD4+         C10       RD4-         C11       SD5+         C12       RD5+         C13       SD6+         C14       RD6-         C15       SD7+         C16       RD7+         C17       SD8-         C18       RD8-         C19       SD9-         C20       SD10+         C21       RD9+         C22       RD10-         C23       SD11-         C24       RD11-         C25       SD12-         C26       RD13-         C28       RD13+         C29       SD14-         C30       RD14- |

.

# WIRE-WRAP CONNECTOR PIN OUT DIAGRAM - HIGH TRUE, ROW A

| 27114<br>CONN.<br>OPIN NO.                  | SIGNAL<br>NMEM.                      | WIRE<br>Color |                                                                                                                                            |

|---------------------------------------------|--------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| A2                                          | SD0<br>SPAR0<br>SD1                  |               | Data Bit O, High True, SEND<br>Parity bit O,High True, SEND<br>Data Bit 1, High True, SEND                                                 |

|                                             | SD2                                  |               | Data Bit 2, High True, SEND                                                                                                                |

| A7<br>A8<br>A9<br>A10<br>A11                | SD3<br>RPAR1<br>SD4<br>SHIELD<br>SD5 |               | Data Bit 3, High True, SEND<br>Parity bit 1,Low True,RECEIVE<br>Data Bit 4, High True, SEND<br>Frame ground<br>Data Bit 5, High True, SEND |

| A14<br> A15<br> A16                         | SD6<br>PCTL<br>SD7                   |               | Data Bit 6, High True, SEND<br>PCTL , High True, SEND<br>Data Bit 7, High True, SEND                                                       |

| A17<br> A18<br> A19                         | CTL1                                 |               | CONTROL 1 , High True, SEND                                                                                                                |

| A20<br> A21<br> A22<br> A23<br> A24<br> A25 | GND<br>RD9<br>PFLG                   |               | Signal Ground<br>Data Bit 9,High True,RECEIVE<br>PFLAG ,High True,RECEIVE                                                                  |

| A29<br>A30                                  | ATTN                                 |               | ATTENTION ,High True,RECEIVE                                                                                                               |

| A31<br> A32                                 | STS2                                 |               | STATUS 2 ,High True,RECEIVE                                                                                                                |

# WIRE-WRAP CONNECTOR PIN OUT DIAGRAM - HIGH TRUE, ROW B

| 27114<br>CONN.<br>PIN NO.                                                   | SIGNAL                                                 | SIGNAL<br>DEFINITION                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <br> B1<br> B2                                                              | RDO                                                    | Data Bit 0, High True, RECEIVE                                                                                                                                                                                                        |

| B3                                                                          | RD1<br>RPARO                                           | Data Bit 1, High True, RECEIVE<br>Parity bit 0,High True, RECEIVE                                                                                                                                                                     |

| B6<br> B7<br> B8<br> B9                                                     | SPAR1<br>RD3                                           | Parity bit 1,High True, SEND<br>Data Bit 3, High True, RECEIVE                                                                                                                                                                        |

|                                                                             | RD5<br>PDIR                                            | Data Bit 5, High True, RECEIVE<br>DIRECTION , High True, SEND                                                                                                                                                                         |

| B15                                                                         | RD7<br>CTLO                                            | Data Bit 7, High True, RECEIVE<br>CONTROL 0 , High True, SEND                                                                                                                                                                         |

| B19<br> B20<br> B21<br> B22                                                 | SD10<br>GND                                            | Data Bit 10, High True, SEND<br>Signal Ground                                                                                                                                                                                         |

| B24                                                                         | STSO                                                   | STATUS 0 , High True, RECEIVE                                                                                                                                                                                                         |

| B26<br> B27<br> B28<br> B29<br> B30<br> B31                                 |                                                        | STATUS 1 , High True, RECEIVE<br>Data Bit 13, High True, RECEIVE<br>ATTENTION , High True, RECEIVE<br>Data Bit 14, High True, RECEIVE<br>CONTROL 2 , High True, SEND<br>Data Bit 15, High True, RECEIVE<br>STATUS 2 High True RECEIVE |

| B21<br> B22<br> B23<br> B24<br> B25<br> B26<br> B27<br> B28<br> B29<br> B30 | STS0<br>STS1<br>RD13<br>ATTN+<br>RD14+<br>CTL2<br>RD15 | Signal Ground<br>STATUS 0 , High True, RECEIVE<br>STATUS 1 , High True, RECEIVE<br>Data Bit 13, High True, RECEIVE<br>ATTENTION , High True, RECEIVE<br>Data Bit 14, High True, RECEIVE<br>CONTROL 2 , High True, SEND                |

# 27114 ERS, Nov 7, 1986

## WIRE-WRAP CONNECTOR PIN OUT DIAGRAM - HIGH TRUE, ROW C

| 27114<br>CONN.<br>PIN NO.                        | SIGNAL<br>NMEM.                              |                                                                                                                                                                                                       |

|--------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1<br>C2<br>C3<br>C4<br>C5<br>C6                 | RD2                                          | Data Bit 2, High True, RECEIVE                                                                                                                                                                        |

| C7<br> C8<br> C9<br> C10<br> C11<br> C12<br> C13 | RD4                                          | Data Bit 4, High True, RECEIVE                                                                                                                                                                        |

| C14<br>C15<br>C16                                | RD6                                          | Data Bit 6, High True, RECEIVE                                                                                                                                                                        |