HP 9000 Series 800 Computers

# HP 27114B

# **Asynchronous FIFO Interface**

**Reference Manual**

Hewlett-Packard Company Roseville Networks Division 8000 Foothills Boulevard Roseville, California 95678 Manual Part Number: 27114-90004 E0989 September 1989 Printed in U.S.A.

# **Printing History**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition or a new update is published. No information is incorporated into a reprinting unless it appears as a prior update; the edition does not change when an update is incorporated. Many product updates do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one-to-one correspondence between product updates and manual updates.

# Notice

The information contained in this document is subject to change without notice. Hewlett-Packard Company makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material. Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard. This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated into another language without the prior written consent of Hewlett-Packard.

Copyright © 1989 by Hewlett-Packard Company

# Contents

| Chapter 1 | General Information                           |

|-----------|-----------------------------------------------|

|           | Description                                   |

|           | Replacement Manuals 1-2                       |

|           | Equipment Supplied 1-3                        |

|           | Options 1-3                                   |

|           | Other Recommended Equipment                   |

|           | Identifying the AFI 1-4                       |

|           | System Requirements 1-4                       |

|           | System Configuration 1-5                      |

| Chapter 2 | Configuration and Installation                |

| •         | Protecting the AFI Against ESD 2-1            |

|           | Unpacking the AFI 2-2                         |

|           | Default Configuration 2-2                     |

|           | Factory Jumper Settings 2-2                   |

|           | Reset Default Conditions                      |

|           | Choosing the Mode for the External Device 2-5 |

|           | Single-Ended Configurations 2-5               |

|           | Single-Ended, High-True Logic Applications    |

|           | Mode Jumper Installation 2-7                  |

|           | High-True Resistor Networks 2-7               |

|           | Single-Ended, Low-True Logic Applications     |

|           | Mode Jumper Installation 2-9                  |

|           | Low- True Resistor Networks 2-9               |

|           | Differential Configurations                   |

|           | Mode Jumper Installation                      |

|           | Line Termination Resistor Networks            |

|           | Handshake Timing Control Jumpers              |

|           | PCTL Pulse Delay/Extension                    |

|           | PFLG Filtering                                |

|           | Cables                                        |

|           | Custom Length Cables                          |

|           | Single-Ended Cables                           |

|           | Differential Cables                           |

|           | Wiring the Custom AFI Cable                   |

|           | Planning the AFI Cable                        |

|           | Constructing the Cable                        |

# Chapter 2

# er 2 Configuration and Installation (cont'd)

| Installing the AFI               |

|----------------------------------|

| Selecting a Slot                 |

| Orienting the PCA                |

| Inserting the PCA                |

| Connecting the Cable             |

| Startup and Verification         |

| Applying Power to the PCA        |

| Configuring the Operating System |

| Testing the AFI                  |

| Connecting the Peripheral Device |

| Grounding the Cable              |

| Wiring the Peripheral Device     |

| Logic Sense                      |

Chapter 3

4

# Theory of Operation

| Frontplane Interface Control Circuitry                 |   | 22  |

|--------------------------------------------------------|---|-----|

| Frontplane Signal Definitions                          |   |     |

|                                                        |   |     |

| RD[15:0]                                               |   |     |

| SD[15:0]                                               |   |     |

| PCTL                                                   |   | 3-4 |

| PFLG                                                   |   | 3-4 |

| PDIR                                                   |   | 3-4 |

| CTL[5:0]                                               |   | 3-4 |

| STS[5:0]                                               |   | 3-5 |

| ATTN                                                   |   | 3-5 |

| HEND                                                   |   | 3-5 |

| PEND                                                   |   | 3-5 |

| Shield Ground                                          |   | 3-6 |

| Signal Ground                                          |   | 3-6 |

| Line Termination Resistor Networks                     |   | 3-7 |

| Differential Line Termination                          |   | 3-7 |

| Single-Ended Line Termination                          |   |     |

| Burst Mode Data Transfer to the CIO Backplane          |   |     |

| Midplane Circuitry                                     |   |     |

| Register Definitions                                   |   |     |

| Data Register (Read or Write Register 0)               |   |     |

| CIO Sense Register (Read Register 1)                   |   |     |

| CIO Control Register (Write Register 1)                |   |     |

| CIO ID Register (Read Register 3)                      |   |     |

| AFI Status Register (Read Register 7)                  |   |     |

| AFI Control Register (Write Registers 7 and B)         |   |     |

| CIO Status Register (Read Register 9)                  |   |     |

| AFI Transfer Counter Register (Read Registers A and B) |   |     |

| AFI Transfer Counter(Write Registers A and B)          |   |     |

|                                                        | • |     |

| Chapter 3 | Theory of Operation (cont'd)    |

|-----------|---------------------------------|

|           | Midplane Circuitry (cont'd)     |

|           | Register Operation              |

|           | Interrupt Handling              |

|           | Backplane Interface Circuitry   |

|           | Backplane Data Transfer         |

|           | Output Transfers                |

|           | Input Transfers                 |

|           | Handshake Control State Machine |

|           | Frontplane Handshaking          |

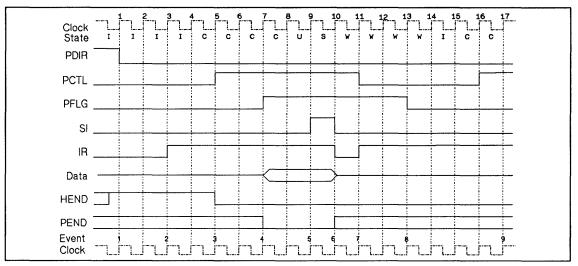

|           | FIFO Handshaking Mode           |

|-----------|---------------------------------|

|           | Full Master Handshake Output    |

|           | Full Slave Input Handshake      |

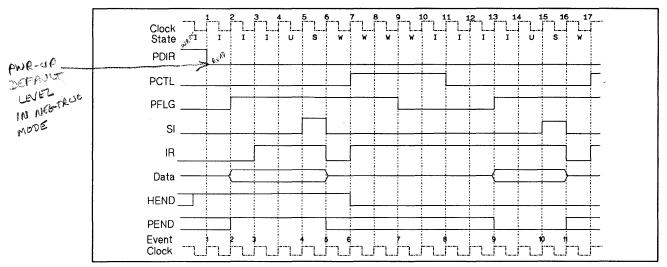

|           | Full Master Input Handshake     |

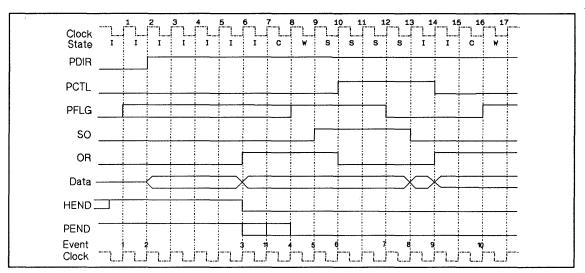

|           | Full Slave Output Handshake     |

|           | Backplane Handshaking           |

| Chapter 4 | Application Design              |

|           | Transfers through the Backplane |

|           | Output Transfers                |

|           | Input transfers                 |

|           | Application Planning            |

|           | Writing the Application         |

#### Chapter 5 Hardware Troubleshooting

| Field Replaceable Units       |     | • | • |     | • | <br>• | • | • | • | • | • | • |    | 5-1 |

|-------------------------------|-----|---|---|-----|---|-------|---|---|---|---|---|---|----|-----|

| Troubleshooting Strategy      | • • | • | • |     |   | <br>• |   |   |   |   |   | • |    | 5-2 |

| Maintenance Aids              |     |   |   |     |   |       |   |   |   |   |   |   |    |     |

| AFI Device Adapter Diagnostic | • • | • | • |     | • |       |   |   | • | • | • | • | •• | 5-3 |

| Removing the AFI              |     | • | • | ••  |   |       |   |   |   |   | • | • |    | 5-5 |

| Reshipping the AFI            |     | • | • | ••• | • | <br>• |   |   | • |   | • | • |    | 5-5 |

| Appendix A | Connector and Cables                                 |

|------------|------------------------------------------------------|

|            | Frontplane Connector                                 |

|            | Differential Signal Cable Assignments A-2            |

|            | Single-Ended, High-True Signal Cable Assignments A-4 |

|            | Single-Ended, Low-True Signal Cable Assignments A-6  |

|            | Cable Pin Assignments for Cable 27114-63001 A-8      |

|            | Alternative Termination of Cable                     |

| Appendix B | Product History                                      |

# **Product History**

| Error Messages             |

|----------------------------|

| Schematics                 |

| Address Decoder PAL        |

| Timing Extension PAL       |

| FIFO PAL                   |

| Interrupt Control PAL      |

| Backplane Control PAL D-12 |

| AFI Schematic Diagrams     |

|                            |

6

# Figures

| Chapter 1 | General Information                                                 |

|-----------|---------------------------------------------------------------------|

|           | Figure 1-1. The AFI Identification Stickers                         |

|           | Figure 1-2. AFI in a Typical Hewlett-Packard System         1-5     |

| Chapter 2 | Configuration and Installation                                      |

| _         | Figure 2-1. Locations of Configuration Jumpers 2-4                  |

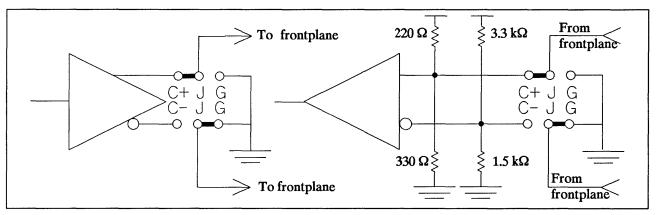

|           | Figure 2-2. Single-Ended, High-True Configuration 2-6               |

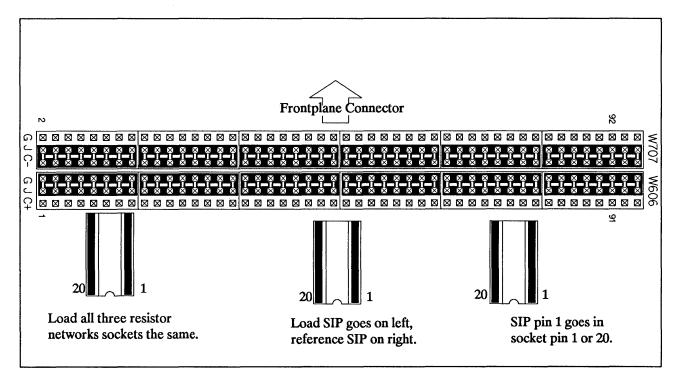

|           | Figure 2-3. Installing the High-True Resistor Network SIPs 2-6      |

|           | Figure 2-4. Driver/Receiver Grounding in Single-Ended,              |

|           | High-True Mode 2-7                                                  |

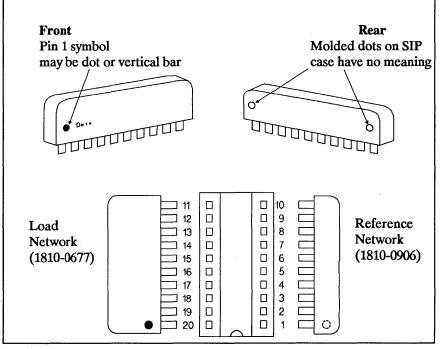

|           | Figure 2-5. Single-Ended, Low-True Configuration 2-8                |

|           | Figure 2-6. Installing the Low-True Resistor Network SIPs 2-8       |

|           | Figure 2-7. Driver/Receiver Grounding in Single-Ended,              |

|           | Low-True Mode 2-9                                                   |

|           | Figure 2-8. Differential Mode Configuration                         |

|           | Figure 2-9. Installing the Differential Resistor Network DIPs 2-10  |

|           | Figure 2-10. Driver/Receiver Connection in Differential Mode 2-10   |

|           | Figure 2-11. Output Control Jumpers                                 |

|           | Figure 2-12. Example of a Pulse Length Delay/ Extension 2-13        |

|           | Figure 2-13. Example of Window Rejecting PFLG Signal 2-14           |

|           | Figure 2-14. Filling in the AFI Cabling Worksheet                   |

|           | Figure 2-15. Wiring the Custom AFI Cable                            |

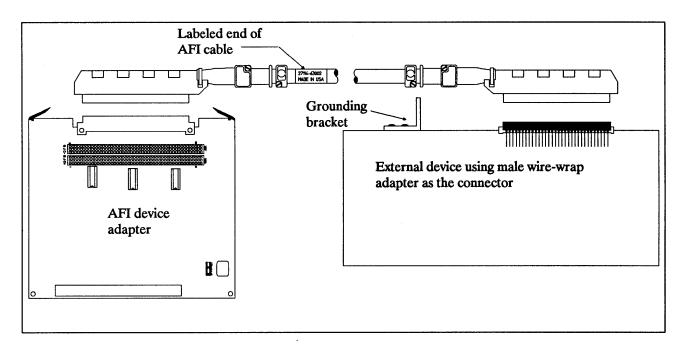

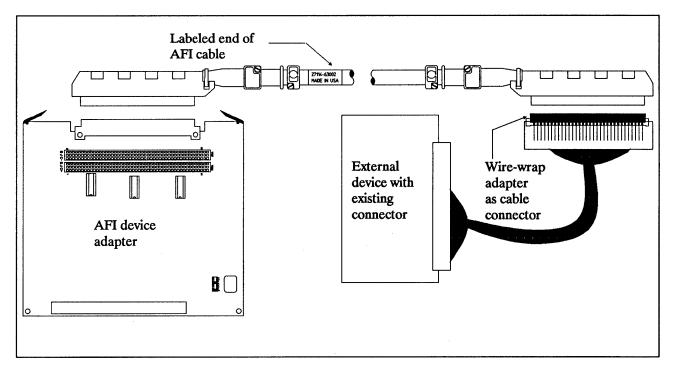

|           | Figure 2-16. A Typical AFI Installation                             |

|           | Figure 2-17. A Cable Grounding Bracket                              |

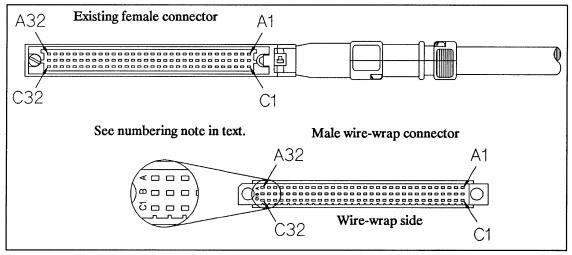

|           | Figure 2-18. The Wire-Wrap Pinout Orientation                       |

|           | Figure 2-19. The Wire-Wrap Adapter as the External Device           |

|           | Connector                                                           |

|           | Figure 2-20. The Wire-Wrap Adapter in an Intermediate Cable 2-28    |

|           | Figure 2-21. Differential Wiring for External Device Connector 2-29 |

|           | Figure 2-22. Single-Ended Cabling to External Device                |

|           |                                                                     |

Chapter 3

# Theory of Operation

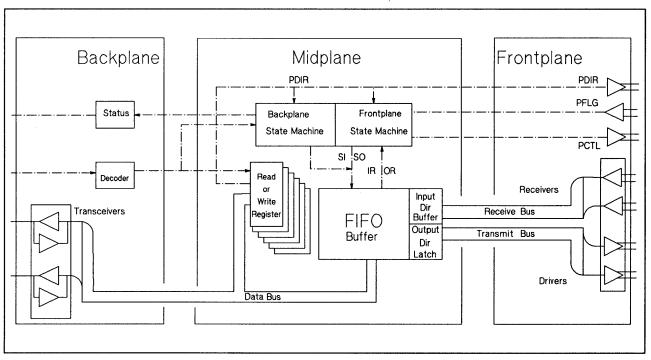

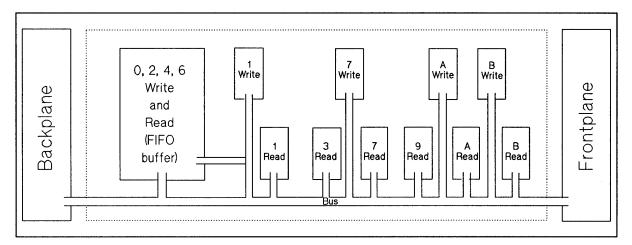

| Figure 3-1. The AFI Planes         3-1     |

|--------------------------------------------|

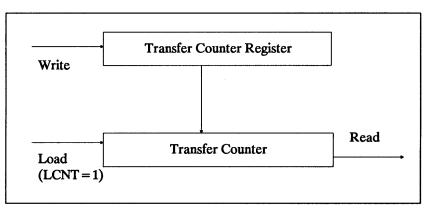

| Figure 3-2. Transfer Counter Operation     |

| Figure 3-3. AFI Registers on the Data Bus  |

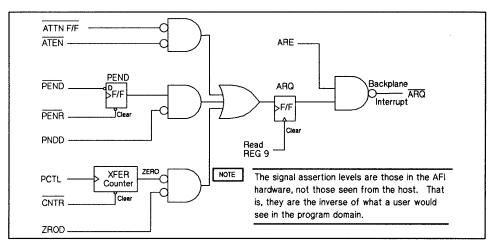

| Figure 3-4. AFI Interrupt Circuitry        |

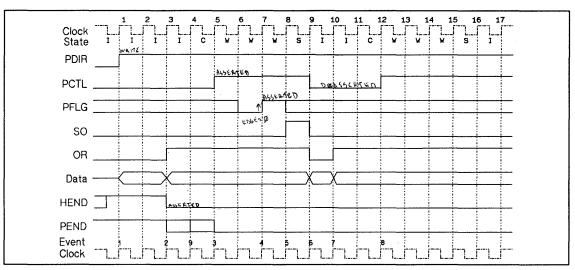

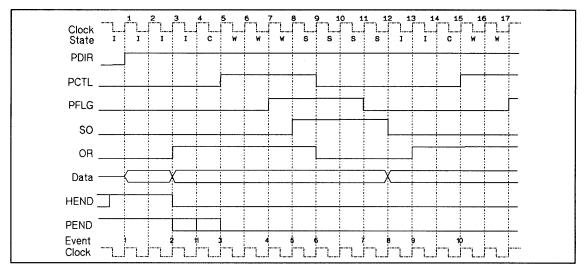

| Figure 3-5. Output FIFO Handshake          |

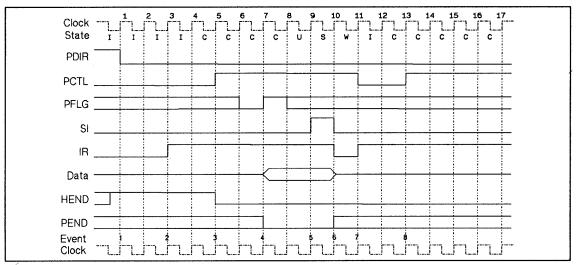

| Figure 3-6. Input FIFO Handshake           |

| Figure 3-7. Output Full Master Handshake   |

| Figure 3-8. Input Full Slave Handshake     |

| Figure 3-9. Input Full Master Handshake    |

| Figure 3-10. Output Full Slave Handshake   |

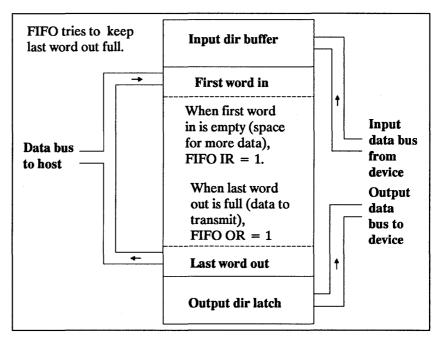

| Figure 3-11. FIFO Buffer Signals IR and OR |

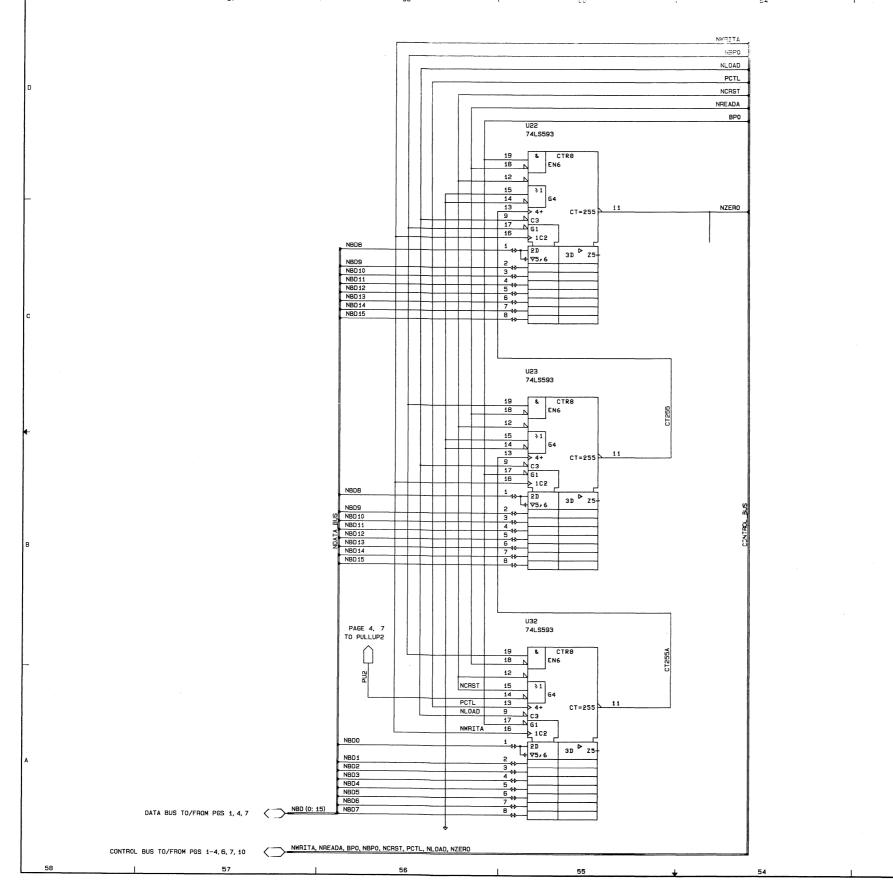

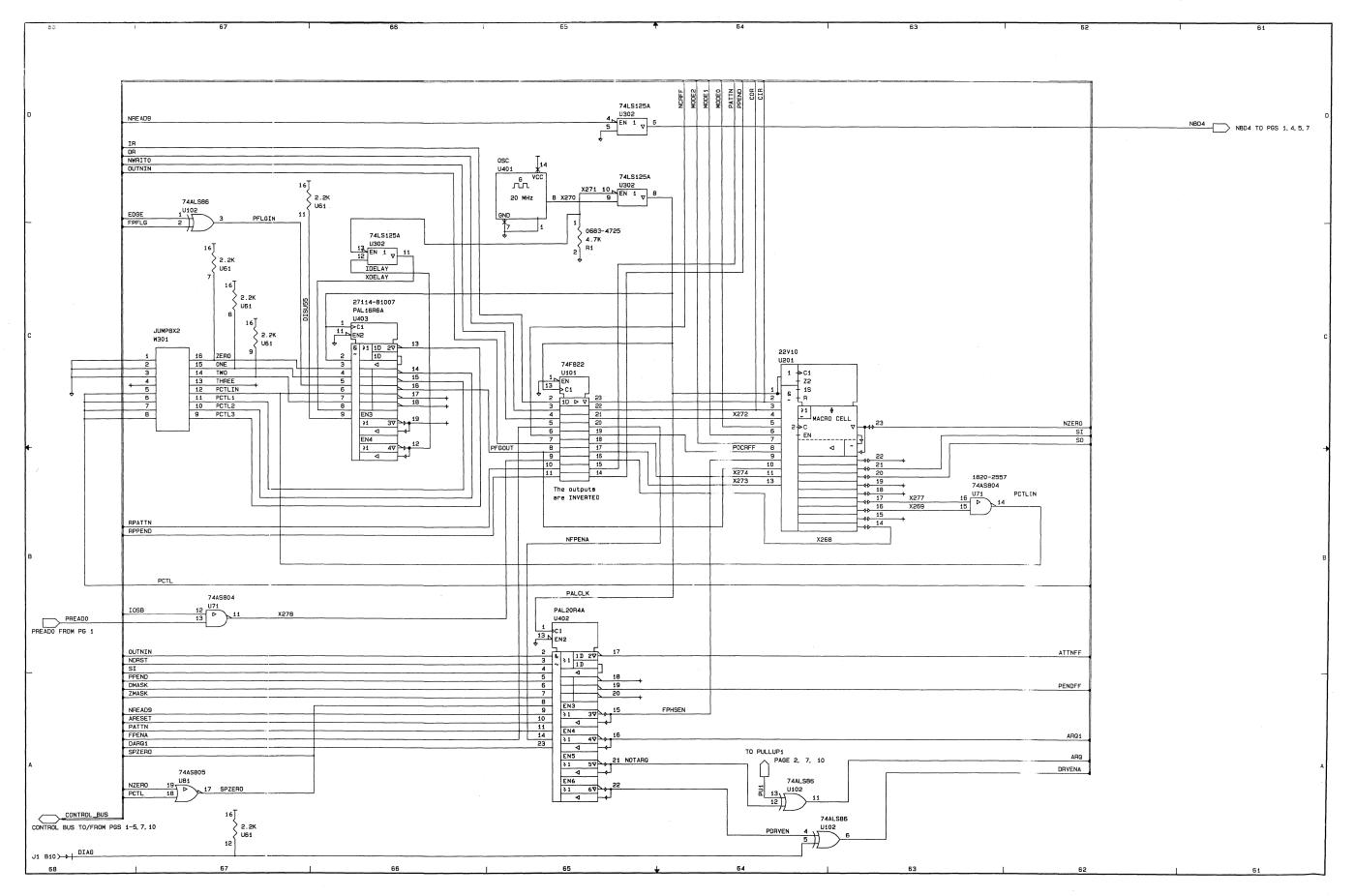

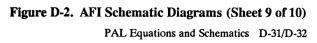

# Appendix DPAL Equations and Schematics

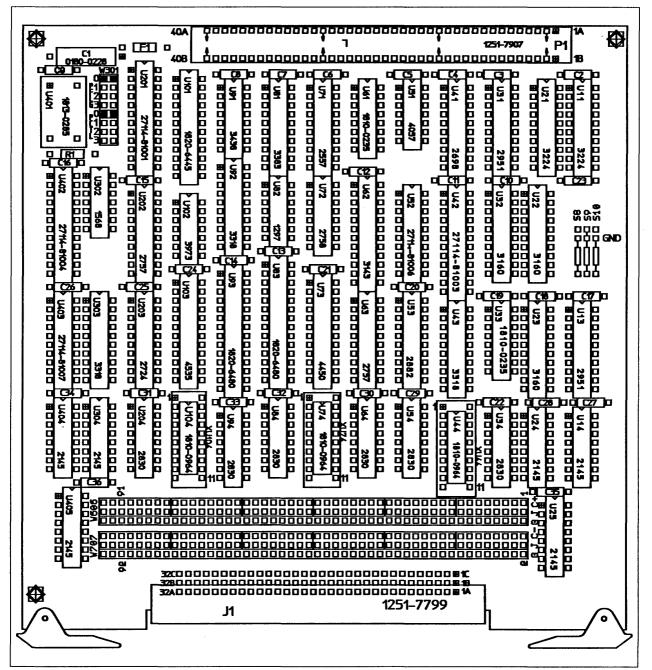

| Figure D-1.  | AFI Parts Location Diagram               | D-14      |

|--------------|------------------------------------------|-----------|

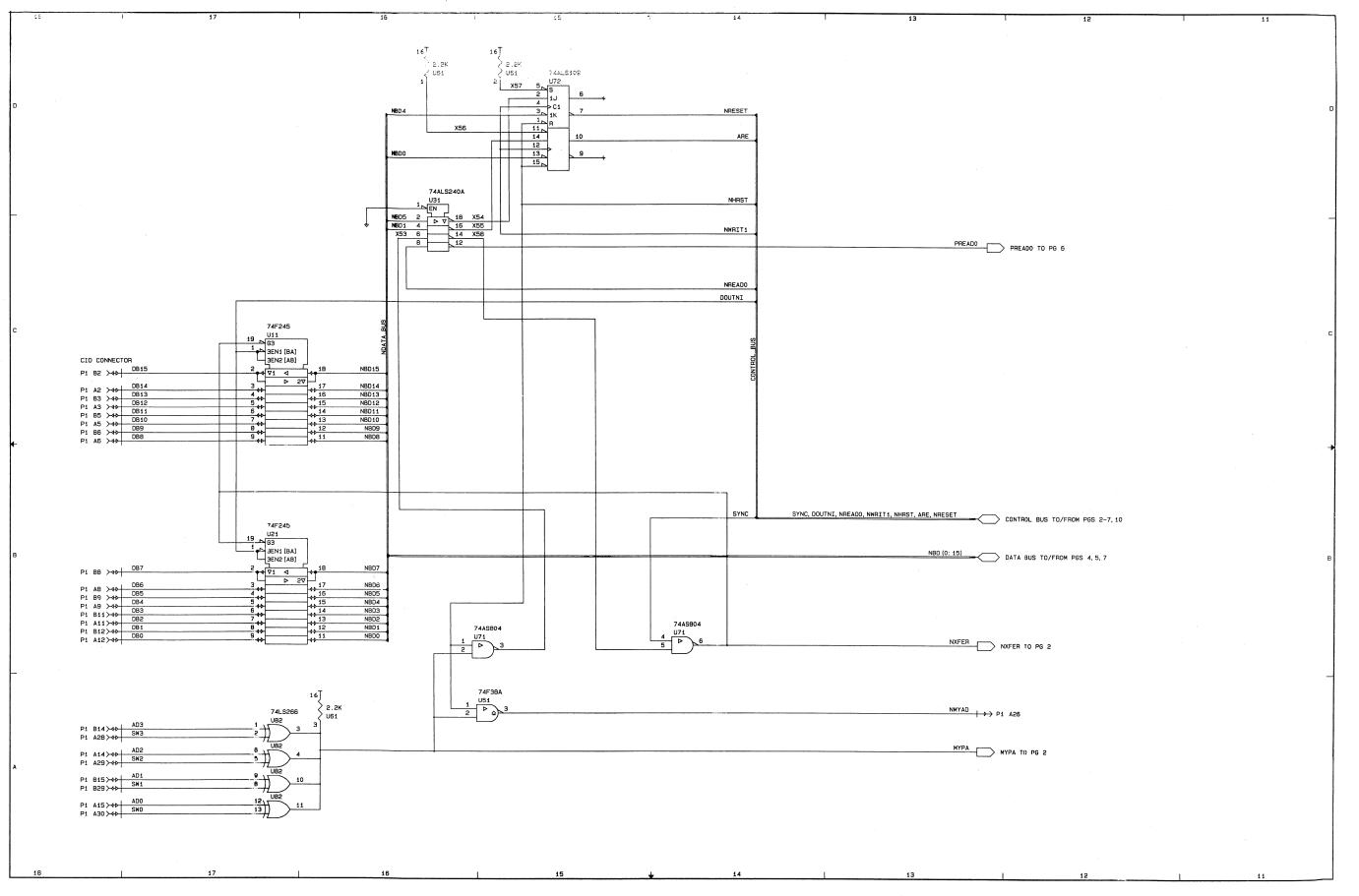

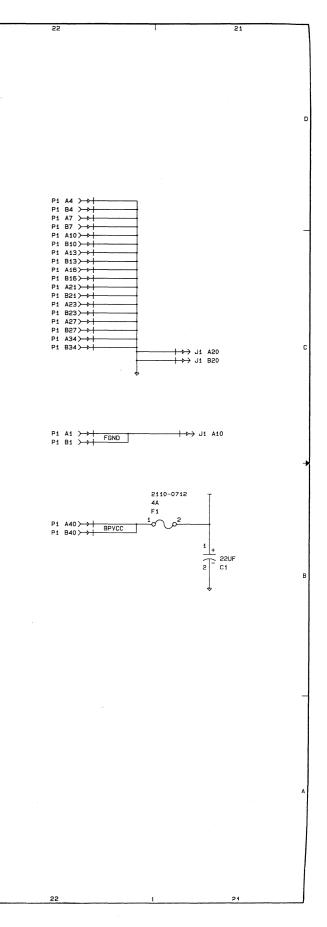

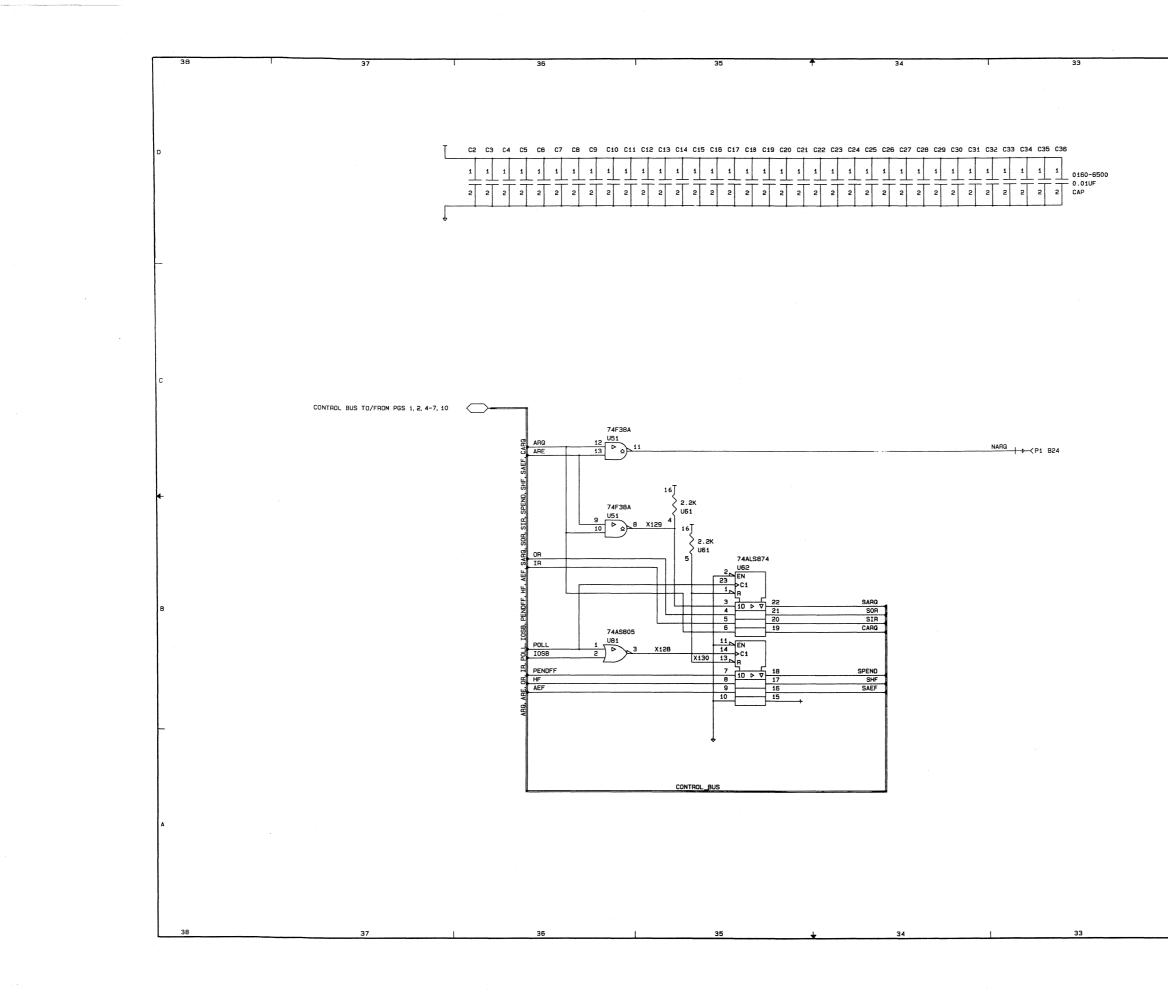

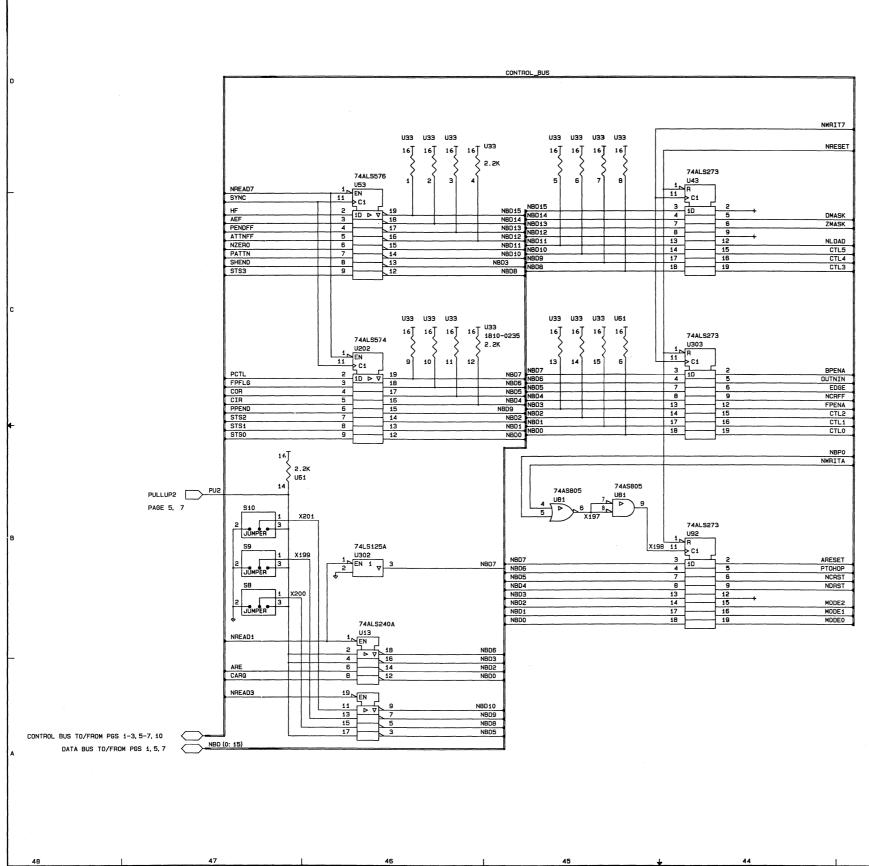

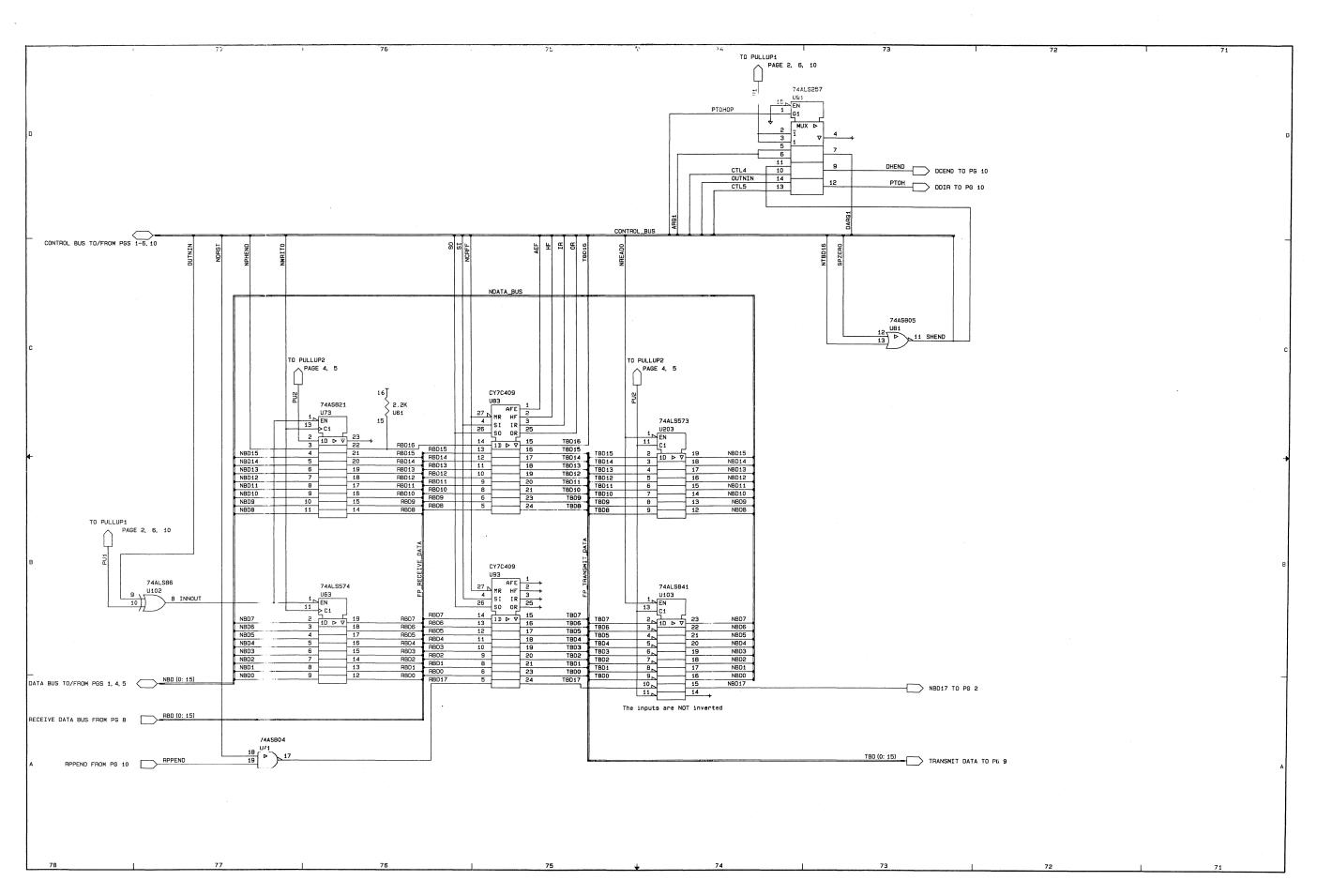

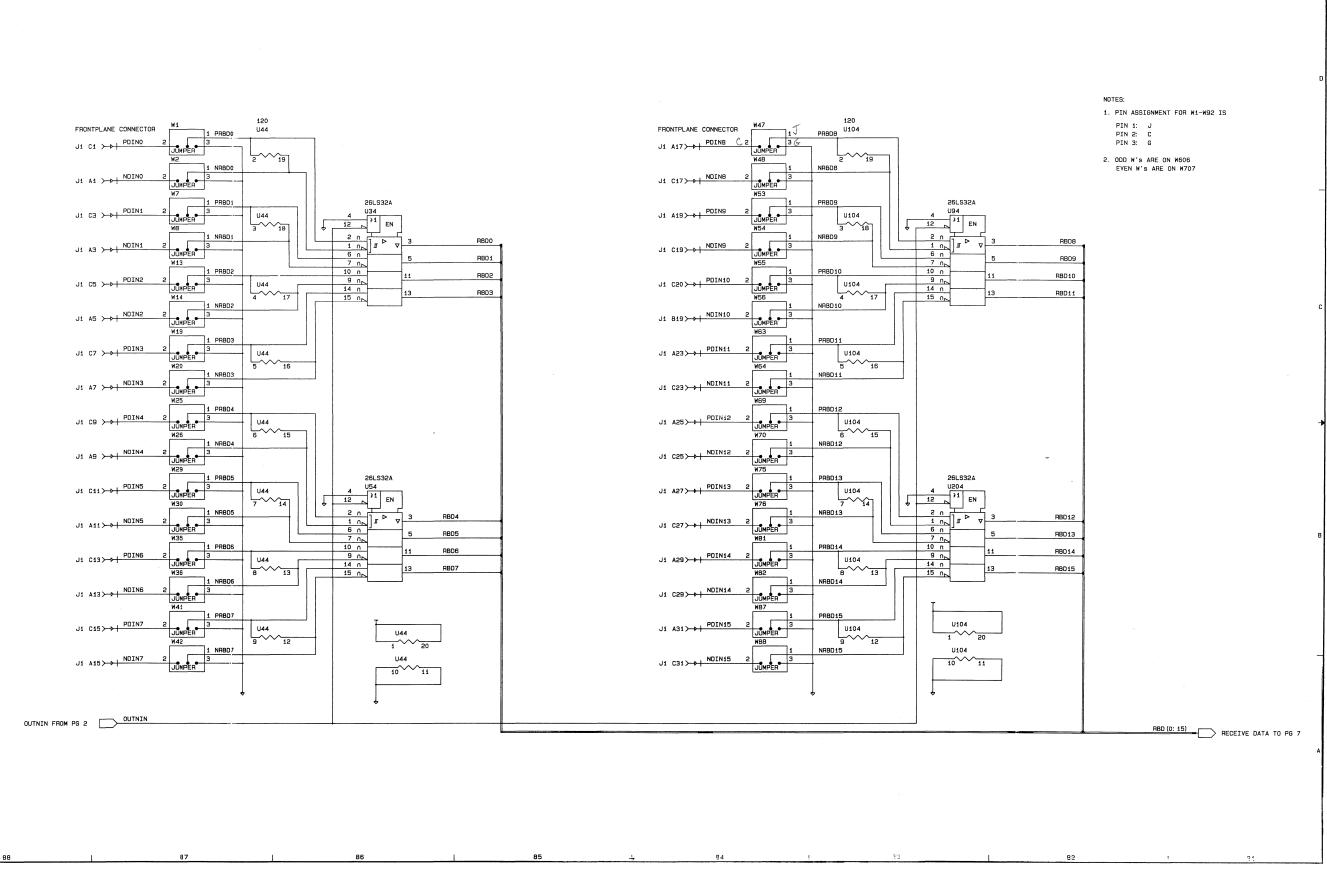

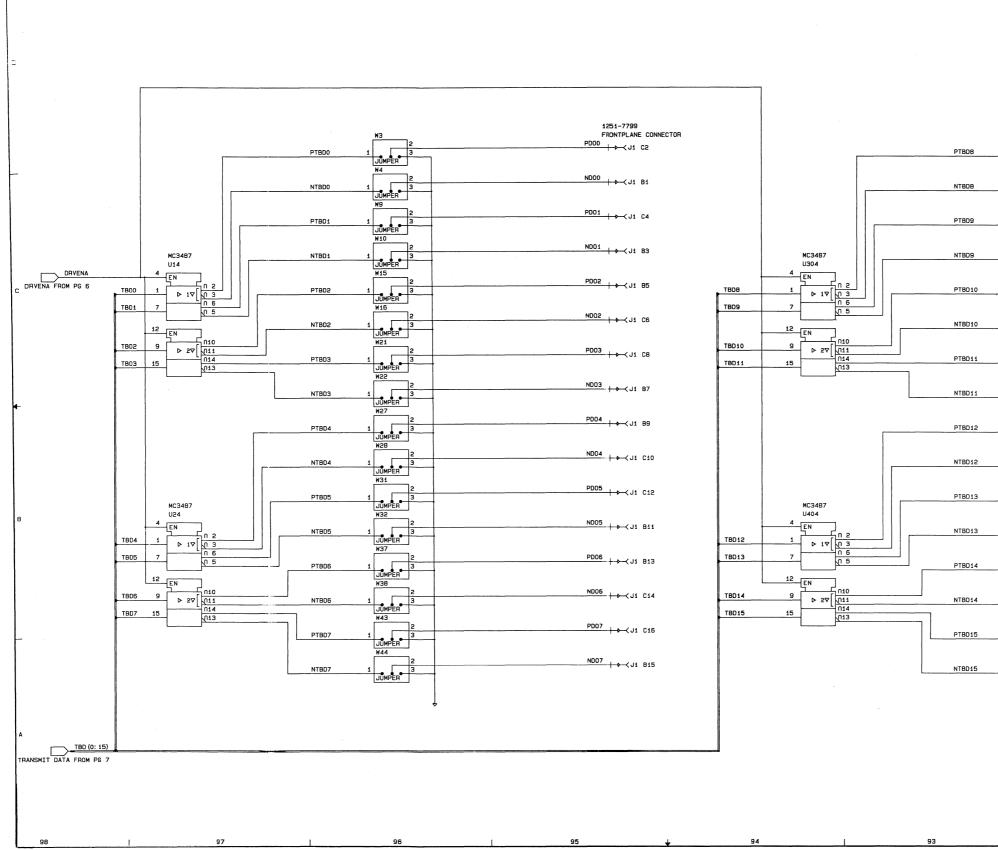

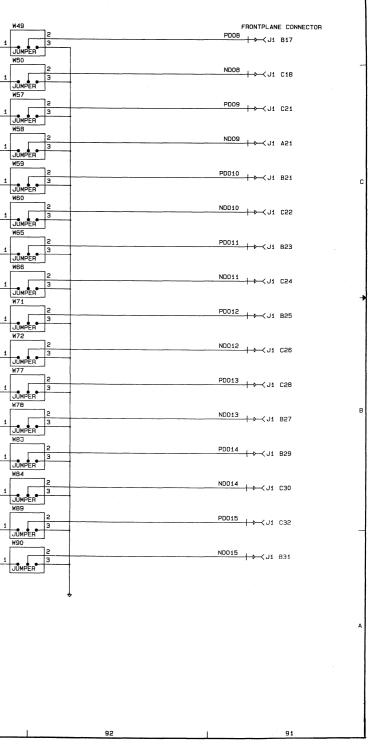

| Figure D-2.  | HP27114B AFI Schematics (Sheet 1 of 10)  | D-15/D-16 |

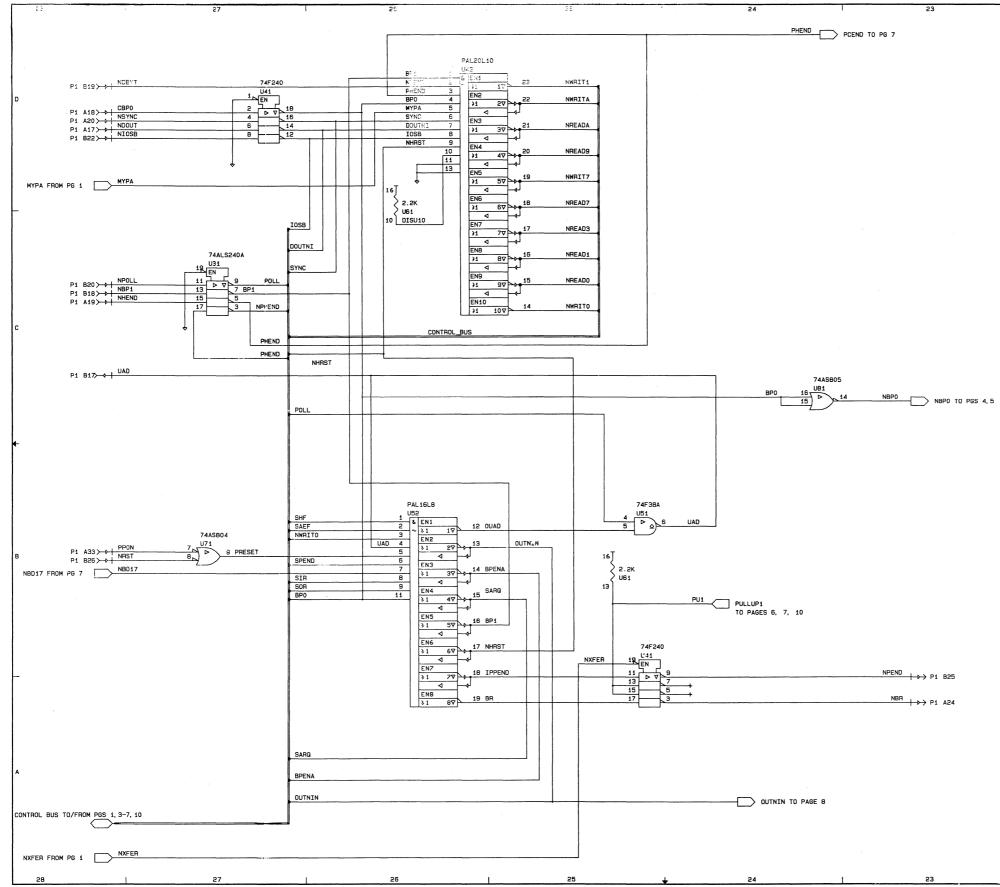

| Figure D-2.  | HP27114B AFI Schematics (Sheet 2 of 10)  | D-17/D-18 |

| Figure D-2.  | HP27114B AFI Schematics (Sheet 3 of 10)  | D-19/D-20 |

| Figure D-2.  | HP27114B AFI Schematics (Sheet 4 of 10)  | D-21/D-22 |

| Figure D-2.  | HP27114B AFI Schematics (Sheet 5 of 10)  | D-23/D-24 |

| Figure D-2.  | HP27114B AFI Schematics (Sheet 6 of 10)  | D-25/D-26 |

| Figure D-2.  | HP27114B AFI Schematics (Sheet 7 of 10)  | D-27/D-28 |

| Figure D-2.  | HP27114B AFI Schematics (Sheet 8 of 10)  | D-29/D-30 |

|              | HP27114B AFI Schematics (Sheet 9 of 10)  | D-31/D-32 |

| ' Figure D-2 | HP27114B AFI Schematics (Sheet 10 of 10) | D-33/D-34 |

# **Tables**

| Chapter 1  | General Information                                                     |

|------------|-------------------------------------------------------------------------|

|            | Table 1-1. HP 27114B AFI Specifications    1-6                          |

|            | Table 1-2. External Device Driver and Receiver Requirements         1-6 |

|            | Table 1-3. Factory Configuration    1-7                                 |

| Chapter 2  | Configuration and Installation                                          |

| -          | Table 2-1. Factory Configuration    2-2                                 |

|            | Table 2-2. Default Configuration    2-3                                 |

|            | Table 2-3. PCTL Pulse Extension Jumpers                                 |

|            | Table 2-4. PFLG Filtering Jumpers                                       |

|            | Table 2-5. AFI Cabling Worksheet                                        |

| Chapter 3  | Theory of Operation                                                     |

| <b>-</b>   | Table 3-1. Program Domain to AFI Hardware Domain Conversion         3-2 |

|            | Table 3-2. Register Access Address Decoding       3-9                   |

|            | Table 3-3. FIFO Buffer Status as Shown by AEF and HF                    |

|            | Table 3-4. Mode Bit Patterns   3-18                                     |

| Chapter 4  | Application Design                                                      |

|            | Table 4-1. Device Requirements Table   4-3                              |

| Appendix A | Connector and Cables                                                    |

|            | Table A-1. AFI Frontplane Connector (J2) Pin Assignments       A-1      |

|            | Table A-2. AFI Cable (27114-63001) Signal Locations                     |

|            | (Differential Mode)                                                     |

|            | Table A-3. AFI Cable (27114-63001) Signal Locations                     |

| ÷          | (Single-Ended, High-True)                                               |

|            | Table A-4. AFI Cable (27114-63001) Signal Locations                     |

|            | (Single-Ended, Low True)                                                |

|            | Table A-5. AFI Cable (27114-63001) Wiring Assignments                   |

|            | Table A-6. Conductor Assignment for Cable 27114-63001                   |

The Hewlett-Packard Asynchronous FIFO Interface (AFI) device adapter (interface card) fits all HP Precision Architecture Computers using the Channel I/O Bus (CIB). This chapter gives general information about the AFI, its requirements and specifications, and what you need to make it work. Specific information follows in subsequent chapters and appendixes. Throughout the manual, all part numbers (in parentheses) refer to Hewlett-Packard part numbers, unless noted otherwise.

#### Note

The AFI is a very versatile I/O device adapter. In order to make it function, you must understand your application, the external (peripheral) device, and the AFI device adapter. Chapter 3, *Theory of Operation*, contains the material you need to know to understand the AFI. Chapter 4, *Application Design*, tells you how to plan an application. Please read both of these chapters before trying to program the AFI or design a new external device.

This manual is intended for Hewlett-Packard Customer Engineers (CEs), HP Systems Engineers (SEs) and customers. Some of the material presented is inappropriate to some of these groups, and requires specialized training offered by Hewlett-Packard Company. If you do not understand a topic, check to be sure the subject matter covered is not identified as needing such training. If it is, contact HP for assistance before proceeding.

# Description

The AFI has five key components:

- The printed circuit assembly (PCA) (part number 27114-60101) When shipped from the factory, the PCA is configured for differential mode. Therefore, only resistor networks for differential mode are included.

- The connecting cable (part number 27114-63001) works either in a differential or a single-ended application. The cable component also includes a 96-pin, male, wire wrap adapter (part number 1252-1643) used for the peripheral connector or as the connector for an extension cable.

- The reference manual kit (part number 27114-92001) which contains this manual (the Asynchronous FIFO Interface Reference Manual) (part number 27114-90004), the Asynchronous FIFO Interface Programmer's Guide (part number 27114-90003), the Asynchronous FIFO Interface Application Notes (part number 5958-9044) and the Asynchronous FIFO Interface Performance Brief (part number 5958-9045).

- The software driver (gpio0) part of the HP-UX Fundamental Operating System included with your computer.

- The application software (which you supply).

For an AFI application to function, you must have each of these parts. Hewlett-Packard Company does not supply the application software, but the reference manuals explain how to write one. If you will be using the Hewlett-Packard Device I/O Library (DIL), you should also have available the *Device I/O and User Interfacing* (part number 97089-90054) manual from the *HP 9000 Programmer Series: Concepts and Tutorials*.

#### **Replacement Manuals**

The manuals shipped with your AFI come as a single unit. However, to order replacement manuals, you need to order the contents individually.

- Asynchronous FIFO Interface Reference Manual (27114-90004).

- Asynchronous FIFO Interface Programmer's Guide (27114-90003).

- Asynchronous FIFO Interface Application Notes (5958-9044).

- Asynchronous FIFO Interface Performance Brief (5958-9045).

# **Equipment Supplied**

Of the five components, three are included with the AFI product:

- The PCA (27114-60101).

- The connecting cable (27114-63001) and wire wrap adapter (1252-1643).

- The reference manual kit (27114-92001).

**Options** Hewlett-Packard offers many options to adapt the features of the AFI to your needs. The options are:

| Option #0B0:                   | Deletes the manual kit (part number 27114-92001).                                                                                                                                                             |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Option #002:</b>            | Adds the loopback test hood (part number 27114-60002).                                                                                                                                                        |

| <b>Option #003:</b>            | Single-ended option.                                                                                                                                                                                          |

|                                | Adds three reference SIP resistor networks (part number 1810-0906) and three load SIP resistor networks (part number 1810-0677).                                                                              |

| Option #004:                   | 12-meter cable option.                                                                                                                                                                                        |

|                                | Deletes the 3-meter, 96-conductor cable (part number 27114-63001).<br>Adds a 12-meter, 96-conductor cable (part number 27114-63003).                                                                          |

| Option #005:                   | Deletes the 3-meter, 96-conductor cable (part number 27114-63001).                                                                                                                                            |

| Other Recommended<br>Equipment | You need the loopback hood (part number 27114-60002) to run the AFI diagnostic tests included with the HP-UX Fundamental Operating System. If you ordered option #002, you already have a loopback test hood. |

# Identifying the AFI

Every product Hewlett-Packard makes has a product number (such as HP 27114B), and each component of the product has a part number. You can identify the AFI PCA by locating the two paper stickers attached to the fiberglass board. They will look like this:

| 27114-66666 21   | 2823A56789     | DIV |

|------------------|----------------|-----|

| A-4321 52A654321 | MADE IN U.S.A. | 52  |

#### Figure 1-1. The AFI Identification Stickers

The information on the stickers will help HP give you faster help if you need it. Copy these identification numbers to a convenient location, such as your log book, where they will be available when you call.

# System<br/>RequirementsFor the AFI to operate properly, the host computer system must meet<br/>certain requirements.The computer must be a Hawlett Backard 0000 series 800 computer

- The computer must be a Hewlett-Packard 9000 series 800 computer with the CIO backplane. Use of the HP 27114B AFI card in any other computer will not work.

- The HP-UX Fundamental Operating System must be release 7.0 or later to take advantage of all the features and diagnostics.

# **System Configuration**

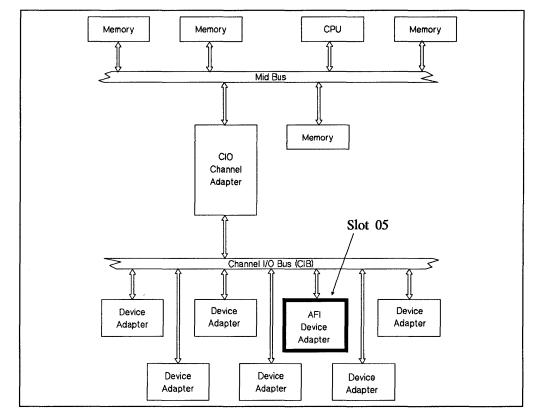

Figure 1-2 is a block diagram showing a typical HP computer system with an AFI installed.

Figure 1-2. AFI in a Typical Hewlett-Packard System

You must place the AFI in the lowest group of the card cage slots (slots 0-7). The default slot is 5. Lower numbered slots have priority over higher numbered slots. Refer to the *System Administrator's Manual* for information on configuring the AFI device adapter into your computer system.

| Features                                | 16-bit, half-duplex transfers with separate data input and output lines.                                          |                  |                    |                                       |                 |               |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------|--------------------|---------------------------------------|-----------------|---------------|

|                                         | Differential re                                                                                                   | ceivers and driv | vers; optional sin | gle-ended, high                       | - (+5 V) or low | - (GND) true. |

|                                         | Three asynchronous handshaking modes: Full Master, Full Slave and FIFO Master.                                    |                  |                    |                                       |                 |               |

|                                         | Up to 64 words of FIFO buffering in the input direction and 55 words in output transfers.                         |                  |                    |                                       |                 |               |

|                                         |                                                                                                                   |                  | • •                | plus interrupt, d<br>xclusive. See ch |                 |               |

| Cable<br>Specification<br>(27114-63001) | Impedance: approximately 120 $\Omega$ .<br>Resistance/meter: 190 m $\Omega$ .<br>Propagation delay: 5.5 ns/meter. |                  |                    |                                       |                 |               |

| Electrical and                          | Backplane                                                                                                         | Cu               | rrent              | Power D                               | issipation      |               |

| Cooling                                 | Voltage                                                                                                           | typical          | 2σ                 | typical                               | 2σ              |               |

| Requirements                            | +5 V                                                                                                              | 2.63 A           | 2.8 A              | 13.15 W                               | 14.00 W         |               |

### Table 1-1. HP 27114B AFI Specifications

Table 1-2. External Device Driver and Receiver Requirements

| Peripheral<br>Line Driver | Single-Ended Mode:<br>minimum $V_{OH} = 2.4V @ I_{OH} = -2.6mA$ .<br>maximum $V_{OL} = 0.4V @ I_{OL} = 24 mA$ .<br>Differential Mode: RS-422 or RS-485 compatible.       |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Peripheral<br>Receiver    | Single-Ended Mode:<br>minimum $V_{IH} = 2.0 V @ I_{IH} = 20 \mu A$ .<br>maximum $V_{IL} = 0.8 V @ I_{IL} = -0.4 mA$ .<br>Differential Mode: RS-422 or RS-485 compatible. |

÷

| AFI Features                                                                                                                                             | Options                                                         | Factory Setting                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------|

| signal mode                                                                                                                                              | differential or single-<br>ended signals                        | differential signals                                  |

| line termination<br>resistor networks                                                                                                                    | differential or single-<br>ended line termination<br>resistors* | Differential line<br>termination resistor<br>networks |

| PCTL pulse width extension time                                                                                                                          | 0–150 ns<br>in 50 ns increments                                 | 0 ns                                                  |

| PFLG pulse width filtering time                                                                                                                          | 0–50 ns to 150–200 ns<br>with a 50 ns window                    | 0–50 ns                                               |

| * DIP line termination resistor networks are used for differential signals.<br>SIP line termination resistor networks are used for single-ended signals. |                                                                 |                                                       |

Table 1-3. Factory Configuration

This chapter contains the following information for the HP 27114B Asynchronous FIFO Interface (AFI) device adapter:

- Protecting the AFI against electrostatic discharge.

- Unpacking and inspection.

- Factory configuration.

- Configuration jumper placement.

- Cabling information, including pinouts.

- Installing the PCA and cable.

- Connecting the external device.

- Start-up and verification.

# Protecting the AFI Against ESD

Some of the components used in this product are susceptible to damage by electrostatic discharge (ESD). Refer to the safety information at the front of your host system manual before handling the AFI printed circuit assembly (PCA). The PCA is shipped in a static-shielding bag. Leave it in the bag until you install it in the computer system. When handling the PCA outside of this container, do not touch any components. Hold the PCA by its edges, avoid working in a carpeted area, use a grounding wrist strap, reduce unnecessary movements; all of these precautions will reduce the chances of ESD damage.

#### Caution

ESD can destroy any electronic assembly. Failure to follow anti-ESD procedures can invalidate your warranty.

Ideally, while you are configuring the device adapter for your application, you will have a special anti-ESD work area set aside. If you do not, we suggest using a work station kit like the one provided with part number 9300-1155. It contains a grounding wrist strap, a conductive work mat and other items to shunt any charge safely to ground. Instructions for use come with the kit.

# Unpacking the AFI

Carefully examine the condition of the box and other packaging material. If you discover any damage, stop. Call your HP Sales and Support Office. Have the carrier's agent present to ensure that your claim will be upheld in case of damage. The Sales and Support Office will help with these details. Keep the packaging material for later use.

# Default Configuration

## Factory Jumper Settings

Table 2-1 shows the physical settings on the PCA as shipped by the factory. Table 2-2 shows the AFI default configuration on power-up.

The AFI has several options selected using jumpers. See table 2-1. These options are:

- Differential or single-ended mode.

- Length of PCTL pulse extension, from 0 to 150 ns in 50 ns increments.

- PFLG filter, a window of 50 ns, from 0–50 ns to 150–200 ns.

| Options                                                         | Factory Setting                                                                                                                                                         |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| differential or single-<br>ended signals                        | differential signals                                                                                                                                                    |

| differential or single-<br>ended line termination<br>resistors* | Differential line<br>termination resistor<br>networks                                                                                                                   |

| 0–150 ns<br>in 50 ns increments                                 | 0 ns                                                                                                                                                                    |

| 0–50 ns to 150–200 ns<br>with a 50 ns window                    | 0–50 ns                                                                                                                                                                 |

|                                                                 | differential or single-<br>ended signals<br>differential or single-<br>ended line termination<br>resistors*<br>0–150 ns<br>in 50 ns increments<br>0–50 ns to 150–200 ns |

#### **Table 2-1. Factory Configuration**

\* DIP line termination resistor networks are used for differential signals. SIP line termination resistor networks are used for single-ended signals.

During the assembly of the device adapter, Hewlett-Packard inserts the jumpers for these choices:

- Differential mode.

- PCTL pulse extension of 0 ns.

- PFLG filtering of 0–50 ns.

To choose an alternative setting, remove the appropriate jumper and place it in another position. This chapter explains these procedures in each configuration section.

## Reset Default A Conditions s

After recovering from any reset condition, including the initial state after switching the computer on, the AFI device adapter takes on certain characteristics defined by its software driver defaults. See table 2-2.

| Driver Selected Parameter | Reset Default                |

|---------------------------|------------------------------|

| Transfer counter          | disabled                     |

| PEND option               | disabled                     |

| ATTN interrupt            | enabled                      |

| HEND/CTL4                 | HEND selected (CTL4 ignored) |

| ATTN/STS5                 | ATTN selected (STS5 ignored) |

| PDIR/CTL5                 | PDIR selected (CTL5 ignored) |

| PEND/STS4                 | STS4 selected (PEND ignored) |

#### Table 2-2. Default Configuration

The defaults are:

- Transfer counter is disabled.

- ATTN (attention) interrupt is enabled.

- PEND (peripheral end) is disabled.

- Output control lines selected:

- HEND (host end) is selected over CTL4.

- ATTN (attention) is selected over STS5.

- PDIR (transfer direction) is selected over CTL5.

- STS4 is selected over PEND (peripheral end).

To choose any of the options, your application program must explicitly override these default settings. The Asynchronous FIFO Interface Programmer's Guide (part number 27114-90003) explains this process.

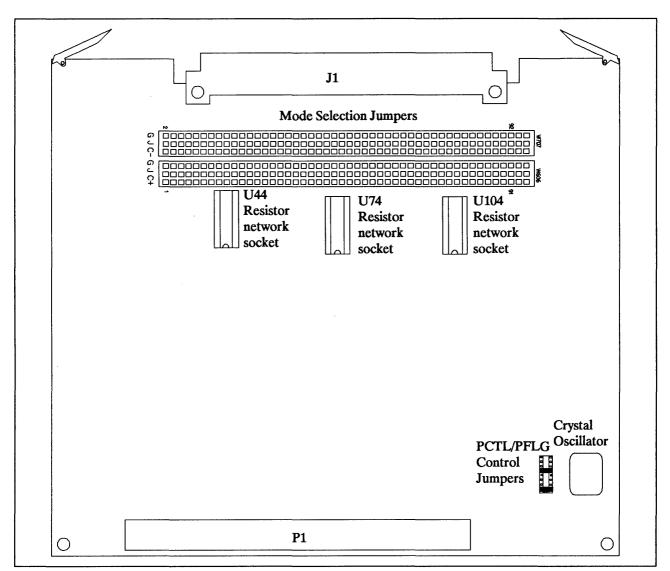

Figure 2-1. Locations of Configuration Jumpers

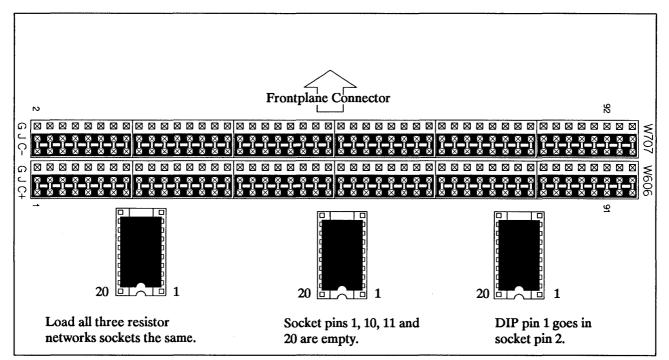

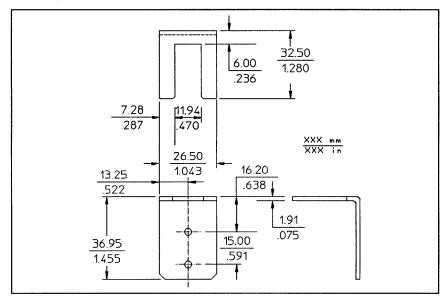

Figure 2-1 shows the PCA with the component side facing you and the frontplane connector, J1, uppermost. The most noticeable component is the mode jumper block, near the connector. On the PCA, it has 12 jumpers (not shown here) installed. Below the jumper block are the three resistor network sockets with DIP networks (not included in this illustration) installed. In the lower right corner, near the crystal oscillator, is the jumper block for the PFLG and PCTL timing controls.

#### Note

Configuring the PCA may require moving the mode jumpers. This task is difficult because they fit tightly on the jumper pins. When removing the jumpers, use a very small, flat-bladed screwdriver or similar tool. This modification is usually required only once.

# Choosing the Mode for the External Device

The AFI allows for either differential ("balanced") or single-ended ("unbalanced") external devices. Differential devices have distinct advantages in terms of usefulness. The choice of a single-ended peripheral device imposes some limitations on your application. The principal ones are:

- Restricted cable length.

- Increased noise susceptibility.

The other design concern is logic sense, either low- or high-true. The AFI supports both, but there are advantages to using a low-true device.

#### Note

If you do not understand CIO logic inversion, read "Logic Sense" later in this chapter. Terminology used here refers to the AFI hardware logic, not to what a user sees from the host computer.

Of the three configuration sections (two single-ended, one differential) that follow, you need to read only the one that applies to your application.

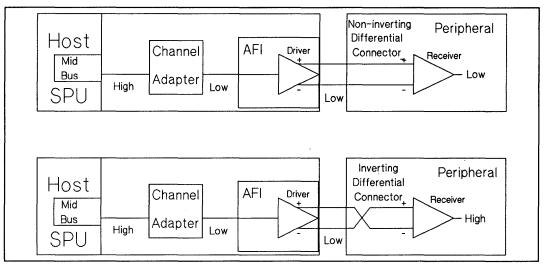

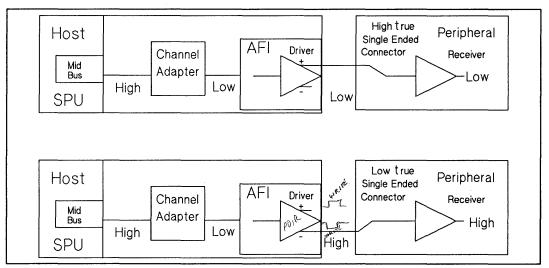

# Single-Ended<br/>ConfigurationsBecause of the limitations of single-ended data transfers, Hewlett-Packard<br/>suggests you design a differential peripheral device if you have the choice.<br/>However, the AFI device adapter supports single-ended applications in<br/>either high-true or low-true mode. Here, we explain how to configure the<br/>AFI for single-ended mode, both for high-true and low-true logic. You<br/>need to read only the section that applies to your configuration needs.To use a single-ended peripheral,• Move the mode selection jumpers from the factory setting (differen-<br/>tial mode) to the correct locations for your application.• Remove the differential termination resistor networks and install the<br/>termination resistor networks for single-ended applications.Figure 2-2 shows the jumper block with the jumpers in the single-ended,<br/>high-true positions. Figure 2-5 shows a low-true application.

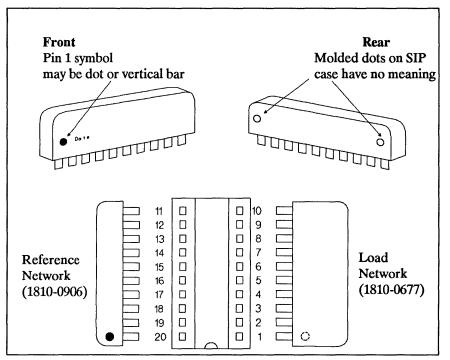

#### Note

The networks have a printed pin 1 designator, a dot or vertical bar. Molded dots on the case have no meaning. Do not confuse these marks.

Figure 2-2. Single-Ended, High-True Configuration

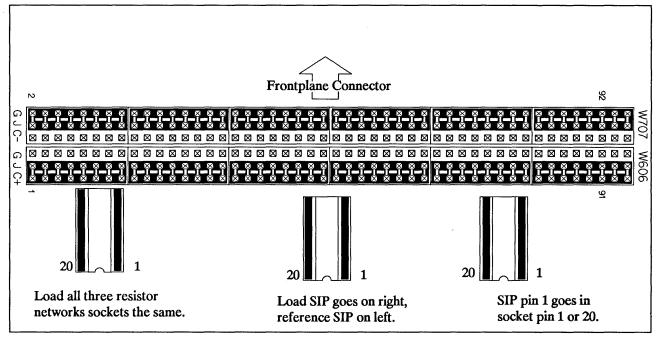

Figure 2-3. Installing the High-True Resistor Network SIPs

## Single-Ended, High-True Logic Applications

In a high-true logic application, move six of the mode jumpers and replace the DIP termination resistor networks with SIP termination resistor networks.

Caution

ESD can destroy any electronic assembly. Failure to follow anti-ESD procedures can invalidate your warranty.

#### **Mode Jumper Installation**

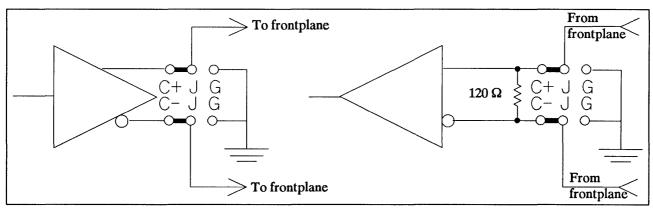

There are two blocks of jumper pins. The upper block (W707) is labeled **G J C-** on the left end; the lower (W606) labels are **G J C +**. To use a single-ended, high-true application, remove all six of the jumpers from the upper jumper blocks (nearer the frontplane connector). Then place them as shown in figure 2-2. The jumpers on the upper blocks will now connect the pins in row J to row G. Those on the lower blocks will remain connecting the jumper pins from row J to the pins in row C+.

By moving the jumpers on the upper blocks, the signals coming from the frontplane connector to the pins in row J are grounded to row G. This permits single-ended high-true use.

The pins in row C + are the leads from the (+) side of the AFI drivers or receivers. Pins in row J go to the frontplane cable connector. By shorting these pins, the output signals from the (+) side of the drivers go to the connector, and the input signals from the peripheral will go to the (+) side of the receivers. This is the factory setting for the lower jumpers.

Figure 2-4. Driver/Receiver Grounding in Single-Ended, High-True Mode

#### High-True Resistor Networks

The AFI drivers and receivers must have resistor networks installed in the three 20-pin sockets shown in figure 2-2. Figure 2-3 shows the orientation for the single, in-line packages (SIP) for high-true applications. Position the taller "load" SIP (part number 1810-0677) with its pin 1 in pin 1 of each socket. Place pin 1 of the "reference" SIP (part number 1810-0906) into socket pin 20. Identify pin 1 on the SIP by the printed symbol, either a dot or a bar. The molded dots on the plastic case have no meaning.

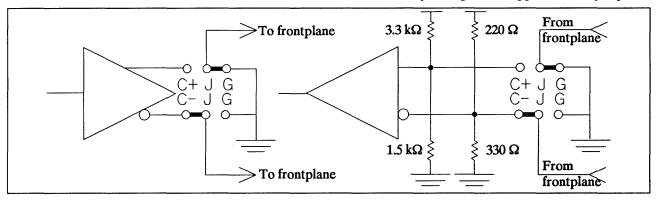

Figure 2-5. Single-Ended, Low-True Configuration

Figure 2-6. Installing the Low-True Resistor Network SIPs

## Single-Ended, Low-True Logic Applications

Low-true logic provides a method of correcting the logic inversion built into the channel adapter. Refer to the logic sense section for more detailed information. For this reason, it is the preferred logic sense for use with the AFI device adapter if you use a single-ended mode.

Caution

ESD can destroy any electronic assembly. Failure to follow anti-ESD procedures can invalidate your warranty.

#### **Mode Jumper Installation**

There are two blocks of jumper pins. The upper block (W707) is labeled **G J C-** on the left end; the lower (W606) labels are **G J C +**. To use a single-ended, low-true application, remove all six of the jumpers from the lower jumper blocks. Then place them as shown in figure 2-5. The jumpers on the lower blocks will now connect the pins in row J to row G. Those on the upper blocks will remain connecting the pins from row J to the pins in row C-.

By moving the jumpers on the lower blocks, the signals coming from the frontplane connector to the pins in row J are grounded to row G. This permits single-ended low-true use.

The pins in row C- are the leads from the (-) side of the AFI drivers or receivers. Pins in row J go to the frontplane cable connector. By shorting these pins, the output signals from the (-) side of the drivers go to the connector, and the input signals from the peripheral will go to the (-) side of the receivers. This is the factory setting for the upper block of jumpers.

Figure 2-7. Driver/Receiver Grounding in Single-Ended, Low-True Mode

Low- True Resistor Networks The AFI drivers and receivers must have resistor networks installed in the three 20-pin sockets shown in figure 2-5. Figure 2-6 shows the orientation for the single, in-line package (SIP) networks for low-true applications. Position pin 1 of the "reference" SIP (part number 1810-0906) into pin 1 of each socket. Place the taller, "load" SIP (part number 1810-0677) with pin 1 in socket pin 20. Identify pin 1 on the SIP by the printed symbol, a dot or vertical bar. The molded dots on the plastic case have no meaning.

Figure 2-8. Differential Mode Configuration

Figure 2-9. Installing the Differential Resistor Network DIPs

Figure 2-10. Driver/Receiver Connection in Differential Mode

# Differential Configurations

Differential mode provides the greatest noise immunity and the longest distances between the host and the external device. For this reason, it is the mode of choice for any application. Differential applications may use either high- or low-true logic. The connector on the external device determines the logic sense used in hardware. If you do not understand this concept, decide on a logic sense after reading "Logic Sense" later in this chapter. Terminology used here refers to the logic sense on AFI device adapter hardware, and not to what a user sees from the host computer.

#### Caution

ESD can destroy any electronic assembly. Failure to follow anti-ESD procedures can invalidate your warranty.

#### Note

If you have not previously configured the AFI in a single-ended mode, you will not have to change the factory configuration settings for mode selection or line termination. The AFI comes configured in differential mode.

If you are changing your AFI application from single-ended to differential mode to gain the noise immunity and increased cable length available, return the PCA to its factory configuration. This includes the mode selection jumpers, the termination resistor networks, and, possibly, the handshake timing control jumpers (discussed later in this chapter).

Mode Jumper<br/>InstallationTo install the jumpers for differential configuration, locate the six<br/>connected to one of the two rows labeled G. Replace them as shown in<br/>figure 2-8, so the upper block row J connects to row C + and the lower to<br/>row C-.

With the jumpers in this position, the pins in the lower block connect the frontplane (row J) to the (+) side of the drivers and receivers (row C+). The jumpers in the upper block connect the (-) side of the drivers and receivers to the frontplane (row J). With both the (+) and (-) sides connected to the frontplane, the AFI operates in the differential mode.

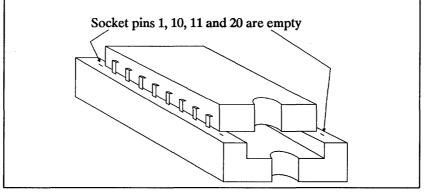

To set up a differential configuration to the line termination resistor networks, remove the six SIP resistor networks installed when the AFI was in its single-ended mode. Install the original DIP termination resistor networks (part number 1810-0964), with pin 1 of the network in pin 2 of the socket. All three sockets will have identical networks installed, leaving the four corner pins empty in each socket. See figure 2-9.

## Line Termination Resistor Networks

# Handshake Timing Control Jumpers

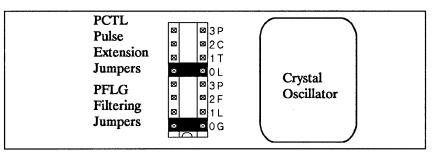

The AFI device adapter allows control over the timing of the data transfers by using two jumpers to define the PCTL pulse length and the time the AFI must see PFLG before responding. Use these features in a noisy electrical environment.

#### Caution

The AFI will not work without the PCTL jumper installed. If it is missing, or if you install two jumpers in one field (PCTL or PFLG), you risk possible loss of your data. With no jumper, PFLG defaults to PFLG0: 0-50 ns.

Figure 2-11. Output Control Jumpers

Figure 2-11 shows the two jumpers in their factory configuration. To change these settings, pull them straight up and replace them in the correct locations.

# PCTL Pulse Delay/Extension

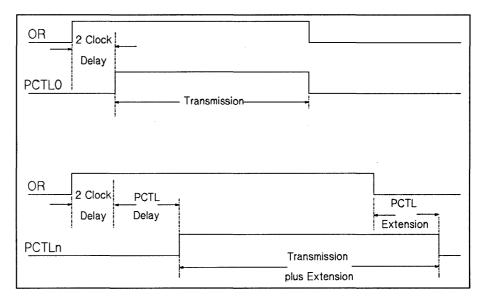

Jumper positions PCTL0 through PCTL3 select the duration of the PCTL pulse delay and extension to shift and lengthen the PCTL pulse in the AFI hardware. By choosing the appropriate position, you can tailor the AFI handshake to take account of propagation delays in long cables. Table 2-3 gives the values of the delay and extension for each jumper position.

#### Figure 2-12. Example of a Pulse Length Delay/ Extension

Figure 2-12 shows the values of the extension in relation to the internal FIFO buffer signal output ready (OR). In addition to the value of the jumper selection, the pulse length varies as a factor of the transition.

| Jumper<br>Position | PCTL Transition Delay |             |  |

|--------------------|-----------------------|-------------|--|

|                    | High-to-Low           | Low-to-High |  |

| PCTL0              | 0 ns                  | 0 ns        |  |

| PCTL1              | 50 ns                 | 50 ns       |  |

| PCTL2              | 100 ns                | 50 ns       |  |

| PCTL3              | 150 ns                | 50 ns       |  |

Table 2-3. PCTL Pulse Extension Jumpers

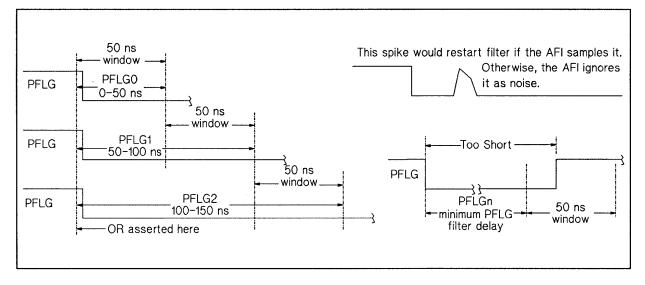

#### **PFLG Filtering**

See table 2-4 for the values of jumper positions PFLG0 through PFLG 3. They allow you to select the delay after which the AFI will accept a PFLG signal from the external device. For example, choosing position PFLG1 causes the AFI to "see" a stable PFLG signal 150 ns or longer, and reject any 100 ns or shorter. During a 50 ns "window" at the end of the delay, the AFI may miss PFLG. In this example, PFLG should be at least 150 ns.

Figure 2-13. Examples of PFLG Filter Accepting and Rejecting Signal

Any time PFLG changes and AFI samples it, the PFLG filter resets itself and PFLG must once again meet the pulse length requirement to be seen.

| Jumper Position | PFLG Sync Time |

|-----------------|----------------|

| PFLG0           | >0–50 ns       |

| PFLG1           | >50–100 ns     |

| PFLG2           | >100–150 ns    |

| PFLG3           | >150–200 ns    |

Table 2-4. PFLG Filtering

| Cables                      | There are two cables offered with the AFI:                                                                                                                                                                                                                                 |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | <ul> <li>The standard 3-meter cable (part number 27114-63001).</li> <li>The optional 12-meter cable (part number 27114-63003).</li> </ul>                                                                                                                                  |

|                             | Either will work in differential or single-ended mode. There is no<br>difference, in terms of the logic sense, between the ends of these cables.<br>That is, you may connect either end of the cable to the AFI and the<br>resulting "distant end" to the external device. |

| <b>Custom Length Cables</b> | You may have a need for a special cable length. If so, fabricate a cable of<br>any length (up to 3 meters for a single-ended mode or 12 meters for<br>differential mode). The cable should meet the following specifications:                                              |

|                             | • The conductors must be 32 AWG with a single foil/braid shield around all 96 conductors.                                                                                                                                                                                  |

|                             | • The (+) and (-) versions of each signal (or a ground return when using a single-ended application) must form a twisted pair.                                                                                                                                             |

|                             | • Impedance should not exceed 120 $\Omega$ and resistance should be approximately 190 m $\Omega$ per meter.                                                                                                                                                                |

|                             | • The end you will connect to the AFI must have a ground contact that will transfer all shield currents to the host computer card cage.                                                                                                                                    |

| Warning                     | The total cable ground path (shield) must not exceed 80 m $\Omega$ . Higher resistance creates a shock hazard.                                                                                                                                                             |

|                             | • The AFI connector is a 96-pin, male, DIN 41650, Eurocard type "C" header.                                                                                                                                                                                                |

| Note                        | Before determining your cable length, consider the possibility of reflected signals. Ensure your design will not be subject to excessive self-induced noise due to standing waves, harmonics or other causes.                                                              |

|                             | The E.I. duPont de Nemours Company, Connector Systems Division                                                                                                                                                                                                             |

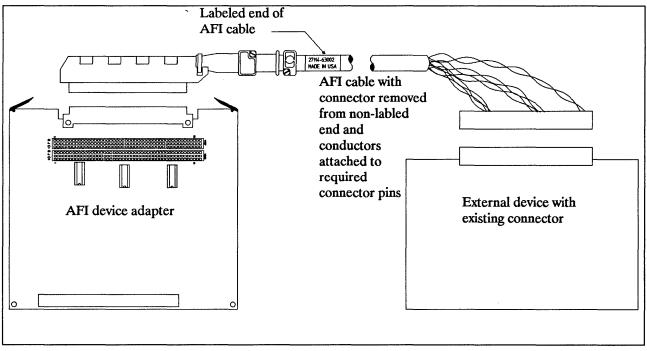

| Single-Ended Cables | By following the wiring tables in this manual, you can fabricate a custom<br>cable for your application. Be sure the total length is less than 3 meters to<br>avoid noise and other transmission problems associated with single-ended<br>applications. Use table 2-5, AFI Cabling Worksheet (later in this<br>chapter), to design the connections.                                              |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Figure 2-15 illustrates the way to make the cable. Cut off the connector<br>and the grounding grommet from the unlabeled end of the cable. Using<br>the information from table 2-5 that you will have filled in, wire the connec-<br>tor that will attach to your external device.                                                                                                               |

|                     | Tables A-3 and A-4 identify each signal from the AFI or the external device (as well as ground return lines) used by the HP cables. If you design a cable, or the connector for the external device, use these tables to do so.                                                                                                                                                                  |

|                     | Table A-5 gives the cable pin assignments for both ends of the cables. Use<br>the same twisted pairs and ground return lines as listed in table A-6 to<br>gain the greatest possible noise immunity.                                                                                                                                                                                             |

| Differential Cables | In the differential mode, both range and reliability are greatly improved<br>over either single-ended mode. The supplied 3-meter or optional 12-<br>meter cable will work in either high- or low-true mode, depending on the<br>connector on the external device.                                                                                                                                |

|                     | By following the wiring tables in this manual, you can fabricate a custom<br>cable for your application. Use table 2-5, AFI Cabling Worksheet (later in<br>this chapter), to design the connections. HP strongly recommends the<br>length be less than 12 meters. Longer cables will reduce reliability by<br>introducing detrimental signal characteristics, such as skew and attenua-<br>tion. |

|                     | Figure 2-15 shows how to make the cable. Cut off the connector and the grounding grommet from the unlabeled end of the cable so the conductor colors will match the table information. Using the information from table 2-5 that you will have filled in, wire the connector that will attach to your external device.                                                                           |

|                     | If you build the entire cable assembly, the best results occur when the design uses the same conductor pairings as in the supplied cable. This gives the pair twisting that reduces both electro-magnetic interference (EMI) radiation from the cable and susceptibility to external EMI sources.                                                                                                |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                  |

# Wiring the Custom AFI Cable

Note

Making a custom cable for connecting the AFI to the external device requires that you plan the wiring and that you build the cable. This section explains these two steps.

When cutting the existing cable, be sure to keep the end labeled "Made in U.S.A." so the conductor colors will match the tables.

#### **Planning the AFI Cable**

Table 2-5 is a worksheet you use to establish the pin assignments for the external device end of the cable. To use the table, first fill in the column labeled "External Device Signal Name" on the right side of the table for all three pages. Be sure to include the ground return lines for a single-ended application. See chapter 3 for a description of the mnemonics. These signals will be the complements of those listed in the left hand column. For instance: "RDO-" (first low received data line) on the AFI (in the left column) requires a connection either to a send (or transmitted) data line or to ground. Which one is correct depends on the logic sense and mode of your external device. Then write in the connector pin numbers corresponding to the signals you just filled in.

Figure 2-14 shows a portion of the table with the data filled in for signals in a single-ended, low-true application.

|                    | Fill in this column first.<br>Fill in this column second. |                    |                        |                                |

|--------------------|-----------------------------------------------------------|--------------------|------------------------|--------------------------------|

| AFI<br>Signal Name | Frontplane<br>Pin                                         | Conductor<br>Color | External<br>Device Pin | External Device<br>Signal Name |

| RD0-               | A01                                                       | TAN/brn            | C04                    | TD0                            |

| RD1-               | A03                                                       | TAN/orn            | <u>C03</u>             | TD1                            |

| RD2-               | A05                                                       | TAN/blu            | C06                    | TD2                            |

| RD3-               | A07                                                       | YEL/brn            | C05                    | TD3                            |

Figure 2-14. Filling in the AFI Cabling Worksheet

#### **Constructing the Cable**

If you are constructing the cable in the previous example, solder the tan conductor of the tan/brown pair to pin C04 of the external device connector. This will pass the first transmitted data signal (TD0) from the external device to the first low received data (RD0-) line on the AFI. Then continue by soldering the tan conductor of the tan/orange pair to pin C03 on the connector, the tan of the tan/blue pair to pin C06, and so on.

## Note

This process does not take into account the layout of the connector you are working with. Use the most convenient order for actually attaching the conductors to your connector.

In table 2-5, the color in capital letters is the conductor used, the other color is its twisted-pair mate. Thus "TAN/brn" is the tan conductor of the tan/brown pair, and "YEL/brn" indicates the yellow wire of the yellow/brown pair.

Figure 2-15. Wiring the Custom AFI Cable

| AFI            | Frontplane  | Conductor          | External   | External Device |  |  |  |

|----------------|-------------|--------------------|------------|-----------------|--|--|--|

| Signal Name    | Pin         | Color              | Device Pin | Signal Name     |  |  |  |

| RD0-           | A01         | TAN/brn            |            |                 |  |  |  |

| RD1-           | A01<br>A03  | TAN/orn            |            |                 |  |  |  |

| RD2-           | A05         | TAN/blu            |            |                 |  |  |  |

| RD3-           | A07         | YEL/brn            |            |                 |  |  |  |

|                |             |                    |            |                 |  |  |  |

| RD4-           | A09         | YEL/orn            |            |                 |  |  |  |

| RD5-           | A11         | YEL/red            |            |                 |  |  |  |

| RD6-           | A13         | YEL/gra            |            |                 |  |  |  |

| RD7-           | A15         | WHT/vio            |            |                 |  |  |  |

| RD8-           | C17         | BLU/wht            |            |                 |  |  |  |

| RD9-           | C19         | BRN/gra            |            |                 |  |  |  |

| RD10-          | B19         | GRN/gra            |            |                 |  |  |  |

| RD11-          | C23         | BLK/gra            |            |                 |  |  |  |

|                |             |                    |            |                 |  |  |  |

| RD12-          | C25         | VIO/orn            |            |                 |  |  |  |

| RD13-          | C27         | BLK/orn            |            |                 |  |  |  |

| RD14-          | C29         | VIO/blu            |            |                 |  |  |  |

| RD15-          | C31         | VIO/grn            |            |                 |  |  |  |

| SD0-           | B01         | GRN/tan            |            |                 |  |  |  |

| SD1-           | B03         | WHT/tan            |            |                 |  |  |  |

| SD2-           | C06         | TAN/yel            |            |                 |  |  |  |

| SD3-           | B07         | GRN/yel            |            |                 |  |  |  |

| SD4            | C10         | VEI /l.4           |            |                 |  |  |  |

| SD4-<br>SD5-   | B11         | YEL/wht<br>BLU/yel |            |                 |  |  |  |

| SD5-<br>SD6-   | C14         | WHT/brn            |            |                 |  |  |  |

| SD0-<br>SD7-   | B15         | ORN/wht            |            |                 |  |  |  |

| -1U7-          | <b>B</b> 13 |                    |            |                 |  |  |  |

| SD8-           | C18         | WHT/blk            |            |                 |  |  |  |

| SD9-           | A21         | GRA/orn            |            |                 |  |  |  |

| SD10-          | C22         | GRA/red            |            |                 |  |  |  |

| SD11-          | C24         | ORN/brn            |            |                 |  |  |  |

| SD12-          | C26         | ORN/red            |            |                 |  |  |  |

| SD12-<br>SD13- | B27         | BRN/blu            |            |                 |  |  |  |

| SD13-<br>SD14- | C30         | BLU/red            |            |                 |  |  |  |

| SD14-<br>SD15- | B31         | RED/grn            |            |                 |  |  |  |

|                | 531         | NLD/gill           |            |                 |  |  |  |

# Table 2-5. AFI Cabling Worksheet (1 of 3) (See instructions for use)

| AFI<br>Signal Name | Frontplane<br>Pin | Conductor<br>Color | External<br>Device Pin | External Device<br>Signal Name |

|--------------------|-------------------|--------------------|------------------------|--------------------------------|

| RD0+               | C01               | BRN/tan            |                        |                                |

| RD1+               | C03               | ORN/tan            |                        |                                |

| RD2+               | C05               | BLU/tan            |                        |                                |

| RD3+               | C07               | BRN/yel            |                        |                                |

| RD4+               | C09               | ORN/yel            |                        |                                |

| RD5+               | C11               | RED/yel            |                        |                                |

| RD6+               | C13               | GRA/yel            |                        |                                |

| RD7+               | C15               | VIO/wht            |                        |                                |

| RD8+               | A17               | WHT/blu            |                        |                                |

| RD9+               | A19               | GRA/brn            |                        |                                |

| RD10+              | C20               | GRA/grn            |                        |                                |

| RD11+              | A23               | GRA/blk            |                        |                                |

| RD12+              | A25               | ORN/vio            |                        |                                |

| RD13+              | A27               | ORN/blk            |                        |                                |

| RD14+              | A29               | BLU/vio            |                        |                                |

| RD15+              | A31               | GRN/vio            |                        |                                |

| SD0+               | C02               | TAN/grn            |                        |                                |

| SD1+               | C04               | TAN/wht            |                        |                                |

| SD2+               | B05               | YEL/tan            |                        |                                |

| SD3+               | C08               | YEL/grn            |                        |                                |

| SD4+               | B09               | WHT/yel            |                        |                                |

| SD5+               | C12               | YEL/blu            |                        |                                |

| SD6+               | B13               | BRN/wht            |                        |                                |

| SD7+               | C16               | WHT/orn            |                        |                                |

| SD8+               | B17               | BLK/wht            |                        |                                |

| SD9+               | C21               | ORN/gra            |                        |                                |

| SD10+              | B21               | RED/gra            |                        |                                |

| SD11+              | B23               | BRN/orn            |                        |                                |

| SD12+              | B25               | RED/orn            |                        |                                |

| SD13+              | C28               | BLU/brn            |                        |                                |

| SD14+              | B29               | RED/blu            |                        |                                |

| SD15+              | C32               | GRN/red            |                        |                                |

# Table 2-5. AFI Cabling Worksheet (2 of 3) (See instructions for use)

| AFI<br>Signal Name | Frontplane<br>Pin | Conductor<br>Color  | External<br>Device Pin | External Device<br>Signal Name |

|--------------------|-------------------|---------------------|------------------------|--------------------------------|

| PFLG-              | A14               | WHT/grn             |                        |                                |

| STS0-              | B16               | RED/wht             |                        |                                |

| STS1-              | A18               | WHT/gra             |                        |                                |

| STS2-              | B12               | BLK/yel             |                        |                                |

| STS3-              | A02               | TAN/vio             |                        |                                |

| STS4-/PEND-        | B06               | BLK/tan             |                        |                                |

| ATTN-/STS5-        | B30               | BRN/grn             |                        |                                |

| Shield             | A10               | Shield              |                        |                                |

| PFLG +             | B14               | GRN/wht             |                        |                                |

| STS0+              | A16               | WHT/red             |                        |                                |

| STS1+              | B18               | GRA/wht             |                        |                                |

| STS2+              | A12               | YEL/blk             |                        |                                |

|                    |                   |                     |                        |                                |

| STS3+              | B02               | VIO/tan             |                        |                                |

| STS4+/PEND+        | A06               | TAN/blk             |                        |                                |

| ATTN +/STS5 +      | A30               | GRN/brn             |                        |                                |

| No Connection      | B10               |                     |                        |                                |

|                    |                   |                     |                        |                                |

| PCTL-              | A22               | GRA/blu             |                        |                                |

| CTL0-              | B24               | GRN/orn             |                        |                                |

| CTL1-              | B26               | BLU/orn             |                        |                                |

| CTL2-              | A28               | BLU/grn             |                        |                                |

| CTL3-              | B04               | RED/tan             |                        |                                |

| HEND-/CTL4-        | A08               | YEL/vio             |                        |                                |

| PDIR-/CTL5-        | A08<br>A32        | PNK/gra             |                        |                                |

| 1DIK-/C1L3-        | A32               | I INN/gra           |                        |                                |

| PCTL+              | B22               | BLU/gra             |                        |                                |

| CTL0+              | A24               | ORN/grn             |                        |                                |

| CTL1+              | A24<br>A26        | ORN/grii<br>ORN/blu |                        |                                |

| CTL2+              | B28               | GRN/blu             |                        |                                |

|                    | 1520<br>          |                     |                        |                                |

| CTL3+              | A04               | TAN/red             | ]                      |                                |

| HEND+/CTL4+        | B08               | VIO/yel             |                        |                                |

| PDIR +/CTL5+       | B32               | GRA/pnk             |                        |                                |

| Ground             | B32<br>B20        | VIO/gra             |                        |                                |

| Ground             | A20               | GRA/vio             |                        |                                |

| ~                  |                   |                     |                        |                                |

# Table 2-5. AFI Cabling Worksheet (3 of 3) (See instructions for use)

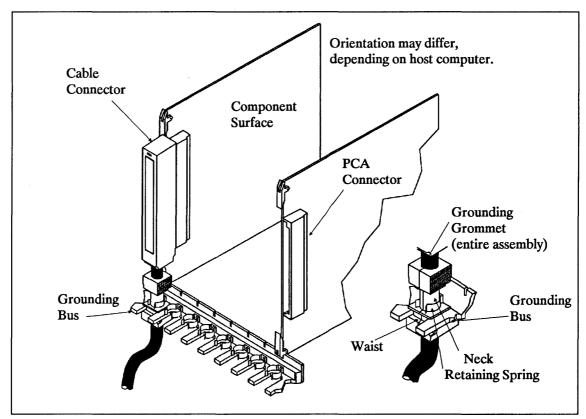

| Installing the AFI | Installing the device adapter into the host computer backplane is straight-<br>forward:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <ul> <li>Select the appropriate host slot.</li> <li>Orient the PCA correctly.</li> <li>Insert it into the backplane.</li> <li>Attach the cable.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Warning            | Never install a PCA with the power on. If you do, you risk serious electrical shock. The system manuals explain how to shut down the operating system and switch off the host computer.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Selecting a Slot   | The default slot for the AFI is slot 5. To install the PCA in another slot, you must identify the slot to the operating system. This requires regenerating the kernel, a task more complex than this manual can address. To do so, see the <i>HP-UX System Administrator's Manual</i> for your computer. If you choose to install the AFI in a non-default slot, it must be in one of the first eight slots (0 through 7) of the CIO bus (CIB). If none of these is open, you will have to make one available by moving another device adapter. Check in the system manuals to determine which device adapters can go into the slots you have empty. |

| Note               | CIB slots are numbered in orange. Some computers offer the option of<br>converting CIB slots into Mid Bus slots. In these computers, the slots may<br>have dual numbering in other colors. Before installing the AFI device<br>adapter, check the I/O configuration table in the system manuals.                                                                                                                                                                                                                                                                                                                                                     |