# HD-6101 **CMOS PARALLEL INTERFACE ELEMENT** (PIE)

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Pinout                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

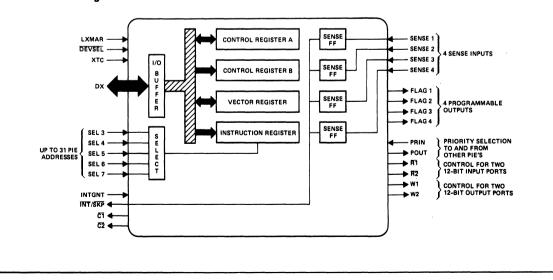

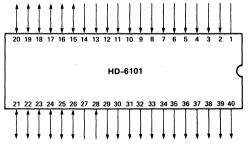

| <ul> <li>HM-6100 COMPATIBLE</li> <li>LOW POWER STANDBY -500µW MAX</li> <li>SINGLE SUPPLY 4-11 VOLTS</li> <li>FULL TEMPERATURE RANGE -55°C TO +125°C</li> <li>STATIC OPERATION</li> <li>4 PROGRAMMABLE OUTPUTS (FLAGS)</li> <li>4 PROGRAMMABLE SENSE INPUTS</li> <li>CONTROL FOR TWO 12 BIT INPUT PORTS</li> <li>CONTROL FOR TWO 12 BIT OUTPUT PORTS</li> <li>PRIORITY VECTORED INTERRUPTS</li> <li>UP TO 31 PIE'S PER SYSTEM</li> <li>16 INSTRUCTIONS FOR PIE CONTROL</li> </ul> <b>Description</b> The HD-6101 Parallel Interface Elements (PIE) are high speed, low power, silicon gate CMOS general purpose devices which provide addressing interrupt and control for a variety of peripheral functions, such as UARTS, FIFOS, Keyboards, etc. Data transfers between the HM-6100 CMOS Microprocessor and the HD-6101 are via Input-Output Transfer (IOT) instructions, control lines and DX bus. Data transfers between peripheral devices and the DX bus are controlled by the PIE via 2 read, 2 write, 4 sense and 4 flag functions. Internal PIE registers are programmed under software control for write polarities, sense levels or edges, flag values and interrupt enables. Another software controlled register stores the address for vectored interrupt operation. | V <sub>CC</sub> 1 • 40 POUT<br>INTGNT 2 39 SKP/INT<br>PRIN 3 38 WRITE 2<br>SENSE 4 4 37 READ 2<br>SENSE 3 05 36 WRITE 1<br>SENSE 2 6 35 READ 1<br>SENSE 1 7 34 CZ<br>SEL 3 08 33 C1<br>SEL 4 9 32 FLAG 1<br>LXMAR 10 31 FLAG 2<br>SEL 5 11 30 FLAG 3<br>SEL 6 12 29 FLAG 4<br>XTC 13 28 DEVSEL<br>SEL 7 14 27 GND<br>DX0 15 26 DX11<br>DX1 16 25 DX10<br>DX2 17 24 DX9<br>DX3 C 18 23 DX8<br>DX4 19 22 DX7<br>DX5 0 20 21 DX6 |

| Functional Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LXMAR<br>DEVSEL<br>XTC<br>I/O<br>B<br>CONTROL REGISTER A<br>CONTROL REGISTER B<br>SENSE<br>FF<br>SENSE<br>FF<br>SENSE<br>FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SENSE 1<br>SENSE 2<br>SENSE 3<br>SENSE 4<br>SENSE 4                                                                                                                                                                                                                                                                                                                                                                           |

## ABSOLUTE MAXIMUM RATINGS

| Supply Voltage (VCC - GND)      | -0.3V to +8.0V               |

|---------------------------------|------------------------------|

| Input or Output Voltage Applied | (GND - 0.3V) to (VCC + 0.3V) |

| Storage Temperature Range       | -65°C to +150°C              |

| Operating Temperature Range     |                              |

| Industrial HD-6101-9            | -40°C to +85°C               |

| Military HD-6101-2              | -55°C to +125°C              |

### ELECTRICAL CHARACTERISTICS

A.C.

$V_{CC} = 5.0V \pm 10\%$ ; TA = Industrial or Military

|      | SYMBOL            | PARAMETER                                                               | MINIMUM         | TYPICAL | MAXIMUM         | UNITS        | TEST CONDITIONS      |

|------|-------------------|-------------------------------------------------------------------------|-----------------|---------|-----------------|--------------|----------------------|

|      | VIH<br>VIL<br>IIL | Logical "1" Input Voltage<br>Logical "0" Input Voltage<br>Input Leakage | 70% Vcc<br>-1.0 |         | 20% VCC<br>+1.0 | V<br>V<br>µА | 0V ≤ VIN ≤ VCC       |

| D.C. |                   | Logical "1" Output Voltage(1)                                           | 2.4             |         | 110             | V            | IOH = -0.2mA         |

|      | VOL               | Logical "0" Output Voltage                                              |                 |         | 0.45            | v            | IOL = 2.0mA          |

|      | 10                | Output Leakage                                                          | -1.0            |         | +1.0            | μΑ           | 0v ≼ vo ≼ vcc        |

|      | Icc               | Supply Current (Static)                                                 |                 | 1.0     | 100             | μΑ           | VIN = VCC, Freq. = 0 |

|      | CI                | Input Capacitance(2)                                                    |                 | 5       | 7               | pF           |                      |

|      | СО                | Output Capacitance (2)                                                  | i               | 8       | 10              | pF           |                      |

|      | CIO               | Input/Output Capacitance(2)                                             |                 | 8       | 10              | pF           |                      |

NOTE: (1) Except pins 33, 34, 39

(2) Guaranteed and sampled, but not 100% tested.

|        |                          | 25°C<br>5.0V(1) | TA =<br>INDUSTRIAL<br>VCC = 5V ±10% |     | TA =<br>MILITARY<br>VCC = 5V ±10% |     |     |       |                 |

|--------|--------------------------|-----------------|-------------------------------------|-----|-----------------------------------|-----|-----|-------|-----------------|

| SYMBOL | PARAMETER                | MIN             | МАХ                                 | MIN | МАХ                               | MIN | MAX | UNITS | TEST CONDITIONS |

| tDR    | Delay: DEVSEL to READ    |                 | 200                                 |     | 300                               |     | 330 | ns    | CL = 50pF       |

| tDW    | Delay: DEVSEL to WRITE   | 100             | 220                                 | 140 | 300                               | 150 | 330 | ns    | See Timing      |

| tDF    | Delay: DEVSEL to FLAG    |                 | 200                                 |     | 375                               |     | 415 | ns    | Diagram         |

| tDC    | Delay: DEVSEL to C1, C2  |                 | 160                                 |     | 460                               |     | 510 | ns    |                 |

| tDI    | Delay: DEVSEL to SKP/INT |                 | 210                                 |     | 460                               |     | 510 | ns    |                 |

| tDA    | Delay: DEVSEL to DX      |                 | 350                                 |     | 460                               |     | 510 | ns    |                 |

| tLX    | LXMAR Pulse Width        | 200             |                                     | 240 |                                   | 265 |     | ns    |                 |

| tAS    | Address Set-Up Time      | 60              |                                     | 80  |                                   | 90  |     | ns    |                 |

| tAH    | Address Hold Time        | 100             |                                     | 125 |                                   | 140 |     | ns    |                 |

| tDS    | Data Set-Up Time         | 50              |                                     | 80  |                                   | 80  |     | ns    |                 |

| tDH    | Data Hold Time           | 100             |                                     | 100 |                                   | 110 |     | ns    | 1               |

NOTE (1): All devices guaranteed at worst case limits. Room temperature, 5V data provided for information - not guaranteed.

## ABSOLUTE MAXIMUM RATINGS

Supply Voltage (VCC - GND) Input or Output Voltage Applied Storage Temperature Range Operating Temperature Range Industrial HD-6101C-9 -0.3V to +8.0V (GND - 0.3V) to (VCC +0.3V) -65°C to +150°C

-40°C to +85°C

#### ELECTRICAL CHARACTERISTICS

$V_{CC} = 5.0V \pm 5\%$ ; TA = Industrial

| SYMBOL | PARAMETER                     | PARAMETER MINIMUM TYPICAL |     | MAXIMUM | UNITS | TEST CONDITIONS      |

|--------|-------------------------------|---------------------------|-----|---------|-------|----------------------|

| VIH    | Logical ''1'' Input Voltage   | 70% VCC                   |     |         | v     |                      |

| VIL    | Logical "0" Input Voltage     |                           |     | .8      | v     |                      |

| ΠL     | Input Leakage                 | -10                       |     | +10     | μΑ    | 0V ≤ VIN ≤ VCC       |

| ∨он    | Logical "1" Output Voltage(1) | 2.4                       |     |         | v     | 10H = -0.2mA         |

| VOL    | Logical "0" Output Voltage    |                           |     | 0.45    | v     | IOL = 1.6mA          |

| ю      | Output Leakage                | -10                       |     | +10     | μΑ    | ov ≼ vo ≼ vcc        |

| ICC    | Supply Current (Static)       |                           | 1.0 | 800     | μΑ    | VIN = VCC, Freq. = 0 |

| CI     | Input Capacitance (2)         |                           | 5   | 7       | pF    |                      |

| CO     | Output Capacitance (2)        |                           | 8   | 10      | рF    |                      |

| CIO    | Input/Output Capacitance(2)   |                           | 8   | 10      | рF    |                      |

NOTES: (1) Except pins 33, 34, 39

(2) Guaranteed and sampled, but not 100% tested.

|            |                                                     |           |            | INDUS      | 4 =<br>STRIAL<br>5V ±5% |          |                         |

|------------|-----------------------------------------------------|-----------|------------|------------|-------------------------|----------|-------------------------|

| SYMBOL     | PARAMETER                                           | MIN       | МАХ        | MIN        | МАХ                     | UNITS    | TEST CONDITIONS         |

| tDR        | Delay: DEVSEL to READ<br>Delay: DEVSEL to WRITE     | 100       | 230<br>240 | 125        | 375<br>375              | ns       | CL = 50pF<br>See Timing |

| tDW<br>tDF | Delay: DEVSEL to FLAG                               | 100       | 240<br>230 | 125        | 375<br>475              | ns<br>ns | Diagram                 |

| tDC<br>tDI | Delay: DEVSEL to C1, C2<br>Delay: DEVSEL to SKP/INT |           | 190<br>250 |            | 560<br>560              | ns<br>ns |                         |

| tDA        | Delay: DEVSEL to DX                                 |           | 400        |            | 560                     | ns       |                         |

| tLX<br>tAS | LXMAR Pulse Width<br>Address Set-Up Time            | 230<br>80 |            | 300<br>100 |                         | ns<br>ns |                         |

| tAH        | Address Hold Time                                   | 120       |            | 150        |                         | ns       |                         |

| tDS<br>tDH | Data Set-Up Time<br>Data Hold Time                  | 60<br>120 |            | 90<br>150  |                         | ns<br>ns |                         |

NOTE (1): All devices guaranteed at worst case limits. Room temperature, 5V data provided for information - not guaranteed.

D.C.

A.C.

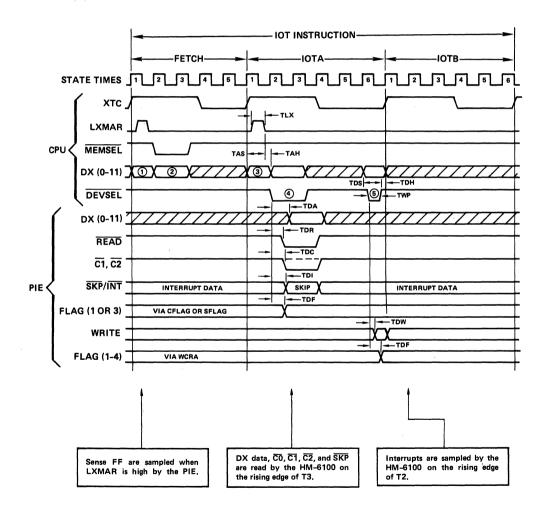

Timing for a typical transfer is shown below. During an instruction fetch the processor places the contents of the PC on the bus (1) and obtains from memory an IOT instruction of the form 6XXX (2). During IOTA of the execute phase the processor places that instruction back on the DX lines (3) and pulses LXMAR transferring address and control information for the IOT transfer to all peripheral devices. A low going pulse on DEVSEL while XTC is high (4) is used by the addressed PIE along with the decoded control information to generate CPU control signals C1, C2, and SKP. Also at this time either the Control Register A or the Interrupt Vector Register are outputed

on the DX lines, or control outputs READ1 and READ2 are generated to gate peripheral data to the DX lines. A low going pulse on DEVSEL while XTC is low (5) is used to generate WRITE 1 and WRITE 2 controls. These signals are used to latch accumulator data into peripheral devices.

All PIE timing is generated from HM-6100 signals LXMAR, DEVSEL, and XTC. No additional timing signals, clocks, or one shots are required.

Propagation delays, pulse width, data setup and hold times are specified for direct interfacing with the HM-6100.

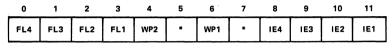

The HM-6100 communicates with the PIE and with peripherals through the PIE via IOT commands. During the IOTA cycle an instruction of the form 6XXX is loaded into all PIE instruction registers. The bits are interpreted as shown below. The 5 address bits (3-7) are compared with the pin programmable select inputs SEL3, SEL4, SEL5, SEL6, SEL7 to address 1 of 31 possible PIEs. Address zero is reserved for IOT's internal to the HM-6100. The four control bits are decoded by the PIE to select one of 16 instructions which are described below.

#### PIE INSTRUCTION FORMAT

| _ | 0 | 1 | 2 | 3 | 4 | 5    | 6  | 7 | 8 | 9   | 10   | 11 |

|---|---|---|---|---|---|------|----|---|---|-----|------|----|

|   | 1 | 1 | 0 |   | A | DDRE | SS |   |   | CON | ITRO | L  |

| CONTROL             | MNEMONICS        | ACTION                                                                                                                                                                                                                                                                                                      |

|---------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000<br>1000        | READ1<br>READ2   | The READ instructions generate a pulse on the appropriate read outputs. This signal is used by the peripheral device to gate onto the DX bus to be "OR'ed" with the HM-6100 accumulator data. The HM-6100 accumulator is cleared prior to reading peripheral data when $\overline{\rm CO}$ is asserted low. |

| 0001<br>1001        | WRITE1<br>WRITE2 | The WRITE instructions generate a pulse on the appropriate write output. This signal is used by peripherals to load the HM-6100 accumulator data on the DX lines into peripheral data registers. The HM-6100 AC is cleared after the write operation when the $\overline{\rm CO}$ input is asserted low.    |

| 0010                | SKIP1            | The SKIP instructions test the state of the sense flip flops. If the input conditions have set the                                                                                                                                                                                                          |

| 0011                | SKIP2            | sense flip flop, the PIE will assert the SKP/INT output causing the HM-6100 to skip the next                                                                                                                                                                                                                |

| 1010                | SKIP3            | program instruction. The sense flip flop is then cleared. If the sense flip flop is not set, the PIE                                                                                                                                                                                                        |

| 1011                | SKIP4            | not assert the $SKP/INT$ output and the HM-6100 will execute the next instruction.                                                                                                                                                                                                                          |

| 0100                | RCRA             | The Read Control Register A instruction gates the contents of CRA onto the DX lines during time 4 to be "OR" transferred to the HM-6100 AC.                                                                                                                                                                 |

| 0101                | WCRA             | The Write Control Register A, Write Control Register B and Write Vector Register instructions                                                                                                                                                                                                               |

| 1101                | WCRB             | transfer HM-6100 AC data on the DX lines during time 5 of IOTA into the appropriate register.                                                                                                                                                                                                               |

| 1100                | ₩VR              |                                                                                                                                                                                                                                                                                                             |

| 0110                | SFLAG1           | The SET FLAG instructions set the bits FL1 and FL3 in control register A to a high level. PIE                                                                                                                                                                                                               |

| 1110                | SFLAG3           | outputs FLAG1 and FLAG3 follow the data stored in bits FL1 and FL3 of CRA.                                                                                                                                                                                                                                  |

| 0111                | CFLAG1           | The CLEAR FLAG instructions clear the bits FL1 and FL3 in control register A to a low level.                                                                                                                                                                                                                |

| 1111                | CFLAG3           |                                                                                                                                                                                                                                                                                                             |

| (6007) <sub>8</sub> | CAF              | HM-6100 internal IOT instruction CLEAR ALL FLAGS clears the interrupt requests by clearing<br>the sense flip flops.                                                                                                                                                                                         |

## Programmable Outputs

**FLAGs (1-4)** - The FLAGs are general purpose outputs that can be set and cleared under program control. GLAG1 follows bit FL1 in Control Register A and etc. FLAGs can be changed by loading new data into CRA via the WCRA commands. In addition, FLAG1 and FLAG3 can be set and cleared directly by the commands SFLAG1, CFLAG1, SFLAG3 and CFLAG3.

## Programmable Sense Inputs

The sense inputs are used to set sense flip flops (SENSEFF) inside the PIE. For each sense input there are two FF's, one for skip and one for interrupt. Conditions for setting each SENSE FF, levels or edges and positive or negative polarities, are set by control bits SL and SP in CRB.

The SENSE FF's are sampled when LXMAR is high. Interrupt requests are generated only when the sense flip flops are set by an edge and interrupts are enabled by writing to control reg A. Sense flip flops are reset on the following conditions.

|                                 | SENSE FLIP FLOPS        |                                                                     |  |  |  |  |  |

|---------------------------------|-------------------------|---------------------------------------------------------------------|--|--|--|--|--|

| CONDITION                       | SKIP FF                 | INTERRUPT FF                                                        |  |  |  |  |  |

| CAF Instruction (60078)         | Clears All              | Clears All                                                          |  |  |  |  |  |

| SKIP Instruction                | Clears Corresponding FF | Clears Corresponding FF                                             |  |  |  |  |  |

| Vectored Interrupt              | Not Cleared             | Clears Highest Priority FF<br>on Selected PIE After<br>Vectoring    |  |  |  |  |  |

| Interrupt Disabled (IE = ''0'') | Not Cleared             | Disables Interrupt by Holding<br>Corresponding FF in Reset<br>State |  |  |  |  |  |

## **Controls for Input and Output Ports**

**READ** (1-2) — The READ outputs are activated by the read instructions and are used by peripheral devices to get data onto the DX lines for transfer to the HM-6100. Read lines are active low.

<u>WRITE (1-2)</u> — The WRITE outputs are activated by the write instructions and are used by peripheral devices to load HM-6100 AC data from the DX lines into peripheral data registers. Output polarity is controlled by the WRITE POLARITY bits of CRA. A logic one causes pulses to be positive while a logic zero causes pulses to be negative.

<u>I/O CONTROL LINES</u>. – There are three I/O control lines from the PIE to the microprocessor – C1, C2, and  $\overline{INT/SKP}$ . The type of data transfer, during an IOT in-

struction, is specified by the PIE's assertion of the  $\overline{C1}$  and  $\overline{C2}$  control lines as shown below.

Interrupt and skip information are time multiplexed on the same line ( $\overline{SKP}/\overline{INT}$ ). Since the HM-6100 samples skip and interrupt data at separate times there is no degradation in system performance. The PIE samples the sense flip flops and generates an interrupt request for enabled bits (IE1-4) when LXMAR is high. Interrupt requests are asserted by the PIE driving the  $\overline{INT}/\overline{SKP}$  line low. During IOTA of SKIP instructions the  $\overline{INT}/\overline{SKP}$  reflects the SENSE FF data when  $\overline{DEVSEL}$  is low and XTC is high. If the SENSE filp flop is set, the  $\overline{INT}/\overline{SKP}$  line is driven low to cause the HM-6100 to skip the next instruction. All these outputs are open drain.

|     | CONTROL LINES |    |    |                     |                                                                                                     |

|-----|---------------|----|----|---------------------|-----------------------------------------------------------------------------------------------------|

| SKP | <u>C0</u> *   | C1 | C2 | OPERATION           | DESCRIPTION                                                                                         |

| н   | н             | н  | н  | PIE 🛶 AC            | The contents of the AC is sent to the PIE.                                                          |

| н   | н             | L  | Н  | AC 🛥 AC V PIE       | Data is received from the PIE,<br>OR'ed with the data in the AC<br>and the result stored in the AC. |

| H   | н             | L  | L  | PC 🛥 Vector Address | Vector address received from<br>PIE and loaded into PC. This is<br>referred to as an absolute jump. |

| L   | н             | н  | н  | PC PC + 1           | Forces Microprocessor to skip next sequential instruction.                                          |

NOTE: \*The  $\overline{C0}$  line must be connected to VCC using a pull-up resistor.

#### CONTROL REGISTER A (CRA)

The CRA can be read and written by the HM-6100 via the RCRA and WCRA commands.

The format and meaning of control bits are shown below.

<u>FL (1-4)</u> – Data on FLAG outputs corresponds to data in FL (1-4). Changing the FL bits under software control changes the corresponding FLAG outputs. <u>**IE**(1-4)</u> — A high level on INTERRUPT ENABLE enables interrupts for the SENSE inputs.

Otherwise these inputs provide conditional skip testing as defined by the SKIP1-4 instructions.

<u>WP (1-2)</u> — A high level on WRITE POLARITY bits causes positive pulses at the WRITE outputs.

\* = Don't Care

#### **CONTROL REGISTER B (CRB)**

The CRB can be written by the HM-6100 via the WCRB instruction. It has no read back capability. The format and meaning of control bits are shown.

<u>SL (1-4)</u> — A high level on the SENSE LEVEL bits causes the SENSE inputs to be level sensitive. A low level in the SL bits causes the SENSE inputs to be edge sensitive. An interrupt request is generated only if a sense line is set up to be edge sensitive and interrupts are enabled via the IE bits of CRA.

<u>SP (1-4)</u> – A high level on the SENSE POLARITY bits causes the flip flop to be set by high level or positive going edge. A low level causes the flip flop to be set by a low level or negative going edge.

#### VECTOR REGISTER

A hardware priority network uniquely selects a PIE to provide a vectored address. The first IOT command of any type, after the HM-6100 signal INTERRUPT GRANT goes high, resets the INTGNT line to a low level. The INTGNT signal is used to freeze the priority network and enable vector generation. The highest priority PIE has PIN tied to V<sub>CC</sub>. The lowest priority PIE is the last one on the chain. Within the PIE, SENSE1 has the highest priority and SENSE 4 has the lowest. The vector address generated by the PIE consists of 10 bits from the vector register and two bits that indicate the sense input within the highest priority PIE that generated the interrupt. If PIN is tied to GND, then the PIE will respond as a non-vectored interrupt device.

| 0 | 1 | 2 | 3   | 4    | 5    | 6        | 7  | 8 | 9 | 10 | 11 |

|---|---|---|-----|------|------|----------|----|---|---|----|----|

|   |   |   | VEC | TORR | EGIS | STER     |    |   |   | VP | RI |

|   |   |   |     | VPRI | с    | ONDITIO  | NS |   |   |    |    |

|   |   |   |     | 00   |      | SENSE 1  |    |   |   |    |    |

|   |   |   |     | 01   |      | OF NOT O |    |   |   |    |    |

|   |   |   |     | 01   |      | SENSE 2  |    |   |   |    |    |

|   |   |   |     | 10   |      | SENSE 2  |    |   |   |    |    |

## Pin Definitions

| PIN    | SYMBOL        | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2 | VCC<br>INTGNT | н               | Positive voltage<br>A high level on INTERRUPT GRANT<br>inhibits recognition of new interrupt requests<br>and allows the priority chain time to<br>uniquely specify a PIE.                                                                                                                                                                                                                                                                                                                          |

| 3      | PRIN          | н               | A high level ON PRIORITY IN and an<br>interrupt request will select a PIE for<br>vectored interrupt.                                                                                                                                                                                                                                                                                                                                                                                               |

| 4      | SENSE 4       | PROG            | The SENSE input is controlled by the SL<br>(sense level) and SP (sense polarity) bits of<br>control register B. A high SL level will cause<br>the sense flip flop to be set by a level while a<br>low SL level causes then sense flip flop to be<br>set by an edge. A high SP level will cause the<br>sense flip flop to be set by a positive going<br>edge or high level. A high IE (interrupt<br>enable) level generates an interrupt request<br>whenever the sense flip flop is set by an edge. |

| 5      | SENSE 3       | PROG            | See pin 4 - SENSE 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6      | SENSE 2       | PROG            | See pin 4 – SENSE 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7      | SENSE 1       | PROG            | See pin 4 – SENSE 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PIN | SYMBOL | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                       |

|-----|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   | SEL 3  | TRUE            | Matching SELECT(3-7) inputs with PIE<br>addressing on DX(3-7) during IOTA selects a<br>PIE for programmed input output transfers.                                                                                                 |

| 9   | SEL 4  | TRUE            | See Pin 8 SEL 3                                                                                                                                                                                                                   |

| 10  | LXMAR  | H,              | A positive pulse on LOAD EXTERNAL<br>ADDRESS REGISTER loads address and<br>control data from DX (3-11) into the address<br>register.                                                                                              |

| 11  | SEL 5  | TRUE            | See Pin 8 - SEL 3                                                                                                                                                                                                                 |

| 12  | SEL 6  | TRUE            | See Pin 8 - SEL 3                                                                                                                                                                                                                 |

| 13  | хтс    | н               | The XTC input is a timing signal produced by<br>the microprocessor. When XTC is high a low<br>going pulse on DEVSEL initiates a "read"<br>operation. When XTC is low, a low going pulse<br>on DEVSEL initiates a write operation. |

| 14  | SEL 7  | TRUE            | See Pin 8 - SEL 3                                                                                                                                                                                                                 |

| 15  | DX 0   | TRUE            | Data transfers between the microprocessor and<br>PIE take place via these input/output pins.                                                                                                                                      |

| 16  | DX 1   | TRUE            | See Pin 15 - DX 0                                                                                                                                                                                                                 |

| 17  | DX 2   | TRUE            | See Pin 15 – DX 0                                                                                                                                                                                                                 |

| 18  | DX 3   | TRUE            | See Pin 15 DX 0                                                                                                                                                                                                                   |

| 19  | DX 4   | TRUE            | See Pin 15 – DX 0                                                                                                                                                                                                                 |

| 20  | DX 5   | TRUE            | See Pin 15 – DX 0                                                                                                                                                                                                                 |

| PIN | SYMBOL | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | DX 6   | TRUE            | See Pin 15 DX 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 22  | DX 7   | TRUE            | See Pin 15 – DX 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23  | DX 8   | TRUE            | See Pin 15 – DX 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 24  | DX 9   | TRUE            | See Pin 15 - DX 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 25  | DX 10  | TRUE            | See Pin 15 - DX 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 26  | DX 11  | TRUE            | See Pin 15 DX 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 27  | GND    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 28  | DEVSEL | L               | The DEVSEL input is a timing signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |        |                 | produced by the microprocessor during IOT<br>instructions. It is used by the PIE to generate<br>timing for controlling PIE registers<br>and "read" and "write" operations.                                                                                                                                                                                                                                                                                                                                |

| 29  | FLAG 4 | PROG            | The FLAG outputs reflect the data stored in<br>control register A. Flags (1-4) can be set or<br>reset by changing data in CRA via a WRA<br>(write control register A) command. FLAG1<br>and FLAG3 can be controlled directly by<br>PIE commands SFLAG1, CFLAG1,<br>SFLAG3 and CFLAG3.                                                                                                                                                                                                                     |

| 30  | FLAG 3 | PROG            | See Pin 29 - FLAG 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 31  | FLAG 2 | PROG            | See Pin 29 - FLAG 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 32  | FLAG 1 | PROG            | See Pin 29 - FLAG 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 33  | टा     | L               | The PIE decodes address, control and priority<br>information and asserts outputs $\overline{C1}$ and $\overline{C2}$<br>during the IOTA cycle to control the type of<br>data transfer. These outputs are open drain<br>for bussing and require a pullup register<br>to V <sub>CC</sub> .<br>$\overline{C1}(L)$ , $\overline{C2}(L)$ - vectored interrupt<br>$\overline{C1}(L)$ , $\overline{C2}(H)$ - READ1, READ2 or<br>RRA commands<br>$\overline{C1}(H)$ , $\overline{C2}(H)$ - all other instructions |

| PIN | SYMBOL    | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                                                                     |

|-----|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34  | <u>C2</u> | L               | See Pin 33 – C1                                                                                                                                                                                 |

| 35  | READ1     | PROG            | Outputs READ1 and READ2 are used to gate<br>data from peripheral devices onto the DX bus<br>for input to the <b>HM-6100</b> Note the data<br>does not pass through the PIE.                     |

| 36  | WRITE1    | PROG            | Outputs WRITE1 and WRITE2 are used to<br>gate data from the <b>HM-6100</b> DX bus into<br>peripheral devices. Data does not pass<br>through the PIE.                                            |

| 37  | READ2     | PROG            | See Pin 35 READ1                                                                                                                                                                                |

| 38  | WRITE2    | PROG            | See Pin 36 WRITE1                                                                                                                                                                               |

| 39  | SKP/INT   | L               | The PIE asserts this line low to generate<br>interrupt requests and to signal the <b>HM_6100</b><br>when sense flip flops are set during SKIP<br>instructions. This output is open drain.       |

| 40  | POUT      | н               | A high level on priority out indicates no<br>higher priority PIE interrupt requests are<br>outstanding. This output is tied to the PIN<br>input of the next lower priority<br>PIE in the chain. |