Digital Equipment Corporation Maynard, Massachusetts

digital

**PDP-15 Systems**

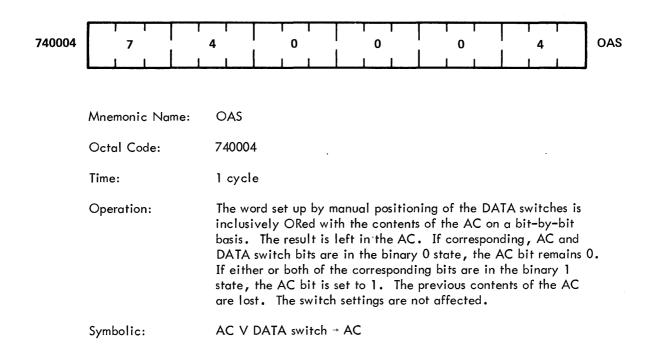

# User's Handbook Vol.1 Processor

# PDP-15 SYSTEMS USER'S HANDBOOK VOLUME 1 PROCESSOR

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

Ist Edition, September 1970 2nd Printing (Rev) November 1970 3rd Printing (Rev) April 1971 4th Printing, June 1973

Copyright © 1970, 1971, 1973 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

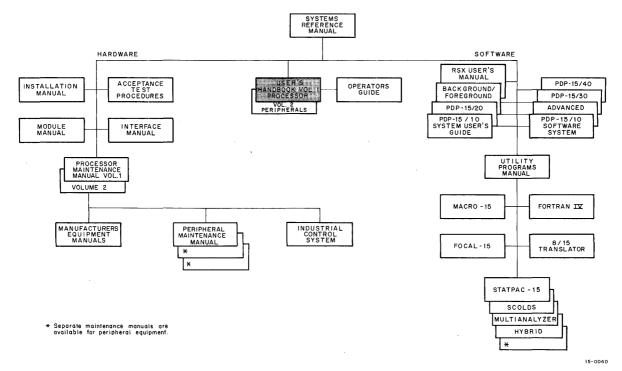

#### PDP-15 FAMILY OF MANUALS

SYSTEMS REFERENCE MANUAL – Provides overview of PDP-15 hardware and software systems and options, instruction repertoire, expansion features, and descriptions of system peripherals. (DEC-15-BRZC-D)

**USER'S HANDBOOK VOLUME 1, PROCESSOR** – Principal guide to system hardware includes system and subsystem features, functional descriptions, machine-language programming considerations, instruction repertoire, and system expansion data. (DEC-15-H2DC-D)

**VOLUME 2**, **PERIPHERALS** – Features functional descriptions and programming considerations of peripheral devices. (DEC-15-H2DC-D)

**OPERATOR'S GUIDE** – Lists procedural data, including operator maintenance, for using the operator's console and the peripheral devices associated with PDP-15 Systems. (DEC-15-H2CB-D)

**PDP-15/10 SYSTEM USER'S GUIDE** – Features COMPACT and Basic I/O Monitor operating procedures. (DEC-15-GG1A-D)

PDP-15/20 SYSTEM USER'S GUIDE – Lists Advanced Monitor System operating procedures. (DEC-15-MG2B-D)

BACKGROUND/FOREGROUND MONITOR SYSTEM USER'S GUIDE – Lists operating procedures for the DECtape and disk-oriented Background/Foreground monitors. (DEC-15-MG3A-D)

PDP-15/10 SOFTWARE SYSTEM – Describes COM-PACT software system and Basic I/O Monitor System. (DEC-15-GR1A-D)

PDP-15/20/30/40 ADVANCED MONITOR SOFTWARE SYSTEM – Describes Advanced Monitor System; programs include system monitor language, utility, and application types; operation, core organization, and input/output operations within the monitor environment are discussed. (DEC-15-MR2B-D) **PDP-15/30/40 BACKGROUND/FOREGROUND MONI-TOR SOFTWARE SYSTEM** – Describes Background/Foreground Software System including the associated language, utility, and applications program. (DEC-15-MR3A-D)

**RSX USER'S MANUAL** – Describes the disk-oriented real time system executive language and applications.

MAINTENANCE MANUAL VOLUME 1, PROCESSOR – Provides block diagram and functional theory of operation of the processor logic; lists preventive and corrective maintenance data. (DEC-15-H2BB-D)

**VOLUME 2, ENGINEERING DRAWINGS** – Provides engineering drawings and signal glossary for the basic processor and options. (DEC-15-H2BB-D)

**INSTALLATION MANUAL** – Provides power specifications, environmental considerations, cabling, and other information pertinent to installing PDP-15 Systems. (DEC-15-H2AB-D)

ACCEPTANCE TEST PROCEDURES – Lists step-by-step procedures designed to insure optimum PDP-15 Systems operation.

**PDP-15 MODULE MANUAL** – Provides characteristics, specifications, timing and functional descriptions of modules used in PDP-15 Systems. (DEC-15-H2EA-D)

**INTERFACE MANUAL** – Provides information for interfacing devices to a PDP-15 System. (DEC-15-H0AB-D)

UTILITY PROGRAMS MANUAL – Provides utility programs common to PDP-15 Monitor systems. (DEC-15-YWZA-D)

MACRO-15 – Provides MACRO assembly language for the PDP-15. (DEC-15-AMZA-D)

**FORTRAN IV** – Describes PDP-15 version of the FORTRAN IV compiler language. (DEC-15-KFZB-D)

FOCAL-15 – Describes an algebraic interactive compiler level language developed by Digital Equipment Corporation. (DEC-15-KJZB-D)

#### CONTENTS

| CHAPTER 1 | SYSTEM DESCRIPTION                                              |      |

|-----------|-----------------------------------------------------------------|------|

| 1.1       | System Software                                                 | 1-1  |

| 1.1.1     | Introduction                                                    | 1-1  |

| 1.1.2     | PDP-15/20 Advanced Monitor System                               | 1-2  |

| 1.1.3     | PDP-15/30 Background/Foreground Monitor                         | 1-3  |

| 1.1.4     | PDP-15/40 Disk-Oriented Background/Foreground System            | 1-4  |

| 1.1.5     | PDP-15/10 COMPACT Software System                               | 1-4  |

| 1.1.6     | PDP-15/10E Basic I/O Monitor                                    | 1-5  |

| 1.1.7     | PDP-15/20 Advanced Monitor System                               | 1-5  |

| 1.1.8     | PDP-15/30 Background/Foreground Monitor System                  | 1-9  |

| 1.1.9     | PDP-15/35 Real-Time System Executive                            | 1-10 |

| 1.1.10    | PDP-15/40 Disk-Oriented Background/Foreground Monitor<br>System | 1-10 |

| 1.1.11    | Additional Systems Software                                     | 1-10 |

| 1.2       | PDP-15 System Configurations                                    | 1-11 |

| 1.2.1     | PDP-15/10 Basic System                                          | 1-11 |

| 1.2.2     | PDP-15/20 Advanced Monitor System                               | 1-12 |

| 1.2.3     | PDP-15/30 Background/Foreground System                          | 1-13 |

| 1.2.4     | PDP-15/35 Real-Time System Executive Disk-Oriented<br>System    | 1-13 |

| 1.2.5     | PDP-15/40 Disk-Oriented Background/Foreground System            | 1-13 |

| 1.3       | System Organization                                             | 1-13 |

| 1.3.1     | Central Processor (CPU)                                         | 1-14 |

| 1.3.2     | Memory                                                          | 1-14 |

| 1.3.3     | I/O Processor (IPU)                                             | 1-15 |

| 1.3.4     | Console                                                         | 1-15 |

| 1.3.5     | System Peripherals                                              | 1-15 |

| CHAPTER 2 | PROCESSOR ORGANIZATION                                          |      |

| 2.1       | Central Processor Description                                   | 2-1  |

| 2.1.1     | Internal Registers                                              | 2-1  |

| 2.1.2     | Control Console                                                 | 2-4  |

| 2.2       | Central Processor Expansion Options                             | 2-4  |

| 2.3       | I/O Processor Organization                                      | 2-6  |

| 2.3.1     | Data Transfer Facilities                                        | 2-9  |

#### CONTENTS (Cont)

|       |                               | Page |

|-------|-------------------------------|------|

| 2.3.2 | I/O Processor Activities      | 2-11 |

| 2.3.3 | I/O Processor Organization    | 2-12 |

| 2.4   | Core Memory                   | 2-14 |

| 2.4.1 | Memory Data Transfer          | 2-15 |

| 2.4.2 | Parity                        | 2-15 |

| 2.4.3 | Memory Modularity             | 2-16 |

| 2.4.4 | Memory Addressing             | 2-16 |

| 2.4.5 | Memory Port Switch            | 2-16 |

| 2.4.6 | MX15-A Memory Bus Multiplexer | 2-17 |

#### CHAPTER 3 INSTRUCTION FORMATS

| 3.1   | General                             | 3-1  |

|-------|-------------------------------------|------|

| 3.2   | Memory Reference Instruction Format | 3-1  |

| 3.3   | Augmented Instruction Format        | 3-2  |

| 3.4   | Timing                              | 3-2  |

| 3.5   | Memory Reference Instructions       | 3-3  |

| 3.6   | Augmented Instructions              | 3-12 |

| 3.6.1 | Operate Instructions                | 3-12 |

| 3.7   | Input/Output Transfer Instructions  | 3-28 |

| 3.7.1 | PDP-15 IOTs                         | 3-30 |

| 3.7.2 | Teletype Keyboard                   | 3-32 |

| 3.7.3 | Teletype Teleprinter                | 3-32 |

| 3.8   | Index Instructions                  | 3-33 |

#### CHAPTER 4 ADDRESSING FEATURES

| 4.1   | Introduction to Memory Addressing                  | 4-1 |

|-------|----------------------------------------------------|-----|

| 4.2   | Types of Addressing                                | 4-1 |

| 4.3   | Description of the Types of Addressing             | 4-3 |

| 4.3.1 | Direct Addressing – Bank or Page Mode              | 4-4 |

| 4.3.2 | Indirect Addressing – Bank or Page Mode            | 4-4 |

| 4.3.3 | Auto-Increment Addressing – Bank or Page Mode      | 4-5 |

| 4.3.4 | Indexed Addressing – Page Mode Only                | 4-6 |

| 4.3.5 | Indirect Indexed Addressing – Page Mode Only       | 4-8 |

| 4.3.6 | Auto-Increment Indexed Addressing - Page Mode Only | 4-9 |

#### CONTENTS (Cont)

|           |                          | Page |

|-----------|--------------------------|------|

| 4.4       | Special Addressing Cases | 4-10 |

| 4.5       | Processor Addressing     | 4-11 |

|           |                          |      |

| CHAPTER 5 | I/O PROCESSOR SYSTEM     |      |

| E 1       | Convert Device the       | E 1  |

| 5.1 | General Description               | 5-1  |

|-----|-----------------------------------|------|

| 5.2 | I/O Processor Priority Structure  | 5-3  |

| 5.3 | The Data Channel Controller       | 5-3  |

| 5.4 | Multicycle Channel Block Transfer | 5-3  |

| 5.5 | Single-Cycle Block Transfers      | 5-8  |

| 5.6 | Increment Memory                  | 5-9  |

| 5.7 | Add-To-Memory                     | 5-9  |

| 5.8 | Program–Controlled Transfer       | 5-9  |

| 5.9 | Program Interrupt Facility        | 5-11 |

#### CHAPTER 6 OPTIONS

| 6.1   | KE15 Extended Arithmetic Element  | 6-1  |

|-------|-----------------------------------|------|

| 6.1.1 | EAE Microinstructions             | 6-2  |

| 6.1.2 | EAE Shifting Instructions         | 6-13 |

| 6.1.3 | EAE Arithmetic Instructions       | 6-20 |

| 6.2   | KM15 Memory Protect               | 6-33 |

| 6.3   | KT15 Memory Protect and Relocate  | 6-37 |

| 6.4   | MP15 Memory Parity                | 6-41 |

| 6.5   | KF15 Power Fail Option            | 6-42 |

| 6.6   | KW15 Real-Time Clock Option       | 6-42 |

| 6.7   | KA15 Automatic Priority Interrupt | 6-46 |

| 6.7.1 | API Hardware                      | 6-47 |

| 6.7.2 | API Instructions                  | 6-48 |

| 6.7.3 | Programming Considerations        | 6-49 |

| 6.7.4 | Programming Examples              | 6-53 |

| 6.8   | FP15 Floating-Point Processor     | 6-55 |

|       |                                   |      |

APPENDIX A INSTRUCTION SUMMARY

A-1

#### ILLUSTRATIONS

| Figure No. | Title                                       | Art No. | Page         |

|------------|---------------------------------------------|---------|--------------|

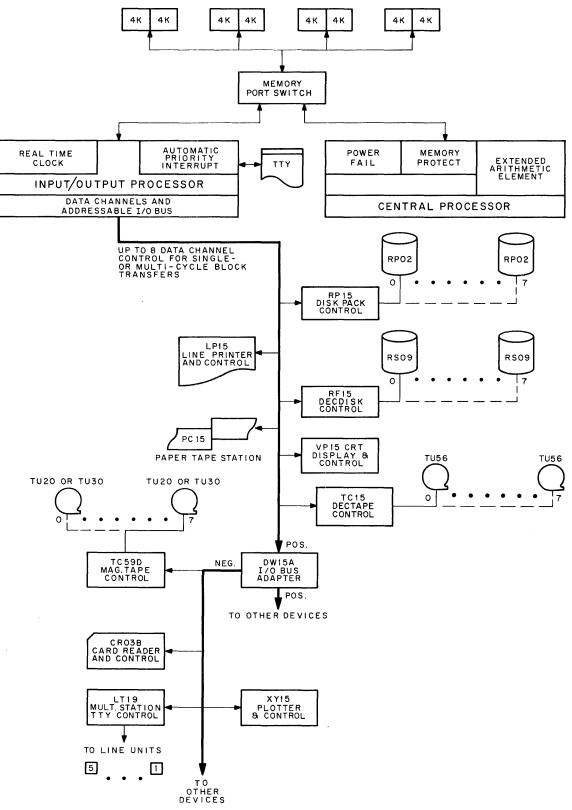

| 1-1        | PDP-15 System Organization                  | 15-0174 | 1-14         |

| 1-2        | System Organization                         | 15-0017 | 1-16         |

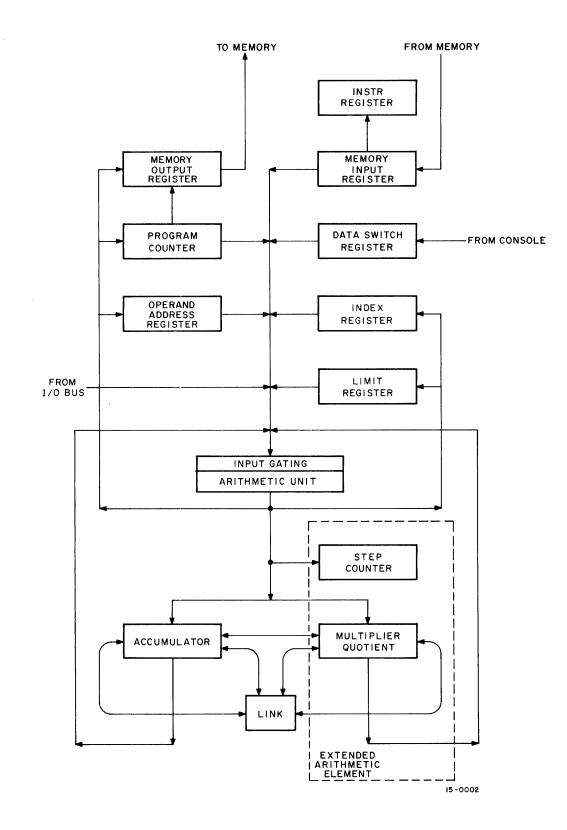

| 2-1        | Central Processor, Simplified Block Diagram | 15-0002 | 2-2          |

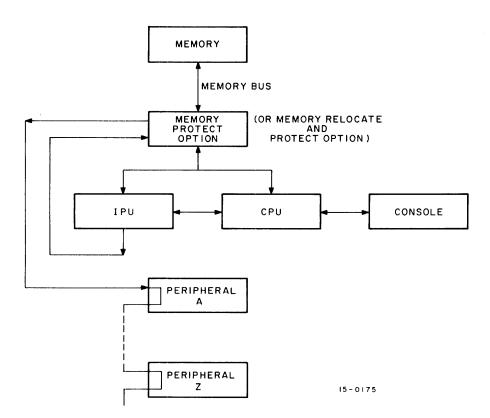

| 2-2        | PDP-15 System with Memory Protect Option    | 15-0175 | 2-6          |

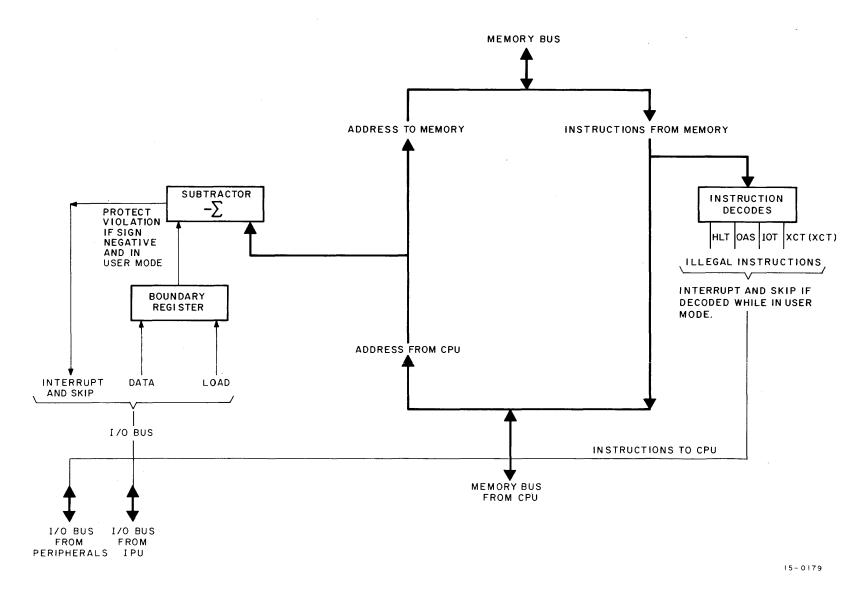

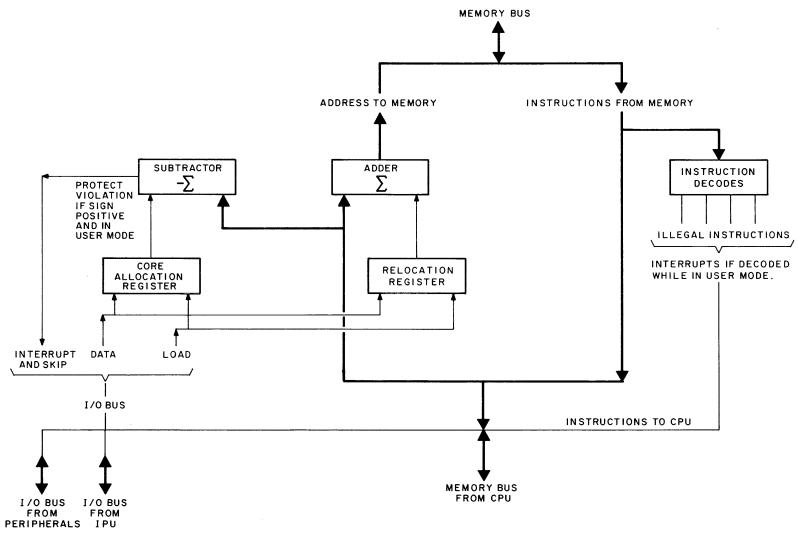

| 2-3        | Memory Protect Block Diagram                | 15-0179 | 2-7          |

| 2-4        | Memory Protect and Relocate Block Diagram   | 15-0178 | 2-8          |

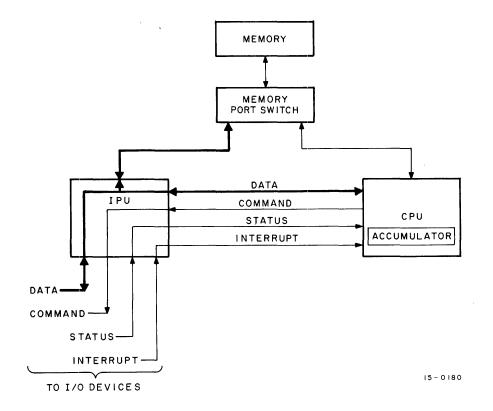

| 2-5        | Data Transfer Facilities                    | 15-0180 | 2-9          |

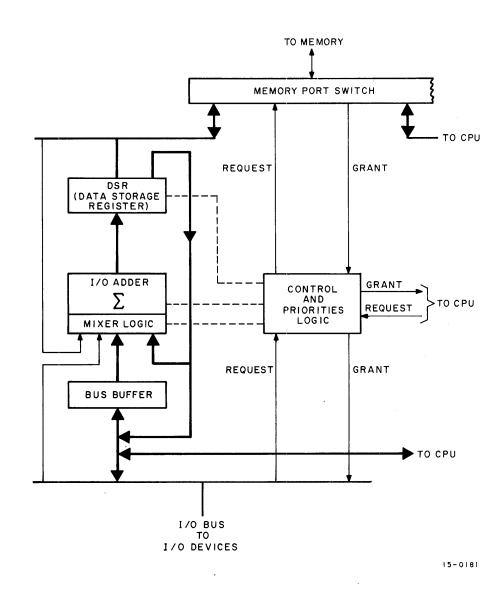

| 2-6        | I/O Processor Block Diagram                 | 15-0181 | 2-13         |

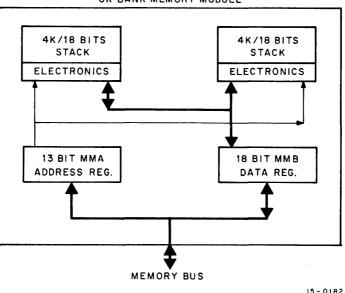

| 2-7        | Memory Organization                         | 15-0182 | 2-14         |

| 2-8        | Physical Memory Organization                | 15-0183 | 2-16         |

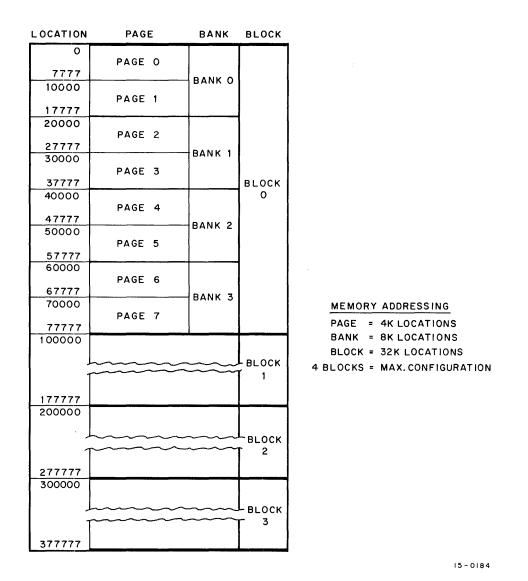

| 2-9        | Memory Addressing                           | 15-0184 | 2-17         |

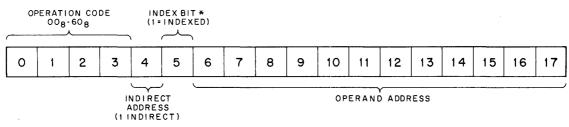

| 3-1        | Memory Reference Instruction Word           | 15-0188 | 3-1          |

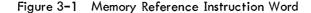

| 3-2        | Augmented Instruction Format                | 15-0204 | 3-2          |

| 3-3        | Instruction Bit Configuration               |         | 3-13         |

| 3-4        | Allowable Microinstruction Combinations     |         | 3-14         |

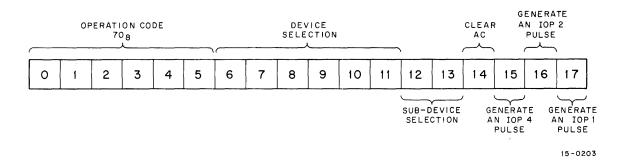

| 3-5        | IOT Instruction Format                      | 15-0203 | 3-28         |

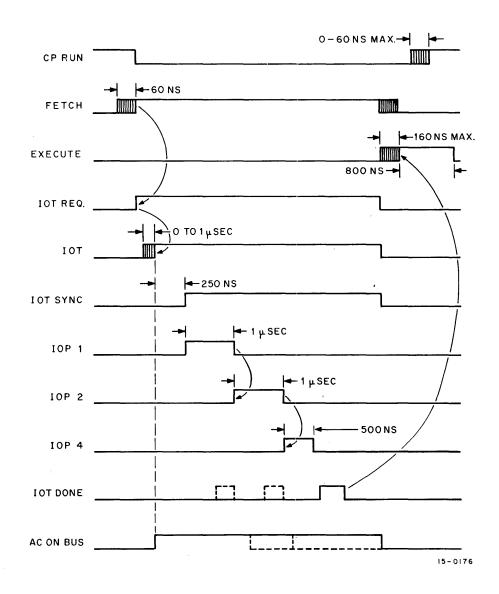

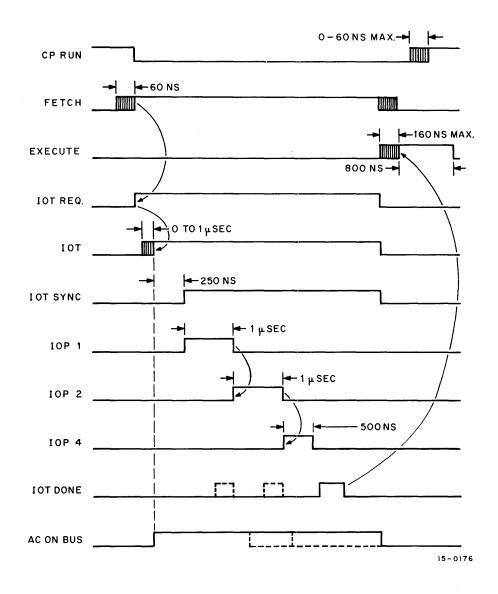

| 3-6        | IOT Instruction Timing                      | 15-0176 | 3-29         |

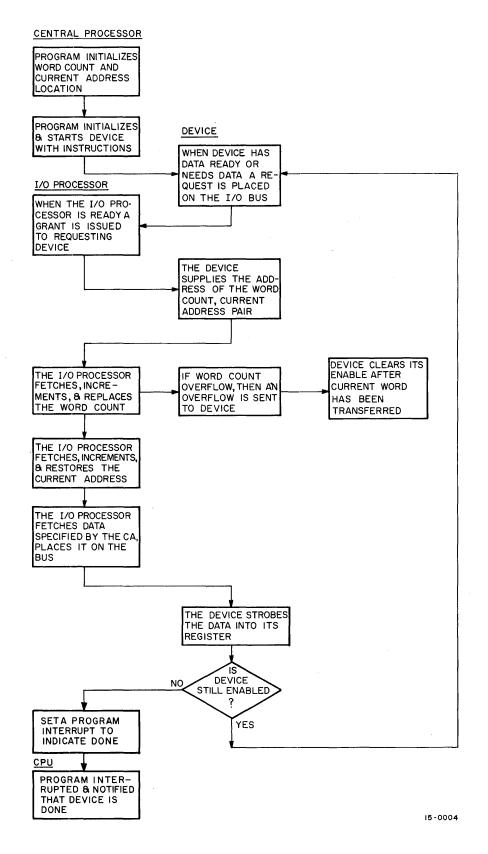

| 5-1        | Multicycle Out Block Transfer, Flowchart    | 15-0004 | 5-5          |

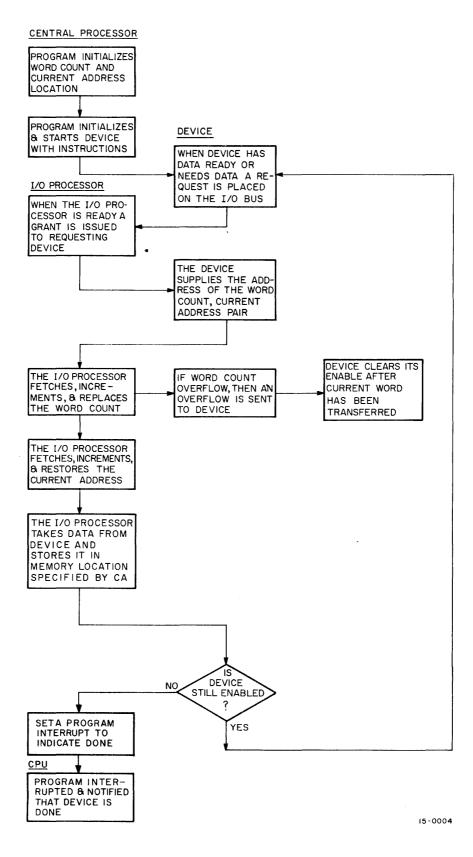

| 5-2        | Multicycle In Block Transfer, Flowchart     | 15-0004 | 5-6          |

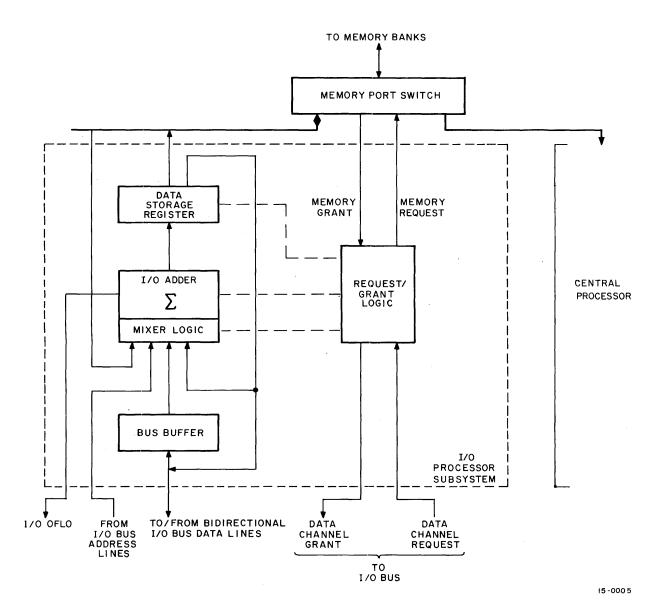

| 5-3        | Multicycle Transfer Implementation          | 15-0005 | 5 <b>-</b> 7 |

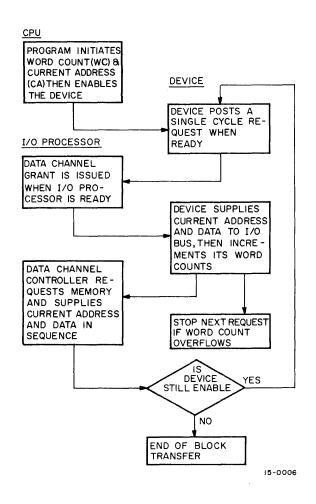

| 5-4        | Single-Cycle Block Transfer Flowchart       | 15-0006 | 5-8          |

| 5-5        | IOT Instruction Timing                      | 15-0176 | 5-11         |

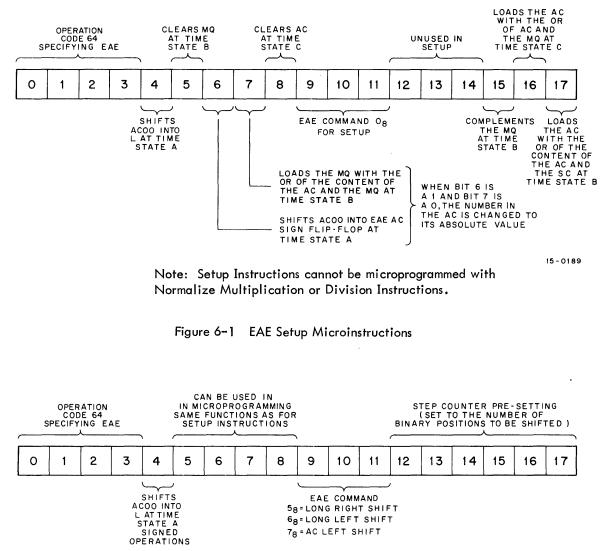

| 6-1        | EAE Setup Microinstructions                 | 15-0189 | 6-2          |

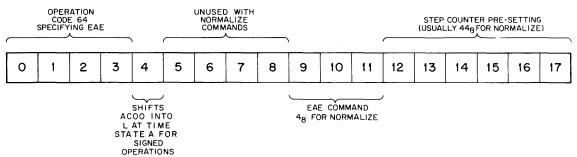

| 6-2        | EAE Shift Microinstructions                 | 15-0190 | 6-2          |

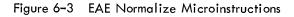

| 6-3        | EAE Normalize Microinstructions             | 15-0191 | 6-3          |

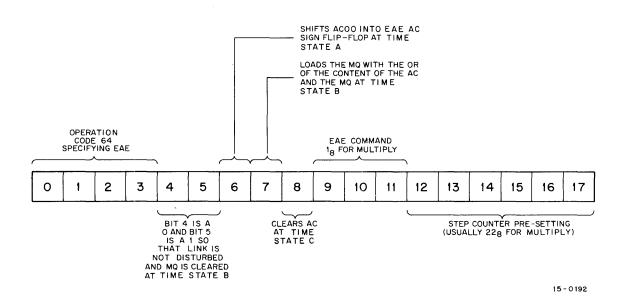

| 6-4        | EAE Multiplication Microinstructions        | 15-0192 | 6-3          |

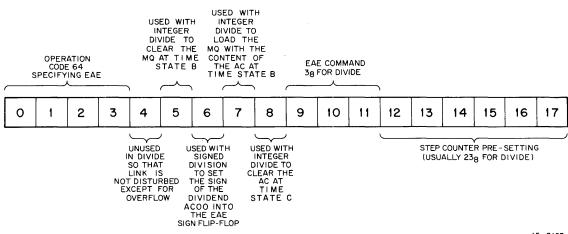

| 6–5        | EAE Division Microinstructions              | 15-0193 | 6-3          |

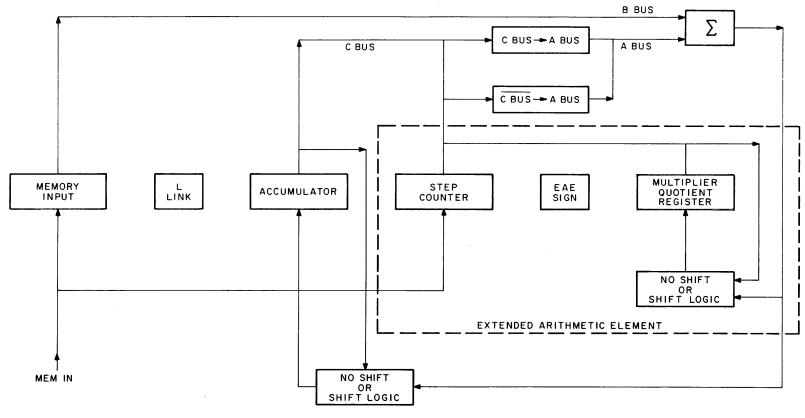

| 6-6        | EAE Simplified Block Diagram                | 15-0177 | 6-4          |

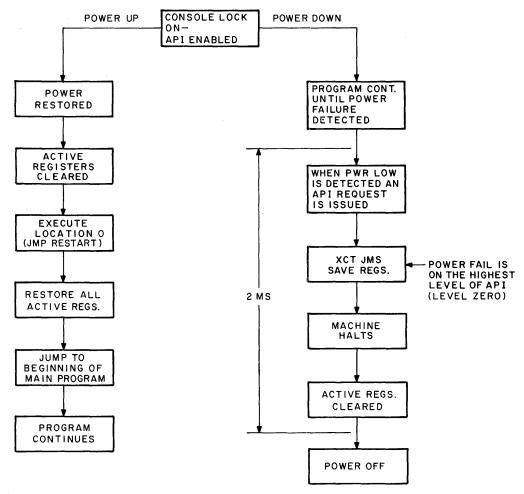

| 6-7        | Power Fail Up/Down Sequence                 | 15-0185 | 6-43         |

| 6-8        | Power Fail Up/Down Sequence                 | 15-0186 | 6-44         |

| 6-9        | Power Fail Up/Down Sequence                 | 15-0187 | 6-45         |

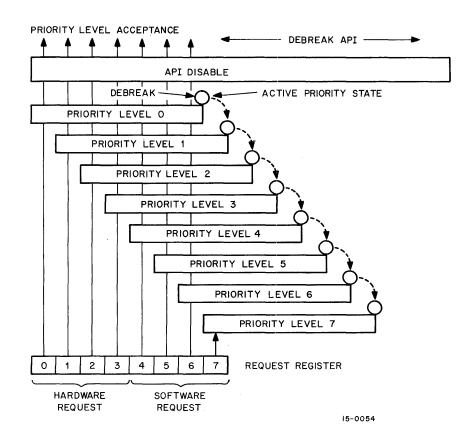

| 6-10       | API System Simplified Block Diagram         | 15-0054 | 6-47         |

| TA | 3L | E | S |

|----|----|---|---|

|----|----|---|---|

.

| Table No. | Title                                                                         | Page         |

|-----------|-------------------------------------------------------------------------------|--------------|

| 2-1       | PDP-15 I/O Capabilities                                                       | 2-10         |

| 3-1       | PDP–15 Central Processor Cycle Times for Basic and<br>Expanded Configurations | 3–3          |

| 4-1       | Types of Addressing                                                           | 4-1          |

| 5-1       | I/O Capabilities                                                              | 5-1          |

| 5-2       | Total Execution Times for IOPs                                                | 5-10         |

| 6-1       | EAE Microinstructions                                                         | 6-5          |

| 6-2       | EAE Microinstructions                                                         | 6-6          |

| 6-3       | KM15 Instruction Set                                                          | 6-36         |

| 6-4       | KT15 Instruction Set                                                          | 6–39         |

| 6-5       | MP15 Instruction Set                                                          | 6-41         |

| 6-6       | IOT Instructions for Real-Time Clock                                          | 6-43         |

| 6-7       | API IOT Instructions                                                          | 6-49         |

| 6-8       | SPI Control Word Format                                                       | 6-50         |

| 6-9       | ISA Control Word Format                                                       | 6-51         |

| 6-10      | Maintenance Instruction Status Word                                           | 6-52         |

| A-1       | Memory Reference Instructions                                                 | A-1          |

| A-2       | Operate Instructions                                                          | A-2          |

| A-3       | Index Register Transfer Instructions                                          | A-4          |

| A-4       | Register Control Instructions                                                 | A-4          |

| A-5       | EAE Instructions                                                              | A-5          |

| A-6       | Standard API Channel/Priority Assignments                                     | A <b>-</b> 6 |

| A-7       | PDP-15 IOT Device Selection Codes                                             | A-7          |

| A-8       | Input/Output Transfer Instructions                                            | A-8          |

#### PREFACE

The PDP-15 Users Handbook is the principal guide to the PDP-15 hardware. This manual is presented in two volumes: Volume 1 PROCESSOR and Volume 2 PERIPHERALS. The PDP-15 Users Handbook includes system features and specifications, functional descriptions, machine language programming considerations, and a detailed description of the instruction repertoire. The chart and table on pages iii and iv show the relationships of the other PDP-15 system documentation and give abstracts of their contents.

### Chapter 1 System Description

#### 1.1 SYSTEM SOFTWARE

#### 1.1.1 Introduction

The PDP-15 System is divided into a number of configurations; each configuration having a powerful software package available. These software packages are designed to service the needs of a particular system configuration.

The PDP-15/10 configuration software is governed by the COMPACT Software System, a complete package including Assembler, Editor, Octal Debugging Technique, and mathematical and utility routines, all designed to function in 4K or 8K systems.

#### COMPACT Software System

Assembler Editor ODT (Octal Debugging Technique) Math Package Utility routines: Hardware Read-in Mode (HRM) punch routine Paper tape handling routines Teletype I/O routines Octal dump routine

Memory scan routine

For PDP-15/10 Systems equipped with DECtape, the FAST (Fast Acquisition of System Tape) System is provided to retrieve frequently-used programs from DECtape.

Installations with a minimum of 8K words of core memory and a high-speed paper tape reader/punch can use the Basic I/O Monitor to extend system capabilities. The PDP-15/20 Advanced Monitor

System operates from mass storage devices (DECtape or DECdisk) and is device independent; consequently programs need not be limited to the use of certain specified I/O devices.

Simple I/O statements control data handling; selection of physical devices is determined at load time on the actual machine, not when the program is written. Real-time I/O level subroutines can easily be integrated into the system as new devices are added.

#### 1.1.2 PDP-15/20 Advanced Monitor System

The PDP-15/20 Advanced Monitor is used for batch processing. In the primary (keyboard) mode, the user has interactive access to a large set of system programs to facilitate program development and testing.

All Advanced Monitor functions, as well as the many available system software routines, are specially designed to make the system as accessible as possible to users who want "hands-on" interaction; at the same time, routine elements of programming can be handled simply and easily.

#### PDP-15/20 Advanced Monitor System

**Keyboard Monitor** Teletype handler Command decoder Input/Output Programming System (IOPS) data handling, device handling, and interrupt routines Real-time clock handler Error detector program Device assignment tables Batch processor (paper tape or card control) FORTRAN IV SYSTEM LOADER FOCAL MACRO-15 Macro Assembler DDT-15 Dynamic Debugging Technique Text Editor PIP-15 Peripheral Interchange Program Linking Loader Chain and Execute Patch

SGEN System Generator Octal Dump (DUMP) Library Update (UPDATE) DECtape Copy (DTCOP)

#### 1.1.3 PDP-15/30 Background/Foreground Monitor

Under control of the PDP-15/30 Background/Foreground Monitor, real-time tasks are executed in the computer foreground and have immediate call on the system's resources. Unused background time, available between service calls for the real-time tasks, is useful in program development, testing, or other lower-priority computation.

PDP-15/30 software encompasses all Advanced Monitor functions and capabilities (see list above). In addition, the PDP-15/30 Background/Foreground Monitor contains all the supervisory controls necessary for concurrent processing of background and foreground tasks.

PDP-15 System users can draw on the resources of the program library and the applications knowledge of DECUS, the Digital Equipment Computer Users Society, in addition to the Advanced Monitor programs and routines. DECUS members share in the exchange of programs and technical papers at regularly scheduled meetings throughout the year; the proceedings of all DECUS society meetings are published under DEC sponsorship.

#### PDP-15/30 Background/Foreground Monitor System

Background/Foreground Monitor controls the use of the PDP-15 by two co-resident programs.

System loader Command decoder IOPS data-handling, device-handling, and interrupt routines Real-time clock handler Error detector program Device assignment tables

In addition to the above programs, the programs of the PDP-15/20 Advanced Monitor System are included in the 15/30 System.

#### 1.1.4 PDP-15/40 Disk-Oriented Background/Foreground System

PDP-15/40 Disk-oriented Background/Foreground Systems are responsive to the high demands of industrial and engineering environments, where the need for a background/foreground mode of operation is compounded by the necessity of large random-access files. PDP-15/40 Systems with 24,576 words of core memory, high-speed paper tape facilities, and DECtape storage, also incorporate a DECdisk control and two random-access disk files. The disks, whose storage capacity is 524,288 18-bit words, can be expanded to 2,097,152 words, permit high-speed overlays, chaining, and system and user loading.

The disk-oriented background/foreground monitor system handles all the functions of the PDP-15/30 Background/Foreground Monitor in a high-speed disk environment.

#### PDP-15/40 Disk-Oriented Background/Foreground Monitor System

Disk-oriented Background/Foreground Monitor Systems loader Command decoder IOPS data-handling, device-handling, and interrupt routines Real-time clock handler Error detector program Device assignment tables

The programs in the PDP-15/20 Advanced Monitor are included in this section.

#### 1.1.5 PDP-15/10 COMPACT Software System

The PDP-15/10 COMPACT Software System is a concise programming system that includes a symbolic assembler, a text editor for creating programs on-line, debugging routines, utility routines, and mathematical routines. The COMPACT Software System is designed to operate in the 4K or 8K paper-tape input/output environment of the basic PDP-15/10. PDP-15/10 Systems with more than 8K of core are not supported by the COMPACT Software System. Installations with a minimum of 8K of core and a high-speed paper tape reader/punch can use the Basic I/O Monitor Software to extend system capabilities.

Utility routines in the COMPACT Software System include a Hardware Read-in Mode (HRM), punch routines, paper tape handling routines, Teletype I/O routines, an octal dump routine, and a memory scan routine used for scanning areas of memory for a particular bit configuration. For systems with DECtape, the FAST system can retrieve frequently used programs from DECtape.

COMPACT Assembler – The two-pass COMPACT Assembler has a useful set of selected pseudo-ops for functions such as table formations, symbol table and variable control, and text handling.

COMPACT Debugging Routines – Debugging routines are included in the COMPACT Software System. ODT (Octal Debugging Technique) is an aid to the user conducting interactive, on-line debugging sessions using octal numbers and Teletype commands.

COMPACT Editor – The COMPACT Editor takes advantage of the powerful character string, search, and modification commands developed for the larger systems. It provides for the creation and/or identification of source programs, other than ASCII text material, using keyboard commands. The Compact Editor also offers an efficient method for on-line processing of paper tapes.

#### 1.1.6 PDP-15/10E Basic I/O Monitor

The Basic I/O Monitor, for 8K configurations, provides a link between the call for I/O, by either user or system programs, and the actual I/O execution. All I/O calls to system devices are serviced by DEC-supplied device handlers which reside in the Input/Output Programming System (IOPS). The device handlers actually move data between the program and the I/O devices. Device handlers initialize the devices and perform all other functions peculiar to a given I/O device, such as servicing interrupts in a real-time environment. User-supplied device handlers can be incorporated into the system to perform the functions described above for special I/O devices.

#### 1.1.7 PDP-15/20 Advanced Monitor System

The PDP-15/20 Advanced Monitor combines the functions of the Basic Monitor with the executive control of bulk storage devices (to provide automatic operation), which includes batch processing, keyboard interaction, and real-time queuing. The Advanced Monitor has a large set of commands that direct the operation of the system. These commands perform three major functions:

- a. Provide information about the system such as commands available and their functions; error diagnostics; the standard logical-physical I/O device associations; I/O level programs available (device handlers); special memory registers and their functions.

- b. Permit the standard physical-logical device associations to be modified, thereby enabling the dynamic allocation of devices at load-time. This is a natural extension of device independence provided by the Basic I/O Monitor.

- c. Supervise the loading and execution of all system and user programs, their associated I/O device handlers, and library subroutines, in addition to generating error messages and recovery procedures.

Coupled with keyboard control of system programs, the Advanced Monitor enables the user to deal with his entire problem (editing, assembling, compiling, loading, debugging and running) in a straightforward manner. The Advanced Monitor consists of command decoder, IOPS routines, real-time clock handler, error detector routine, and device assignment table (DAT).

The system loader always resides in upper memory and is responsible for loading the Monitor into lower memory. Return calls from system or user programs cause restoration of control to the Monitor.

The Monitor command decoder detects requests for system programs and loads the system loader, which brings in the requested program. In response to control cards or keyboard commands, it also manipulates the device assignment table to provide device independence. The Monitor Input/Output Programming System (IOPS) routines include data handling subroutines, device handlers, and interrupt service routines for the priority interrupt system, as well as the Teletype keyboard and printer. All other IOPS device handlers are stored on the system device until required by object programs.

The Monitor contains a device assignment for each table entry; because the contents of the table can be altered by commands to the Advanced Monitor, actual I/O devices can be changed without altering the program references to these devices. The following system software is supplied with all PDP-15/20 Advanced Monitor System.

FORTRAN IV – The PDP-15 FORTRAN IV compiler is a two-pass system which accepts statements written in the FORTRAN language and produces a relocatable object code capable of being loaded by the Linking Loader program. The PDP-15 FORTRAN IV compiler is compatible with USA FORTRAN IV, as defined in the USA Standard X3.9-1966, modified to allow the compiler to operate in 8,192 words of core storage. The FORTRAN IV compiler generates programs which operate with the program interrupt enabled and works with assembly language programs that recognize and service real-time devices. Subroutines written in either FORTRAN IV or the MACRO Assembler language can be loaded with and called by FORTRAN IV main programs. Source language diagnostics are produced during compilation, and a symbol table is generated for use in on-line debugging.

FOCAL – An on-line, interactive (conversational) algebraic language designed to aid scientists, engineers, and students in solving numerical problems. The language consists of short, easy-to-learn English imperative statements. Mathematical expressions are usually typed in standard notation. FOCAL puts the full calculating power and speed of the PDP-15 under easy conversational control. For example, FOCAL can be used to simulate mathematical models, to plot curves, to handle sets of simultaneous equations in n-dimensional arrays, and to solve many other kinds of problems. FOCAL runs in the Advanced Software Environment.

1-6

MACRO-15 Assembler - MACRO-15 Assembler enables the programmer to use mnemonic symbols to represent operation codes, locations, and numeric data. The programmer can direct the MACRO Assembler's processing through use of a full set of pseudo-operations. An output listing can be obtained to illustrate the programmer's source coding, as well as the binary object code produced by the MACRO Assembler. An optional third pass by the MACRO Assembler provides a cross reference listing. PDP-15 users can also make use of highly sophisticated macro generating and calling facilities within the context of a symbolic assembler. Some features of MACRO-15 are as follows:

- a. The ability to define and call nested macros

- b. Conditional assembly based on the computational results of symbols or expressions

- c. Repeat functions

- d. Boolean manipulation

- e. Optional symbolic listing cross reference

- f. Two forms of radix control (octal and decimal) and two text modes (7-bit ASCII and 6-bit trimmed ASCII)

- g. Global symbols for easy linking of separately assembled programs

- h. Choice of output format: relocatable, absolute binary (checksummed), or full binary (unchecksummed), capable of being loaded via the hardware READ-IN switch.

- i. The ability to call I/O system macros that expand into IOPS calling sequences.

Dynamic Debugging Technique DDT-15 - A versatile tool for dynamic program checkout and modification. An operator can load a program and run all or selected portions of it in a real-time interrupt environment under interactive supervision of DDT-15. The Teletype keyboard controls DDT and program examination and modification. The operator can insert a breakpoint, specify the number of program iterations before interrupting the program, and start the program at any point using a simple set of commands. The operator can examine or alter any location symbolically and then rerun the program using other commands.

Text Editor – Using the PDP-15 Advanced Software System, an operator can create or edit symbolic text utilizing any input or output device. A "context" method is employed throughout to identify the block of data which the user wishes to modify; that is, the block is specified by its ASCII text rather than by a numbering scheme imposed externally upon the text. The Text Editor operates on these lines of ASCII text. Commands are available which facilitate insertion, deletion, and modification of data in the object file.

PIP-15 Peripheral Interchange Program - PIP-15 facilitates the manipulation and transfer of data files from any input device to any output device. It can be used to update file descriptions, verify, delete, segment, or combine files, perform code conversions, and copy tape.

Linking Loader - The Linking Loader loads any PDP-15 FORTRAN IV or MACRO-15 object program, in either relocatable or absolute format. Its tasks are loading and relocation of programs, loading of called subroutines, retrieval and loading and relocation of the necessary symbol tables.

CHAIN and EXECUTE - The programs CHAIN and EXECUTE facilitate a user-generated system of core overlays in the PDP-15 Advanced Monitor environment. This system of overlays consists of a resident main program, other indicated resident routines, a resident blank COMMON storage area, and a set of subroutines which overlay each other, as directed by the user. These subroutines are grouped into units called LINKS. Many, or all, LINKS can overlay each other, and several LINKS can overlay a larger LINK without overlaying each other. Cascading of suboverlays is not limited.

A LINK is loaded into core when a subroutine within the LINK is called and remains resident until overlayed. A LINK's core image is not recorded or "swapped out" when it is overlayed. The same image is brought into core each time a LINK is loaded.

Subroutines are called and return control to the calling routine in the normal fashion. There is no imposed order in which routines must be called, nor is there restriction of the routines callable by any routine.

The program CHAIN is used to build an XCT file, and the program EXECUTE supervises core residency during the execution of a CHAIN-built Overlay System.

PATCH - The user can conveniently examine and modify system program parameters and system programs stored on mass storage devices (DECtape or DECdisk) using the utility program PATCH.

UPDATE - The contents of binary library files on mass storage devices can be listed and updated, by insertion, deletion, or replacement operations using the library update utility program UPDATE. A binary library file is defined as any set of relocatable programs stored together as one unit in a single file. The PDP-15/20 Advanced Monitor System library file (.LIBR BIN) is a typical example. DUMP - The user has the capability to output, on any listing device, specified core locations stored on the SAVE or QAREA of a mass storage device using the DUMP utility program. The listing output of any block of mass storage (DECtape or DECdisk) is obtained through the DUMP program.

SRCCOM - The source compare (SRCCOM) utility program compares any two symbolic programs and lists the differences between them. SRCCOM is useful in proofing an edited program and in keeping track of symbolic changes.

SGEN - The system generator (SGEN) utility program is used to build resident mass storage systems tailored to the customer's installation. Operating in conversational mode, SGEN uses the query/response technique to build the operating system to the customer's needs.

#### 1.1.8 PDP-15/30 Background/Foreground Monitor System

The PDP-15/30 Background/Foreground Monitor system is an extension of the Advanced Monitor system which enables the concurrent, time-shared use of the PDP-15/30 through protected, foreground user programs with a background of batch processing, through program development, or through low-priority user programs. The system handles a variety of tasks, from high-speed data gathering applications such as those in physics to thousand-channel input/output applications such as warehouse inventory control. With the Background/Foreground Monitor the user can:

- a. Effectively have two computers: one for on-line data acquisition and control, one for off-line program development, and data reduction at the price of one system;

- b. Achieve 100% use of his system, independent of data rates.

The foreground programs are assumed to be checked out and to operate from requests to the program interrupt or priority interrupt facilities. At LOAD TIME, foreground programs have first priority over core memory and I/O devices, and at EXECUTION TIME they have priority (according to their assigned priority levels) over processing time and shared I/O devices.

The background program (or sequential series of programs) is essentially the same as the single-user program under the Advanced Monitor system; that is, it can be an assembly, a compilation, a debugging run, a production run, an editing task, or batch processing. The background program can use whatever facilities (core, I/O, processing time, etc.) are available and not required by the foreground programs.

The Background/Foreground Monitor can be used to direct the time-shared use of the PDP-15/30 by the two coresidential programs and to perform the following functions:

- a. Schedules processing time

- b. Protects the foreground job's core

- c. Protects the foreground job's I/O devices

- d. Allows the sharing of multi-unit device handlers, such as DECtape, by both foreground and background jobs

- e. Directs the shared use of the system real-time clock to time specified intervals

- f. Directs communication between background and foreground jobs via core-to-core transfers.

#### 1.1.9 PDP-15/35 Real-Time System Executive

The PDP-15/35 Real-Time System Executive (RSX) is a disk-based system designed for multitask, multiprogramming environments, where real-time interrupts, time interval task activation, and a priority job queue must all be coordinated under a priority structure.

#### 1.1.10 PDP-15/40 Disk-Oriented Background/Foreground Monitor System

The PDP-15/40 system uses a disk-oriented version of the Background/Foreground Monitor; it contains all of the features described above in the PDP-15/30 Background/Foreground Monitor section. The disk system enables high-speed overlays, chaining, and system and user program loading to occur. The number of records that can be opened on the disk is limited only by available word space. The PDP-15/40 system contains 524,288 words of disk storage, expandable to 2,097,152 words.

#### 1.1.11 Additional Systems Software

8TRAN - The 8TRAN translator is used to translate programs written for PDP-8 in PAL III, PAL-D, or MACRO-8 assembly language to MACRO-15 assembly language. The purpose of the translator is not to produce a program which runs on the PDP-15 by simulating the PDP-8, but rather to do the straight-forward portion of the translation and clearly indicate to the programmer those parts of the code which require review in the light of the PDP-15's greater word length and more powerful instruction set.

STATPAC - STATPAC is a comprehensive and open-ended package of modular statistical programs designed to operate under the PDP-15 Advanced Monitor. The user with limited computer knowledge can use STATPAC to obtain statistically meaningful results from data. STATPAC includes modules for CONTROL, INPUT, DESCRIPTIVE STATISTICS, STEPWISE LINEAR REGRESSION, and MULTIPLE LINEAR REGRESSION functions.

#### 1.2 PDP-15 SYSTEM CONFIGURATIONS

PDP-15 Systems offer comprehensive solutions to real-time data problems by combining new design concepts with a wide variety of traditional DEC features. Through DEC's experience in the medium-scale scientific computer field, the PDP-15 System simplifies the user's tasks in a demanding real-time environment.

Because certain data-handling tasks require specific hardware and software configurations, DEC has developed four standard PDP-15 Systems, ranging in power from the modestly priced basic PDP-15/10 to the PDP-15/40 Background/Foreground Disk Monitor System. At every level, the capabilities of the hardware are under the control of a monitor designed specifically for them.

The software systems are designed around the hardware with the user environment in mind. The principal design objectives are to provide (a) a system that is convenient for the user to implement and that affords the user access to the full power of the hardware, (b) a system that allows the user to easily integrate his applications program and special peripheral device handlers, and (c) a system that can expand naturally. PDP-15 Systems software enables the user to move from a very basic machine to a sophisticated system without the cost and complication of reprogramming at each upward step.

The hardware systems were designed with complete autonomy between central processor, input/output processor, and memory, so that processing and I/O operations can occur concurrently in overlapping cycles; TTL integrated-circuit construction for high reliability; fast internal speeds, including an 800-ns memory cycle time, to meet the demands of real-time data processing; core memory expansion to 131,072 words for future growth; and a sophisticated memory protect system for multi-user integrity. Peripheral device handling and interfacing to other instruments are easily accomplished, and system growth potential is virtually unlimited with the modular structure of PDP-15 Systems.

#### 1.2.1 PDP-15/10 Basic System

The PDP-15/10 is the first level PDP-15 System. The system's design provides limited budget users access to the power, speed, and 18-bit word length of PDP-15 hardware, in the expectation that the system can later be expanded to take full advantage of the advanced software capabilities inherent in the system's design.

Hardware includes 4,096 18-bit words of core memory and a Model 33 ASR Teletype console teleprinter. The system has the rapid PDP-15 800-ns memory cycle time which provides 1.6-µs add capability. Facilities for later expansion are prewired into the system; additional memory and peripherals can be plugged in as required. Software is governed by the COMPACT Programming System, a complete package including Assembler, Editor, Octal Debugging Technique, and mathematical and utility routines. All are designed to function in a 4096 word system. The software offers complete upward compatibility at the source level and field-proven reliability. Programs written for execution under COMPACT can also run, with little modification, within all PDP-15 System levels up through PDP-15/30 and PDP-15/40 Background/ Foreground Systems.

#### 1.2.2 PDP-15/20 Advanced Monitor System

PDP-15/20 is an 8,192-word mass storage-oriented system designed for research and engineering environments where real-time data acquisition and control tasks are combined with program development and testing.

Program development, debugging, and modification are all handled under monitor control, virtually ending intermediate operations. Unique real-time input/output routines can also be integrated into the system monitor to accelerate set-up and recovery.

Users are spared the task of writing system software to handle input/outputs to all standard system peripherals, since appropriate routines are supplied with the monitor. The net result is that even inexperienced computer users can get their applications programs "on the air" in a minimum amount of time.

PDP-15/20 hardware facilities include not only, 8,192-words of core memory and high-speed papertape facilities but also, a DECtape control unit and two tape transports for convenient mass-memory storage. The extra-heavy duty 35 KSR Teletype unit is included in the PDP-15/20 configuration to guarantee a high degree of reliability under the strain of continued heavy use. Also included is the extended arithmetic element described in Chapter 6. This unit facilitates high-speed multiplication, division, shifting, normalization, and register manipulation.

The 15/20 Advanced Monitor System permits two types of user interaction. These are (1) batch processing for routine production jobs, and (2) keyboard interaction which enables the user to operate the system with simple commands typed at the keyboard.

Other PDP-15/20 Advanced Monitor features that make use of processor options are: a real-time clock control and a priority interrupt control.

#### 1.2.3 PDP-15/30 Background/Foreground System

The PDP-15/30 System is designed to meet the demands of research, engineering, and industrial environments, where one or more real-time tasks typically require continuous responsiveness from the computer, but do not use 100% of its capacity.

The PDP-15/30 Background/Foreground System requires a minimum of 16,384 words of core memory and all the devices standard for the PDP-15/20. In addition, PDP-15/30 Systems are equipped with a memory protect system, a real-time clock, automatic priority interrupt, two DECtape transports, and a second on-line Teletype for background use.

#### 1.2.4 PDP-15/35 Real-Time System Executive Disk-Oriented System

The PDP-15/35 System contains 16,384 words of core memory, high-speed paper-tape facilities, two DECtape transports, the automatic priority interrupt option, real-time clock, and a DECdisk file with 262,144 words of storage.

#### 1.2.5 PDP-15/40 Disk-Oriented Background/Foreground System

PDP-15/40 Disk-Oriented Background/Foreground System fulfills the demands of industrial and engineering environments where the need for a Background/Foreground mode of operation is compounded by the necessity for large random-access files.

The PDP-15/40 System with 24, 576 words of core memory, high-speed paper-tape facilities, and DECtape storage, also incorporates a DECdisk control and two random-access DECdisk files. The two disks, whose storage capacity of 524,288 18-bit words can be expanded to 2,097,152 words, permit high-speed overlays chaining and system and user loading.

Other hardware features of the PDP-15/40 include a memory protect system, background Teletype, and a real-time clock.

The PDP-15/40 Disk-Oriented Background/Foreground Monitor System handles all the functions of the 15/30 Background/Foreground Monitor in a high-speed disk environment.

#### 1.3 SYSTEM ORGANIZATION

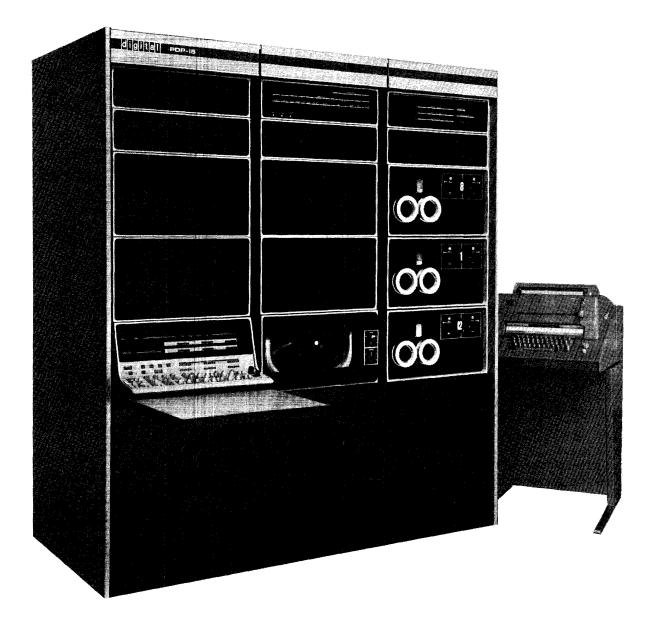

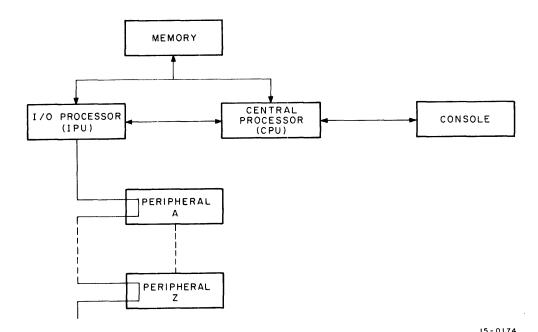

The basic PDP-15 hardware is shown in Figure 1-1. Three autonomous subsystems, central processor, memory, and I/O processor, operating together under console control define the PDP-15 System.

Figure 1-1 PDP-15 System Organization

An extensive line of peripherals including mass storage displays, data communication, and data acquisition equipment is coupled to the PDP-15 I/O processor and serviced under the supervision of the monitor systems.

#### 1.3.1 Central Processor (CPU)

The central processor functions as the main component of the computer by carrying on bidirectional communication with both the memory and the I/O processor. Provided with the capability to perform all required arithmetic and logical operations, the central processor controls and executes stored programs. It accomplishes this with an extensive complement of registers, control lines and logic gates.

#### 1.3.2 Memory

The memory, second of three autonomous subsystems, is the primary storage area for computer instructions and system data. The memory is organized into pages which are paired into memory banks. Each page has 4096, 18-bit binary words of high-speed, random-access magnetic core storage. Each bank is an asynchronous unit of 8192 words. The central processor has provisions to address up to 131,072 words of core memory. Any word in memory can be addressed by either the central processor or the I/O processor.

#### 1.3.3 I/O Processor (IPU)

The third autonomous subsystem handles peripheral data transfer. A diverse line of system peripherals available to the PDP-15 require this processor to interface three modes of input/output:

- a. Single-cycle block data transfer; blocks of data transfer at rates up to one million words per second.

- b. Multicycle block data transfer; blocks of data transfer at rates up to 250,000 words per second for input and 188,000 words per second for output.

- c. Program-controlled data transfers; single-word transfers to/from the accumulator in the central processor.

The I/O processor provides timing, control, and data lines for information transfers between memory or the central processor and the peripheral devices; it also includes provision for such options as the automatic priority interrupt system and the real-time clock.

#### 1.3.4 Console

The PDP-15 control console provides facilities for operator initiation of programs, monitoring of important CPU and IPU registers during program execution, and manual examination and modification of memory contents.

#### 1.3.5 System Peripherals

The PDP-15 System peripherals range from simple input/output Teletypes to sophisticated interactive display processors. These peripherals communicate with the PDP-15 I/O processor via one 72-wire bidirectional cable called the common I/O bus.

Figure 1-2 depicts a large system showing the CPU and IPU options and some of the PDP-15 Systems.

15-0017

Figure 1-2 System Organization

## Chapter 2 Processor Organization

#### 2.1 CENTRAL PROCESSOR DESCRIPTION

The central processor (CPU) is the main component for control and execution of stored programs. By coordinating its operation with other subsystems, it provides supervisory control over the entire PDP-15 System.

The central processor contains arithmetic and control logic hardware for a wide range of operations. These include: high-speed, fixed-point arithmetic with a hardware multiply and divide option; extensive test and branch operations implemented with special hardware registers; high-speed input/output instructions; and other arithmetic and control operations.

The PDP-15 central processor contains several major registers for processor-memory communications, a program counter, an instruction register, an accumulator, an index register, and a limit register.

The CPU performs calculations and data processing in a parallel binary mode through step-by-step execution of individual instructions. Both the instructions and the data on which the instructions operate are stored in the core memory of the PDP-15. The arithmetic and logical operations necessary for the execution of all instructions are performed by the arithmetic unit operating in conjunction with central processor registers. Figure 2-1 shows a simplified block diagram of the central processor.

#### 2.1.1 Internal Registers

#### Arithmetic Unit

The PDP-15 arithmetic unit handles all Boolean functions and contains an 18-bit, 85-ns adder. The arithmetic unit acts as the transfer path for inter-register transfers and shift operations.

#### Instruction Register (IR)

The instruction register accepts the six most-significant bits of each instruction word fetched from memory. Of these bits, the four most-significant constitute the operation code, the fifth signals when the instruction indicates indirect addressing, and the sixth indicates indexing.

Figure 2-1 Central Processor, Simplified Block Diagram

#### Accumulator (AC)

This 18-bit register retains (accumulates) the result of arithmetic or logical operations for storage between instructions.

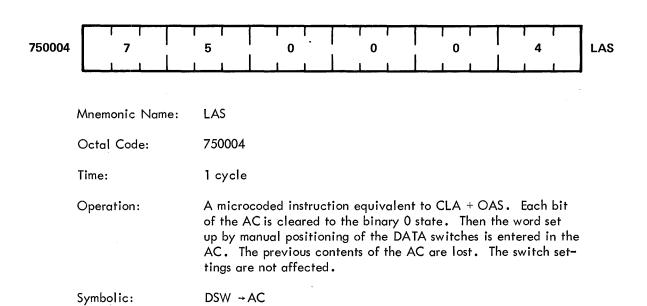

For all program-controlled input-output transfers, information is transferred between core memory and an external device through the AC. The AC can be cleared and complemented. Its contents can be rotated right or left with the Link (see below). The contents of the memory, buffered through the memory input register, can be added to the contents of the AC with the result left in the AC. The contents of both registers can be combined by the logical operations AND and exclusive OR, the result remaining in the AC. The inclusive OR can be performed between the AC and the DATA switches on the operator console (through the data switch register) and the result left in the AC.

#### Data Switch Register (DSW)

The data switch register receives and buffers an 18-bit word through the console.

#### Link (L)

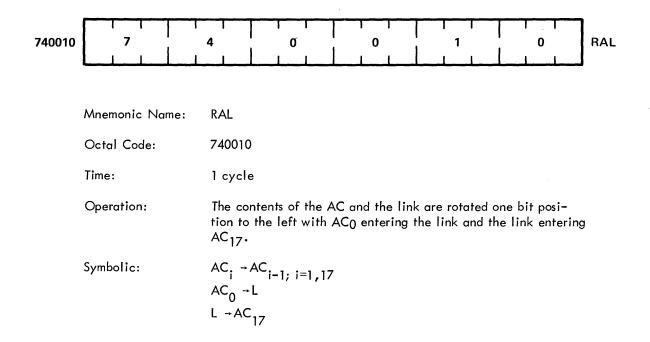

This 1-bit register is used to extend the arithmetic capability of the accumulator. In 1's complement arithmetic, the Link is an overflow indicator; in 2's complement arithmetic, it logically extends the accumulator to 19 bits and functions as a carry register. The program can check carry into the Link to simplify and speed up single- and multi-precision arithmetic routines. The Link can be cleared and complemented and its state sensed independent of the accumulator. It is included with the accumulator in rotate operations and in logical shifts.

#### Program Counter (PC)

The program counter determines the program sequence (the order in which instructions are performed). This 18-bit register contains the address of the memory location from which the next instruction is to be taken. The least-significant 15 bits are used for addressing 32,768 words of core memory. Two remaining bits provide the capability to address memory systems greater than 32,768 words.

#### Operand Address Register (OA)

The operand address register is a temporary holding register (not available to the programmer) which contains the effective address of the last (or current) memory reference operand.

#### Memory Input and Output Buffer Registers (MI and MO)

Information is read from a memory location into the memory input register and is interpreted as either an instruction, address, or a data word. Information is read from the central processor into memory through the memory output register and is interpreted as either an address or a data word. The use of two 18-bit registers for memory buffer functions allows the processor to overlap with memory cycle time to decrease execution time and to allow autonomous operation of the CPU and memory.

#### Index Register (XR)

This 18-bit register is used to perform indexing operations with no increase in instruction execution time. An indexed operation adds the contents of the index register to the address field of the instruction operand producing an effective address for the data fetch cycle. The index value is a signed 17-bit integer 131,072).

#### Limit Register (LR)

The limit register enables a program to detect loop completion. The base address of a data array is loaded into the index register and the ending address is loaded into the limit register. Within an indexing loop, add to index and skip (AXS) instruction, adds a signed value ( $\pm 256$ ) to the index register and compares the sum in the index to the contents of the limit register. If the contents of the index register are equal to or greater than those of the limit register, the next instruction is skipped.

#### 2.1.2 Control Console

The PDP-15 control console contains the keys, switches, and indicators required for operator initiation, control, and monitoring of the system. Up to twenty-four 18-bit registers can be displayed to provide the user with visual indication of most registers and buses.

Some of the features of the console are:

- a. A READ-IN switch to initiate the reading of binary paper tapes.

- b. REGISTER indicators and REGISTER DISPLAY switches for continuous monitoring of key points in the system such as the accumulator, index register, limit register, multiplier-quotient register, program counter, memory address, interrupt status, input/output bus, input output address, and I/O status.

- c. DATA switches to establish an 18-bit data or instruction word to be read into memory by the DEPOSIT switch, to be entered into the accumulator by a program instruction, or to be executed as an instruction by pressing the EXECUTE key.

- d. EXAMINE switch initiates the manual examination of the contents of any memory location specified by the ADDRESS switches.

#### 2.2 CENTRAL PROCESSOR EXPANSION OPTIONS

The following additional expansions extend the processing capabilities of PDP-15 Systems.

#### Extended Arithmetic Element (EAE)

The extended arithmetic element (standard on PDP-15/20/30/40 Systems) facilitates high-speed arithmetic operations and register manipulations. Installation of the EAE adds an 18-bit multiplierquotient register (MQ) to the system as well as a 6-bit step counter register (SC). EAE instructions can be microcoded so that several operations are performed by one instruction to simplify arithmetic programming and reduce execution time. Worst case multiplication time is 7.42 µs; division time is 7.68 µs. The EAE is optionally available for the PDP-15/10.

#### Multiplier-Quotient Register (MQ)

The multiplier-quotient register and accumulator perform as a 36-bit register during shifting, normalizing, multiplication, and division operations. The contents of the multiplier-quotient register are displayed by the REGISTER indicators on the operator's console when the REGISTER DISPLAY control is in the MQ position.

During the multiply instruction, the MQ receives the 18 least-significant bits of the double word product formed in the AC and MQ. During the divide instruction, the MQ is the least-significant 18 bits of the double word DIVIDEND formed by the AC and MQ.

#### Step Counter (SC)

The step counter is used to count the number of steps in an EAE instruction. The step counter is preloaded, except during normalize operations, with the numbers of steps specified by an instruction and is counted down as the instruction is executed. When the SC reaches zero, the EAE operation is terminated.

#### Memory Protection

The memory protection feature, standard on PDP-15/30 and 15/40 Systems, establishes a background/ foreground environment for PDP-15 processing activity by specifying the boundary between protected (lower) and unprotected (upper) regions of system core memory. Allocation of memory locations (in increments of 256 words) to the protected region is dynamic and program-controlled under the Background/Foreground Monitor. Figure 2-2 shows a PDP-15 System with the memory protect option. The protect feature increases all memory cycle times by 30 ns and write cycles in user mode by an additional 175 ns. Memory cycle times are specified in Table 3-1.

The protection option also provides a user/monitor mode of operation. When in user mode, attempted execution of any privileged instructions results in a trap to the monitor and a corresponding error message. These illegal instructions include IOT instructions, halts, chained executes, any references to the memory protect option itself, or protected memory. In monitor mode, all instructions are executable.

2-5

Figure 2-2 PDP-15 System With Memory Protect Option

The option is activated (set to user mode) with an I/O instruction, and when active, it monitors all CPU/memory instructions and addresses for illegal conditions and provides an interrupt if such conditions occur. Figure 2-3 gives more detail on the contents of the memory protect option.

#### Memory Relocate and Protect

Memory relocation is optional on all PDP-15 Systems. This feature is installed with the memory protect option on the memory bus (see Figure 2-2) and provides a relocation register and an upper boundary register to permit hardware relocation of user programs. It allows the relocated program to execute only within its specified boundaries, thereby providing protection for other programs resident in memory. Figure 2-4 shows a block diagram of the memory relocate and protect option. Note that it functions essentially the same as the basic protect hardware and gives the added capability to relocate programs in increments of 256 locations.

#### 2.3 I/O PROCESSOR ORGANIZATION

The I/O processor is an autonomous subsystem of the PDP-15 which supervises and synchronizes all data and control transfers between the devices and the PDP-15 central processor and memory.

Figure 2–3 Memory Protect Block Diagram

2-7

Figure 2-4 Memory Protect and Relocate Block Diagram

15-0178

The I/O processor contains sufficient arithmetic and control logic hardware to supervise all I/O device activity. The IPU is, however, a passive subsystem: it responds to requests for activity from the devices or the CPU rather than initiating activity.

# 2.3.1 Data Transfer Facilities

The PDP-15 I/O processor contains a number of different facilities for handling I/O activity. Each facility has been designed to serve a basic requirement of the I/O devices. All I/O device transfers can be placed into one of the following catagories. (See Figure 2-5.)

Command Transfers - Command transfers from the CPU to a device initiate or stop all device activity, and establish device operating modes, transfer directions, and other control parameters.

Status Transfers - Status transfers from a device to the CPU are usually initiated by the CPU for the purpose of monitoring the progress (or status) of a previously initiated activity.

Figure 2-5 Data Transfer Facilities

Data Transfers – Data transfers take place between a device and memory or a device and the CPU under program control, and information may be transferred in either direction. Transfers of data from a device to the CPU are initiated by the CPU. Transfers of blocks of information from a device to memory or from memory to a device are initiated by the CPU. However, the transfer of individual words in a block is usually signaled by the I/O devices.

Interrupt Requests - Interrupt requests, from the I/O device to the IPU, signal the IPU that the device needs service. The interrupt system relieves the processor of the task of continuously polling each device's status to determine its need for service.

Several capabilities in each transfer category are available from the PDP-15 I/O processor: 1) maximum flexibility is afforded the user who wishes to interface special equipment to the PDP-15 and to the programmer who writes the device handler; 2) simple, inexpensive devices such as the Teletype can be easily interfaced to the PDP-15, and require total CPU supervision; 3) complex devices (such as the LP15 line printer) that need only one instruction to initiate a complete block transfer are built to minimize the amount of CPU supervision required. The trade offs between these extremes are device cost, transfer rates, and percentage of CPU time.

Table 2-1 shows the I/O capabilities of the PDP-15 under each transfer category.

| Category          | Capability                          |

|-------------------|-------------------------------------|

| Command           | IOT command instructions            |

|                   | IOT AC transfer instructions        |

| Status            | IORS system read status instruction |

|                   | IOT skip instructions               |

|                   | IOT AC transfer instructions        |

| Data Transfers    | IOT AC transfer instructions        |

|                   | Multicycle data channel transfers   |

| s.                | Single-cycle data channel transfers |

| Special Transfers | Add to memory and increment memory  |

Table 2–1 PDP-15 I/O Capabilities

2.3.2 I/O Processor Activities

The following paragraphs describe the uses of each of the I/O processor activities. Note that some facilities have multiple uses.

IOT Commands - IOT command instructions from the CPU initiate, stop, or set the mode of the I/O device.

IOT AC Transfers - IOT AC transfer instructions from the CPU transfer up to 18 bits of data or command information from the CPU accumulator to the device's data or command registers, or command up to 18 bits of data or status information from the device's data or status registers to the CPU accumulator.

IORS Instruction - The IORS (input/output read status) instruction transfers up to 18 bits of status information (typically one bit from each device) to the CPU accumulator.

IOT Skip Instructions - IOT skip-instructions initiated by the CPU interrogate a specific flag or status bit in one of the 256 allowable devices and increments the CPU's PC (skips the next instruction) if the bit interrogated is asserted.

Multicycle Data Channel Transfer – Multicycle data channel transfers are IPU supervised transfers of data between the I/O device and sequential memory locations (in either direction). The word count and current address are kept in a pair of preassigned memory locations, and the counting and overflow detection is accomplished by the I/O processor.

Single-cycle Data Channel Transfers - Single-cycle (Direct Memory Access) transfers are device supervised transfers of information (up to 18 bits/word) between the I/O device and memory. The I/O device must contain word count and current address registers and provide overflow (job done) detection.

Program Interrupt - Program interrupt (PI) requests from the I/O devices cause the running program (at the completion of the current instruction) to transfer to a common subroutine that polls the devices to determine which device needs service. The program then transfers to the device service subroutine, and when finished handling the device, returns to the program which was interrupted by the request.

Automatic Priority Interrupt – Automatic priority interrupt (API) provide the same facility as the program interrupt except eight levels of priority are provided (4 software levels and 4 hardware levels). Instead of interrupting to a common device polling subroutine, the interrupting device provides a unique address of the subroutine call to its device handler. This eliminates the need for a device polling sequence and improves the interrupt response latency. Interrupts from different priority levels are fully nested and a debreak and restore instruction provides for orderly priority level dismissal.

Add-To-Memory - Multicycle data channel, add-to-memory facilities function in the same manner as other multicycle data channel transfers except a data word provided by the device is added to memory and the results are left in memory and transferred back to the device. Typical uses for this facility are high-speed averaging and in-core up-down counting.

Increment Memory - Data channel increment memory transfers cause the contents of a device-specified memory location to be incremented by one. A typical use for this facility is an incore histogram updated by nuclear pulse height analyzer information.

#### 2.3.3 I/O Processor Organization

The I/O processor has fully parallel arithmetic capabilities which provide autonomous I/O device supervision without interruption of central processor activities. In this manner, the I/O processor can perform an add-to-memory calculation initiated by an I/O device at the same time the CPU performs multiply or index instructions. To implement this capability, the I/O processor contains independent registers, adder, and control circuitry. Figure 2-6 is a block diagram of the I/O processor.

#### I/O Buffer

The I/O buffer is an 18-bit register which buffers input data from the I/O device.

#### I/O Adder

The I/O adder is an 18-bit adder which contain the basic arithmetic capabilities of the IPU.

#### DSR

The data storage register receives all output calculations from the I/O adder. It holds addresses or data destined for use by the memory, and it also holds data for presentation to the I/O bus lines.

The mixer logic, at the input to the I/O adder switches, appropriates data to the inputs of the adder, in order to perform the proper arithmetic operation. An example of the operation is as follows: during the data cycle of the add-to-memory data channel transfer, the contents of the memory location are

Figure 2–6 I/O Processor Block Diagram

presented to one input of the adder and the contents of the I/O buffer (which contains the devicespecified word) are placed on the other input to the adder. The 18-bit sum is strobed into the DSR which presents the data to the memory and to the I/O bus.

Control and priority logic in the IPU synchronizes the requests from CPU or devices for IPU activity, grants action to the activities in appropriate order of priority, and controls the process of the transfer.

Chapter 6 contains a more detailed description of the I/O processor and its facilities.

#### 2.4 CORE MEMORY

The magnetic core memory is the primary storage facility of the PDP-15. It provides random-access data and instruction storage for both the central processor and the I/O processor. The basic PDP-15/10 memory contains 4096 18-bit word locations. The contents of each location are available for processing in 400 ns. A parity bit can be added as an option to each word for parity checking during transfer of information into or out of core memory. If the parity option is incorporated into a PDP-15 System, all memory banks must contain that option and memory cycle time becomes 1.1 µs. The basic subsystem of memory is the memory bank; it is organized into pages, and each bank has two pages of 4096 words each for a total of 8192 words of 3D 3-wire cores. Further, every bank contains a data buffer, an address buffer, and all the necessary read/write and control circuitry to make it an autonomous unit operating on a request/grant basis with either the central processor or I/O processor. Figure 2-7 illus-trates the organization of a memory bank.

8K BANK MEMORY MODULE

Figure 2-7 Memory Organization

2-14

#### 2.4.1 Memory Data Transfer

The PDP-15 memory interacts directly with the central processor and the I/O processor through the memory bus. Data and instruction words of each bank are read from and written into individual memory locations through a buffered register, referred to as the memory buffer.

Words in a memory bank are selected according to the address in the memory address buffer. The capacity of the memory address buffer enables 8192 words to be referenced in each bank.

The memory address buffer receives the memory address from the central processor or I/O processor. The address provides the coordinates for locating a word in a memory bank.

Decoding of the memory address to select a particular word location containing 18 bits is performed by the memory selection logic. Bit 5 of the memory cell address selects the page of the location, and the remaining bits select the X and Y coordinates of the location.

Bits 1 to 4 of the memory bus select lines are used to select which bank of memory the word is in. Up to four banks can normally be added to the PDP-15, but a special provision to expand memory up to 16 banks can be accommodated by the 18-bit address register in the CPU.

#### 2.4.2 Parity

The memory parity option provides core planes that have 19 bits for each word and parity checking/ generating control logic. When the parity option is present, the accuracy of transfers to and from memory is verified through parity checking. A parity bit is added to each word stored in memory, so that the total number of 1 bits in the word, including the parity bit, is odd. For example, if the 18-bit word to be stored in memory contains an even number of 1s, the parity bit is automatically made a 1, and is stored with the word. When the word is later read from memory, the computed parity bit is calculated on the basis of the content of the 18-bit word. The calculated and actual parity bits are then compared, if they do not agree, the memory parity error alarm is initiated, causing a program interrupt or automatic priority interrupt request, or a halt.

All 18 bits and the accompanying parity-check bit (when present) are transferred in parallel (simultaneously) between the core array and the memory buffer. The memory buffer is connected to the memory bus, and therefore, to the rest of the PDP-15 System. This is also an 18-bit parallel transfer.

#### 2.4.3 Memory Modularity

The PDP-15/10 System contains one page of 4096 memory words; however, additional modules (pages) can be added to the system. The basic system can accommodate up to 32,768 core memory words (eight 4K pages) in the basic 19-in. cabinet. Expansion beyond 32,768 words requires the addition of another cabinet to the system configuration. Memory communicates with the central processor and the I/O processor on the bidirectional memory bus (see Figure 2-8).

#### UP TO FOUR BLOCKS PER PDP-15 SYSTEM 32K WORD BLOCK **8K BANK 8K BANK 8K BANK 8K BANK** 4K 4 K 4K 4K 4 K 4K 4K 4K PAGE PAGE PAGE PAGE PAGE PAGE PAGE PAGE MEMORY BUS 15-0183

Figure 2-8 Physical Memory Organization

#### 2.4.4 Memory Addressing

The PDP-15 memory system is broken down into four basic memory entities. The maximum configuration system contains 131,072 words of 18 or 19 bits and is subdivided into four blocks of 32K words. Each block contains up to four banks of 8K words, which contain two pages of 4K words. Figure 2-9 shows breakdown of locations, pages, banks, and blocks within the PDP-15 System.

Note that all valid addresses are positive addresses, i.e., negative addresses with bit 0 set (400000-777777) are illegal and cause the machine to wait indefinitely for memory response. Such addresses can be generated by the CPU or IPU under certain circumstances, but are trapped if the memory protect option is present.

#### 2.4.5 Memory Port Switch

The memory port switch allows both the central processor and I/O processor to share core memory. In the event that both request a memory cycle simultaneously, the I/O processor is serviced first and the central processor must wait. However, if only one processor is using memory, both can process at the same time. For example, the central processor can be executing an EAE instruction, while the I/O processor transfers data out of memory to a DECdisk.

Figure 2-9 Memory Addressing

#### 2.4.6 MX15-A Memory Bus Multiplexer

The MX15-A Memory Bus Multiplexer is a multiport memory option. It provides three ports for multiprocessor configurations, direct memory access (DMA) facilities, and the KP15-A Dual Bus Processor option. The MX15-A is a prerequisite for systems with greater than 32K of core memory. A PDP-15 System can accommodate up to four MX15-A Memory Bus Multiplexers. Each port has its own set of address switches that can be preset in any 8K increment. This feature enables one processor to address an 8K bank of core memory as its lowest bank (bank 0). A second processor can access the same bank of core memory through the MX15-A as its highest bank. The MX15-A introduces a delay for each memory cycle. Refer to the MX15-A Maintenance Manual for specific delay times introduced by the MX15-A.

# Chapter 3 Instruction Formats

#### 3.1 GENERAL

The PDP-15 instruction set is divided into "memory reference instructions," which address core memory, and "augmented instructions," which do not address core memory. Memory reference instructions address, either directly or indirectly, core memory locations for the purpose of retrieving, entering, or modifying the contents. The augmented instructions are used to execute a certain action or actions. This type of instruction is subdivided into four groups: operate instructions (link and accumulator operations including rotates, skips, clears, and complements); IOT instructions (input/output transfer of data, command and status between the central processor, and peripheral devices); EAE (extended arithmetic element, optional hardware multiply, divide, shift, and normalize); and index instructions (accumulator, limit register, and index register transfers, clears, additions, and skips).

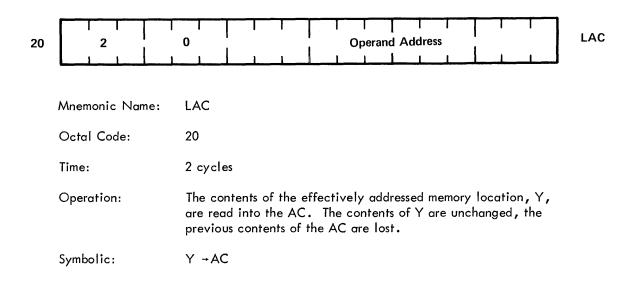

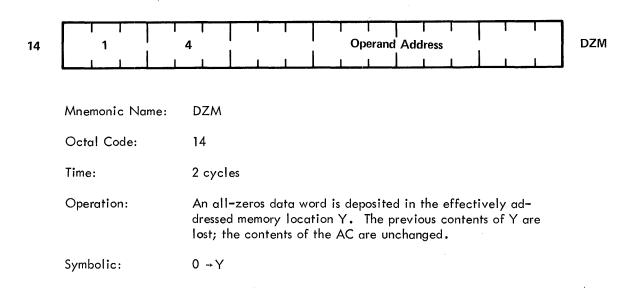

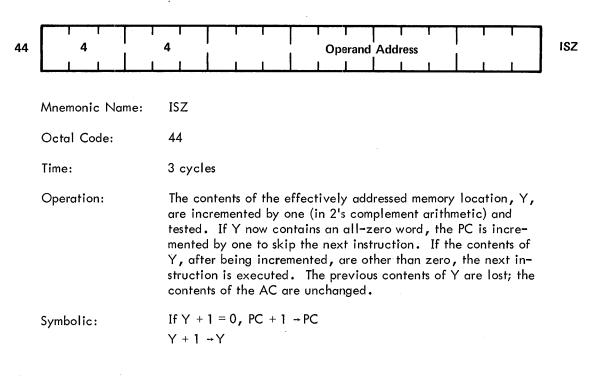

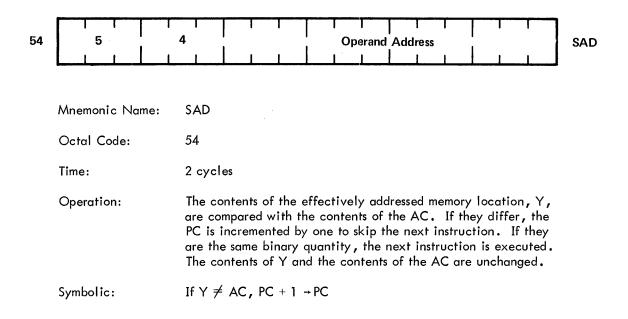

#### 3.2 MEMORY REFERENCE INSTRUCTION FORMAT

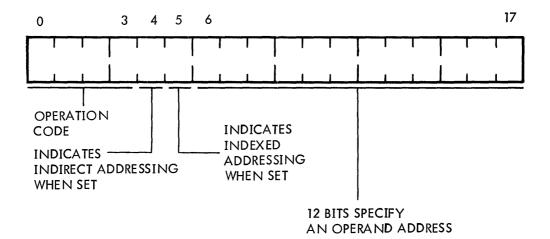

The memory reference instruction word consists of an operation code, an indirect address bit, an index bit, and an operand address (see Figure 3-1). The operation code, bits 0 through 3, specifies one of the 13 PDP-15 memory reference instructions. When the PDP-15 is in "page mode," the indirect bit indicates whether the 12-bit (bits 6-17) operand address is to be directly or indirectly (bit 4=1) addressed and the index bit determines whether or not the index register should be added to the operand address. In "bank mode," the indirect bit indicates whether the 13-bit (bits 5-17) operand address is

\*USED AS A THIRTEENTH ADDRESS BIT IN BANK MODE

15-0188

to be used as the direct address or the indirect address (bit 4=1). The operand address is used in generating the effective address or the address in memory which will be referenced. Chapter 4 is a detailed description of addressing.

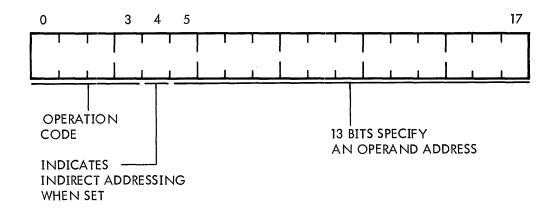

#### 3.3 AUGMENTED INSTRUCTION FORMAT

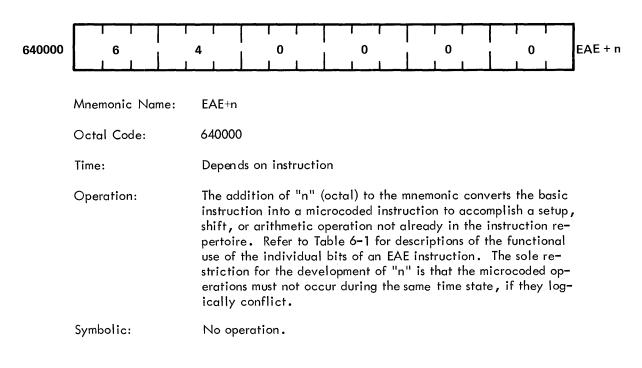

The augmented instruction word (see Figure 3-2) consists of an operation code and an instruction code. The operation code designates whether the instruction is an extended arithmetic element instruction,  $64_8$  (bits 0-3), an Input/Output transfer instruction,  $70_8$  (bits 0-5), an Index instruction,  $72_8$  (bits 0-5) or an operate instruction  $74_8$  (bits 0-3). The instruction code designates which action is to be taken by the augmented instruction. An important and useful feature of the PDP-15 augmented instruction is its microprogramming capability. Multiple instruction codes having the same operation code can be combined to form one instruction word. Execution of all microprogrammed functions occurs during the time allocated to the type of instruction (operate instructions require one machine cycle, IOTs require two, three, or four cycles, EAE requires one or three, plus a variable time interval to complete their function, and index instructions require two cycles). Thus, microprogramming decreases program running time, lessens the number of instruction words required, and simplifies programming efforts.

Figure 3-2 Augmented Instruction Format

#### 3.4 TIMING

The amount of time required to perform each instruction is expressed in the number of machine cycles. The length of each machine cycle for various configurations is given in Table 3-1.

Instructions which indirectly address memory require one extra machine cycle in order to fetch and compute the indirect address. Only one level of indirect addressing is possible on the PDP-15.

Instructions which use the auto increment locations indirectly require two extra machine cycles; one for the increment of the location, and one for the indirect address.

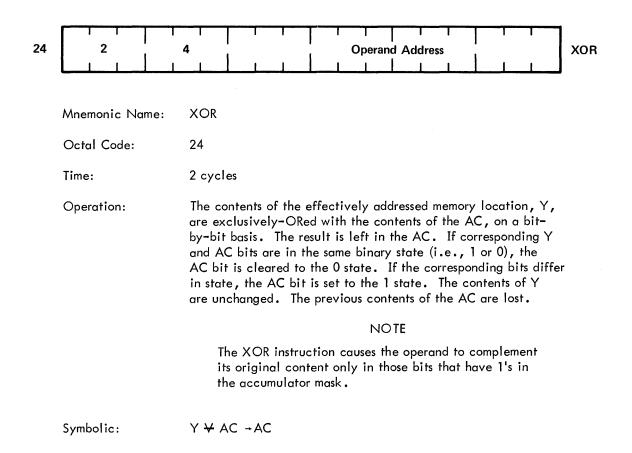

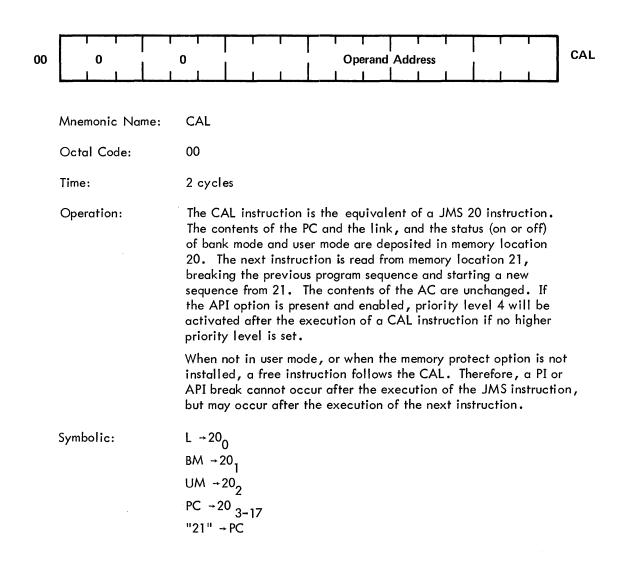

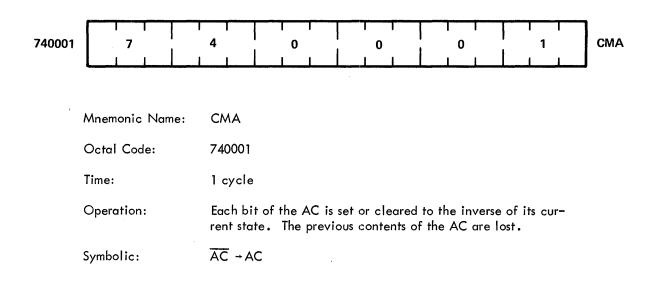

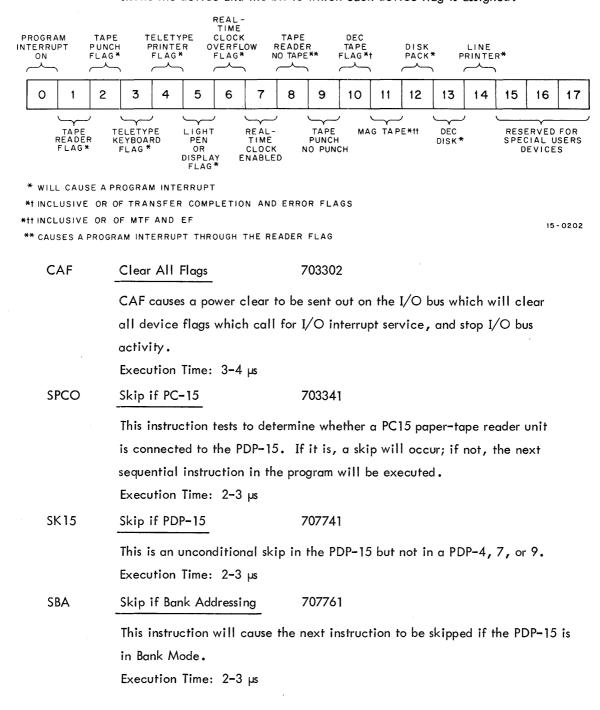

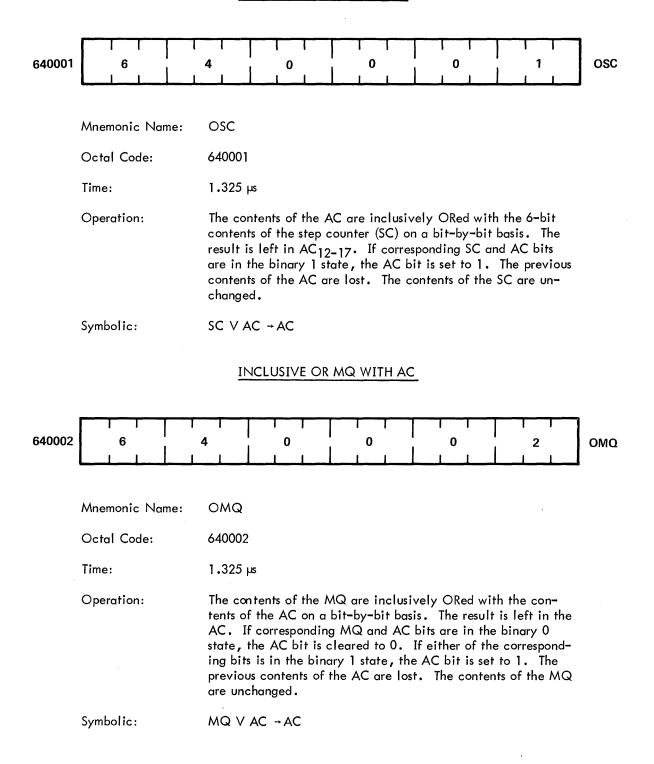

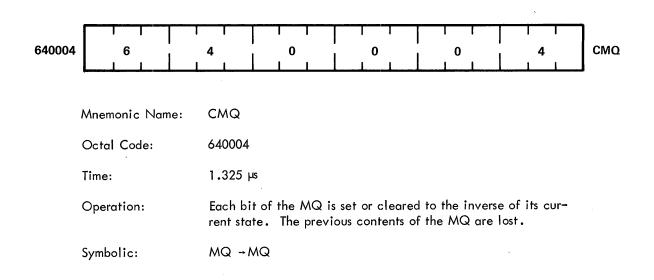

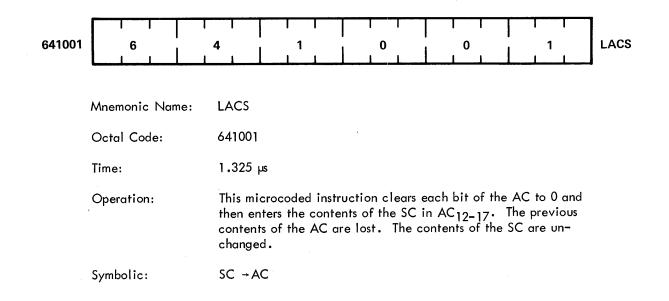

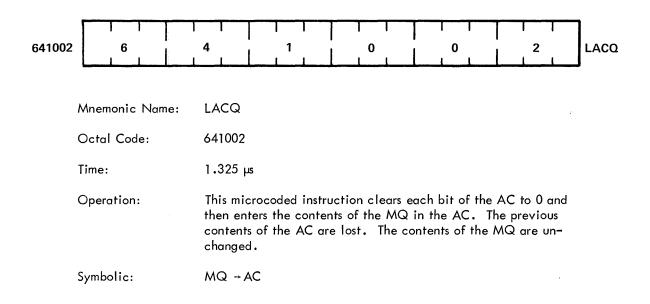

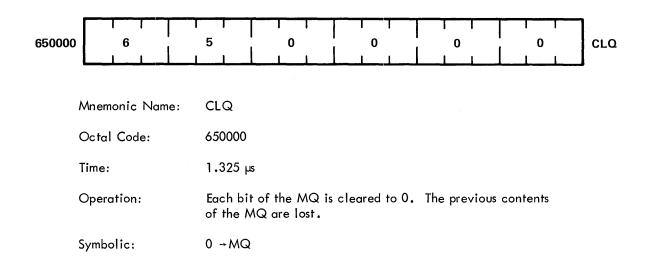

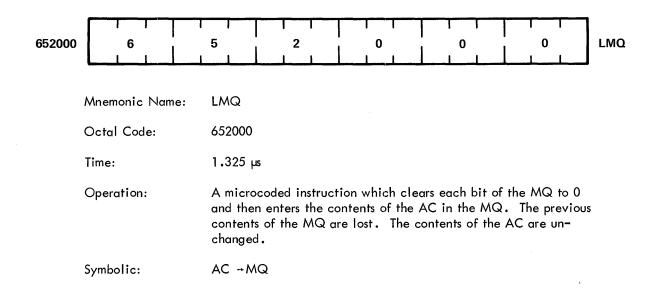

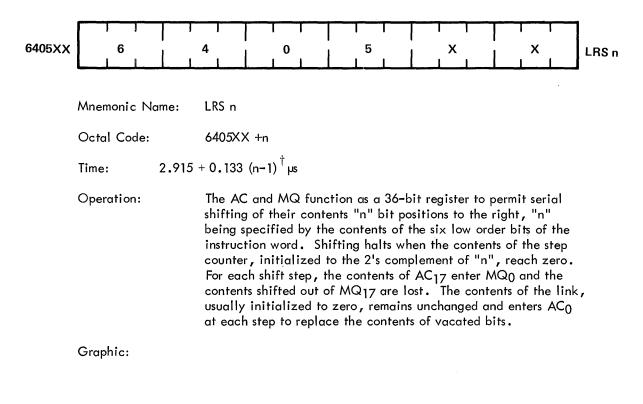

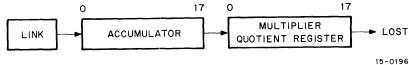

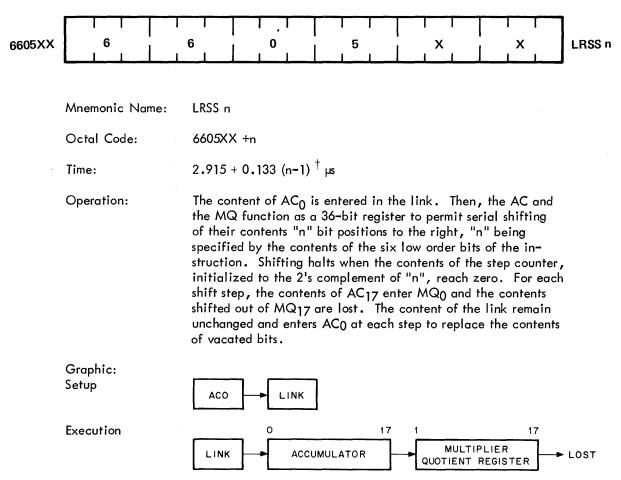

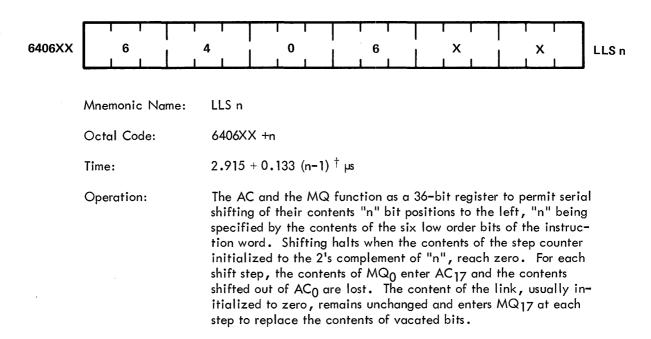

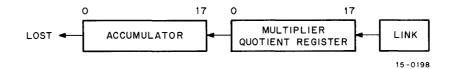

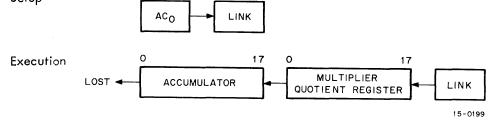

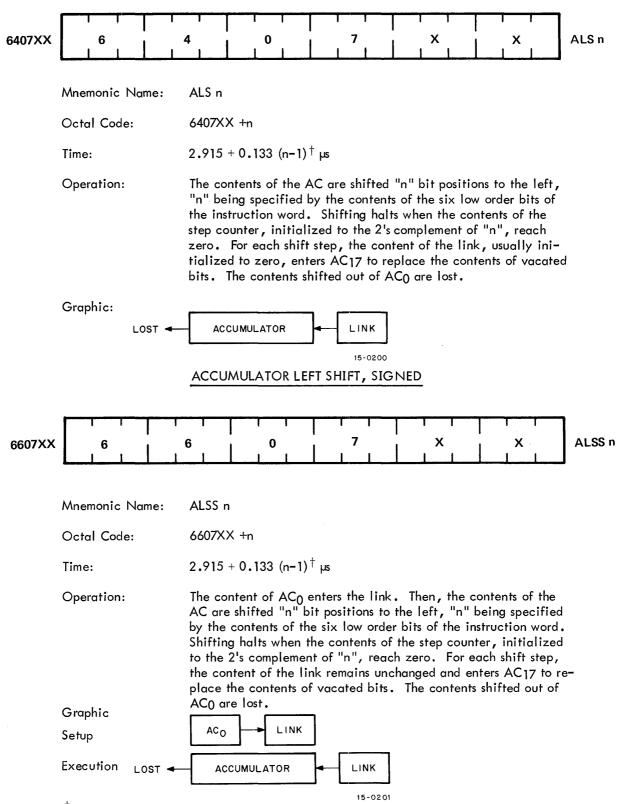

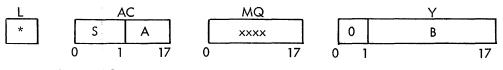

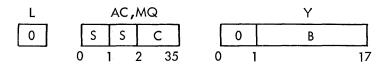

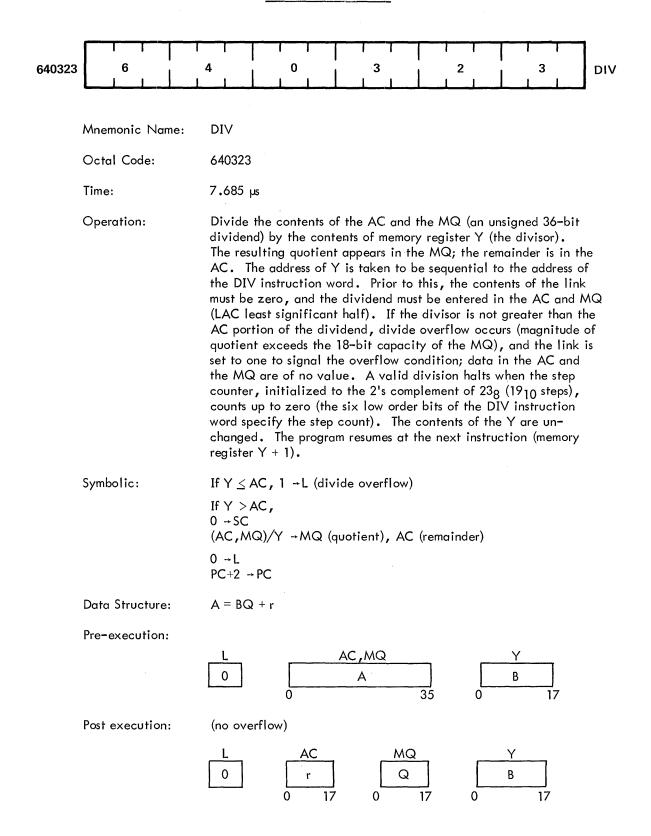

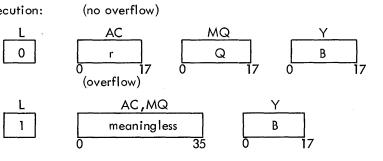

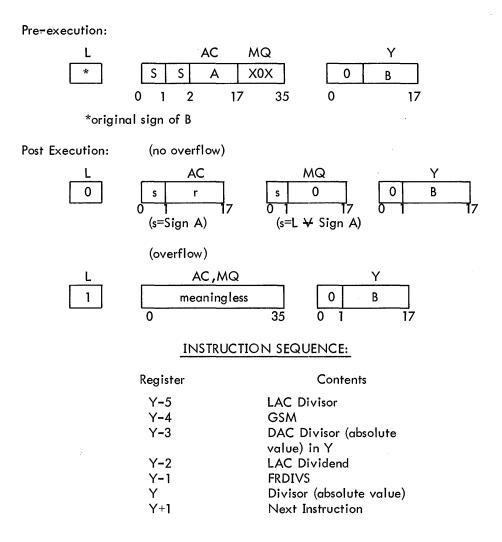

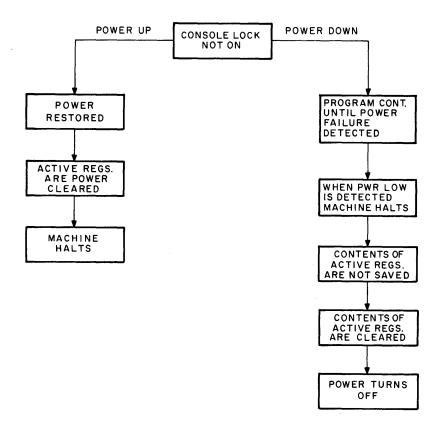

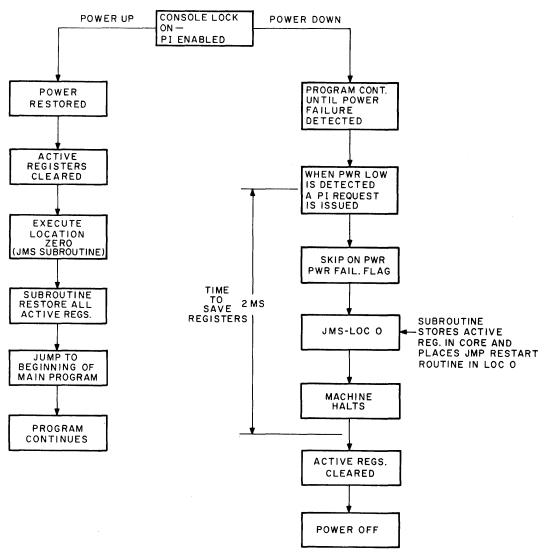

|                                                                                |      | Not In U | ser Mod | e       |      | In User | Mode |         |