I-L85(A)

## LINC – 8 PROGRAMMING MANUAL

DIGITAL EQUIPMENT CORPORATION . MAYNARD, MASSACHUSETTS

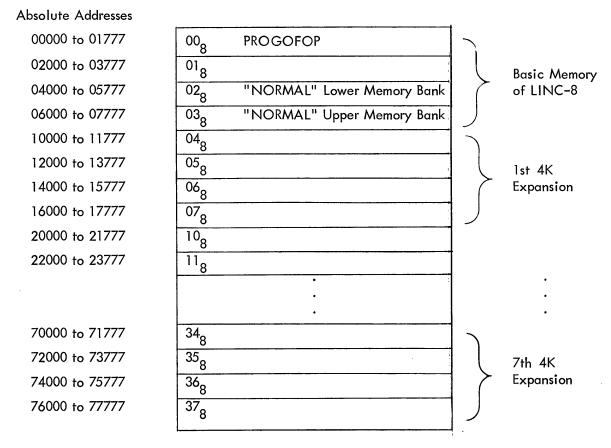

1st Printing October 1966 2nd Printing May 1968 3rd Printing February 1969 4th Printing July 1969

## Copyright (C) 1966, 1968, 1969 by Digital Equipment Corporation

Instruction times, operating speeds and the like are included in this manual for reference only; they are not to be taken as specifications.

The following are registered trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC PDP FLIP CHIP FOCAL DIGITAL COMPUTER LAB

#### PREFACE

This document is derived from several works developed by persons outside of DEC. "Programming the LINC" <u>LINC V16 Section 2 Programming and Use</u>, April 1965, by Mary Allen Wilkes and Wesley A. Clark, Washington University, St. Louis, Mo., was used, with some changes felt appropriate, for the discussion of the instruction set of the LINC portion of the LINC-8. "A LINC Utility System" <u>Technical Report 1</u>, March 19, 1965, written by M.D. McDonald, S.R. Davisson, and J.R. Cox, Jr., Biomedical Computer Laboratory, Washington University, St., Louis, Mo., was used to provide a basis for the discussion of the LAP4 and GUIDE systems. To the above individuals, as well as others at the Computer Research Laboratory of Washington University, the National Institutes of Health, the National Aeronautics and Space Administration, and individual LINC users, we are greatly indebted.

## CONTENTS

|        |                                                    | Page |

|--------|----------------------------------------------------|------|

| 1      |                                                    | 1    |

| 1-1    | Manual Organization                                | 1    |

| 1-2    | Number Systems                                     | 2    |

| 2      | INSTRUCTIONS                                       | 2    |

| 2-1    | Simple Instructions                                | 2    |

| 2-2    | Shifting                                           | 2    |

| 2-3    | LINC Memory and Memory Reference Instructions      | 8    |

| 2-3.1  | The Store-Clear Instruction (4000 + X)             | 9    |

| 2-3.2  | The ADD Instruction and Binary Addition (2000 + X) | 9    |

| 2-3.3  | Instruction Location Register                      | 10   |

| 2-3.4  | The Jump Instruction (6000 + X)                    | 11   |

| 2-4    | Address Modification and Program Loops             | 12   |

| 2-5    | Index Class Instructions I                         | 18   |

| 2-5.1  | Indirect Addressing                                | 18   |

| 2-5.2  | Index Registers and Indexing                       | 20   |

| 2-5.3  | Logic Instructions                                 | 22   |

| 2-6    | Special Index Register Instructions                | 23   |

| 2-6.1  | The Index and Skip Instruction                     | 23   |

| 2-6.2  | The SET Instruction                                | 25   |

| 2-7    | Index Class Instructions II                        | 28   |

| 2-7.1  | Double Register Forms                              | 28   |

| 2-7.2  | Multiple Length Arithmetic                         | 31   |

| 2-7.3  | Multiplication                                     | 36   |

| 2-8    | Half–Word Class Instructions                       | 41   |

| 2-9    | The Keyboard Instruction                           | 45   |

| 2-10   | The LINC Scopes and the Display Instructions       | 46   |

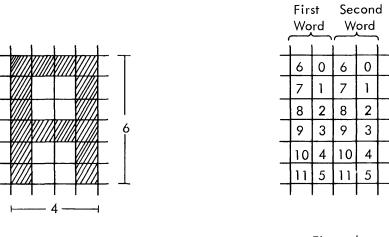

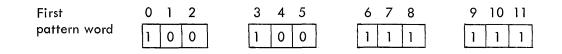

| 2-10.1 | Character Display                                  | 49   |

| 2-11   | Analog Input and the Sample Instruction            | 55   |

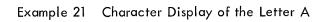

| 2-12   | The Skip Class Instructions                        | 59   |

| 2-13   | Subroutine Techniques                              | 62   |

| 2-13.1 | Main Program                                       | 63   |

| 2.13.2 | Subroutine                                         | 64   |

## CONTENTS (continued)

|          |                                                         | Page |

|----------|---------------------------------------------------------|------|

| 2-14     | Processor Intercommunication                            | 64   |

| 2-14.1   | Control Transfer between Processors                     | 64   |

| 2-14.2   | Example of Use of the OPR 13 Instruction (LINC Program) | 70   |

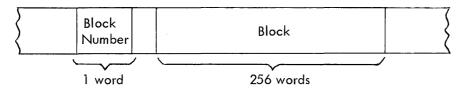

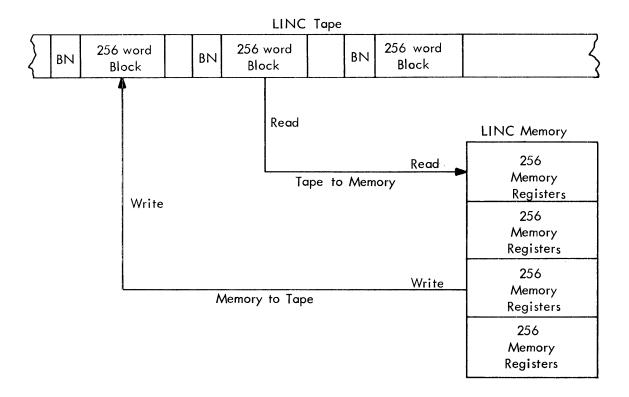

| 2-15     | Magnetic Tape Instructions                              | 70   |

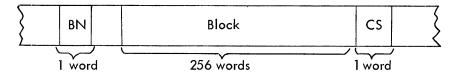

| 2-15.1   | Block Transfers and Checking                            | 72   |

| 2-15.2   | Group Transfers                                         | 80   |

| 2-15.3   | Tape Motion and the Move toward Block Instruction       | 82   |

| 2-15.4   | Tape Format                                             | 85   |

| 2-15.5   | Tape Motion Timing                                      | 88   |

| 3        | GUIDE                                                   | 91   |

| 3-1      | General                                                 | 91   |

| 3-2      | General Operating Procedure                             | 91   |

| 3–3      | Basic System Commands                                   | 91   |

| 3-4      | Use of Basic Commands                                   | 92   |

| 3-5      | Loading a User's Program into Memory                    | 94   |

| 4        | LAP4                                                    | 95   |

| 4-1      | General                                                 | 95   |

| 4-2      | General Operating Procedure                             | 95   |

| 4-3      | Basic System (Meta) Commands                            | 95   |

| 4-4      | Use of Basic (Meta) Commands                            | 97   |

| 4-5      | LAP4 Language                                           | 102  |

| Appendix |                                                         |      |

| 1 | GLOSSARY                    | 107  |

|---|-----------------------------|------|

| 2 | CHARTS                      | 115  |

| 3 | EXTENDED MEMORY PROGRAMMING | 125  |

| 4 | INSTRUCTIONS                | 1.29 |

## Index

| INDEX OF PROGRAMMING EXAMPLES     |     |  |  |  |  |  |

|-----------------------------------|-----|--|--|--|--|--|

| PAGE INDEX OF LINC-8 INSTRUCTIONS | 146 |  |  |  |  |  |

## CHAPTER 1 INTRODUCTION

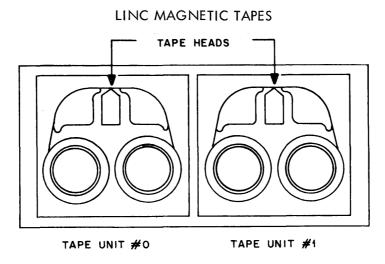

The Digital Equipment Corporation LINC-8 system is comprised of two subsystems: a standard Programmed Data Processor-8 (PDP-8); and the LINC subsystem consisting of a central processing portion, a display scope, and a dual tape transport. The two subsystems are interconnected by a special interface section which mediates the interchange of data and control, and both share a dual console. The LINC-8 is designed to operate in one of two modes. In the first mode, it operates as a standard basic PDP-8 computer system. In the second, it operates essentially as a LINC having certain special in/out and speed characteristics. Despite these differences and improvements, the LINC subsystem will often be referred to simply as the LINC throughout the manual.

In the LINC mode, the LINC section is controlled by an ordinary LINC program held in the upper half of the PDP-8 memory (which is arranged to correspond exactly to the standard LINC memory of 2048 words). The PDP-8 memory can be expanded to 32,768 words. The LINC section is designed to call and carry out all instructions of the LINC program except MTP, OPR, and a new instruction called EXC. Instructions of this excepted class, called the execute class, are carried out by interpretive routines held in the lower half of the PDP-8 memory, which also holds programs for the interpretive program is named PROGOFOP (PROGram OF OPeration), and is automatically read into the PDP-8 memory from magnetic tape by a wired-in LOAD mode initiated at the console.

#### 1-1 MANUAL ORGANIZATION

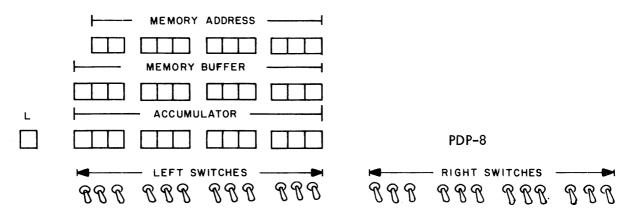

This manual presents programming information relating to the LINC subsystem of the LINC-8 computer. The registers, switches, and indicators referenced in this document are associated with the LINC section and are located on the left half of the LINC-8 dual console. The RIGHT SWITCHES used in the LINC mode of operation also serve as the switch register for PDP-8 operation. Programming information for the PDP-8 subsystem of the LINC-8 can be obtained from the PDP-8 Users Handbook, F-85.

The first two chapters of this document acquaint the reader with number systems, instructions, and programming examples. Chapters 3 and 4 discuss the LINC Utility System (GUIDE and LAP4) which provides the user with information necessary to use these basic system programs for compiling and manipulating LINC-8 programs.

Like most digital computers, the LINC-8 operates by manipulating binary numbers held in various registers under the control of a program of instructions which are themselves coded as binary numbers and stored in other registers. LINC-8 instructions generally fall into types or classes, the instructions of a class having certain similarities. In this description, however, instructions are introduced as they are

1

relevant to the discussion. Reference to chart I appendix 2 is therefore recommended when class characteristics are described. Furthermore, not all LINC-8 instructions are described here in detail; therefore this document should be read in conjunction with the LINC-8 order code summary in appendix 2.

#### 1–2 NUMBER SYSTEMS

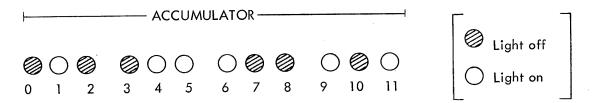

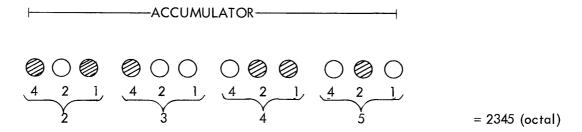

The best way to begin studying number systems is to consider only a few of the registers and switches which are shown on the LINC-8 control console: the ACCUMULATOR (ACC) which is a register of twelve lights; the LINK bit (L); the LEFT and RIGHT SWITCHES, which are rows of twelve toggle switches each; and one lever switch labeled DO. The number systems and operation of several of the instructions can be understood in terms of these few elements.

The elements (bits) of each register or row of toggle switches are to be thought of as numbered from left to right starting with 0. This will serve to identify the elements and to relate them to the numerical value of the binary integer held in the register. C(ACC) denotes the contents of the accumulator register, etc. If the accumulator is illuminated thus

then the binary number stored in the accumulator is

C(ACC) = 010 011 100 101 (binary)

which has the decimal value

$$C(ACC) = 2^{10} + 2^7 + 2^6 + 2^5 + 2^2 + 2^0$$

= 1024 + 128 + 64 + 32 + 4 + 1

= 1253 (decimal)

This can also be considered as an octal number by considering each group of three bits in turn. In this example, grouping and factoring proceed as follows:

$$C(ACC) = (2^{10}) + (2^{7}+2^{6}) + (2^{5}) + (2^{2}+2^{0})$$

= (2^{1}) \cdot 2^{9} + (2^{1}+2^{0}) \cdot 2^{6} + (2^{2}) \cdot 2^{3} + (2^{2}+2^{0}) \cdot 2^{0}

= (2) \cdot 8^{3} + (3) \cdot 8^{2} + (4) \cdot 8^{1} + (5) \cdot 8^{0}

= 2 3 4 5

= 2345 (octal)

To put this more simply, each octal digit can be treated as an independent 3-bit binary number whose value (0, 1, ..., 7) can be obtained from the weights  $2^2$ ,  $2^1$ , and  $2^0$ :

This ease of representation (the eight possible combinations within a group are easily perceived and remembered) is the principal reason for using octal numbers; the octal system can be viewed simply as a convenient notational system for representing binary numbers. Of course, octal numbers can also be manipulated arithmetically.

Translation from one system to the other is easily accomplished in either direction. Here are some examples:

| 1   | 0            | 7            | 3            | 0   | 2            | 6            | 5            | 7   | 2            | 4            | 6            | (octal)  |

|-----|--------------|--------------|--------------|-----|--------------|--------------|--------------|-----|--------------|--------------|--------------|----------|

| 1   | 1            | 1            | ſ            | 1   | 1            | Î            | T            | 1   | $\uparrow$   | ſ            | 1            |          |

| L   | $\downarrow$ | $\downarrow$ | $\checkmark$ | ł   | $\checkmark$ | $\checkmark$ | $\checkmark$ | Ţ   | $\checkmark$ | $\checkmark$ | $\downarrow$ |          |

| 001 | 0Ó0          | 111          | 011          | 000 | 010          | 110          | 101          | 111 | 010          | 100          | 110          | (binary) |

Sometimes it is useful to view the contents of a register as a signed number. One of the bits must be reserved for the sign of the number. The leftmost bit is therefore identified as the sign bit (0 for +, 1 for -). To change the sign of a binary number, complement the number (replace all 0's by 1's and vice versa). Examples:

| 000 | 000 | 000 | 011 = +3                   |                                                                                       |

|-----|-----|-----|----------------------------|---------------------------------------------------------------------------------------|

| 111 | 111 | 111 | 100 = -3                   |                                                                                       |

|     |     |     | 111 = +3777<br>000 = -3777 | The largest positive and negative octal integers in the 12–bit signed–number system . |

The pair of binary numbers 101111110011 and 010000001100 (5763<sub>8</sub> and 2014<sub>8</sub>) are complements of each other, and denote the complement of the number N by  $\overline{N}$ . Note that the sum of each binary digit and its complement is the number 1, and that the sum of each octal digit and its complement is the number 7. Note also that there are two representations of 0:

- $000 \quad 000 \quad 000 \quad 000 = +0$

- $|11| \quad |11| \quad |11| \quad |11| = -0$

Note finally that the sum of any binary number and its complement is always -0 in this system.

# CHAPTER 2

#### 2–1 SIMPLE INSTRUCTIONS

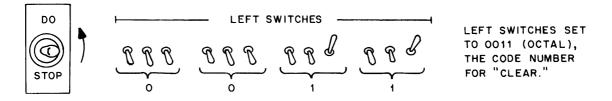

LINC-8 instructions themselves are encoded as binary numbers and held in various registers. The simplest of these instructions, namely those which operate only on the accumulator, are described first with reference to the LEFT SWITCHES.

Raising the DO lever (DO means "do toggle instruction") causes the LINC to execute the instruction whose binary code number is held in the LEFT SWITCHES. The LINC then halts. For example, if the LEFT SWITCHES are set to the code number for the instruction CLEAR, which happens to be  $0011_8$ , and the DO lever is then momentarily raised, the ACCUMULATOR lights all go out as does the LINK bit light, so that C(ACC) = 0, and C(L) = 0. In setting a switch, up corresponds to 1.

Briefly: If C(LEFT SWITCHES) =  $0011_8$ , DO has the effect  $0 \rightarrow C(ACC)$  and  $0 \rightarrow C(L)$ . (Read "0 replaces the contents of the accumulator," etc.).

Clear (or CLR) is an instruction of the class known as miscellaneous instructions. A second miscellaneous class instruction, COM (complement), with the code number  $0017_8$ , directs the LINC to complement the contents of the accumulator and therefore has the effect  $\overline{C(ACC)} \rightarrow C(ACC)$ . (Read: "the complement of the contents of the accumulator replaces the contents of the accumulator.")

Two other instructions of this class transfer information between the accumulator and the relay register. The relay register, displayed on the control console, operates six relays which can be used to control or run external equipment. An instruction with the code  $0014_8$ , called ATR (accumulator to relay), directs the LINC to transfer the contents of the right half of the accumulator, i.e., the rightmost six bits, into the relay register. The accumulator itself is not changed when the instruction is executed. Another instruction, called RTA (relay to accumulator),  $0015_8$ , causes the LINC to clear the accumulator and then transfer the contents of the right half of the accumulator. In this case the relay register is not changed and the left half of the accumulator remains cleared (i.e., contains 0's).

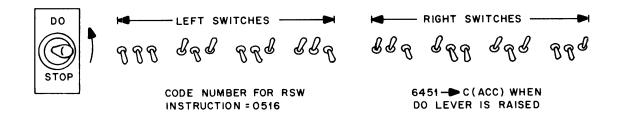

Another instruction called RSW (right switches), 0516<sub>8</sub>, directs the LINC to copy the contents of the RIGHT SWITCHES into the accumulator. By setting the LEFT SWITCHES to 0516<sub>8</sub>, the RIGHT SWITCHES to whatever value wanted in the accumulator, and then momentarily raising the DO lever,

the operator can change the contents of the accumulator to any desired new value. The drawing shows how the switches should be set to put the number  $6451_8$  into the accumulator:

#### 2-2 SHIFTING

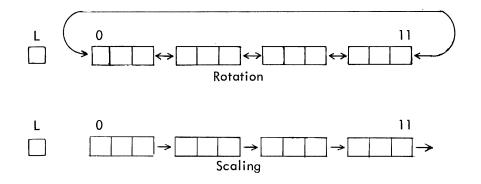

After a number has been put into the accumulator it can be repositioned (shifted) to the right or left. There are two ways of shifting: rotation, in which the end-elements of the accumulator are connected together to form a closed ring, and scaling, in which the end-elements are not so connected.

Examples of shifts of one place:

|        | Effect of rotating<br>right 1 place | Effect of scaling<br>right 1 place      |

|--------|-------------------------------------|-----------------------------------------|

| Before | 000 000 011 001                     | 000 000 011 001 = +25 (decimal)         |

| After  | 100 000 001 100                     | 000 000 001 100 = +12                   |

| Before | 111 111 100 110                     | 111 111 100 110 = <b>-</b> 25 (decimal) |

| After  | 011 111 110 011                     | 111 111 110 011 = -12                   |

Note that, in scaling, bits are lost to the right, which amounts to an error of rounding off; the original sign is preserved in the sign bit and replicated in the bit positions to the right of the sign bit. This has the effect of reducing the size of the number by powers of two (analogous to moving the decimal point in decimal calculations).

#### ROR, ROL, SCR

The LINC has three instructions, called the shift class instructions, which shift the contents of the accumulator: rotate right, rotate left, and scale right. Unlike the simple instructions considered so far, the code number for a shift class instruction includes a variable element which specifies the number of places to shift. For example, write ROL n (rotate the contents of the accumulator n places to the left), where n can be any number from 0-17<sub>8</sub>.

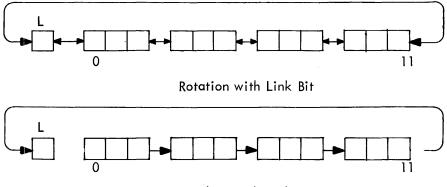

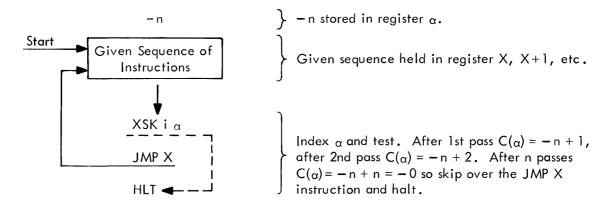

As a further variation of the shift class instructions, the link bit can be adjoined to the accumulator during rotation to form a 13-bit ring as shown below, or to bit 11 of the accumulator during scaling to preserve the low order bit scaled out of the accumulator:

Scaling with Link Bit

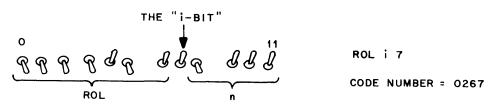

The code number of a shift class instruction, e.g., rotate left, therefore includes the number of places to shift and an indication of whether or not to include the link bit. Use the full expression ROL in, which has the octal coding:

ROL in 0240 + 20i + n

$$(n = 0, 1, ..., 17)$$

$i = 0: ACC only$

$i = 1: link \leftrightarrow ACC$

so that, for example, rotate ACC left 3 places has the code 0243, and rotate ACC with link left 7 places has the code 0267. Note the correspondence between the code terms and bit positions of the binary-coded instruction as it appears, for example, in the LEFT SWITCHES:

Similar coding is used with ROR in (rotate right), 300 + 20i + n, and SCR in (scale right), 340 + 20i + n.

#### 2-3 LINC MEMORY AND MEMORY REFERENCE INSTRUCTIONS

Before proceeding to other instructions, it is necessary to introduce the LINC memory. This memory is to be regarded as a set of  $1024_{10}$  registers<sup>†</sup> each holding 12-bit binary numbers in the manner of the accumulator. These memory registers are numbered 0, 1, ...,  $1023_{10}$ , or 0, 1, ...,  $1777_8$ , and reference is made to "the contents of register 3," C(3), "the contents of register X," C(X), etc., referring to "3" and "X" as memory addresses.

The memory actually consists of a remotely-located array of magnetic storage elements with related electronics, but for introductory purposes view it in terms of two registers of lights, namely the memory address register and the memory buffer register:

By using these two registers in conjunction with the LEFT SWITCHES it is possible to find out what values the memory registers contain. For example, to find the contents of register 3, set the RIGHT SWITCHES to memory address 0003 and then operate the key labeled EXAM. As 0003 appears in the memory address register, the contents of register 3 appear in the memory buffer register. By setting the RIGHT SWITCHES to a memory address and pushing EXAM, the contents of any register in the LINC memory may be examined.

The contents of any selected memory register may be changed by using both the LEFT and RIGHT SWITCHES and the key marked FILL. For example, to make the memory register whose address is 700 contain -1 (i.e., 7776<sub>8</sub>) set memory address 0700 into the RIGHT SWITCHES. Set the LEFT SWITCHES to 7776 and operate the FILL key. A 0700 appears in the memory address register and 7776 appears in the memory buffer register, indicating that the contents of register 700 are now 7776. Whatever value register 700 may have contained before FILL was pushed is lost, and the new value takes its place. In this way any register in the LINC memory can be filled with a new number.

None of the LINC instructions make explicit reference to the memory address register or memory buffer register; rather, in referring to memory register X, an instruction may direct the LINC implicitly to put the address X into the memory address register and the contents of register X, C(X), into the memory buffer register.

<sup>&</sup>lt;sup>†</sup>See appendix 3 for the discussion of extended memory programming.

#### 2-3.1 The Store-Clear Instruction (4000 + X)

Now it is possible to describe the first of the memory reference instructions, STC X (store-clear X), which has the code number 4000 + X, where  $0 \le X \le 1777_8$ . (From now on only octal numbers will be used for addresses.) Execution of STC X has two effects: 1) the contents of the accumulator are copied into memory register X,  $C(ACC) \rightarrow C(X)$ , and 2) the accumulator is then cleared,  $0 \rightarrow C(ACC)$ . (The link bit is not cleared.) Thus, for example, if C(ACC) = 0503 and C(671) = 2345, and the code number for STC 671, i.e., 4671, is set into the LEFT SWITCHES, raising the DO level puts 0 into the accumulator and 0503 into register 671. The original contents of register 671 are lost.

It will be clear that the memory can be filled with new numbers at any time either by using the FILL key and the switches, or by loading the accumulator from the RIGHT SWITCHES with the RSW instruction and the DO lever and then storing the accumulator contents with the STC X instruction and the DO lever.

#### 2-3.2 The ADD Instruction and Binary Addition (2000 + X)

STC is one of three full-address class instructions. Another instruction in this class, ADD X, has the code number 2000 + X where  $0 \le X \le 1777$ . Execution of ADD X has the effect of adding the contents of memory register X to the contents of the accumulator, i.e.,  $C(X) + C(ACC) \rightarrow C(ACC)$ . If the accumulator is first cleared, ADD X has the effect of merely copying into the accumulator the contents of memory register X, i.e.,  $C(X) \rightarrow C(ACC)$ . In any case, the contents of memory register X are unaffected by the instruction.

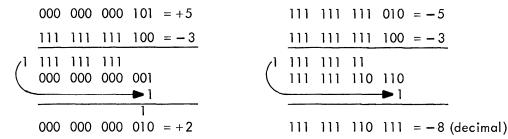

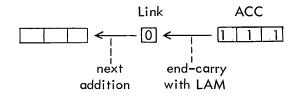

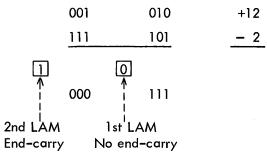

The addition itself takes place in the binary system, \* within the limitations of the 12-bit registers. The basic rules for binary addition are simple: 0 + 0 = 0; 1 + 0 = 1; 1 + 1 = 10 (i.e., zero, with one to carry). A carry arising from the leftmost column (end-carry) is brought around and added into the rightmost column (end-around carry). Some examples (begin at the rightmost column as in decimal addition):

<sup>\*</sup>See Volume 16, Section 1, "An Introduction to Binary Numbers and Binary Arithmetic," Irving H. Thomae.

#### HLT

The reader should try some examples of his own, and verify the fact that adding a number to itself with end-around carry is equivalent to rotating left one place. With signed-integer interpretation, some other examples are:

It can be seen that subtraction of the number N is accomplished by addition of the complement of N,  $\overline{N}$ . Of course, if either the sum or difference is too large for the accumulator to hold, the result of the addition may not be quite the desired number. For example, adding 1 to the largest positive integer in this system (+3777<sub>8</sub>) results in the largest negative integer (-3777<sub>8</sub>). This is sometimes called overflowing the capacity of the accumulator.

#### 2-3.3 Instruction Location Register

It is clear that the code numbers of a series of different instructions can be stored in consecutive memory registers. The LINC-8 is designed to execute this stored program of instructions by fetching and carrying out each instruction in sequence, using a special 10-bit register called the instruction location register (P), to hold the address of the next instruction to be executed. Using the FILL key and the LEFT and RIGHT SWITCHES already discussed, can, for example, put into memory registers 20-24 the code numbers for a series of instructions which divide by 8 the number held in memory register 30 and store the result in memory register 31:

| Memory Address Memory Buffer |                | Buffer | Effect                                              |

|------------------------------|----------------|--------|-----------------------------------------------------|

| Start<br>20                  | CLR            | 0011   | Clear the accumulator.                              |

| 21                           | ADD 30         | 2030   | Add the contents of register 30 to the accumulator. |

| 22                           | SCR 3          | 0343   | Scale C(ACC) right 3 places to divide by 8.         |

| 23                           | STC 31         | 4031   | Store in register 31.                               |

| 24                           | HLT            | 0000   | Halt the computer.                                  |

| :                            |                | •      |                                                     |

| 30                           | N              | N      | Number to be divided by 8.                          |

| 31                           | L <b>⊳</b> N∕8 | N/8    | Result.                                             |

Example 1 Simple Sequence of Instructions

JMP

Use the FILL key and the LEFT and RIGHT SWITCHES to put the code numbers for the instructions into memory registers 20-24 and the number to be divided into register 30. Operating the console key labeled START 20 directs the LINC to begin executing instructions at memory register 20. That is, the value 20 replaces the contents of the instruction location register. As each instruction of the stored program is executed, the instruction location register is increased by 1,  $C(P) + 1 \rightarrow C(P)$ . When the instruction location register contains 24, the computer encounters the instruction HLT, code 0000, which halts the machine. To run the program again, merely operate the START 20 key. (The code numbers for the instructions stay in memory registers 20-24 unless they are deliberately changed.)

#### 2-3.4 The Jump Instruction (6000 + X)

The last full-address instruction, JMP X, code 6000 + X, has the effect of setting the instruction location register to the value X;  $X \rightarrow C(P)$ . That is, the LINC, instead of increasing the contents of the instruction location register by one and executing the next instruction in sequence, is directed by the JMP instruction to get its next instruction from memory register X. In the above example having a JUMP to 20 instruction, code 6020, in memory register 24 (in place of HLT) would cause the computer to repeat the program endlessly. If the program were started with the START 20 switch, the instruction location register (P) would hold the succession of values: 20, 21, 22, 23, 24, 20, 21, etc. (Later instructions will be introduced which increase C(P) by extra amounts, causing it to skip.)

JMP X has one further effect: if JMP 20, 6020, is held in memory register 24, then its execution causes the code for JMP 25 to replace the contents of register 0; i.e.,  $6025 \rightarrow C(0)$ . More generally, if JMP X is in any memory register p,  $0 \le p \le 1777$ , then its execution causes JMP p+1  $\rightarrow C(0)$ .

| Memory<br>Address         | Memory                          | Buffer                                | Effect                                                                       |

|---------------------------|---------------------------------|---------------------------------------|------------------------------------------------------------------------------|

| 0<br>:<br>→ p<br>p+1<br>X | JMP p+1<br>:<br>JMP X<br>:<br>: | 6000 + p+1<br>:<br>6000 + X<br>:<br>- | $X \rightarrow C(P)$ , and JMP p+1 $\rightarrow C(0)$ .<br>Next instruction. |

This JMP p+1 code replaces the contents of register 0 every time a JMP X instruction is executed unless X = 0, in which case the contents of 0 are unchanged. Use of memory register 0 in this way is relevant to a programming technique involving subroutines which is described later<sup>†</sup>. <sup>†</sup>See appendix 3 for a discussion of JMP X when using extended memory.

The following programming example illustrates many of the features described so far. It finds one-fourth of the difference between two numbers  $N_1$  and  $N_2$ , which are located in registers 201 and 202, and leaves the result in register 203 and in the accumulator. After filling consecutive memory registers 175-210 with the appropriate code and data numbers, the program must be started at memory register 175. Since there is no START 175 key on the console, this is done by setting the RIGHT SWITCHES to 0175 and operating the console key labeled START RS (start RIGHT SWITCHES).

| Memory Address | Memory Buffer   |                | Effect                                            |

|----------------|-----------------|----------------|---------------------------------------------------|

| Start<br>→ 175 | CLR             | 0011           | 0→ C(ACC).                                        |

| 176            | ADD 201         | 2201           | $N_1 \rightarrow C(ACC)$ .                        |

| 177            | сом             | 0017           | Forms - N <sub>1</sub> .                          |

| 200            | JMP 204         | 6204           | Jumps around data; 204→ C (P), and JMP 201→ C(0). |

| 201            | N               | N              |                                                   |

| 202            | N <sub>2</sub>  | N <sub>2</sub> | > Data and result.                                |

| 203            | $(N_2 - N_1)/4$ |                |                                                   |

| 204            | →ADD 202        | 2202           | $(N_2 - N_1) \rightarrow C(ACC).$                 |

| 205            | SCR 2           | 0342           | Divides by 4.                                     |

| 206            | STC 203         | 4203           | Stores result in 203; C(ACC)→C(203);<br>0→C(ACC). |

| 207            | ADD 203         | 2203           | Recovers result in ACC.                           |

| 210            | HLT             | 0000           | Halts the LINC.                                   |

Example 2 Simple Sequence Using the Jump Instruction

In executing this program, the instruction location register holds the succession of numbers: 175, 176, 177, 200, 204, 205, 206, 207, 210.

### 2-4 ADDRESS MODIFICATION AND PROGRAM LOOPS

Frequently a program of instructions must deal with a large set of numbers rather than just one or or two. For example, suppose one wishes to add 100<sub>8</sub> numbers and that the numbers are stored in the memory in registers 1000–1077. The sum is to go into memory register 1100. It is possible, of course, to write out all the instructions necessary to do this,

| Memory<br>Address | Memory Buffer |      | Effect                                       |

|-------------------|---------------|------|----------------------------------------------|

| → 20              | CLR           | 0011 | $0 \rightarrow C(ACC); 0 \rightarrow C(L)$ . |

| 21                | ADD 1000      | 3000 | Add 1st number.                              |

| 22                | ADD 1001      | 3001 | Add 2nd number.                              |

| 23                | ADD 1002      | 3002 | Add 3rd number.                              |

| 24                | ADD 1003      | 3003 | Add 4th number.                              |

|                   | etc.          | etc. | etc.                                         |

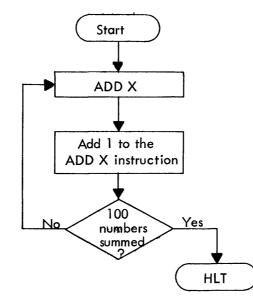

but it is easy to see that the program would be more than 100<sub>8</sub> registers long. A more complex, but considerably shorter, program can be written using a programming technique known as address modification. Instead of writing 100<sub>8</sub> ADD X instructions, write only one ADD X instruction, which is repeated 100<sub>8</sub> times, modifying the X part of the ADD X instruction each time it is repeated. In this case the computer first executes an ADD 1000 instruction; the program then adds one to the ADD instruction itself and restores it, so that it is now ADD 1001. The program then jumps back to the location containing the ADD instruction and the computer repeats the entire process, this time executing an ADD 1001 instruction. In short, the program is written so that it changes its own instructions while running.

The process might be diagrammed:

This technique introduces the additional problem of deciding when all 100 numbers have been summed and halting the computer. In this context a new instruction AZE (accumulator zero), code 0450, should be introduced. This is one of a class of instructions known as skip instructions; it directs the LINC to skip the instruction in the next memory register when  $C(ACC) = \pm 0 (0000_8 \text{ or } 7777_8)_*$  If  $C(ACC) \neq 0$ , the computer does not skip. For example, if C(ACC) = 7777, and one writes:

| Memory Address | Memory Buffer |           |  |

|----------------|---------------|-----------|--|

| → p<br>p+1     | AZE           | 0450<br>- |  |

| p+2            |               | -         |  |

the computer takes the next instruction from p+2. That is, when the AZE instruction in register p is executed, p+2 replaces the contents of the instruction location register, and the computer skips the instruction at p+1. If  $C(ACC) \neq 0$ , then p+1  $\rightarrow C(P)$  and the computer executes the next instruction in sequence as usual.

The following example sums the numbers in memory registers 1000-1077 and puts the sum into memory register 1100, using address modification and the AZE instruction to decide when to halt the computer. (Square brackets indicate registers whose contents change while the program is running.)

| Memory Address                  | Memory Bu       | ffer             | Effect                                                                       |

|---------------------------------|-----------------|------------------|------------------------------------------------------------------------------|

| 10<br>11                        | ADD 1000<br>1   | 3000<br>0001     | Constants used by program.                                                   |

| 12                              | -(ADD 1100)     | 4677 <i>.</i>    |                                                                              |

| $\xrightarrow{\text{Start}} 20$ | :<br>CLR        | :<br>0011        |                                                                              |

| 21                              | ADD 10          | 2010             | Code for ADD 1000 $\rightarrow$ C(25). 0 $\rightarrow$ C(ACC).               |

| 22                              | STC 25          | 4025             |                                                                              |

| 23<br>24                        | STC 1100        | 5100<br>0011     | $0 \rightarrow C(1100)$ , for accumulating sum.                              |

| 24                              | [ ADD X]        | [2000+X]         | Clear ACC and add C(X) to C(ACC).                                            |

| 26                              | ADD 1100        | 3100             | Sum so far + C(ACC) $\rightarrow$ C(ACC).                                    |

| 27                              | STC 1100        | 5100             | Sum so far $\rightarrow C(1100)$ .                                           |

| 30                              | ADD 25          | 2025             | ADD X instruction in register $25 \rightarrow C(ACC)$ .                      |

| 31                              | ADD 11          | 2011             | Add 1 to C(ACC) and replace in register 25.                                  |

| 32                              | STC <u>2</u> 5  | 4025             | J                                                                            |

| 33                              | ADD 25          | 2025             | C(25) + C(12) $C(ACC)$ . If $C(25) = ADD 1100$ ,                             |

| 34                              | ADD 12          | 2012             | then $C(ACC) = 7777$ .                                                       |

| 35<br>36                        | AZE<br>JMP 24   | 0450<br>6024     | Skip to register 37 if C(ACC) = 7777.<br>If not, return and add next number. |

| 37                              | HLT             | 0000             | When $C(ACC) = 7777$ , all numbers have been                                 |

| :                               | :               | •                | summed. Halt the computer.                                                   |

| 1000                            | N1              | N,               |                                                                              |

| 1001                            | N <sub>2</sub>  | N <sub>2</sub>   |                                                                              |

| •                               | -               |                  | Numbers to be summed.                                                        |

| 1076                            | N <sub>77</sub> | N <sub>77</sub>  |                                                                              |

| 1077                            | N100            | N <sub>100</sub> |                                                                              |

| 1100                            | [ Sum ]         | [ Sum ]          |                                                                              |

Example 3 Summing a Set of Numbers Using Address Modification

.

The instructions at locations 20-22 initially set the contents of memory register 25 to the code for ADD 1000. At the end of the program, register 25 will contain 3100, the code for ADD 1100. Adding (in registers 33 and 34) C(25) to C(12), which contains the complement of the code for ADD 1100, results in the sum 7777 only when the program has finished summing all  $100_8$  numbers. This repeating sequence of instructions is called a loop, and instructions such as AZE can be used to control the number of times a loop is repeated. In this example the instructions in locations 24-36 will be executed  $100_8$ times before the computer halts.

The following program scans the contents of memory registers 400 through 450 looking for registers which do not contain zero. Any non-zero entry is moved to a new table beginning at location 500; this has the effect of packing the numbers so that no registers in the new table contain zero. When the program halts, the accumulator contains the number of non-zero entries.

| Memory Address | Memory Bu                | uffer    | Effect                                                                           |

|----------------|--------------------------|----------|----------------------------------------------------------------------------------|

| 4              | ADD 400                  | 2400     |                                                                                  |

| 5              | STC 500                  | 4500     |                                                                                  |

| 6              | 1                        | 0001     | Constants used by the program.                                                   |

| 7              | -(ADD 451)               | 5326     |                                                                                  |

| 10             | -(STC 500)               | 3277     |                                                                                  |

| Start          |                          | •        |                                                                                  |

| → 100          | CLR                      | 0011     |                                                                                  |

| 101            | ADD 4                    | 2004     | Code for ADD 400 $\rightarrow$ C(106).                                           |

| 102            | STC 106                  | 4106     | J                                                                                |

| 103            | ADD 5                    | 2005     |                                                                                  |

| 104            | STC 112                  | 4112     | Code for STC 500 $\rightarrow$ C(112).                                           |

| 105            | ightarrow CLR            | 0011     |                                                                                  |

| 106            | [ADD 400]                | [2000+X] | $C(X) \rightarrow C(ACC)$ .                                                      |

| 107            | <u>AZE</u>               | 0450     | If C(ACC) = 0, skip to location 111.                                             |

| 110            | JMP 112                  | 6112     | $C(ACC) \neq 0$ , therefore JMP to location 112.                                 |

| 111            | JMP 116 4                | 6116     | C(ACC) = 0, therefore JMP to location 116.                                       |

| 112            | └ <b>&gt;</b> [ STC 500] | [4000+X] | Store non-zero entry in new table.                                               |

| 113            | ADD 6                    | 2006     |                                                                                  |

| 114            | ADD 112                  | 2112     | Add 1 to the STC instruction in register 112.                                    |

| 115            | STC 112                  | 4112     |                                                                                  |

| 116            | ADD 6                    | 2006     |                                                                                  |

| 117            | ADD 106                  | 2106     | Add 1 to the ADD instruction in register 106.                                    |

| 120            | STC 106                  | 4106     |                                                                                  |

| 121            | ADD 106                  | 2106     | $C(106) + C(7) \rightarrow C(ACC)$ . If $C(106) = ADD 451$ ,                     |

| 122            | ADD 7                    | 2007     | then C(ACC) = 7777.                                                              |

| 123            | <u>AZE</u>               | 0450     | If C(ACC) = 7777, skip to location 125.                                          |

| 124            | JMP 105                  | 6105     | If not, return to examine next number.                                           |

| 125            | ADD 1124                 | 2112     | If C(ACC) = 7777, then number of non-zero<br>entries →C(ACC) and computer halts. |

| 126            | ADD 10                   | 2010     |                                                                                  |

| 127            | HLT                      | 0000     |                                                                                  |

Example 4 Packing a Set of Numbers

ADA

At the end of the program, register 106 contains the code for ADD 451, and all numbers in the table have been examined. If, say, 6 entries were found to be non-zero, registers 500-505 will contain the non-zero entries, and register 112 will contain the code for STC 506. Therefore by adding C(112) to the complement of the code for STC 500 (in registers 125-126 above), the accumulator is left containing 6, the number of non-zero entries.

#### 2-5 INDEX CLASS INSTRUCTIONS I

#### 2-5.1 Indirect Addressing

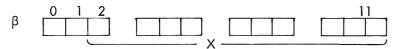

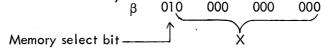

The largest class of LINC instructions, index class, addresses the memory in a somewhat involved manner. The instructions ADD X, STC X, and JMP X are called full address instructions because the 10-bit address X,  $0 \le X \le 1777$ , can address directly any register in the  $2000_8$  register memory. The index class instructions, however, have only 4 bits reserved for an address, and can therefore address only memory registers  $1_8-17_8$ . The instruction ADA i  $\beta$  (add to accumulator),  $1100_8 + 20i + \beta$ , is typical of the index class:

$$i_{\beta} = 0 \text{ or } 1$$

$$ADA \ i_{\beta} = 1100 + 20i + \beta$$

$$i_{\beta} = 17$$

Memory register  $\beta$  should be thought of as containing a memory address, X, in the rightmost 10 bits,

and  $X(\beta)$ , as meaning the right 10-bit address part of register  $\beta$ . The leftmost bit can have any value, and, for the present, bit 1 must be 0. In addressing memory register  $\beta$ , an index class instruction tells the computer where to find the memory address to be used in executing the instruction. This is called indirect addressing.

For example, to add the value 35 to the contents of the accumulator, with 35 held in memory register 270, use the ADA instruction in the following manner:

LDA, STA

| Memory<br>Address | Memo      | ry Buffer              | Effect                                  |

|-------------------|-----------|------------------------|-----------------------------------------|

| β<br>0270         | →0270<br> | 0270<br>:<br>0035<br>: | Address of register contain–<br>ing 35. |

| → p<br>:          | ADÀB      | 1100 + β<br>:          | C(270) + C(ACC)→C(ACC).                 |

Note that the ADA instruction does not tell the computer directly where to find the number 35; it tells the computer instead where to find the address of the memory register which contains 35. By using memory registers 1–17 in this way, the index class instructions can refer to any register in the memory.

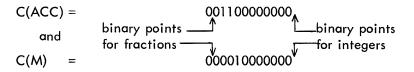

Two other index class instructions, LDA i  $\beta$  (load accumulator), and STA i  $\beta$  (store accumulator), are used in the following program which adds the contents of memory register 100 to the contents of register 101 and stores the result in 102. The LDA i  $\beta$  instruction, code 100 + 20i +  $\beta$ , clears the accumulator and copies into it the contents of the specified memory register. STA i  $\beta$ , code 1040 + 20i +  $\beta$ , stores the contents of the accumulator in the specified memory register; it does not, however, clear the accumulator. Addition with ADA uses 12-bit end-around carry arithmetic.

| Memory<br>Address                                                             | Memory                                                                                                                                                                                               | y Buffer                                                              | Effect                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10<br>11<br>12<br><u>Start</u> 30<br>31<br>32<br>33<br>:<br>100<br>101<br>102 | $ \begin{array}{c}     X_{1} \\     X_{2} \\     X_{3} \\     \vdots \\     LDA 10 \\     ADA 11 \\     STA 12 \\     HLT \\     \vdots \\     N_{1} \\     N_{2} \\     [N_{1}+N_{2}] \end{array} $ | 0100<br>0101<br>0102<br>1010<br>1111<br>1052<br>0000<br>-<br>-<br>[-] | Address of N <sub>1</sub> .<br>Address of N <sub>2</sub> .<br>Address of (N <sub>1</sub> +N <sub>2</sub> ).<br>N <sub>1</sub> , i.e., C(100), $\rightarrow$ C(ACC).<br>N <sub>2</sub> , i.e., C(101), + C(ACC) $\rightarrow$ C(ACC).<br>N <sub>1</sub> +N <sub>2</sub> $\rightarrow$ C(102). |

Example 5 Indirect Addressing

## SAE 2-5.2 Index Registers and Indexing

When i is used with an index class instruction, that is, when i = 1, the computer is directed to add 1 to the X part of memory register  $\beta$  before it is used to address the memory. This process is called indexing, and registers 1–17 are frequently referred to as index registers. In the example below, -6 is loaded into the accumulator after index register  $\beta$  is indexed from 1432 to 1433 by the LDA i  $\beta$  instruction.

| Memory<br>Address                | Memory Buffer                       |                                         | Effect                                                                                                |

|----------------------------------|-------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------|

| β<br><br>→ p<br><br>1432<br>1433 | [X]<br>:<br>LDA i β<br>:<br>-<br>-6 | [1432]<br>:<br>1020+β<br>:<br>-<br>7771 | Address minus 1 of register<br>containing 7771.<br>X + 1, i.e., 1433, → C(β), and<br>C(1433) →C(ACC). |

When the LDA i  $\beta$  instruction is executed, the value  $X(\beta) + 1$  replaces the address part of register  $\beta$  (the leftmost 2 bits of register  $\beta$  are unaffected). This new value, 1433, is now used to address the memory. Note that if the LDA instruction at p were repeated, it would deal with the contents of register 1434, then 1435, etc. Utility of index registers in scanning tables of numbers should be obvious.

Indexing involves only 10-bit numbers, and does not involve end-around carry. Therefore the address following 1777 is 0000. (The same kind of indexing takes place in the instruction location register, which counts from 1777 to 0000.)

The following example using indexing introduces another index class instruction, SAE i  $\beta$  (skip if accumulator equals), code 1440 + 20i +  $\beta$ . This instruction causes the LINC to skip one register in the sequence of programmed instructions when the contents of the accumulator exactly match the contents of the specified memory register. If there is no match, the computer goes to the next instruction in sequence as usual. The program example clears (stores 0000 in) the set of memory registers 1400-1777; the SAE instruction is used to decide whether the last 0000 has been stored.

| Memory Address | Memory Bu | Jffer     | Effect                                                                                           |

|----------------|-----------|-----------|--------------------------------------------------------------------------------------------------|

| 3              | [X]       | [1377]    | Initial address minus 1 for the STA instruction.                                                 |

| 4              | 356<br>:  | 0356<br>: | Address of test number.                                                                          |

| Start<br>→ 350 | ⊢→CLR     | 0011      | Clear the accumulator.                                                                           |

| 351            | STA i 3   | 1063      | Index the contents of register 3; store $C(ACC)$ in the memory register whose address = $X(3)$ . |

| 352            | ADD 3     | 2003      | $C(3) \rightarrow C(ACC)$ .                                                                      |

| 353            | SAE 4     | 1444      | Skip to 0355 if C(ACC) = C(356).                                                                 |

| 354            | JMP 350   | 6350      | If not, return to store 0000 in next register.                                                   |

| 355            | HLT←      | 0000      | Halt the computer.                                                                               |

| 356            | 1777      | 1777      |                                                                                                  |

Example 6 Indexing to Clear a Set of Registers

When the program halts at register 355, register 3 will contain 1777. The SAE instruction is used here (as the AZE instruction was used in earlier examples) to decide when to stop the computer. The instructions in registers 350-354, the loop, are executed 400<sub>8</sub> times before the program halts. A 0 is first stored in register 1400, next in 1401, etc.

Another program scans the memory to see if a particular number, Q, appears in any memory register 0-1777. Q is to be set in the RIGHT SWITCHES, and the address of any register containing Q is to be left in the accumulator.

| Memory Address    | Memory B  | Buffer | Effect                                                                            |

|-------------------|-----------|--------|-----------------------------------------------------------------------------------|

| 17                | [X]       | [-]    | Address of register whose contents are to be com-<br>pared with RIGHT SWITCHES.   |

| Start<br>────> 20 | RSW       | 0516   | $C(RS) \rightarrow C(ACC)$ .                                                      |

| 21                | →SAE i 17 | 1477   | Index register 17, and compare C(ACC) with C(X).                                  |

| 22                | JMP 21    | 6021   | If not equal, return for next test.                                               |

| 23                | CLR←      | 0011   |                                                                                   |

| 24                | ADD 17    | 2017   | If equal, clear ACC, copy address of register<br>containing Q into ACC, and halt. |

| 25                | HLT       | 0000   |                                                                                   |

ADM, BCL, BSE, BCO

If no memory register 0-1777 contains the number Q, the program will run endlessly. The location of the first register to be tested depends on the initial contents of index register 17.

An index class instruction, ADM i  $\beta$  (add to memory), code 1140 + 20i +  $\beta$ , adds the contents of the specified memory register to C(ACC), using 12-bit end-around carry arithmetic (as ADD or ADA). The result is left, however, not only in the accumulator but in the specified memory register as well. The bit clear instruction, BCL i  $\beta$ , code 1540 + 20i +  $\beta$ , is one of three index class instructions which performs a so-called "logical" operation. BCL is used to clear selected bits of the accumulator. For every bit of the specified memory register which contains 1, the corresponding bit of the accumulator is set to 0.

In the following program two sets of numbers are summed term by term. The first set of numbers, each 6 bits long, is in registers 500–577, bits 6 through 11; bits 0–5 contain unwanted information. The second set of numbers is in registers 600–677, and the sums replace the contents of registers 600–677.

| Memory Address | Memory                | Buffer    | Effect                                                                   |

|----------------|-----------------------|-----------|--------------------------------------------------------------------------|

| 3              | [X <sub>1</sub> ]     | [0477]    | Initial address minus 1 of first set.                                    |

| 4              | 0410                  | 0410      | Address of BCL pattern.                                                  |

| 5              | [X <sub>2</sub> ]     | [ 0577 ]  | Initial address minus 1 of second set.                                   |

| 6              | 0411                  | 0411      | Address of test number for halting.                                      |

| Start<br>→ 400 | :<br>_→LDA i 3        | :<br>1023 | Index X(3) and load number from first set into AC.                       |

| 401            | BCL 4                 | 1544      | Clear the left 6 bits of the ACC.                                        |

| 402            | ADM i 5               | 1165      | Index X(5). Add number from second set to C(ACC), and replace in memory. |

| 403            | CLR                   | 0011      |                                                                          |

| 404            | ADD 3                 | 2003      | Check to see if finished.                                                |

| 405            | SAE 6                 | 1446      |                                                                          |

| 406            | JMP 400               | 6400      | C(3) ≠ C(411), i.e., ≠ 0577.                                             |

| 407            | HLT <del>&lt;</del> l | 0000      | C(3) = 0577; halt the program.                                           |

| 410            | 7700                  | 7700      | BCL pattern for clearing left half of ACC.                               |

| 411            | 0577                  | 0577      | Test number for halting.                                                 |

Example 8 Summing Sets of Numbers Term by Term

#### 2-5.3 Logic Instructions

The three logic instructions, BCL i  $\beta$ , BSE i  $\beta$ , and BCO i  $\beta$ , are best understood by studying the following examples. These instructions affect only the accumulator; the memory register M containing the bit pattern is unchanged.

BCLiβ code:  $1540 + 20i + \beta$ bit clear Clear corresponding bits of the accumulator: If C(M) = 010 101 010 101 and C(ACC) = 111 111 000 000 then C(ACC)= 101 010 000 000 BSE i β bit set code:  $1600 + 20i + \beta$ Set to 1 corresponding bits of the accumulator: = 010 101 010 101 If C(M) and C(ACC) = 111 111 000 000 then C(ACC) = 111 111 010 101 code:  $1640 + 20i + \beta$ BCOiβ bit complement Complement corresponding bits of the accumulator: = 010 101 010 101 If C(M)and C(ACC) = 111 111 000 000 then C(ACC) = 101 010 010 101

These instructions have a variety of applications, some of which will be demonstrated later.

#### 2-6 SPECIAL INDEX REGISTER INSTRUCTIONS

Before continuing with the index class, two special instructions which facilitate programming with the index class instructions will be introduced. These instructions do not use the index registers to hold memory addresses; rather they deal directly with the index registers and are used to change or examine the contents of an index register.

#### 2-6.1 The Index and Skip Instruction

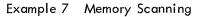

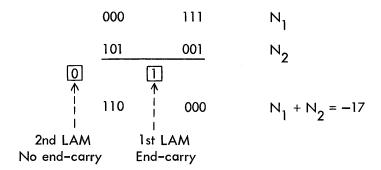

The index and skip instruction, XSK i  $\alpha$ , refers to registers 0-17 ( $0 \le \alpha \le 17$ ).\* It tests to see whether the address part of register  $\alpha$  has its maximum value, i.e., 1777, and directs the LINC to skip the next register in the instruction sequence if 1777 is found. It will also, when i = 1, index the address part (X) of register  $\alpha$  by 1. Like the index class instructions, XSK indexes register  $\alpha$  before examining it, and it indexes from 1777-0000 without affecting the leftmost 2 bits. These 2 bits can therefore have any value. In particular, both can be set to the value 1 and XSK i  $\alpha$  can be assumed to have the effect of skipping the next instruction when it finds the number 7777, (-0), in register  $\alpha$ . Now it is easy to see how to execute any given sequence of instructions exactly n times, where n  $\le 1777$  (octal):

<sup>\*</sup>cf.  $\beta$ ,  $1 \le \beta \le 17$ , which does not refer to register 0.

For example, to store the contents of the accumulator in registers 350-357, using register 6 to count, the following short program can be written.

| Memory Address | Memory Bu       | ıffer    | Effect                                       |

|----------------|-----------------|----------|----------------------------------------------|

| 5              | [X]             | [ 0347 ] | Initial address minus 1 for STA instruction. |

| 6              | [-10]           | [7767]   | -n, where n = number of times                |

|                |                 |          | to store C(ACC).                             |

| Start<br>200   | STA i 5         | 1065     | Index register 5 and store C(ACC).           |

| 201            | X <u>SK i 6</u> | 0226     | Index register 6 and test for X(6) = 1777.   |

| 202            | JMP 200         | 6200     | X(6)≠1777, return.                           |

| 203            | HLT -           | 0000     | X(6) = 1777, halt.                           |

Example 9 Index Registers Used as Counters

Using the XSK instruction with i = 0, which tests  $X(\alpha)$  without indexing, example 6 which stores 0 in memory registers 1400–1777, can be more efficiently written:

| Memory Address | Memory B   | uffer  | Effect                                       |

|----------------|------------|--------|----------------------------------------------|

| 3              | [X]        | [1377] | Initial address minus 1 for STA instruction. |

| Start<br>350   | :<br>CLR   | 0011   | $0 \rightarrow C(ACC)$ .                     |

| 351            | r→ STA i 3 | 1063   | Index register 3 and store zero.             |

| 35 <b>2</b>    | XSK 3      | 0203   | Test for $X(3) = 1777$ .                     |

| 353            | JMP 351    | 6351   | X(3) ≠ 1777, return.                         |

| 354            | HLT        | 0000   | X(3) = 1777, halt.                           |

Example 10 Indexing and Counting to Clear a Set of Registers

Here register 3 is indexed by the STA instruction; the XSK then merely tests to see whether X(3) = 1777, without indexing X(3). The reader should see that example 8 on page 22 can also be more efficiently programmed using XSK.

### 2-6.2 The SET Instruction

The second special instruction which is often used with the index class instructions is SET i  $\alpha$ , code 40 + 20i +  $\alpha$ , where  $\alpha$  again refers directly to the first 20<sub>8</sub> memory registers,  $0 \le \alpha \le 17$ . In some of the examples presented earlier, the contents of index registers are changed, either as counter values or as memory addresses, while the program is running. Therefore, in order to rerun the program the index registers must be reset to their initial values.

The SET instruction directs the LINC to set register  $\alpha$  to the value in any specified memory register. It is different from the instructions so far presented in that the instruction itself always occupies two consecutive memory registers, say p and p + 1:

| Memory<br>Address | Memory Buffer |              |  |

|-------------------|---------------|--------------|--|

| p                 | SETiα         | 40 + 20i + α |  |

| p + 1             | c             | c            |  |

| p + 2             | -             | -            |  |

| ;                 | :             | :            |  |

The computer automatically skips over the second register of the pair, p + 1; that is the contents of p + 1 are not interpreted as the next instruction. The next instruction after SET is always taken from p + 2.

The i-bit in the SET instruction does not control indexing. Instead, it tells the LINC how to interpret the contents of register p + 1. When i = 0, the LINC is directed to interpret C(p + 1) as the memory address for locating the value which will replace C( $\alpha$ ). That is, register p + 1 is thought of as containing X,

| Memory<br>Address | Memory Buffer |      | Effect                 |

|-------------------|---------------|------|------------------------|

| 10                | [N]           | [-]  | C(X), i.e., N, →C(10). |

| :                 | :             | :    |                        |

| → p               | SET 10        | 0050 |                        |

| p+1               | X             | X    |                        |

| :                 | :             | :    |                        |

| X                 | N             | N    |                        |

and the contents of register X replace the contents of 10,  $C(X) \rightarrow C(10)$ . In this case X is the rightmost 10 bits, the address part, of register p + 1; the leftmost bit of C(p + 1) may have any value and, for the present, bit 10 must be 0.

In the second case, when i = 1, the LINC is directed to interpret C(p + 1) as the value which replaces  $C(\alpha)$ . Thus, below,  $C(p + 1) \rightarrow C(5)$ :

| Memory<br>Address | Memory Buffer |      | Effect                     |

|-------------------|---------------|------|----------------------------|

| 5                 | [ N]          | [-]  | C(p + 1), i.e., N, → C(5). |

| ∶                 | :             | :    |                            |

| → p               | SET i 5       | 0065 |                            |

| p+1               | N             | N    |                            |

The following program scans  $100_8$  memory registers looking for a value which matches C(ACC). It halts with the location of the matching register in the accumulator if a match is found, or with -0 in the accumulator if a match is not found. The numbers to be scanned are in registers 1000–1077.

| Memory Address | Memory Buffe                                | Effect                                                                                  |

|----------------|---------------------------------------------|-----------------------------------------------------------------------------------------|

| 3              | [-100] [76                                  | 77] — (number of registers to scan).                                                    |

| 4              | [X] [0]                                     | 77] Scanning address.                                                                   |

| Start<br>→400  | :<br>SET i 3 004                            | 3 $C(401)$ , i.e., $-100$ , $\rightarrow C(3)$ .                                        |

| 401            | -100 767                                    | 7                                                                                       |

| 402            | SETi4 000                                   | 4 C(403), i.e., 777, → C(4).                                                            |

| 403            | 777 072                                     | 7                                                                                       |

| 404            | $\rightarrow SAE i 4$ 14                    | 4 Index X(4) and compare C(X) with C(ACC).                                              |

| 405            | JMP 411 64                                  | 1 $C(ACC) \neq C(X)$ , jump to 411.                                                     |

| 406            | CLR←−- <sup>1</sup> 00 <sup>-</sup>         |                                                                                         |

| 407            | ADD 4 200                                   | 4 C(ACC) = C(X), copy location of matching<br>register into ACC and halt.               |

| 410            | HLT 000                                     |                                                                                         |

| 411            | $ \longrightarrow \underline{XSK i 3} 022 $ | 3 Index register 3 and test for X(3) = 1777.                                            |

| 412            | <u>JMP 404</u> 640                          | 4 X(3) $\neq$ 1777, return.                                                             |

| 413            | CLR <del>&lt;</del> − − <sup> </sup> 00     |                                                                                         |

| 414            | COM 00                                      | 7 $X(3) = 1777$ ; all numbers have been scanned<br>so $-0 \rightarrow C(ACC)$ and halt. |

| 415            | HLT 000                                     |                                                                                         |

Example 11 Setting Initial Index Register Values

The two SET instructions are executed once every time the program is started at 400; initially registers 3 and 4 may contain any values since the program itself sets them to the correct values.

Suppose the programmer had wanted to SET two index registers to the same value, say -100. He could write either:

| Memory<br>Address | Memory   | Buffer | Effect                                         |

|-------------------|----------|--------|------------------------------------------------|

| 11                | [-100]   | [7677] |                                                |

| 12                | [-100]   | [7677] |                                                |

|                   |          |        |                                                |

| <b>→</b> 20       | SET i 11 | 0071   | C(21), i.e., -100,→ C(11).                     |

| 21                | -100     | 7677   |                                                |

| 22                | SET 12   | 0052   | $C(21)$ , i.e., $-100$ , $\rightarrow C(12)$ . |

| 23                | 21       | 0021   |                                                |

| or:               |          |        |                                                |

| <b>→</b> 20       | SET i 11 | 0071   | C(21), i.e., -100,→C(11).                      |

| 21                | -100     | 7677   |                                                |

| 22                | SET 12   | 0052   | (C11), i.e., -100, → C(12).                    |

| 23                | 11       | 0011   |                                                |

The programmer could also, of course, have written SET i 12 in register 22 with -100 in register 23, but there are applications appropriate to each form.

## 2-7 INDEX CLASS INSTRUCTIONS II

#### 2-7.1 Double Register Forms

The index class instructions have been thought of as addressing an index register  $\beta$ ,  $1 \le \beta \le 17$ , which contains a memory address X to be used by the instruction. They have been presented as single register instructions (unlike SET). However, when an index class instruction is written with  $\beta = 0$ , it becomes a double register instruction like SET, whose operand address depends on i and p + 1. These two interpretations are shown for STA.

Case: i = 0,  $\beta = 0$

| Memory<br>Address | Me  | mory Buffer             | Effect         |

|-------------------|-----|-------------------------|----------------|

| 450               | STA | 1040 + <b>20(0)</b> + 0 | C(ACC)→C(330). |

| 451               | 330 | 0330                    |                |

When i = 0, the LINC is directed to use C(p + 1), i.e., C(451) as the memory address at which to store C(ACC). The leftmost bit of C(p + 1) may have any value, and, for the present, bit 1 must be 0. Case: i = 1,  $\beta = 0$

| Memory<br>Address | Memory Buffer |      | Effect        |

|-------------------|---------------|------|---------------|

| 450               | STA i         | 1060 | C(ACC)→C(451) |

| 451               | [-]           | [-]  |               |

When i = 1, the LINC is directed to use p + 1, i.e., 451, directly as the memory address, and the contents of the accumulator are stored in 451. Note that when  $\beta = 0$  in an index class instruction, it does not refer to memory register 0. In fact, when  $\beta = 0$ , no reference is necessarily made to the index registers. As with SET, the computer automatically takes the next instruction from register p + 2.

Index class instructions may be thought of as having four alternative ways of addressing the memory, which depend on i and  $\beta$ , and which are summarized below:

|      | Index Class Address Variations |            |                    |                                                                               |  |  |

|------|--------------------------------|------------|--------------------|-------------------------------------------------------------------------------|--|--|

| Case | i,β                            | Example    | Form               | Comments                                                                      |  |  |

| 1    | i = 0<br>β≠0                   | LDA β      | Single<br>Register | Register β holds operand address.                                             |  |  |

| 2    | i = 1<br>$\beta \neq 0$        | LDA i β    | Single<br>Register | First, index register β by 1.<br>Then, register β holds oper-<br>and address. |  |  |

| 3    | i = 0<br>β = 0                 | LDA<br>X   | Double<br>Register | Second register holds oper-<br>and address.                                   |  |  |

| 4    | i = 1<br>β = 0                 | LDA i<br>N | Double<br>Register | Second register holds op-<br>erand.                                           |  |  |

The next programming example scans memory registers 1350–1447, counting the number of instances in which register contents are found to exceed some threshold value, T. In other words if C(X) >T, X = 1350, 1351, ..., 1447, then  $C(CTR) + 1 \rightarrow C(CTR)$ , where CTR is a memory register used as a counter, initially set to 0. The count, N, is to appear in the accumulator upon program completion.

| Memory Address | Memory B                         | uffer | Effect                                                                                                                                          |

|----------------|----------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 14             | [X]                              | [-]   | Address of register to be tested.                                                                                                               |

| 15             | [-n]<br>•                        | [-]   | -(number of registers to test).                                                                                                                 |

| Start<br>→ 30  | :<br>SET i 14                    | 0074  | Set index register 14 to initial address minus 1.                                                                                               |

| 31             | 1347                             | 1347  |                                                                                                                                                 |

| 32             | SET i 15                         | 0075  | Set index register 15 to -100.                                                                                                                  |

| 33             | -100                             | 7677  |                                                                                                                                                 |

| 34             | CLR                              | 0011  | } Clear CTR; 0→C(51).                                                                                                                           |

| 35             | STC 51                           | 4051  |                                                                                                                                                 |

| 36             | _→LDA i                          | 1020  | C(37), i.e., -T, → C(ACC).                                                                                                                      |

| 37             | -т                               | –т    |                                                                                                                                                 |

| 40             | ADA i 14                         | 1134  | Index the address in register 14 and form C(X)–T in ACC.                                                                                        |

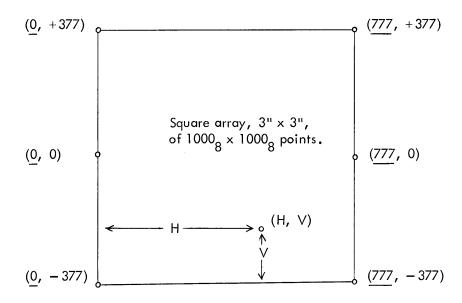

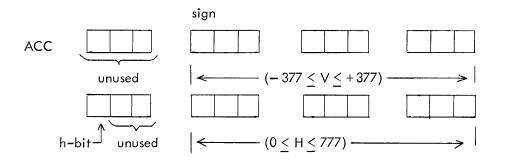

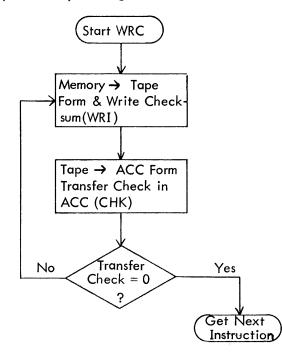

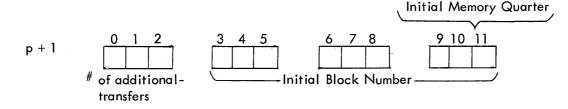

| 41             | BCL i                            | 1560  | Clear all but the sign bit in ACC; C(42) = the bit<br>pattern for clearing. Then if C(X) > T, C(ACC) =<br>0000, but if C(X) < T, C(ACC) = 4000. |