### instruction book

Volume 1

# **C-System Principles of Operation**

Printed in United States of America

| Page No.      | Issue         | Page No.              | Issue      |

|---------------|---------------|-----------------------|------------|

| Title         | Original      | 5-1 thru 5-23         | . Original |

| Α             | Original      | 5-24 Blank            | . Original |

| i thru vii    |               | 5-25                  | . Original |

| viii Blank    | Original      | 5-26 Blank            | . Original |

| 1-1 thru 1-5  | Original      | 6-1 thru 6-17         | . Original |

| 1-6 Blank     | Original      | 6-18 Blank            |            |

| 2-1 thru 2-19 |               | 6-19                  | . Original |

| 2-20 Blank    | Original      | 6-20 Blank            | . Original |

| 2-21          | Original      | 6-21                  | . Original |

| 2-22 Blank    | Original      | 6-22 Blank            | . Original |

| 3-1 thru 3-15 | Original      | 7-1 thru 7-7          | . Original |

| 3-16 Blank    | Original      | 7-8 Blank             | . Original |

| 3-17          |               | 7-9                   | . Original |

| 3-18 Blank    |               | 7-10 Blank            |            |

| 4-1 thru 4-13 |               | Appendix              |            |

| 4-14 Blank    | · · · · · · · | (Paragraphs 1 thru 7) | . Original |

| <b>Record of Revisions</b> |                  | RETAIN THIS RECORD IN THE FRONT OF MANUAL.<br>ON RECEIPT OF REVISIONS, INSERT REVISED PAGES IN THE MANUAL,<br>AND ENTER DATE INSERTED AND INITIALS |    |             |                  |                   |    |

|----------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------|------------------|-------------------|----|

| ASSIGNED T                 | 0 (JOB TITLE)    |                                                                                                                                                    |    |             | LOCAT            | 10N               |    |

| REV.<br>NO.                | REVISION<br>DATE | INSERTION<br>DATE                                                                                                                                  | ВҮ | REV.<br>NO. | REVISION<br>DATE | INSERTION<br>DATE | ВҮ |

|                            |                  |                                                                                                                                                    |    |             |                  |                   |    |

|                            |                  |                                                                                                                                                    |    |             |                  |                   |    |

|                            |                  |                                                                                                                                                    |    |             |                  |                   |    |

|                            |                  |                                                                                                                                                    |    |             |                  |                   |    |

|                            |                  |                                                                                                                                                    |    |             |                  |                   |    |

|                            |                  |                                                                                                                                                    |    |             |                  |                   |    |

| •                          |                  |                                                                                                                                                    |    |             |                  |                   |    |

|                            |                  |                                                                                                                                                    |    |             |                  |                   |    |

|                            |                  |                                                                                                                                                    |    |             |                  |                   |    |

### table of contents

Page

| Section 1 Introduction                                   | 1-1    |

|----------------------------------------------------------|--------|

| 1.1 General                                              | 1-1    |

| 1.2 System Organization                                  | 1-1    |

| 1.3 System Operation                                     | 1-3    |

|                                                          | 1-0    |

| Section 2 System Organization                            | 2-1    |

| 2.1 Introduction                                         | 2-1    |

| 2.2 System Hardware Organization                         | 2 - 1  |

| 2.2.1 Time Division Exchange System                      | 2-1    |

| 2.2.2 Processor                                          | 2-2    |

| 2.2.2.1 Arithmetic Logic and Control Unit                |        |

| (ALCU)-8561 A-2                                          | 2-2    |

| 2.2.2.2 Magnetic Core Storage                            | 2-2    |

| 2.2.2.3 Communications Service Unit                      | 2 - 3  |

| 2.2.2.4 Multiplex Service Unit                           | 2-4    |

| 2.2.2.5 Processor Service Unit                           | 2-5    |

| 2.2.2.6 Transfer Link                                    | 2-5    |

| 2.2.3 Disc Files                                         | 2-6    |

| 2.2.4 Magnetic Tape Units                                | 2-7    |

| 2.2.5 Peripheral Devices                                 | 2-7    |

| 2.2.6 Time Division Multiplex Loop                       | 2-7    |

| 2.3 System Software Organization                         | 2-7    |

| 2.3.1 Time Division Exchange (TDX) Communication         | 2-8    |

| 2.3.2 Operations Control Program                         | 2-8    |

| 2.3.3 Orderwire 1 Channel                                | 2-9    |

| 2.3.4 Orderwire 2 Channel                                | 2-10   |

| 2.3.4.1 Data Collection Service                          | 2-10   |

| 2.3.4.2 Device Acquisition and Control Service           | 2-10   |

| 2.3.4.3 Scheduler Program                                | 2 - 11 |

| 2.3.4.4 Load Regulation Program                          | 2-11   |

| 2.3.5 S Channel                                          | 2 - 11 |

| 2.3.5.1 Control Program Service                          | 2-12   |

| 2.3.5.2 Space Release                                    | 2-13   |

| 2.3.5.3 A and B Channel Queue Service                    | 2-13   |

| 2.3.6 A and B Channels                                   | 2-13   |

| 2.3.7 M Channel                                          | 2-14   |

| 2.3.8 Common Functions                                   | 2-15   |

| 2.3.8.1 Common Space Allocation and Release              | 2 - 15 |

| 2.3.8.2 Disc File Storage Space Allocation and Release . | 2-15   |

| 2.3.8.3 Direct File Transfer                             | 2-16   |

| 2.3.8.4 Indirect File Transfer                           | 2 - 16 |

| 2.3.8.5 Device Control Message Routines                  | 2 - 17 |

| 2.3.8.6 Service Message Transfer                         | 2-17   |

i

|                   |                                                               | Page       |

|-------------------|---------------------------------------------------------------|------------|

| 2.3.8.7 O         | rderwire Translation                                          | 2-17       |

|                   | outing and Conversion                                         | 2-17       |

|                   | bject Program Mapping                                         | 2-18       |

|                   | imer 1 Interface                                              | 2-18       |

| 2.3.8.11 T        | rapped Operation Code Interface                               | 2-18       |

| 2.3.8.12 M        | I Channel Linkage                                             | 2-18       |

| Section 3 Proce   | ssor Operation, Organization, and Control                     | 3-1        |

|                   | ction                                                         | 3-1        |

|                   | sor Operation                                                 | 3-1        |

|                   | Formats                                                       | 3-1        |

|                   | ileged Mode and Protected Memory                              | 3-1        |

|                   | oped Operation Code Execution                                 | 3-3        |

|                   | rupts                                                         | 3-3        |

|                   | rogram Interrupt                                              | 3-4        |

|                   | arity Interrupt                                               | 3-4        |

|                   | imer Interrupts                                               | 3-4        |

|                   | orage Organization                                            | 3-4        |

|                   | essor Interfaces                                              | 3-5        |

|                   | rocessor Interface Table                                      | 3-5        |

|                   | perations Control Table and Operations                        | 3-6        |

|                   | equence Table                                                 | 3-0<br>3-6 |

|                   | evice Control Messages                                        | 3-0        |

|                   | Iultiplex Status Records and the M-Queues         unel Spaces | 3-7        |

|                   | mon Core                                                      | 3-8        |

|                   | ons Control Program                                           | 3-8        |

|                   | c Operations Control                                          | 3-8        |

|                   | ce Control Message Verification                               | 3-10       |

|                   | er Interrupts                                                 | 3-12       |

|                   | imer 0 Interrupts                                             | 3-12       |

|                   | imer 1 Interrupts                                             | 3-13       |

|                   | nel Uses of Operations Control                                | 3-13       |

| Section 4 Service | e Messages                                                    | 4-1        |

|                   | L                                                             | 4-1        |

|                   | Message Flow                                                  | 4-1        |

|                   | ire 1 Service Messages                                        | 4-3        |

|                   | ediate Operations                                             | 4-6        |

|                   | ice Channel Functions                                         | 4-6        |

|                   | erwire 2 Channel Functions                                    | 4-8        |

|                   | nannel Functions                                              | 4-10       |

| 4.3.5 A an        | d B Channel Functions                                         | 4-10       |

.

| 4.3.6 Direct Access Functions                                | 4-11 |

|--------------------------------------------------------------|------|

| 4.4 Orderwire 2 Service Messages                             | 4-11 |

| 4.4.1 Operator Setup                                         | 4-11 |

| 4.4.2 Orderwire 2 Bid Message Input                          | 4-11 |

| 4.4.3 Assign Working Channel                                 | 4-11 |

| Section 5 Time Division Exchange Loop Input/Output Operation | 5-1  |

| 5.1 Introduction                                             | 5-1  |

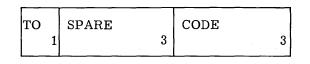

| 5.2 Channel Acquisition                                      | 5-2  |

| 5.3 Input/Output Operations                                  | 5-2  |

| 5.3.1 Orderwire 1 Service Message Transaction                | 5-2  |

| 5.3.2 Disc File Storage Transaction                          | 5-2  |

| 5.3.3 Tape File Storage Transaction                          | 5-3  |

| 5.3.4 Peripheral Device Transactions                         | 5-4  |

| 5.3.5 Orderwire 2 Service Message Transactions               | 5-4  |

| 5.3.6 Direct Access Transaction                              | 5-5  |

| 5.4 Device Control Message Execution                         | 5-6  |

| 5.4.1 Data Channel Operation                                 | 5-10 |

| 5.4.2 Orderwire 1 Channel Operation                          | 5-19 |

| 5.4.3 Orderwire 2 Channel Operation                          | 5-21 |

| Section 6 Time Division Multiplex Input/Output               | 6-1  |

| 6.1 Introduction                                             | 6-1  |

| 6.2 Environment                                              | 6-1  |

| 6.3 Multiplex Service Unit/Multiplex Service Program         |      |

| Communications                                               | 6-3  |

| 6.4 Multiplex Service Unit/Device Communications             | 6-8  |

| 6.4.1 Device to Multiplex Service Unit Supervisory           |      |

| Signals                                                      | 6-8  |

| 6.4.2 Multiplex Service Unit to Device Supervisory           |      |

| Signals                                                      | 6-10 |

| 6.5 M Channel Subroutines                                    | 6-11 |

| 6.5.1 Subroutine Classification                              | 6-11 |

| 6.5.2 Typical Common Subroutines                             | 6-11 |

| 6.5.2.1 Open Write File (OWF)                                | 6-11 |

| 6.5.2.2 Put Segment (PTS)                                    | 6-11 |

| 6.5.2.3 Close Write File (CWF)                               | 6-12 |

| 6.5.2.4 Open Read File (ORF)                                 | 6-12 |

| 6.5.2.5 Get Segment (GTS)                                    | 6-12 |

| 6.5.2.6 Release File (RLF)                                   | 6-12 |

| 6.6 Time Division Multiplex Input/Output                     | 6-13 |

| 6.6.1 Typical Input Operation                                | 6-13 |

| 6.6.1.1 Preparation                                          | 6-13 |

|                                        | Page |

|----------------------------------------|------|

| 6.6.1.2 File or Message Delivery       | 6-13 |

| 6. 6. 1. 3 Completion                  | 6-14 |

| 6.6.2 Output Operations                | 6-14 |

| 6.6.2.1 Preparation                    | 6-15 |

| 6.6.2.2 File or Message Delivery       | 6-15 |

| 6.6.2.3 Completion                     | 6-16 |

| Section 7 File Structures              | 7-1  |

| Section 7 File Structures              | 1    |

| 7.1 Introduction                       | 7-1  |

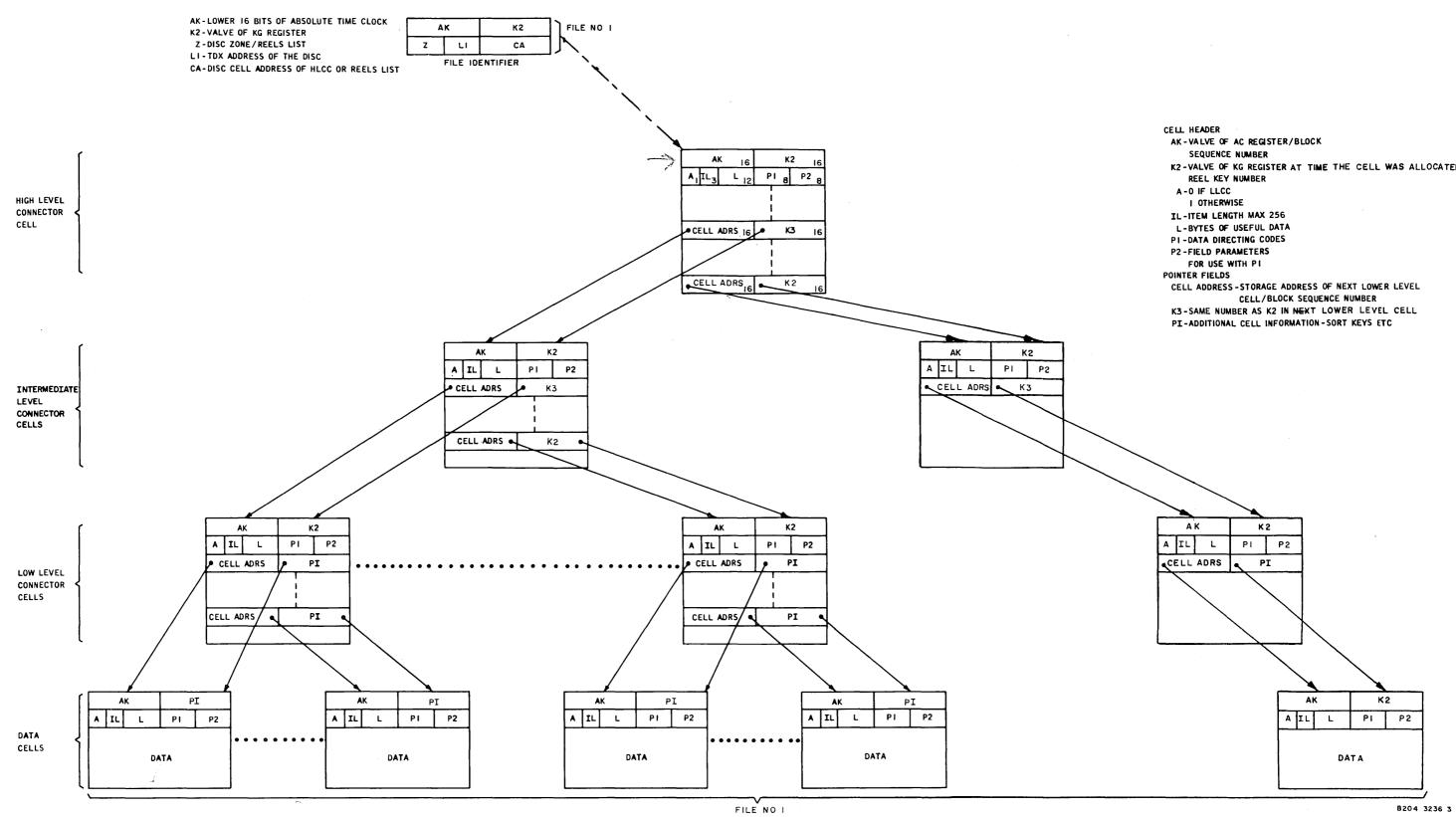

| 7.2 Disc File Structure                | 7-1  |

| 7.2.1 File Identifier                  | 7-1  |

| 7.2.2 Cell Headers                     | 7-2  |

| 7.2.3 Connector Cells                  | 7-2  |

| 7.2.4 Data Cell                        | 7-3  |

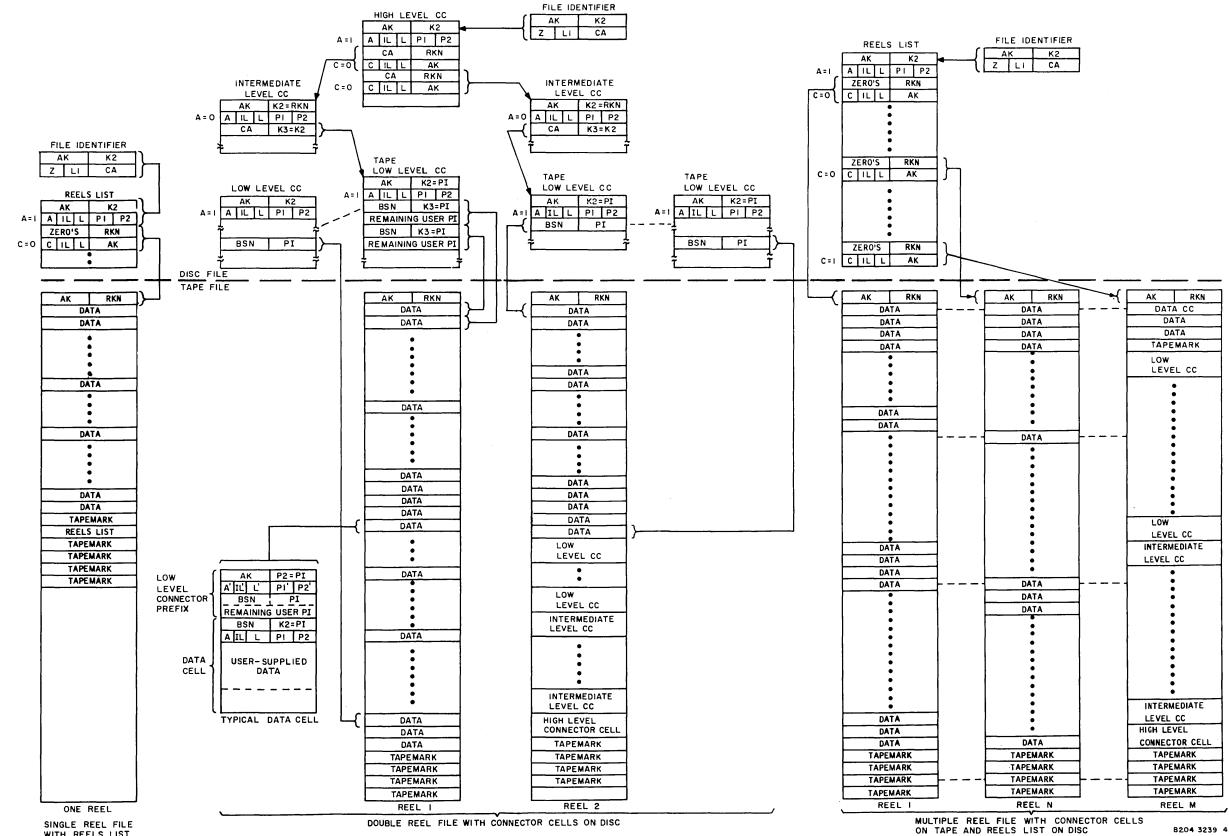

| 7.3 Tape File Structure                | 7-3  |

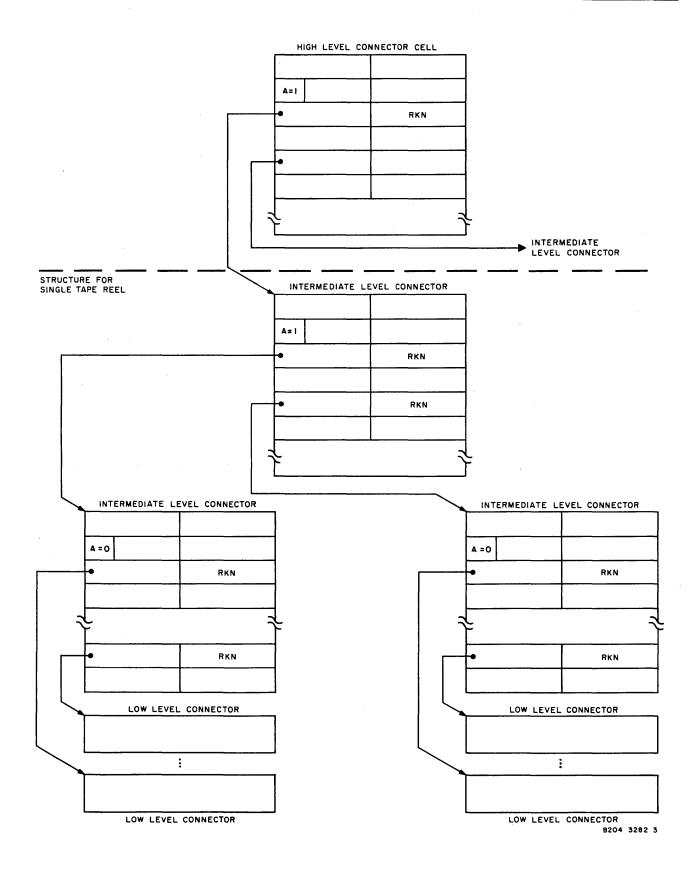

| 7.3.1 Full Connector Structure on Disc | 7-3  |

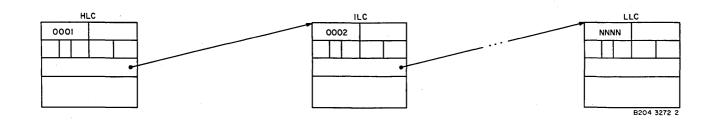

| 7.3.2 Connector Structure on Tape      | 7-4  |

| 7.3.3 Reels List on Disc               | 7-6  |

#### Appendix

| 1. Orde: | rwire 1 Service Message Formats |

|----------|---------------------------------|

|          | mediate Operations Formats      |

| 1.1.1    | Replace Output Tape Return      |

| 1.1.2    | Initialize Ops Control          |

| 1.2 S    | Channel Formats                 |

| 1.2.1    | CPSR Call                       |

| 1.2.2    | Program Return                  |

| 1.2.3    | CP Abnormal Return              |

| 1.2.4    | AP Abnormal                     |

| 1.2.5    | Space Release                   |

| 1.2.6    | CPSR Generator Return           |

| 1.2.7    | Initial CPSR Call               |

| 1.2.8    | Redirect                        |

| 1.3 Oi   | derwire 2 Channel Formats       |

| 1.3.1    | DACS Functions                  |

| 1.3.1.1  | Tape Release                    |

| 1.3.1.2  | DACS Request                    |

| 1.3.1.3  | Replace Output Tape             |

| 1.3.1.4  | DACS Routing Request            |

| 1.3.2    | DCS Functions                   |

| 1.3.2.1  | DCS File Update from CPS        |

| 1.3.2.2  | DCS File Update from Program    |

| 1.3.2.3  | DCS Extract and Delete          |

|          |                                 |

|          |                                 |

- 1.3.2.4 DCS Code Delete

- 1.3.2.5 DCS Code Request (Unload Allowed)

- 1.3.2.6 DCS File Return

- 1.3.2.7 DCS Collection Inhibit

- 1.3.2.8 DCS Extract and Save

- 1.3.3 Scheduler Functions

- 1.3.3.1 Scheduler Service Call

- 1.3.3.2 Scheduler Table Generator Return

- 1.3.4 Load Regulator Functions

- **1.3.4.1** Processor Initialization

- 1.3.4.2 Processor Removal

- 1.3.4.3 Disc Initialization

- 1.3.4.4 Disc Removal

- 1.3.4.5 Overload

- 1.3.4.6 Regulator Tables Update Return

- 1.4 Multiplex Channel Formats

- 1.4.1 I/O Call 1 Service Message

- 1.4.2 I/O Call 2 Service Message

- 1.4.3 TDM Device Initialization Response

- 1.5 B Channel Formats

- 1.5.1 Application Program Call

- 1.5.2 Program Call

- 1.6 A Channel

- 1.6.1 Application Program Call

- 1.6.2 Program Call

- 1.7 Direct Access Message Format

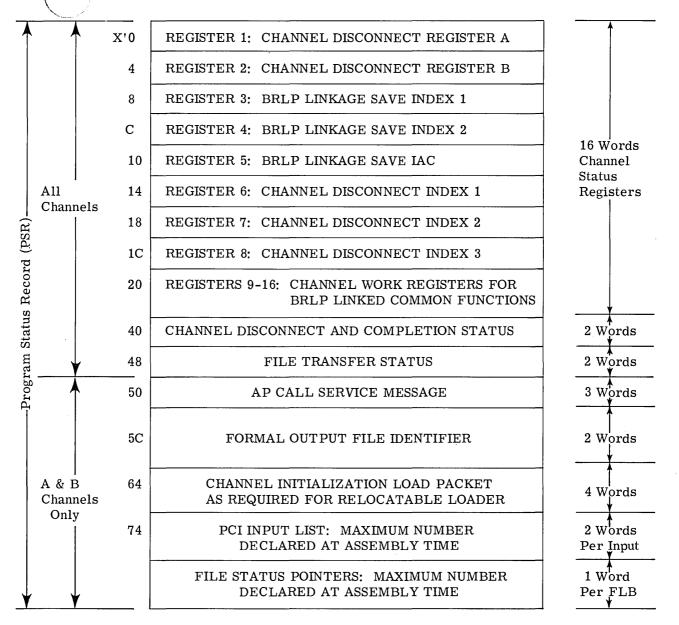

- 2. Device Control Message DCM (DCM) Format

- 3. Operations Control Table Format

- 4. Processor Interface Table Format

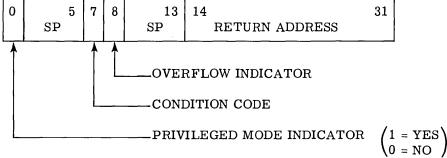

- 5. Channel Save Area Format

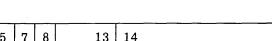

- 6. Processor Status Record

- 7. Multiplex Status Record Format

### list of illustrations

#### Figure

| Page |

|------|

|------|

| 1-1        | System Organization                             | 1-2        |

|------------|-------------------------------------------------|------------|

| 1-2        | System Operation                                |            |

| 2-1        | 8561A-2 Arithmetic Logic and Control Unit       |            |

| 2-2        | Communications Service Unit                     | 2-4        |

| 2-3        | Processor Service Unit, Controls and Indicators | 2-6        |

| 2-4        | Typical C-System Computer Center                | 2-19/2-20  |

| 2-5        | System Software                                 |            |

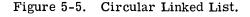

| 3-1        | NRP, NAC, and NWP Relationships                 |            |

| 3-2        | Core Storage Organization                       |            |

| 3-3        | Operations Control Program                      |            |

| 4-1        | Service Message Flow                            |            |

| 5-1        | File Transfer Packets                           |            |

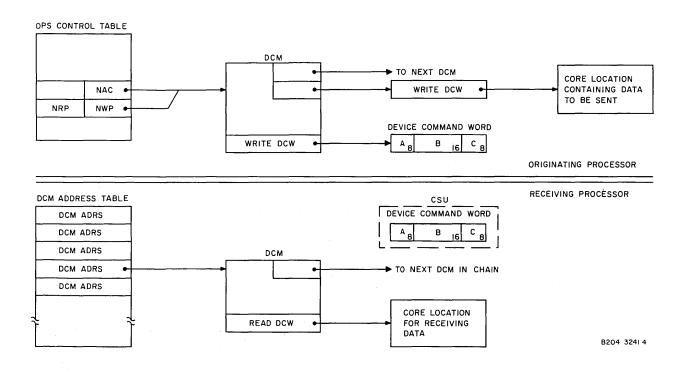

| 5-2        | Direct Access Mechanism DCM's and DCW's to      |            |

|            | Write a Record                                  | 5-5        |

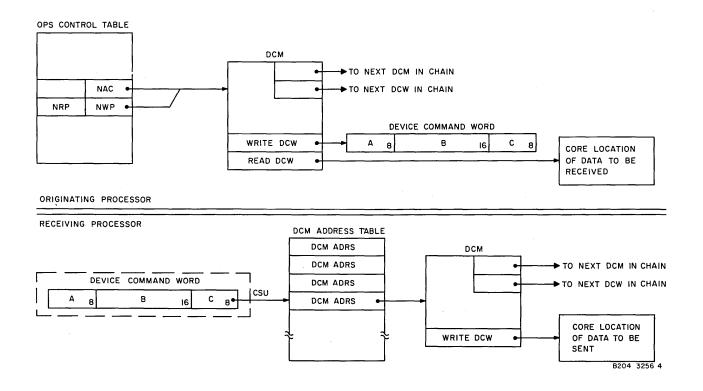

| 5-3        | Direct Access Mechanism DCM's and DCW's to      |            |

|            | Read a Record                                   | 5-6        |

| 5-4        | TDX I/O Hardware Software Interface Diagram     | 5-7        |

| 5-5        | Circular Linked List                            | 5-8        |

| 5-6        | DCM Pointers                                    |            |

| 5-7        | DCM Header                                      |            |

| 5-8        | DCM Operations Code Field                       |            |

| 5-9        | Device Control Message                          |            |

| 5-10       | Data Control Word Lists                         |            |

| 5-11       | Operations Control Table Entry and Processor    | 0 10       |

| • •        | Interface Table Entry                           | 5-20       |

| 5-12       | Input/Output Operation                          |            |

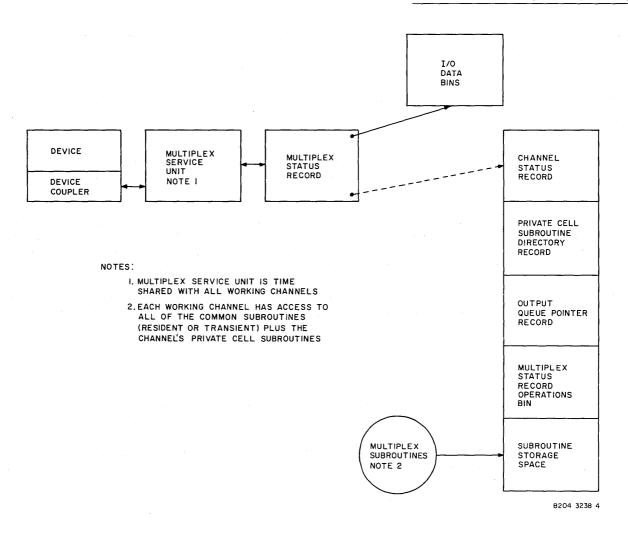

| 6-1        | Working Channel                                 |            |

| 6-2        | Multiplex Status Record Format                  |            |

| 6-3        | TDM Hardware/Software Interface                 |            |

| 0-0<br>7-1 | Multiple Level of Intermediate Level Connector  | 0-11/ 0-10 |

| • - T      | Cells                                           | 7-5        |

| 7-2        | Connector Cell Structure on Tape                |            |

| 7-3        | Basic File Structure                            | _          |

| 7-4        | Multiple Reel Tape File Structure               |            |

| 11         |                                                 | 1-9/1-10   |

### list of tables

| Table |                                              | Page      |

|-------|----------------------------------------------|-----------|

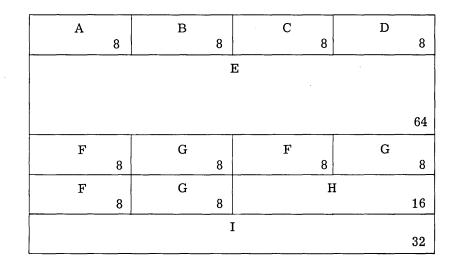

| 3-1   | Alignment Restrictions                       | 3-2       |

| 3-2   | BRLP Codes                                   | 3-2       |

| 3-3   | DCM Chain Verification                       | 3-11      |

| 3 - 4 | Timer 1 Interrupt Handling                   | 3-14      |

| 4-1   | Service Messages                             | 4-4       |

| 6-1   | Device to Multiplex Service Unit Supervisory |           |

|       | Signals Summary                              | 6-9       |

| 6-2   | Multiplex Service Unit to Device Supervisory |           |

|       | Signals Summary                              | 6-10      |

| 6-3   | MSU Operation                                | 6-19/6-20 |

.

## section 1 introduction

#### **1.1 GENERAL**

The C-System is a flexible, expandable hardware system supported by modular software. Time division communication techniques enable single processor installations having limited input/output capacity to be expanded easily into large distributed networks of interconnected processors and peripheral devices. The modular operating software system complements this flexibility and permits the execution of many independent tasks on either a multiprogrammed basis by a single processor or on a multiprocessing basis when more than one processor is installed. The flexibility of both software and hardware allows easy C-System adaptation to a wide range of user requirements. This manual contains a detail explanation of the principles of operation for the C-System center.

#### **1.2 SYSTEM ORGANIZATION**

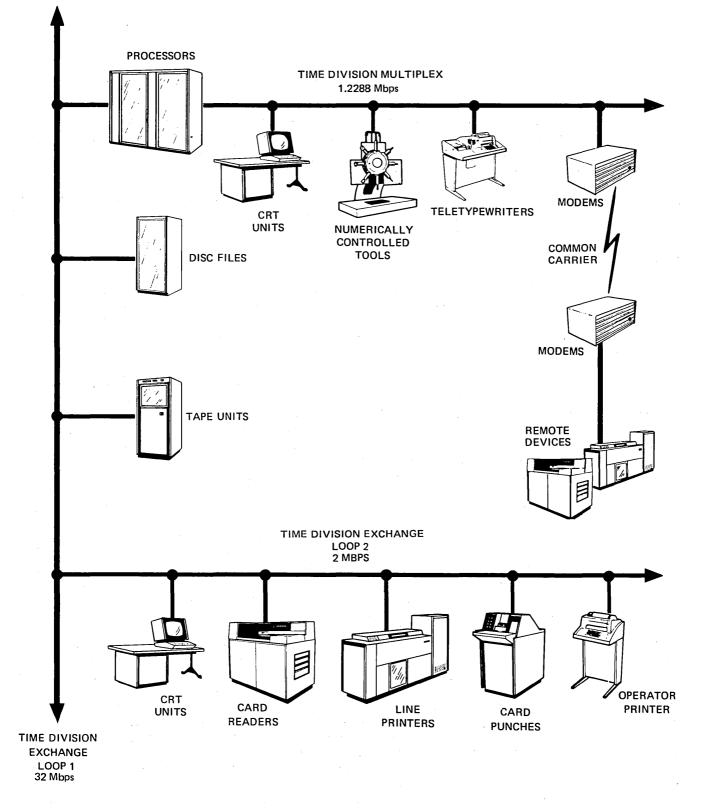

A typical C-System center (figure 1-1) consists of a number of processors, storage units, and peripheral devices interconnected by a high-speed communications facility called the time division exchange. The time division exchange is a switched communications network that allows all processors to have access to all storage facilities and peripheral devices in the center. Communication with devices that require continuous processor service is provided by a time division multiplex facility.

The time division exchange, which operates at 32 million bits per second, uses time division techniques to match its input/output data rate (2, 4, or 8 million bits per second) to that of the peripheral devices. The peripheral devices that operate at high speeds, such as disc files and magnetic tape units, are connected along a coaxial cable loop on the main exchange called loop 1. The slower-speed peripherals (such as cathode-ray-tube displays, line printers, and card readers) are connected by a second loop of coaxial cable called loop 2. This subloop provides the slower data rates (250 to 7.8 thousand bits per second) by subdividing the 2-Mbps data rate from the main exchange. Thus, the data rate from the time division exchange can be tailored to the speeds of the peripheral devices and all devices except disc files can be reassigned dynamically during system operation.

The time division multiplex communications facility connects low- and medium-speed devices directly to a processor and provides for intercenter communications. The multiplex facility operates at 1.2288 million bits per second and uses multiplexing techniques so that it can handle many peripheral devices having various data transfer rates (from 4800 to 153,600 bits per second). Each time division multiplex channel can be used to control teletypewriters, numerically controlled machines, cathode-ray-tube displays, process facilities, and other types of terminal devices.

C-System processor time, data paths, core space, and associated software are divided into independent processor channels that time-share the arithmetic logic and control unit. Consequently, arithmetic logic and control unit time is distributed between channels to provide effective multiprogramming and enables the operating system to automatically distribute work and regulate the workloads within the system. Two processor channels (designated A and B) are used to execute application programs; the A channel is used for major application programs and the B channel is used for minor application programs. Two processor channels (designated the orderwire 1 channel and the service or S channel) are used by the operating system; the orderwire 1 channel is used for processor communication of service messages containing control information and the service channel is used for routing of work to processor channels, queueing of work, and controlling the execution of control programs. One processor in the center contains an orderwire 2 channel which contains center control functions including the load regulator, system scheduler, data collection service, and a program to manage the assignment

#### introduction

### TIME DIVISION

of peripheral devices to programs. The remaining processor channel (designated M channel) is used to service the time division multiplex facility.

The programming procedures employed in the C-System involve partitioning the overall activity into separate, well defined, and manageable tasks. Once the task list has been sequenced, the input requirements and the desired outputs are specified for each task. Together, these steps define a logical order of work and form a directed action network. Within the C-System, this logical order of work to be performed is specified by a control program. The control program directs activity within the system at the program calling level. Each task to be performed is specified by an instruction within the control program and may be dispatched to any suitable facility for execution.

As a result, the C-System operating structure allows completely automatic job execution of complex applied systems in a regulated multiprocessor environment. Messages are exchanged between processors and devices for directing work, reporting results, updating job status records and initiating new work. The result is a completely controlled processing environment.

#### **1.3 SYSTEM OPERATION**

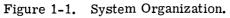

The C-System software controls the distribution of tasks, provides the service necessary for program execution, and manages all output files. The system software implementation is based on a control program structure that allows input directed control. Control programs define the structural relationships among interrelated subtasks of an overall applied system. A control program consists of Program Control Instructions (PCI) as illustrated at the top of figure 1-2. The nodes represent program control instructions; the interconnecting lines show the required sequence of execution and indicate the outputs of program control instructions that become inputs to other program control instructions.

Each program control instruction contains information which identifies all data files necessary to execute the corresponding program, the location of the program, and other program control instructions that will require files created by execution of this program control instruction. The description and status of the control program is maintained in a control program status record. Each control program is executed by the processor that maintains the control program status record for the control program. Control programs may be initiated externally or on a scheduled basis by a system scheduler. In addition to referencing application programs to be executed, program control instructions may reference other control programs resulting in a nested control program structure.

Every processor in a C-System center may read information from any disc file but may only write to disc file space it has been assigned to manage. As shown in figure 1-2, processor 1 can read from or write to disc file 1, but it may only read from disc file 2; processor 2 can read from or write to disc file 2 but it may read only from disc file 1. The assignment of a whole disc file to a given processor has been illustrated here for simplicity; however, in actual practice disc file space may be segmented allowing several processors to write to one physical disc file but each processor is limited to an assigned segment.

The scheduler is a system program that resides in one processor in a center. At the preassigned time for initiation of a control program, a service message is sent to the processor responsible for the control program. The cognizant processor receives the service message and queues the message for subsequent processing by the service channel. A service program called control program service receives this message from the queue, accesses the control program status record from disc file storage, and builds a service message containing the return address of the cognizant processor, the disc address of the control program status constant, and the location of the calling program control instruction. The service message is then sent to the processor address obtained from the load dispatch table. When the program control instruction has been executed, a return service message is sent to the cognizant processor for the control program status update. Service messages are constructed to direct the execution of subsequent program control instructions to dispatch work throughout the center.

#### introduction

Figure 1-2. System Operation.

When a processor receives a service message to execute a program control instruction, the processor reads the control program status record from the calling processors disc file storage and obtains the particular program control instruction identified in the service message from the control program status record. The program identified in the program control instruction is then executed using input files identified in the program control instruction. The program creates an output file and stores the file on disc. At completion of the program, a return service message is sent to the originating processor noting completion of the program control instructions in the location of the output file. This process continues until all program control instructions in the control program status record have been executed.

Work required to execute programs called by the program control instructions may be dispatched to any processor in the center. Thus, all processors may be involved in dispatching work to other processors. To avoid an unbalanced distribution of work, a load regulator program, which resides in one of the processors, periodically samples work queues throughout the system. If an undesirable balance of work is detected, the load regulator program may send appropriate service messages to various processors altering the work dispatch tables to result in a more evenly distributed work load.

More detailed introductory information is contained in the "C-System General Description" (523-0561-697), "C-System Operating System Software Description" (523-0699-114), and other Collins publications.

$\frac{\text{section } 2}{\text{system organization}}$

#### 2.1 INTRODUCTION

This section introduces the hardware organization and operating system software of a typical C-System multiprocessor center.

#### 2.2 SYSTEM HARDWARE ORGANIZATION

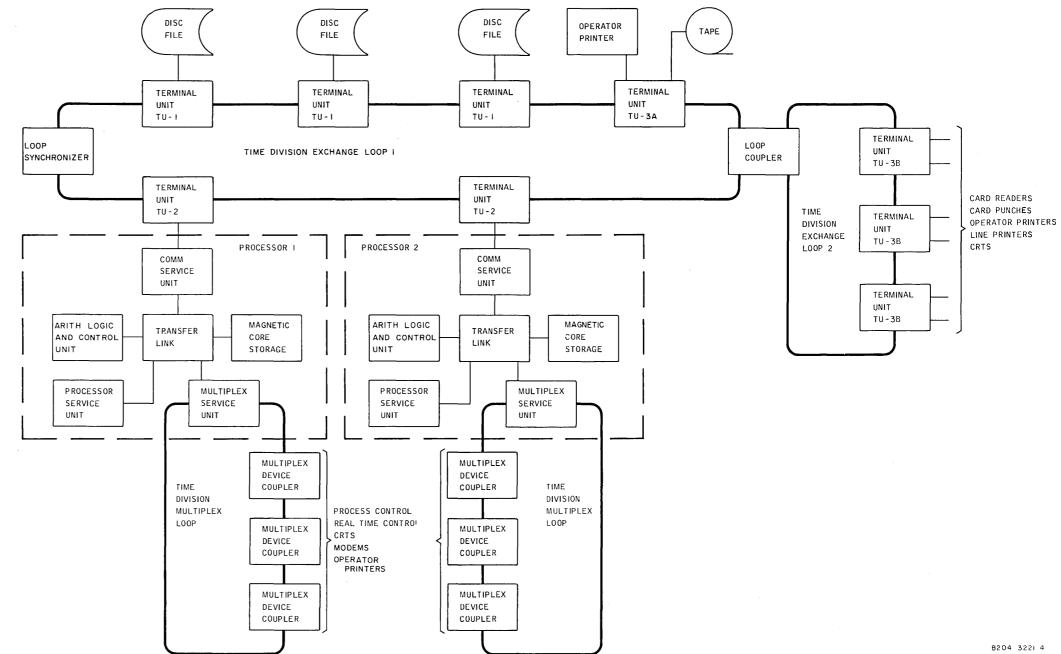

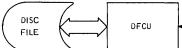

Figure 2-4 shows the basic structure of a typical C-System computer center. In general, a C-System is a multiprocessing system with several processors in a center. Processors and mass storage devices are interconnected via the Time Division Exchange (TDX) system. Connections to the exchange are made through terminal units. TU-1 terminal units connect disc files to the exchange; TU-2 terminal units connect processors to the exchange and TU-3A terminal units connect magnetic tape units and operator printers to the exchange. Subloops, designated loop 2, are connected to loop 1 by loop couplers. Card punches, card readers, line printers, CRT's, and operator printers are connected to loop 2 via TU-3B terminal units.

Two processors are shown in figure 2-4. A processor consists of an arithmetic logic and control unit, a magnetic core storage, a transfer link, a processor service unit, a multiplex service unit, and a communications service unit. The transfer link provides the interface between core storage and the other units of the processor. The communications service unit interfaces the processor to the time division exchange system. The multiplex service unit interfaces the processor to the time division multiplex system. The processor service unit is used during initial program loading and provides diagnostic and status monitoring functions during processor operation.

A Time Division Multiplex (TDM) loop may be attached to each processor for connecting low-speed devices to the processor, such as operator printers, CRT's, process control machines, and modems for remote communications. Devices are interfaced with the time division multiplex loop via a multiplex device coupler.

#### 2.2.1 Time Division Exchange System

The C-System uses time division communication techniques for communication between processors, peripherals, and various input/output terminals. As shown in figure 2-4, communication between processors, disc files, tape stands, and related operating equipment is accomplished via time division multiplex techniques on time division exchange loops (loop 1 and loop 2). In loop 1, the loop synchronizer generates a digital pulse train at 32 Mbps. This pulse stream is used to derive sixteen 2-Mbps bit-inter-laced communication channels (every sixteenth bit is devoted to one channel). The terminal units identify the channels by detection of a synchronization pulse generated by the loop synchronizer. Data transferred on the loops contain a 32-bit word with four additional bits of supervision. It is also possible to use loop 1 channels together resulting in additional channel rates of 4 Mbps or 8 Mbps.

Certain loop 1 communication channels are dedicated to disc file communication; every disc file normally has a private channel for communication. When a processor needs to access a disc file, its terminal unit waits for a poll. The processor bids for the channel and the channel is granted. The processor transfers only one cell or record (128, 256, 512 or 2048 bytes) and then releases the channel. All other processors are polled before this processor is polled again. Other loop 1 communication channels are designated as working channels and are assignable under control of a software system (device acquisition and control service) to other input/output devices. This concept allows many devices to make use of the available

#### system organization

communication channels. The communication channels are assigned to devices such as magnetic tape units, line printers, card readers, etc., only for the duration of time these devices are being used. Party line addressing of devices can be used to allow more than one device to use the same channel.

A 2-Mbps loop 1 channel may be subdivided to provide lower-rate communication channels. The channel subdivision may be accomplished directly on loop 1 or, more commonly, a single 2-Mbps loop 1 channel may be used to drive another loop, designated as loop 2, which then uses the subchannels to communicate with various devices connected to loop 2. Subchannel rates of 7.8125 kbps, 31.25 kbps, 62.5 kbps, 125 kbps, and 250 kbps may be achieved. Loop 2 channels are assignable under the control of device acquisition and control service similar to loop 1 working channel assignments.

In addition to data transfers, the time division exchange system is used to transfer service messages between processors and from processors to peripherals. Orderwire 1 is used for processor-to-processor service message transfer. Orderwire 2 is used for service message transfer between processors and some peripherals. The orderwire channels are subchannels of a loop channel. Orderwire 1 operates at 125 kbps and orderwire 2 operates at 7.8125 kbps. These channels are shared and use party line addressing to enable the device or processor to recognize a call.

#### 2.2.2 Processor

The C-8561A-2 processor consists of an arithmetic logic and control unit, communications service unit, a multiplex service unit, from two to four magnetic core storage units, a processor service unit, and a transfer link.

#### 2.2.2.1 Arithmetic Logic and Control Unit (ALCU)-8561A-2

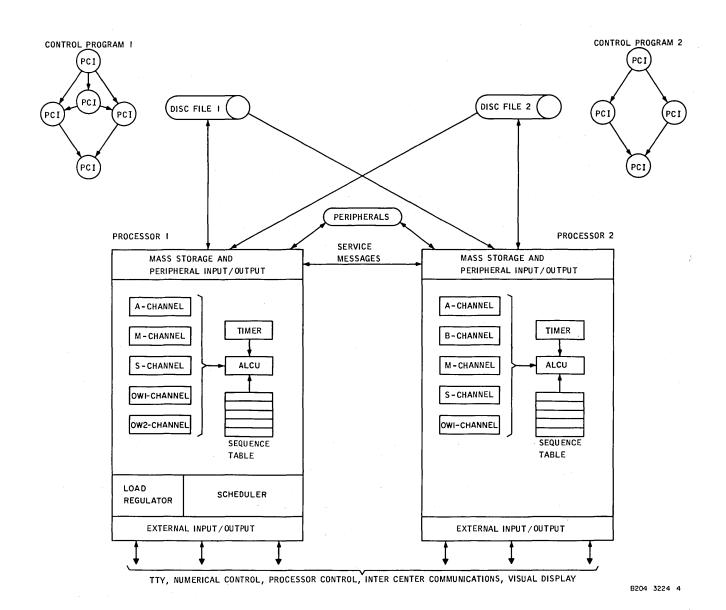

The arithmetic logic and control unit (figure 2-1) operates at 8 MHz and has a typical instruction execution time of 2.9 to 5.6  $\mu$ s, including memory access. A total of 72 instructions is available, 65 fixed-wire and 12 executed in a trapped mode. An optional algorithm unit allows hardware execution of all floating point instructions and fixed point multiply and divide.

The arithmetic logic and control unit (figure 2-1) uses a 32-bit accumulator called the A accumulator, a 32-bit accumulator called the B accumulator, or a combination of both, called the D accumulator. Three 18-bit index registers provide storage for address modifiers used in indexing operations.

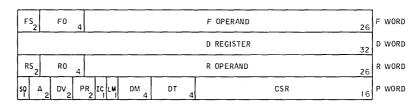

In the arithmetic logic and control unit, the three main registers communicate with the transfer link through input and output commutators. These are the function register, F, the memory exchange register, Z, and the memory address register, S. The F register holds the 14 bits of the instruction that include the operation code and control bits. This register interfaces with the instruction decoding control and timing circuits. The Z register, 32 bits in length, receives or transmits one word in parallel to the transfer link. All data to or from memory passes through the Z register. The S register, 18 bits in length, transmits the address of each memory word to be accessed through the transfer link.

The P register serves as the program counter or Instruction Address Counter (IAC). This register, 18 bits in length, holds the address of the next instruction to be executed in the program. The instruction address counter increments by 4 to skip from one instruction word to the next (memory is organized with byte addressability).

The 32-bit M register serves as temporary storage for data from the other registers during the machine cycle.

#### 2.2.2.2 Magnetic Core Storage

The C-8561A-2 processor memory has a  $2-\mu s$  cycle time and an access time of 510 ns. It is expandable from two to four modules. Each module has a capacity of 65,536 bytes, giving a maximum capacity of

Figure 2-1. 8561A-2 Arithmetic Logic and Control Unit.

262,144 bytes for one processor. In addition to load or unload memory cycles, the unit has the capability of performing an unload-modify-load function in one memory cycle.

Each module in the memory has its own address and data buffers and it is possible for all four modules to operate concurrently. The alcu, communication service unit, processor service unit, and multiplex service unit may all request the use of the memory independently. If four units request the access of different memory modules, the entire memory can be in operation at the same time. The transfer links operate at a speed that makes this possible; together they can perform the four transfers of 32 bits in 2  $\mu$ s.

#### 2.2.2.3 Communications Service Unit

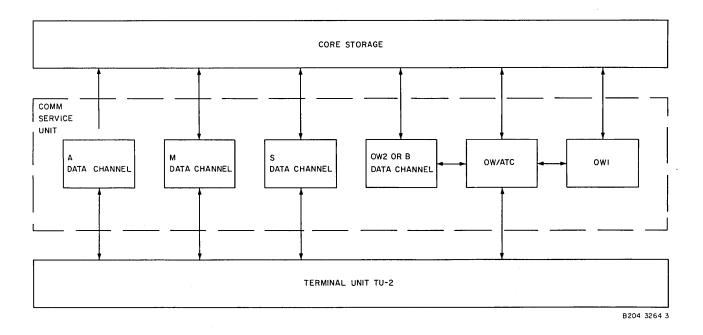

The communications service unit and associated terminal unit (figure 2-2) provide six independent data channels to the time division exchange; all channels may operate simultaneously. One of these data channels, the absolute time clock channel, is used to transmit clock signal from the loop synchronizer to all processors in a center. This information is transmitted every 7.8 ms and stored in a fixed location

Figure 2-2. Communications Service Unit.

in main core storage for use by system programs. Another data channel is used exclusively for orderwire 1 data channel transmission of service messages between processors. Three of the four remaining data channels are dedicated to the processor channels (programming channels) for communication between programs executed in the processor and peripherals connected to the time division exchange loops such as disc files, card readers, printers, etc. The sixth data channel is used by either the orderwire 2 or the B processor channel. One processor in a center is responsible for orderwire 2 functions including assignment of time division exchange working channels to magnetic tape units and loop 2 devices and necessary control messages to these peripherals. In the remaining processors in the center, this channel is used to support B channel processing.

The communications service unit has direct access to core storage through the processor transfer link. Data records to files and messages for other processors are read from and written to core storage directly under communications service unit control. To instruct the communications service unit, the arithmetic logic and control unit builds device control messages which are 9-word instruction packets in core which the communications service unit reads and executes. The instruction packets contain device control information and core location information for data and status. Once a device control message is built for an input/output transaction or a processor message transfer, the arithmetic logic and control unit is free to continue other work while the communications service unit executes the required information transfer.

#### 2.2.2.4 Multiplex Service Unit

The multiplex service unit drives the serial multiplex loop at 1.2288 Mbps and inserts appropriate synchronizing pulses into the bit stream to identify 256, 4.8-kbps time slots. The time division multiplex loop provides word-interlaced channels that allow simultaneous access between a processor and the medium- or low-speed devices connected to the time division multiplex loop.

All devices on the time division multiplex loop are managed independently and simultaneously, so that each device may be in an arbitrary state of completion with respect to all other devices. This mode of operation is particularly suited to the requirements of many low-speed devices, such as teletypewriter inquiry stations and CRT display devices.

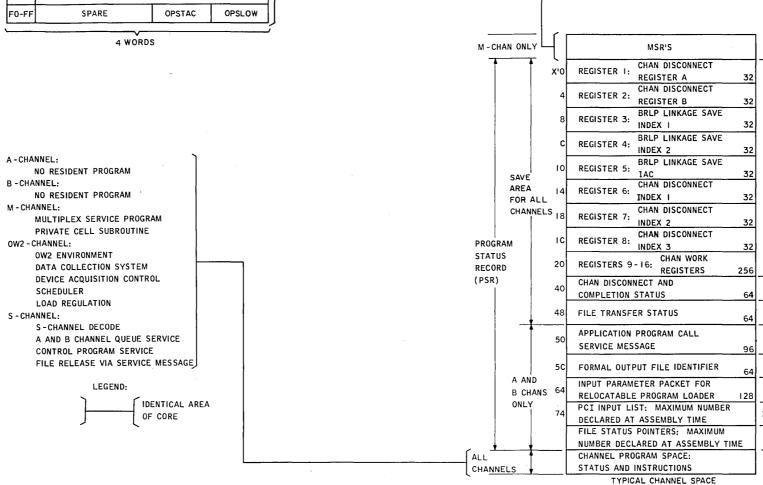

The multiplex service unit allows a device on the time division multiplex loop to communicate with the arithmetic logic and control unit by requesting processor service. The multiplex service unit directs the transfer of data between devices and core storage through the transfer link without arithmetic logic and control unit intervention once the arithmetic logic and control unit has set up the transaction. The multiplex service unit also alleviates the arithmetic logic and control unit of the routine task of monitoring devices on the time division multiplex loop for service requests. When a device needs processing time, an appropriate indication is placed in work queue serviced by the arithmetic logic and control unit. The indicator points to a multiplex status record corresponding to the device requiring service. The multiplex status record is used by the arithmetic logic and control unit and the multiplex service unit to transfer information. A multiplex status record is a 4-word table located in core storage. Each active multiplex status record contains sufficient information for the arithmetic logic and control unit to accomplish the task required by the device. Typical arithmetic logic and control unit tasks include the management and allocation of core storage used for time division multiplex loop data buffers. the transfer of records to and from disc files, and the execution of special device-oriented subroutines. Devices on the time division multiplex loop initiate all communication with their associated processor by transmission of the proper instructions to the multiplex service unit. When a device on the time division multiplex loop is idle, it accepts output information from the computer.

#### 2.2.2.5 Processor Service Unit

The processor service unit performs the functions of controlling initial program loading of the processor, initiating processing, and performing selected diagnostics on processor units. The processor service unit has interface connections with the communications service unit, multiplex service unit, transfer link, arithmetic logic and control unit, terminal unit, and main core storage.

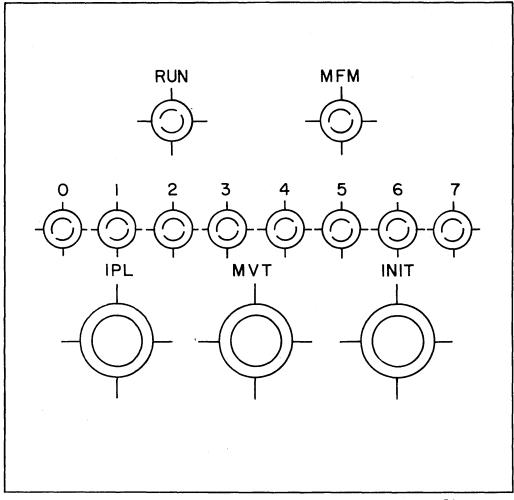

The processor has three manual operating controls which are contained on the front panel of the processor service unit (figure 2-3). The IPL button starts the automatic initial program load sequence, which loads programs from the time division exchange loop. During initial program load, the memory protection feature is overridden. The Initiate(INIT) button initializes the arithmetic logic and control unit without loading a program. Lamps on the panel of the unit indicate that the processor is operating normally (RUN) or that it has failed (Machine Failure Monitor, MFM). An 8-bit lamp-bank indicates which processor function has failed during an initial program load. Upon successful completion of an initial program load, these lights are under program control. The Marginal Voltage Test (MVT) button allows for marginal voltage testing.

The processor service unit controls certain operations of all processor units. These include enabling the arithemetic logic and control unit and communication control equipment, enabling diagnostic mode to all units, controlling marginal voltage tests, forcing memory parity errors in all memory modules, disabling protected memory, controlling interleaved memory mode, and displaying status via the 8-bit lamp-bank on the front of the processor. These functions are controlled by the processor service unit during an initial program load or initiate sequence. After a successful initial program load or initiate, these functions are under the control of software. Every time the arithmetic logic and control unit executes a reset machine failure monitor instruction, the processor service unit will set the above functions to reflect the bits in memory location X'40. This word is referred to as the processor control word.

The processor service unit maintains a processor status word in memory location X'44. This word contains the current status of the fault alarms of all processor hardware.

#### 2.2.2.6 Transfer Link

The transfer link provides the switching for all communication from the arithmetic logic and control unit, multiplex service unit, communications service unit, and processor service unit to core storage. The transfer link performs memory module decoding, resolves contention for a memory module, checks for an invalid address, performs memory protection decoding, gates addresses and data to the memories, and returns data from the memories to the requesting device. A single transfer link module has two source ports and four memory ports permitting two simultaneous paths of communication between two

B204 3265 2

Figure 2-3. Processor Service Unit, Controls and Indicators.

logic modules and any two of four memory modules connected to the transfer link. Up to four logic units may be connected to any of the transfer link module source ports. Also, up to four transfer link modules may be connected in parallel by busing together the memory ports thus allowing eight source ports. If both source ports from the same transfer link attempt to access the same memory module at the same time, the transfer link resolves the conflict on a first in, first out basis. For systems employing more than one transfer link module, a weighted priority between transfer link modules is established by means of the priority interconnect between the boxes.

#### 2.2.3 Disc Files

Two Collins disc files are available for use in the C-System. One is a high-speed, direct-access storage device with a storage capacity of 130 megabytes of data on 26 discs. The unit has an average head positioning time of 93 ms with a 25 ms minimum and 185 ms maximum plus a track verification check requiring 35 to 45 ms. The nominal disc revolution time is 50 ms. There are 81,920 bytes of storage available at 10 fixed-head addresses. Data transfer is serial by byte at a rate of 173,000 bytes per second.

The second unit is a high-speed, random-access device with a storage capacity of 33.5 megabytes on 8 discs. The average head positioning time for this device is 18.4 ms with a 6 ms minimum and 30 ms maximum. The disc revolution time is 25 ms and the data transfer rate is 350,000 bytes per second.

#### 2.2.4 Magnetic Tape Units

The 9-channel magnetic tape unit operates with 1/2-inch magnetic tape. The unit reads in the forward and reverse tape directions and writes in the forward direction at 150 inches per second; the rewind speed is 250 inches per second. Data is stored at a density of 800 bits-per-inch per channel. Eight channels are used for data and one for parity. The data transfer rate is 120,000 bytes per second.

The 7-channel magnetic tape unit operates with 1/2-inch magnetic tape. The unit reads and writes in the forward direction at 150 inches per second; the rewind speed is 360 inches per second. Data is stored at a density of 200, 556, or 800 bits-per-inch per channel. Six channels are used for data and one for parity. The data transfer rate is 30,000, 83,000, or 120,000 bytes per second.

#### 2.2.5 Peripheral Devices

The C-System provides the following optional peripheral devices: card readers, card punches, operator printers, line printers, and CRT display and entry stations. These devices connect to time division exchange loop 2 through TU-3B terminal units.

#### 2.2.6 Time Division Multiplex Loop

The time division multiplex loop provides connection of a large number of low-speed devices to a single computer within the C-System. The loop is physically a coaxial cable which interconnects the various devices in a serial manner and terminates at the multiplex service unit. The basic data rate on the loop is 1.2288 MHz. In contrast to the time division exchange system which is bit interlaced, the time division multiplex loop operates with word interlacing with 256 words (36 bits each) in one frame resulting in a frame length of 9216 bits. Each time division address corresponds to a device channel; the channels are not reassignable as in the time division address is used to identify the channel words in the loop. Data is inserted and extracted from the channels by the multiplex service unit and devices. A device may be assigned 1, 8, 16, or 32 time division addresses, providing effective channel bit rates of 4.8 kbps, 38.4 kbps, 76.8 kbps, or 153.6 kbps.

The multiplex device coupler provides a standard interface to devices on the time division multiplex loop. The multiplex device coupler performs the functions of time division address recognition, serial extraction and insertion of data into its assigned time division address channel, and logical interpretation and generation of the supervision necessary to communicate with the multiplex service unit.

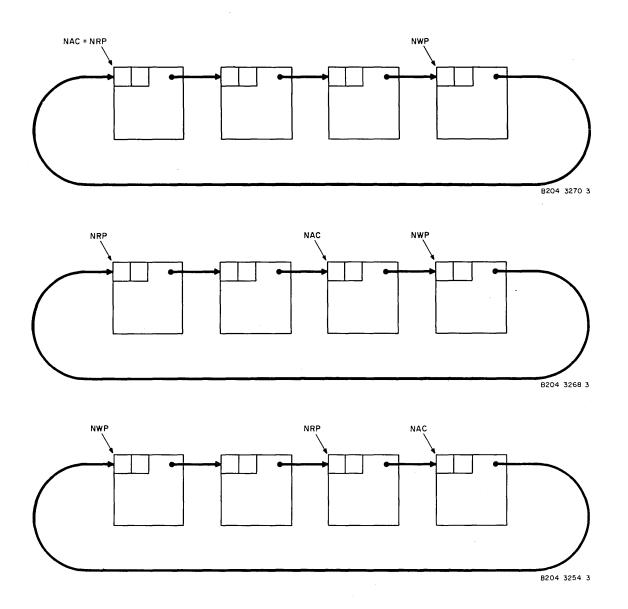

The loop word format for each of the 36-bit time division addresses consists of a 4-bit supervisory code field and 32-bit operand. The supervisory field contains the supervising codes for multiplex service unit to multiplex device coupler communication. The operand contains the instructions, data, parameters, etc., for the device and programs.

#### 2.3 SYSTEM SOFTWARE ORGANIZATION

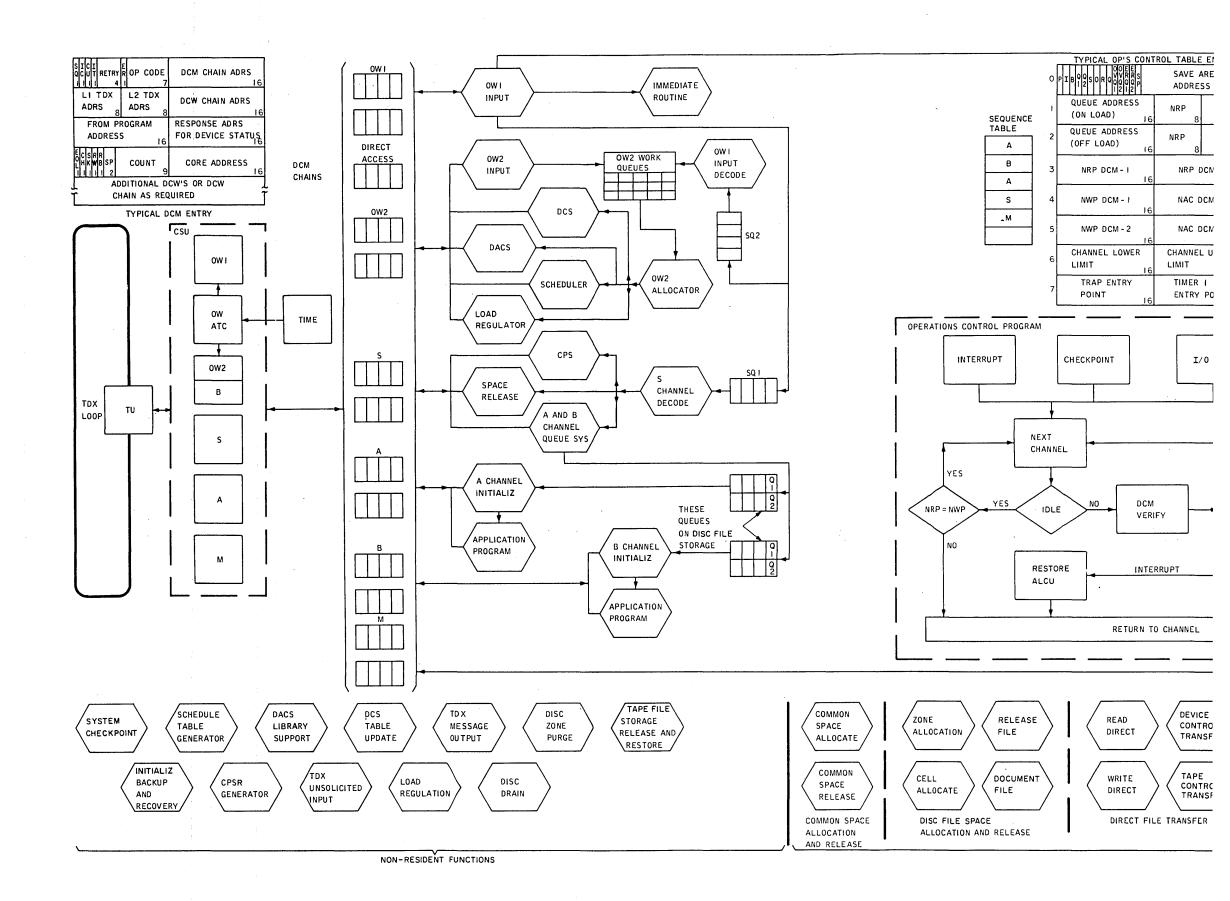

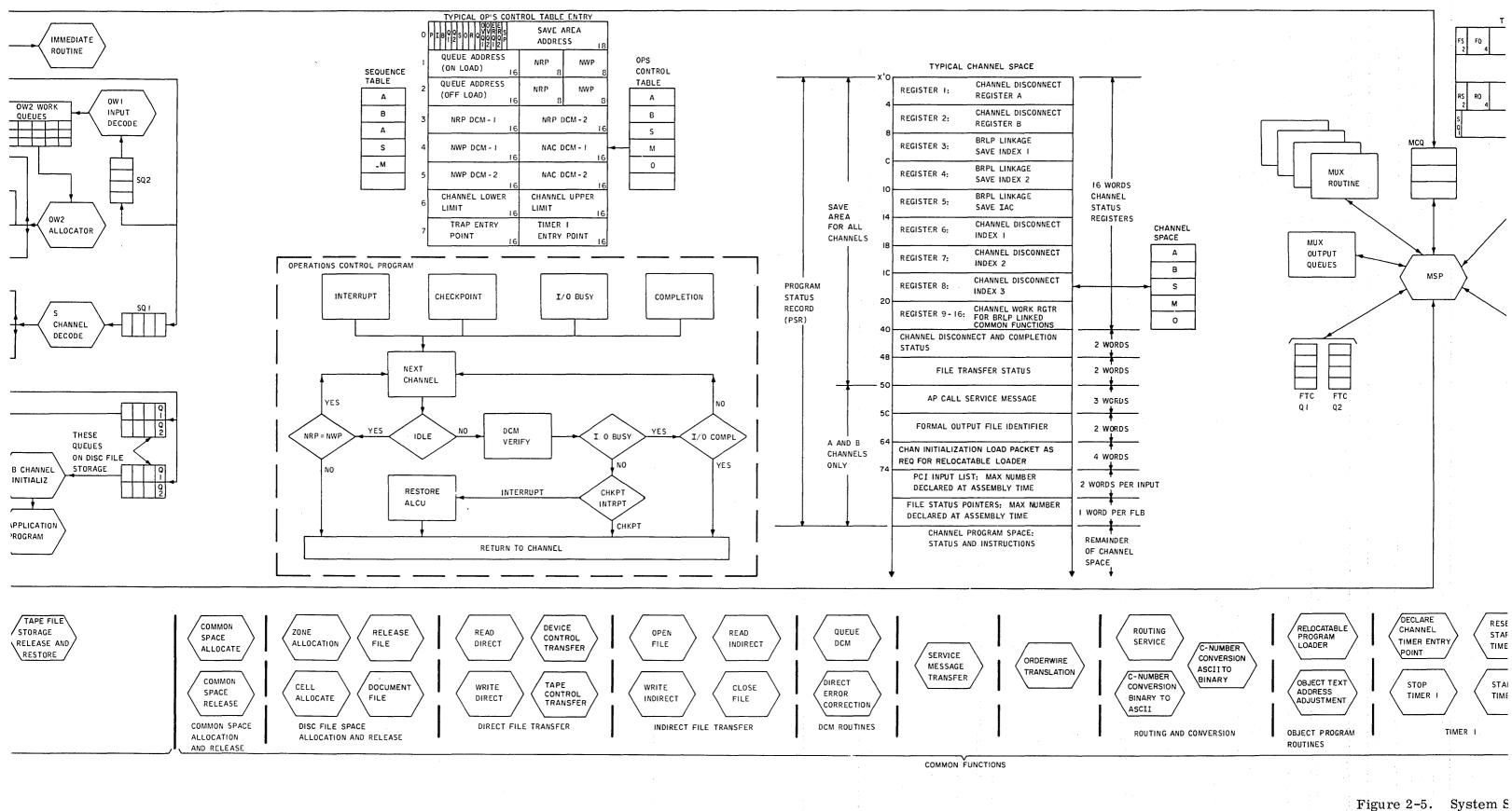

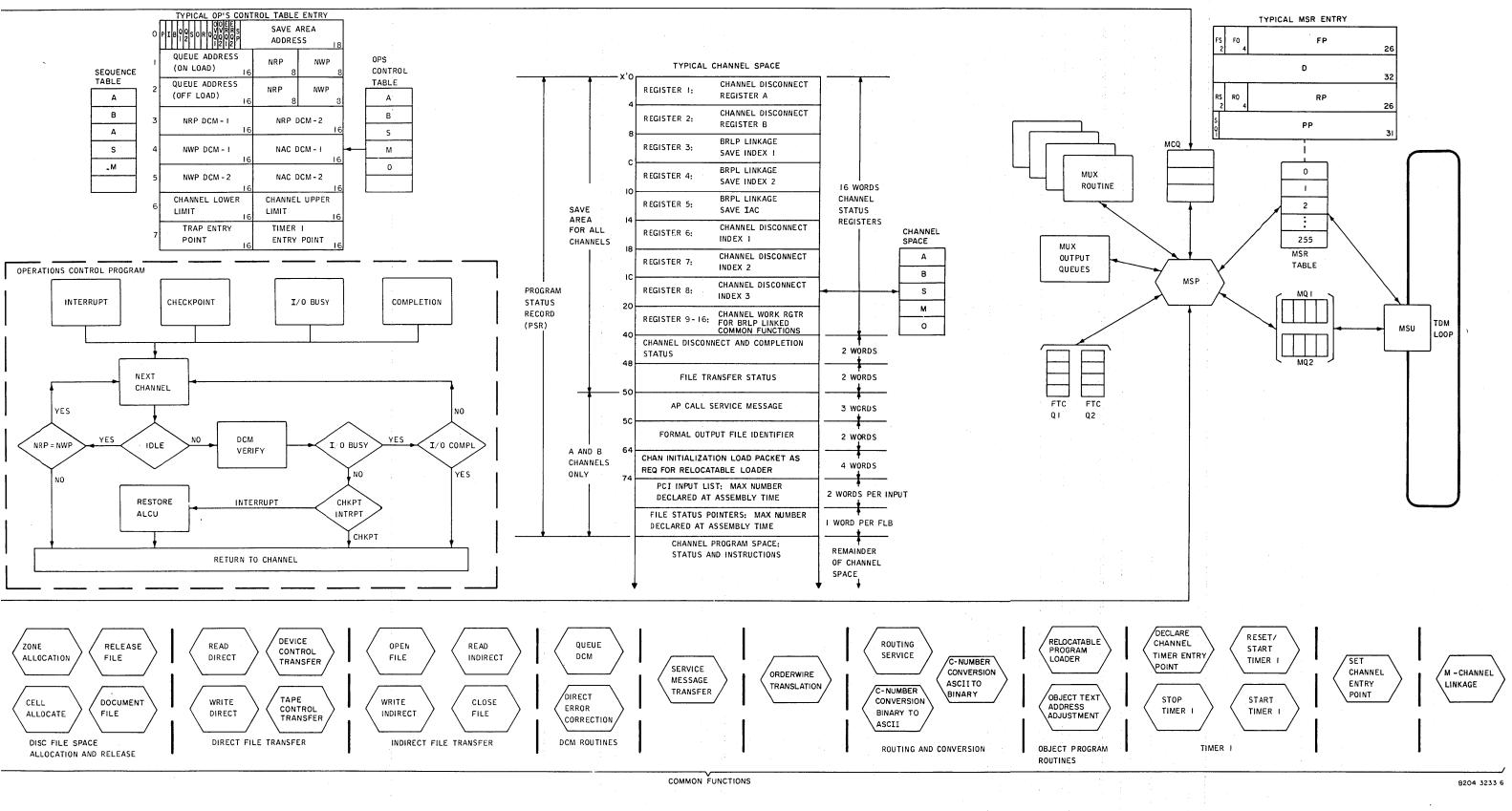

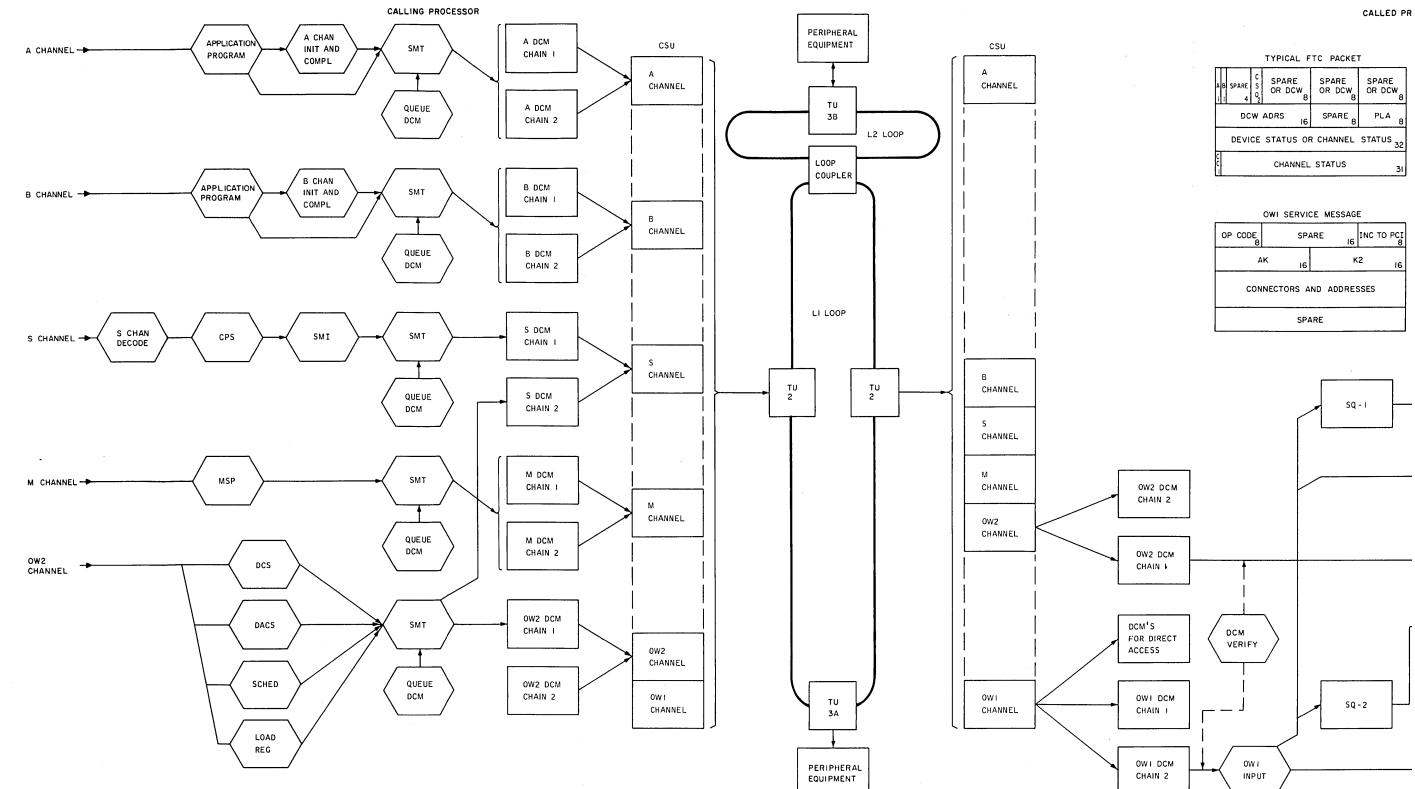

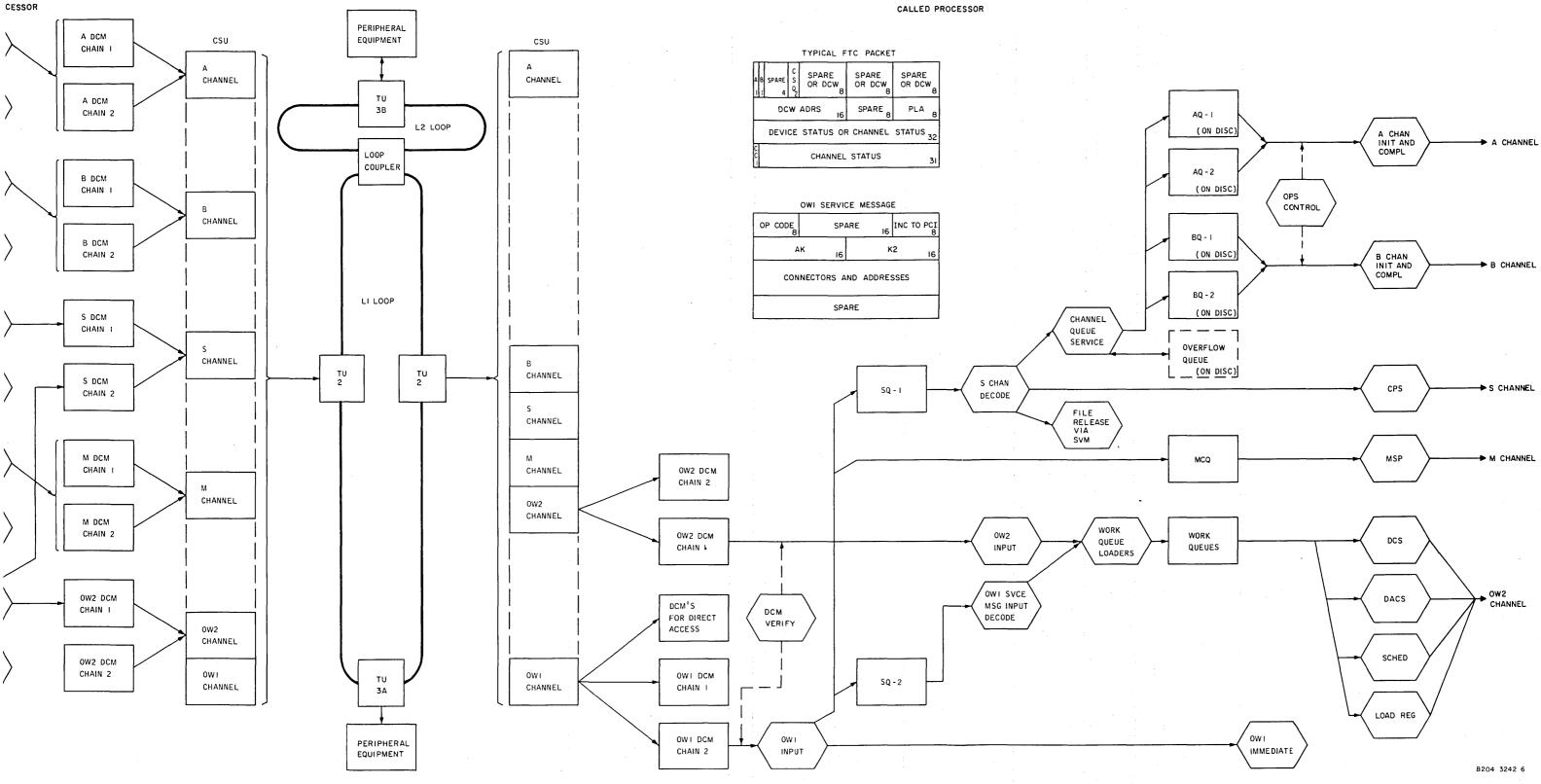

Figure 2-5 shows the general flow and interrelationships between the major software elements of the system. All software elements shown in figure 2-5 do not reside in each processor. Orderwire 2 resides in only one processor in a center and that processor normally has no B channel. The exact core allocation depends on the core space required by the M channel and is defined for each center configuration.

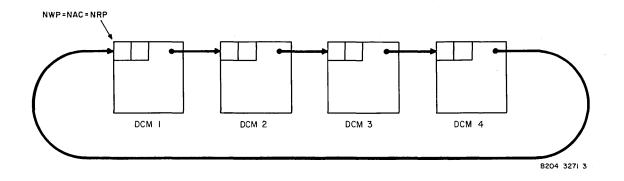

#### 2.3.1 Time Division Exchange (TDX) Communication

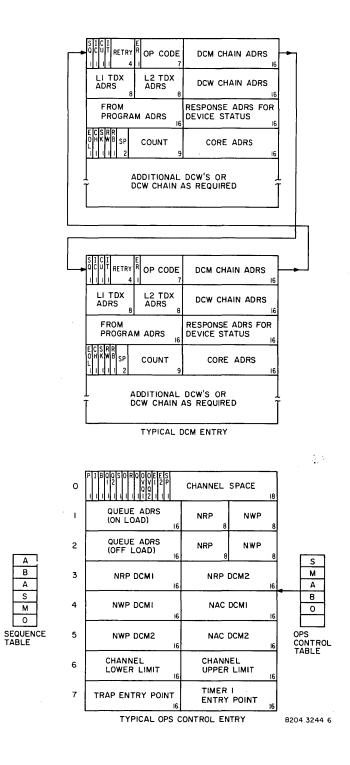

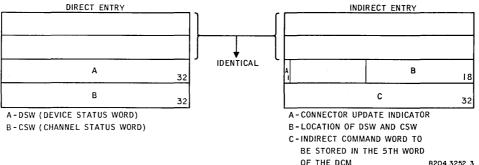

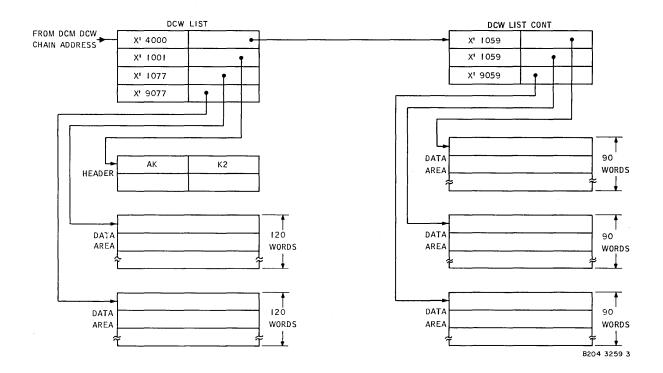

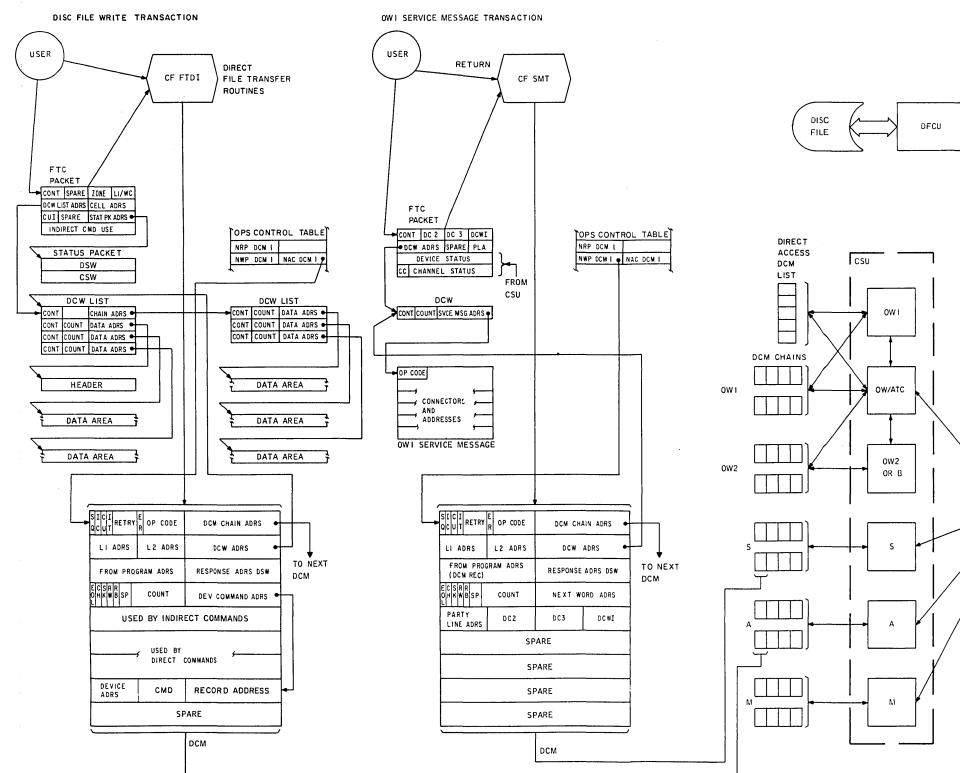

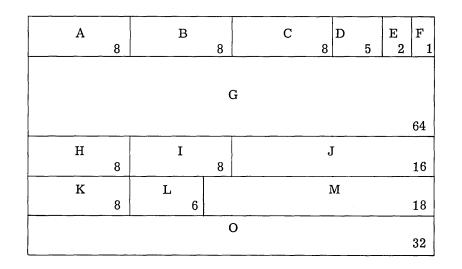

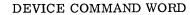

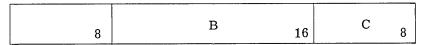

Communication between the communications service unit data channels and programs running in the processor channel is by means of Device Control Messages (DCM's) which are built by system programs on each of the various channel time. Device control messages are instruction packets directing a data or message transfer; the communications service unit reads and executes the packets. As shown in figure 2-5, each processor channel has two device control message chains; a typical device control message is shown in the upper left-hand corner. There are an arbitrary but fixed number of device control messages in each chain and the entire chain is in a fixed location in core storage with each device control message having a fixed starting address. Each device control message in the chain contains a device control message chain pointer to the next device control message in the chain with the last pointing to the first, thus forming an endless chain. The two device control message chains for each processor channel are serviced alternately by the corresponding communications service unit data channel, with one device control message per chain being serviced on each chain access by the communications service unit.

The actual data and message transfer on the time division exchange system takes place strictly under terminal unit and communications service unit control through execution of the device control message chains. The transfer does not involve the arithmetic logic and control unit except for building the device control messages, data control words, device control words, and monitoring device control messages for transfer completion.

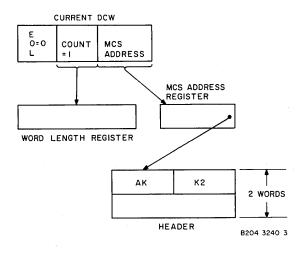

Data Control Words (DCW's) are appended to device control messages. Data control words contain control bits defining the nature of the data or message transfer and the core address of the data to be transferred or the area into which data is to be read. Data control words are also used to point to device command words that identify, for example, the read or write function and the address of a disc file record. A data control word can be used to identify another list of data control words not appended to the device control message but to be executed with this device control message. If such a data control word is encountered in executing a device control message, the data control word chain address is placed in the third and fourth bytes of the second word of the device control message and this address is branched to at an appropriate place in the execution of the data control word list.

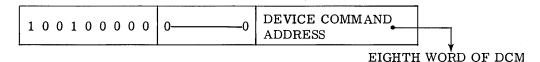

The first word of the device control message contains certain control bits and the device control message chain address pointing to the next device control message in the chain. The second word contains the loop 1 and loop 2 time division exchange address of the device which communication is to be established and two bytes for a data control word chain address. The third word contains a from-program address, which references a program that is branched to in the event of an error and that may be given immediate control upon verification of completion of this device control message. This word also contains the response address for storage of device status at completion of the transfer. The fourth word of the device control message is the first data control word to be executed in the transfer.

In addition to the device control message chains for each channel, each processor core has a set of prebuilt device control messages and data control word lists which reference certain tables in the processor core for direct access by the load regulation program via orderwire 1 service messages. In general, a pair of device control messages and data control words (one for reading and one for updating) is required for each table to which the load regulator has access.

#### 2.3.2 Operations Control Program

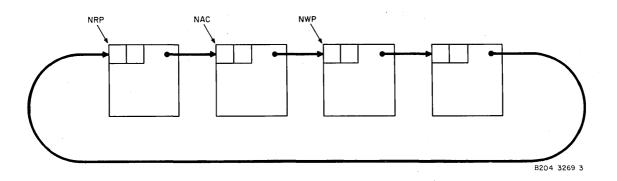

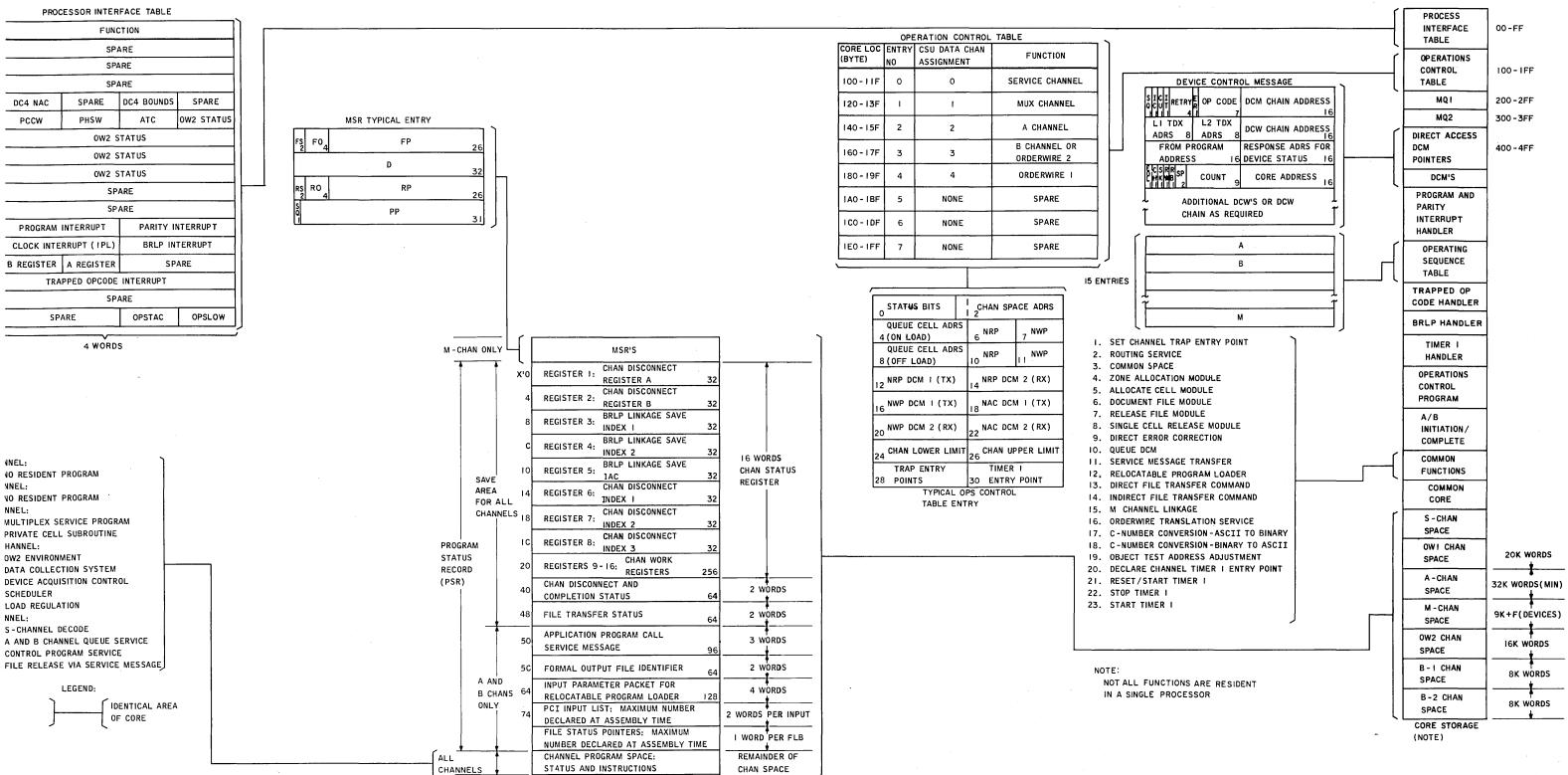

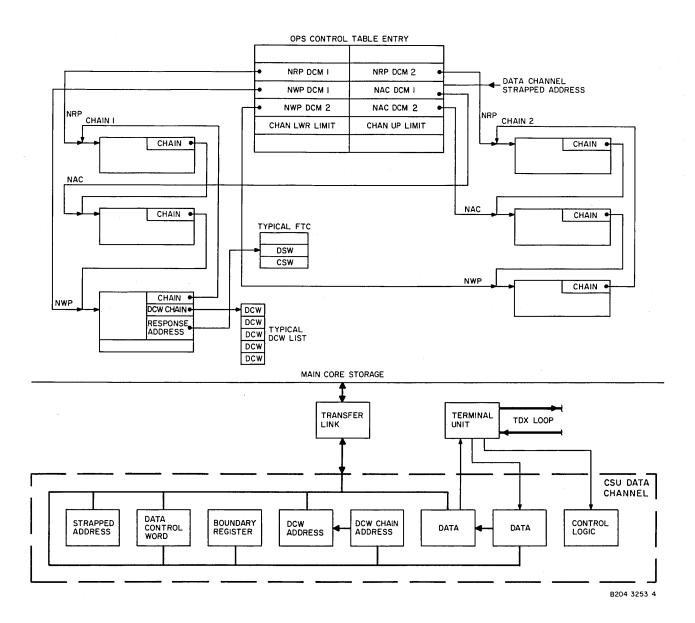

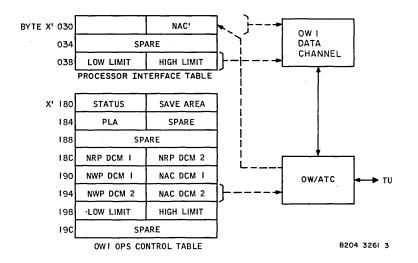

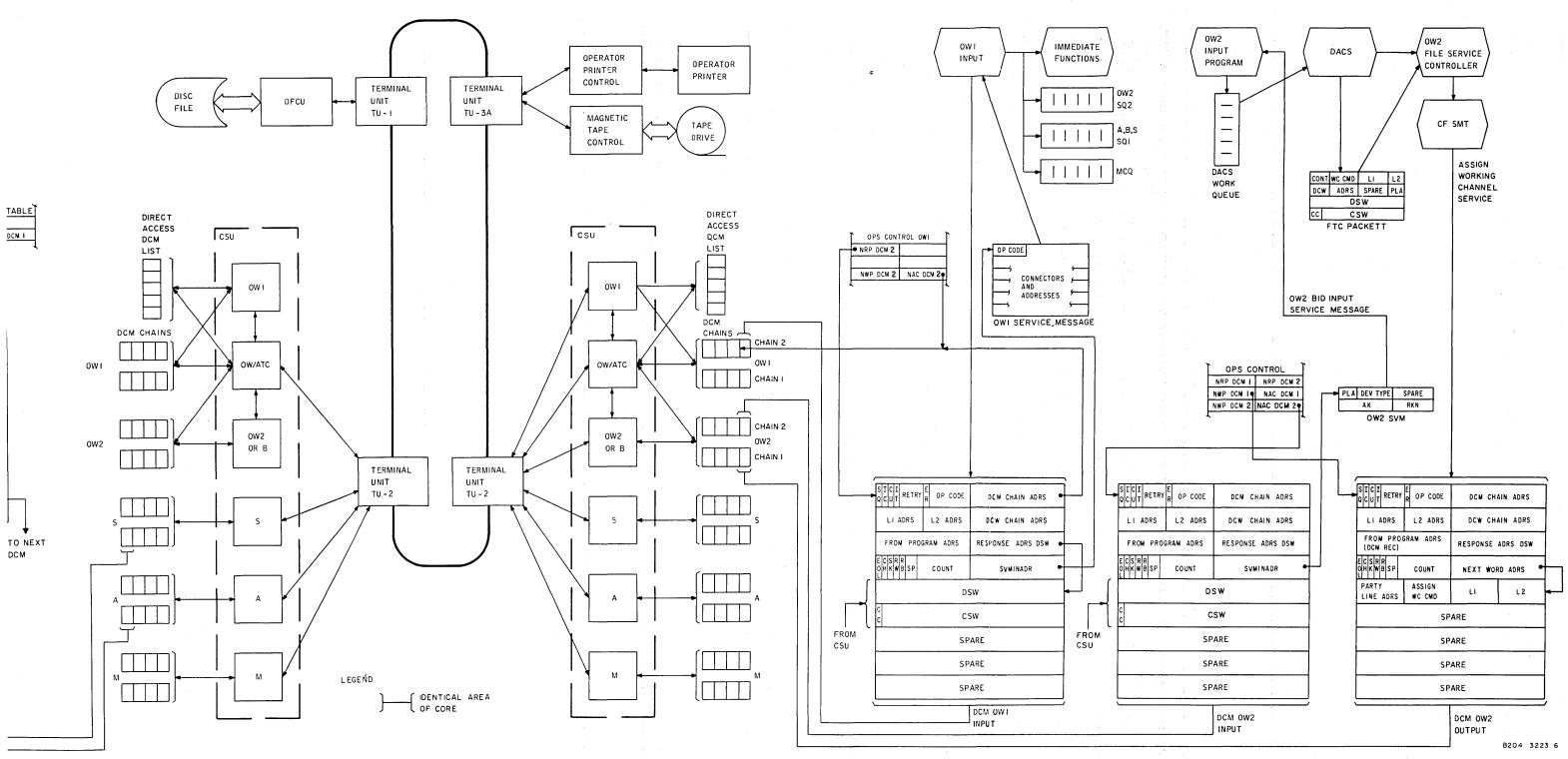

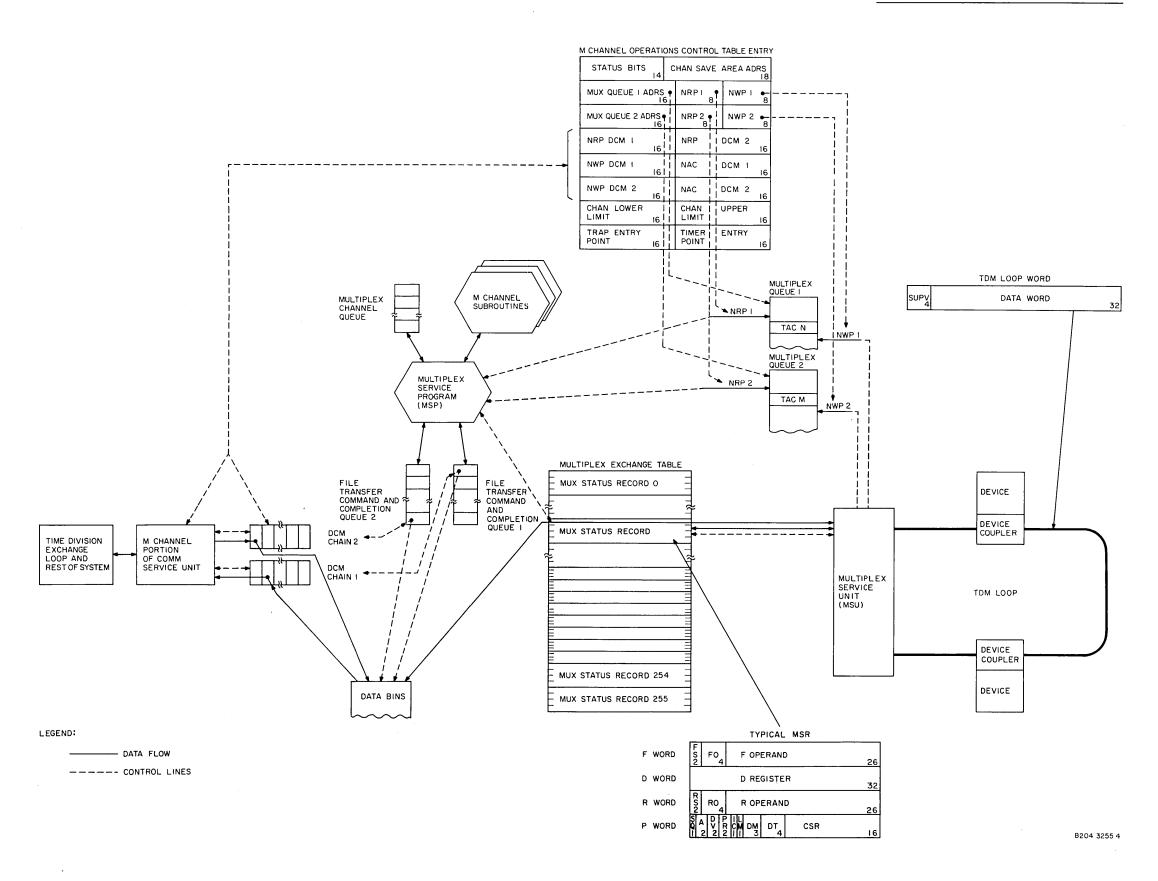

An operations control table exists in core storage with an 8-word entry for each resident processor channel. A typical entry is shown in figure 2-5. The first word contains channel status bits and the address of the channel save area. A typical save area is shown in figure 2-5. The save area is located at the beginning of the processor channel space and is part of the program status record. The second and third words of the operations control table entry identify the location of the channel work queues and the next-write-positions and next-read-positions for these queues. The Next-Write-Position (NWP) pointer is the next place in the queue to post a request for work; the Next-Read-Position (NRP) pointer

is the next entry in the queue to be executed by the channel programs. The next three words in an operations control table entry are device control message chain pointers for chains 1 and 2. The next-readposition pointer is the next device control message to be checked by the operations control program for completion; the next-write-position pointer is the next device control message which can be used to post an input/output request, and the Next Available Cell (NAC) identifies the next device control message to be executed by the communications service unit.

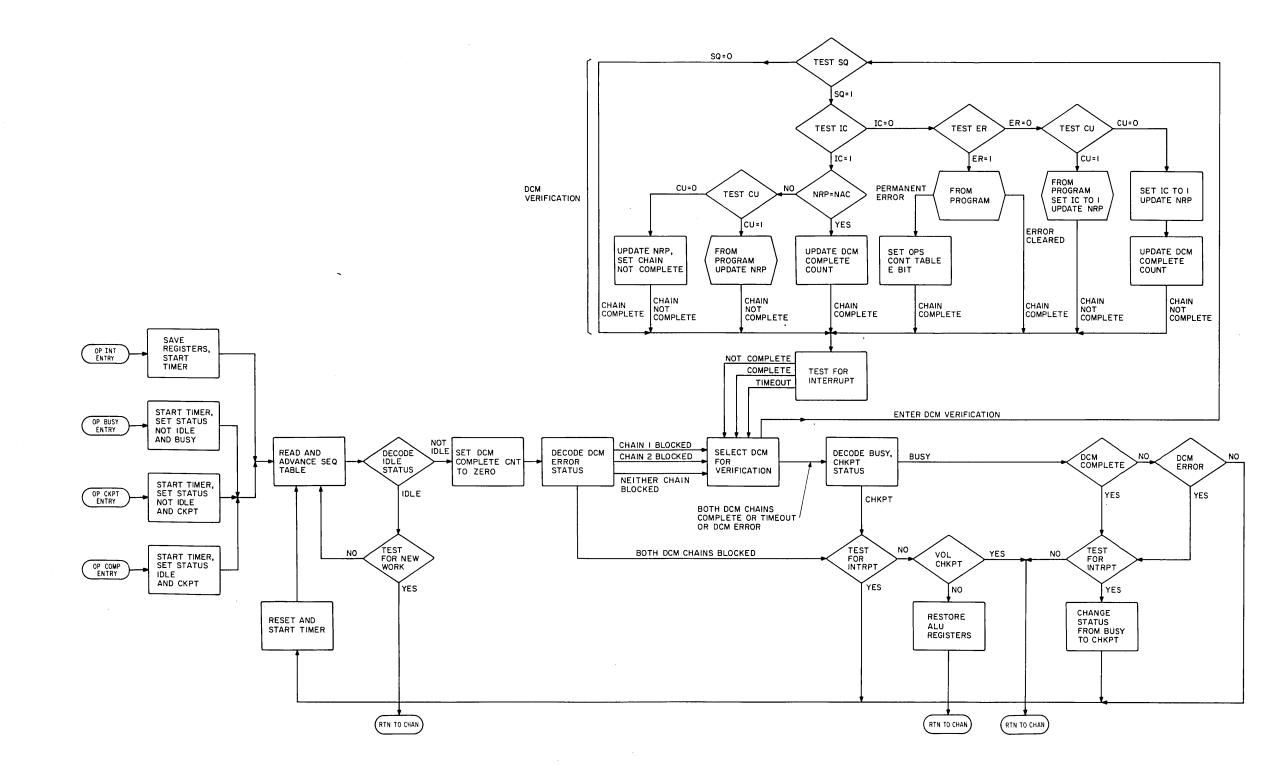

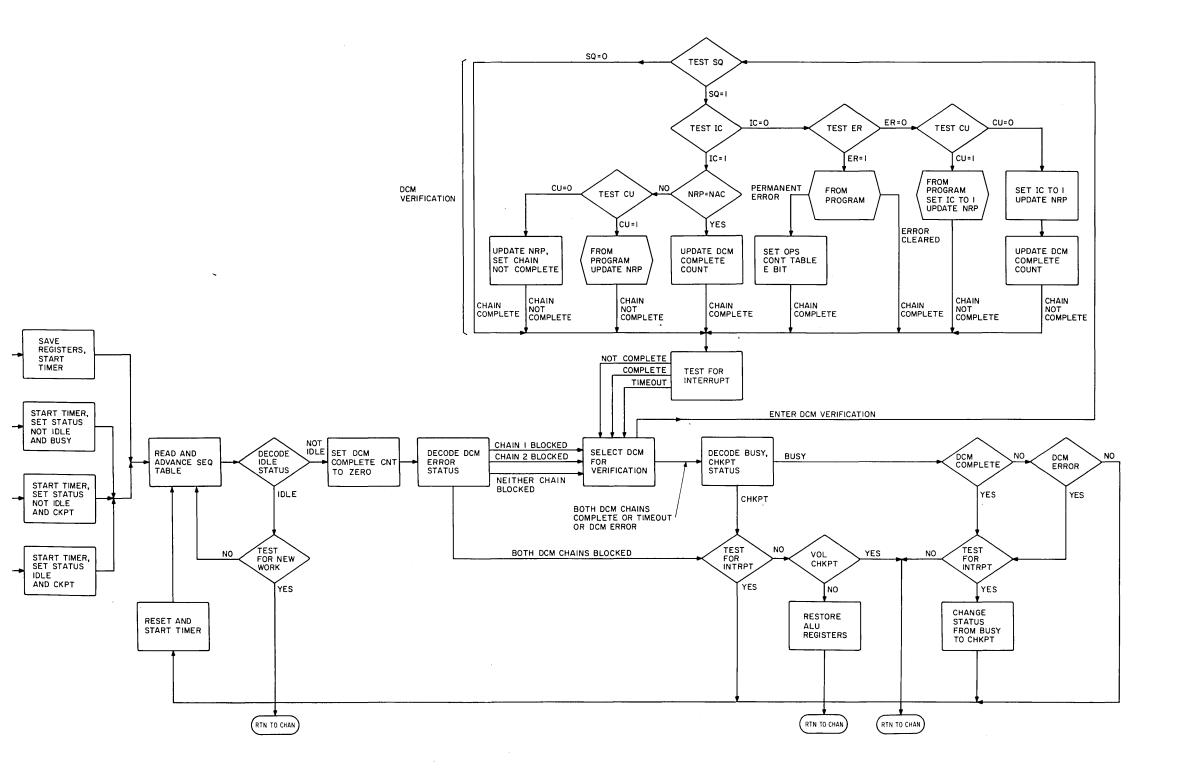

The operations control program, shown in the center of figure 2-5, is the resident software system responsible for allocation of arithmetic logic and control unit time and verification of device control message chains for completion of input/output requests. The operations control program can be entered from a given channel in one of four ways: (1) the channel may run to completion and exit to operations control (OP COMP) in which case the second bit, I, in the operations control table is set to idle and a return address saved; (2) the channel may disconnect busy (OP BUSY) awaiting an input/output completion in which case I is set to not idle and the third bit, B, of the status word in the operations control table is set to busy and a return address saved; (3) the channel may voluntarily relinquish the rest of its time when certain conditions are met in the program execution in which case I is set to not idle and B to checkpoint and a return address saved; or (4) the channel may be interrupted by the interval timer in which case I is set to not idle and B to checkpoint and all arithmetic logic and control unit registers saved in the channel program status record so that the channel may resume processing the next time it gains control of the arithmetic logic and control unit. All methods of entry to the operations control program are used by the A and B channels but, under normal operating conditions, the M and S channels only use entries 3 and 4 while orderwire 1 and 2 channels only use entries 2, 3, and 4. The operations control program works with the operations sequence table which indicates the sequence in which the channels are to be given time. This sequence is arbitrary and may be any order depending on the processing task. Upon entry, the operations control program examines the sequence table for the next channel to service. The idle bit is then checked to determine the channel status. If the channel was idle, the next-read-position pointer and next-write-position pointer for the channel work queues are compared to determine if any channel work has been posted since the channel last had control. If the next-readposition pointer does not equal the next-write-position pointer in either queue, then work is available and operations control exits to the channel. If the next-read-position pointer equals the next-writeposition pointer, no work is required and the operations control program checks the sequence table to determine the next channel to be given time. Only the A and B channels use this test since only these channels enter operations control as idle. The other channels manage their own work queues, using the next-read-position and next-write-position as appropriate.

If the channel was not idle the last time it had control, operations control proceeds to verify device control messages for completion on that channel. By monitoring the status bits in the device control messages for the particular channel, the operations control program can detect whether or not any input/ output requests have been completed. The B bit of the status word of the operations control table can then be checked to determine if the channel was awaiting a data transfer. If the channel was awaiting a data transfer and none has occurred, the channel is skipped and operations control returns to the sequence table; if at least one device control to the channel. If the channel had used the voluntary checkpoint as indicated by the third bit of the operations control table status word, control is returned to the channel program regardless if an input/output has been completed. Likewise, if the channel had been interrupted by the timer, the arithmetic logic and control unit is restored to its prior condition and control returned.

#### 2.3.3 Orderwire 1 Channel

Communication from processor to processor within the C-System is by service messages sent on the orderwire 1 party line communication channel of the time division exchange loop. The orderwire 1 input program has the responsibility of receiving these messages and dispatching them to appropriate work queues to be serviced by the processor on the time of the respective channels. The orderwire 1 input program manages its device control message chain for receipt of orderwire 1 service messages by providing a main core storage buffer for each device control message into which an incoming message

#### system organization

can be written. When orderwire 1 is indicated by the operations sequence table and the operations control program detects one or more completed device control messages in the orderwire 1 device control message chain, the orderwire 1 input program is given control. The orderwire 1 input program decodes the operation code of the service message. Certain service messages require immediate processor action. The orderwire 1 input program immediately initiates the appropriate routine called in the immediate service message. All other service messages are either directed to service queue 2, which is a work queue for the orderwire 2 channel, service queue 1 which is a work quoue for the S channel, or Multiplex Channel Queue (MCQ) which is serviced on M channel time. For service queue 1, service queue 2, and the multiplex channel queue, a pointer indicating the location of the service message in core is placed in the queue. The orderwire 1 input program reinitializes the device control message by obtaining a new bin for a service message. The orderwire 1 input program exits to the operations control program as busy awaiting an I/O when all device control messages have been reinitialized and does not receive control again until another device control message is complete. The orderwire 1 input program uses the voluntary checkpoint entry to operations control if buffer space is not available for assignment or if the work queues are full, ensuring return of control the next time orderwire 1 is indicated in the sequence table.

#### 2.3.4 Orderwire 2 Channel

Orderwire 2 channel time is used for execution of the scheduler, Data Collection Service (DCS), Device Acquisition and Control Service (DACS), and the load regulator. Requests for service for these channel programs are received from orderwire 1 service messages via service queue 2 and from service messages received via orderwire 2 used only by device acquisition control service. An orderwire 1 service message input decode program decodes the service messages from service queue 2 and posts them for various orderwire 2 channel programs. The orderwire 2 input program maintains input device control messages and service message bins for input service messages. When a message is received, the orderwire 2 input program places the message in a work queue and reinitializes the device control message for receipt of subsequent orderwire 2 service messages. Control is given to the orderwire 2 input program each time a channel program gives up control. A channel program gives up control after it performs a file service request or completes processing of a service message. The orderwire 2 allocator gives each channel, in turn, time to process provided the program is not waiting for the completion of a file service request. Each time the work allocator is given control, the work allocator allows only one function to run.

#### 2.3.4.1 Data Collection Service

Data collection service runs on orderwire 2 channel time and provides applied systems with a means of collecting, categorizing, and distributing raw input data from any point in the system. All data input to data collection service must have a preassigned data collection service code. A data collection service code is assigned by data collection service on receipt of a data collection service code request service message. All input files with the same data collection service code are maintained in a collection file. There is only one collection file per assigned data collection service code. The collection file is a file on disc that contains the input file identifiers for the files associated with a data collection service code. When a data collection service extract service message is received, data collection service returns via a program return service message the address of the collection file which the user may then access to obtain the location on disc or tape of the data needed.

#### 2.3.4.2 Device Acquisition and Control Service

Device acquisition and control service runs on orderwire 2 channel time and provides the application systems a means of communication between processors and magnetic tape units or loop 2 devices. Certain time division exchange loop 1 communication channels and all loop 2 communication channels are working channels shared among the various peripherals and must be assigned by device acquisition and control service upon request from an application system; it is the responsibility of device acquisition and control service to make these assignments. Device acquisition and control service operates in two modes: (1) the system mode and (2) the device mode. In the system mode, for example, an application program under control of a control program status record encounters a program control instruction requiring communication with a magnetic tape unit or a loop 2 device. An orderwire 1 service message is sent to device acquisition and control service to establish communication. The orderwire 1 input program directs the service message to service queue 2 where it is decoded by orderwire 1 input decode as a device acquisition and control service request. Device acquisition and control service processes the messages, assigns a working channel to the required device, builds an output file containing control data and device status, and identifies the working channel assigned to the device. A return service message is sent to the calling processor identifying the output file which it then accesses, obtains the working channel identification, and begins communication with the device.

In the device mode, device acquisition and control service receives an unsolicited orderwire 2 input message from a loop 2 device requesting to input data into the system. In this case, a program call service message is issued for a device acquisition and control service defined device-to-disc program which will store and forward the input data.

#### 2.3.4.3 Scheduler Program

The main purpose of the scheduler program is to control the initialization of application program systems or portions of application program systems as a function of time. Orderwire 1 scheduler call service messages are directed to the scheduler program through service queue 2 and the orderwire 2 allocator. The service message identifies the orderwire 1 time division exchange party line address of the calling processor, the time the application system is to be initiated, a priority code, and the disc file storage address of the application system control program status record. The received service messages are placed in one of four priority queues in order of activation time by a table generator program which is a nonresident program that runs on a scheduled basis on A or B channel time. Thus, received service messages are placed in a queue to be serviced later by the table generator program if their execution time is later than the next scheduled run of the table generator program; otherwise, the service message is tabled in an advanced activation cell and can be operated on by the scheduler without being filed by the table generator program. When the scheduler program is executed, the current time obtained from the absolute time clock storage location is compared to the activation time specified in the first service message in each queue. If the current time is greater than or equal to the activation time, a return service message is sent via orderwire 1 to the calling processor indicating time to activate the scheduled program.

#### 2.3.4.4 Load Regulation Program

The purpose of the load regulator program is to automatically regulate the work load in the various processors in the system. The load regulation program is executed in the orderwire 2 channel of one processor in a center and dispatches direct access service messages to the various processors in the center. The communications service unit orderwire 1 data channel hardware recognizes the service messages as direct access messages and executes the prebuilt direct access device control messages and data control word lists which reference particular parameters in core storage to be returned to the load regulator. Having sampled each processor, the load regulator program can detect any undesirable distribution of work that may exist in the various channel work queues throughout the center. If such an undesirable balance is detected, the load regulation program will dispatch additional immediate access messages to change dispatch parameters utilized by the various processors in assigning program control instructions for execution.

#### 2.3.5 S Channel

The S channel is used to execute several processor service programs. S channel decode is the program which directs the activity of the S channel by decoding service messages pointed to in service queue 1. The operation code of the service message is mapped to the S channel decode table for the appropriate S channel program entry address, and control is passed to the S channel program. If, in the course of executing an S channel program, it is necessary to checkpoint the program for any input/output, the device control message requesting the transfer is posted, an entry made in an S channel completion

#### system organization

chain, and control is returned to S channel decode rather than the operations control program. This allows other S channel programs to execute as required on remaining S channel time. S channel decode always uses the voluntary checkpoint entry of the operations control program, unless a timer interrupt forces relinquishing channel time. When S channel decode is entered from either operations control or an S channel program, it always checks its completion chain first to determine whether or not any requested input/output transactions have been completed. If they have, control is transferred to the program requesting the transfer. After the entire completion chain has been checked, service queue 1 is checked for service messages directing further work.

#### 2.3.5.1 Control Program Service

Control Program Service (CPS) runs on S channel time, is resident in each processor in a center, and is responsible for the supervision of the execution of control programs assigned to that processor. Control programs represent the technique utilized in the C-System for implementing input-directed control for automatic and regulated execution of application system programs in a multiprocessor center. Control programs are physical lists of program control instructions each of which identifies a particular segment of the overall system for execution. The program control instruction also identifies any input files required for execution of the program and points to other program control instructions in the control program that require the execution of this program control instruction before being executed. The program control instruction identifies files which can be released after completion and also contains various control parameters required by control program service in the execution of the control program.

It is possible for program control instructions to call lower level control programs resulting in a nested control program structure. Note that control program service does not manipulate files or the application system programs themselves, rather, it directs the execution of these programs and manipulation of these files through orderwire 1 service messages. For example, if during the execution of a control program the necessary conditions have been satisfied enabling a certain program control instruction to be executed, control program service causes the transmission of an application call service message to a processor in the center. The service message identifies the disc file storage address of the calling control program status record. The service message also identifies the A or B channel work queue to be used. This service message is queued in the appropriate A or B channel work queue of the called processor. When it is reached, the calling control program status record is read from disc file storage and the invoking program control instruction isolated. The program control instruction identifies the application program which is to be accessed and executed using the input files identified in the program control instruction as necessary. Upon completion of the program, a program return service message is sent via orderwire 1 to the calling processor noting the completion and identifying any output files created during execution of the program. Control program service in the calling processor receives this message, updates the control program status record, and initiates execution of subsequent program control instructions in a similar manner. Many other service messages are used by control program service depending on the particular program control instruction to be executed. For example, a program control instruction may require a scheduler call service message to be sent to the system scheduler identifying a time for the scheduler to return a service message. The return service message can then be used to key the execution of another complete control program by making the scheduler program control instruction prerequisite to the execution of the first program control instruction in the control program. Program control instructions can direct the sending of the data collection service file extract service messages by control program service causing particular information to be retrieved from the data collection service files. Messages can be sent to device acquisition and control service for establishing communication with tape units and loop 2 peripherals. As program control instructions are completed and certain disc storage files are no longer needed, disc file storage space release service messages are sent to the space release program executed in the respective processor S channels. In a similar manner, tape release service messages are sent. For nested control programs, control program service sends program return or abnormal return service messages to higher level control programs. In this manner, making use of the various service messages, control program service supervises and directs the complete execution of an applied system. Control programs may be run once or may be cyclic,

running on a periodic basis. The latter is implemented by sending a service message to the scheduler upon completion of a control program, directing the scheduler to return a message at a certain time automatically reinitiating the control program.