# mitra 15 Reference manual

Contents

| General                                         | 1-1  |

|-------------------------------------------------|------|

| Introduction                                    | 1-1  |

| MITRA 15 main features                          | 1-1  |

| Models MITRA 15/20, MITRA 15/30                 | 1-3  |

| MITRA 15 operating system                       | 1-8  |

| Applications                                    | 1-11 |

|                                                 |      |

| GENERAL LAYOUT                                  | 2-1  |

| Core memory                                     | 2-1  |

| Processing units                                | 2-1  |

| Micro-programmed ROM (or micro-processor)       | 2-2  |

| Registers                                       | 2-4  |

| Logical and arithmetical operator               | 2-4  |

| Indicators                                      | 2-5  |

| Communication with the environment              | 2-6  |

| Interrupts, suspensions, traps                  | 2-6  |

| Mode and protection                             | 2-9  |

| STRUCTURE OF A PROGRAM                          | 3-1  |

| Definition of modularity                        | 3-1  |

| Definition of a section                         | 3-1  |

| Section and segment bases                       | 3-1  |

| Consequences of modularity on MITRA 15 programs | 3-1  |

|                                                 |      |

| Constituents of a program<br>Section calls      | 3-5  |

|                                                 | 3-7  |

| System's management concepts                    | 3-10 |

| ASSEMBLY LANGUAGE                               | 4-1  |

| Source line format                              | 4-2  |

| Basic character set                             | 4-2  |

| Symbols                                         | 4-2  |

| Constants                                       | 4-3  |

| Expressions                                     | 4-4  |

| ADDRESSING MODES                                | 5-1  |

|                                                 | 5-1  |

| Symbolic representation of the instruction      |      |

| Addressing mode representation                  | 5-2  |

| PSEUDO-INSTRUCTIONS                             | 6-1  |

| Source text segmentation                        | 6-1  |

| Assembly pseudo-instructions                    | 6-6  |

| Page pseudo-instruction                         | 6-14 |

|                                                 |      |

© compagnie internationale pour l'informatique 1973

| Con | tents |

|-----|-------|

|-----|-------|

| INSTRUCTIONS                                                                                                                                      | 7-1                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| General                                                                                                                                           | 7-1                                                                                                                                  |

| Symbolic notations                                                                                                                                | 7 -2                                                                                                                                 |

| Load and store instructions                                                                                                                       | 7 -6                                                                                                                                 |

| LBL                                                                                                                                               | 7 -8                                                                                                                                 |

| SBL                                                                                                                                               | 7-9                                                                                                                                  |

| LBR                                                                                                                                               | 7-10                                                                                                                                 |

| SBR                                                                                                                                               | 7-10                                                                                                                                 |

| LBX                                                                                                                                               | 7-12                                                                                                                                 |

| LDA                                                                                                                                               | 7-13                                                                                                                                 |

| STA                                                                                                                                               | 7 - 1 4                                                                                                                              |

| LDE                                                                                                                                               | 7 - 1 5                                                                                                                              |

| STE                                                                                                                                               | 7 - 1 6                                                                                                                              |

| LDX                                                                                                                                               | 7-17                                                                                                                                 |

| STX                                                                                                                                               | 7-18                                                                                                                                 |

| LDR                                                                                                                                               | 7-19                                                                                                                                 |

| STR<br>LEA<br>SPA                                                                                                                                 | 7-17<br>7-20<br>7-21<br>7-22                                                                                                         |

| STS                                                                                                                                               | 7-23                                                                                                                                 |

| DLD                                                                                                                                               | 7-24                                                                                                                                 |

| DST                                                                                                                                               | 7-25                                                                                                                                 |

| Fixed-point arithmetic                                                                                                                            | 7-25                                                                                                                                 |

| ADD                                                                                                                                               | 7-26                                                                                                                                 |

| ADM                                                                                                                                               | 7-27                                                                                                                                 |

| SUB                                                                                                                                               | 7-28                                                                                                                                 |

| MUL                                                                                                                                               | 7-29                                                                                                                                 |

| DIV                                                                                                                                               | 7-30                                                                                                                                 |

| Logical operations                                                                                                                                | 7-31                                                                                                                                 |

| IOR                                                                                                                                               | 7-31                                                                                                                                 |

| EOR                                                                                                                                               | 7-32                                                                                                                                 |

| AND                                                                                                                                               | 7-33                                                                                                                                 |

| CMP                                                                                                                                               | 7-34                                                                                                                                 |

| Register incrementation and decrementation                                                                                                        | 7-35                                                                                                                                 |

| ICX                                                                                                                                               | 7-35                                                                                                                                 |

| DCX                                                                                                                                               | 7-36                                                                                                                                 |

| ICL                                                                                                                                               | 7-37                                                                                                                                 |

| DCL                                                                                                                                               | 7-37                                                                                                                                 |

| Shift operations<br>SHR<br>SLLS<br>SRCS<br>SAD<br>SLCD<br>SLCD<br>SLCS<br>SAS<br>SRLS<br>SRCD<br>SHC<br>SLLD<br>SHC<br>SLLD<br>SRLD<br>PTY<br>NLZ | 7-38<br>7-40<br>7-41<br>7-42<br>7-43<br>7-44<br>7-45<br>7-46<br>7-47<br>7-48<br>7-47<br>7-48<br>7-49<br>7-51<br>7-52<br>7-53<br>7-54 |

|                                                                                                                                                   |                                                                                                                                      |

#### Contents

|    | Inter-register operations         | 7-55          |

|----|-----------------------------------|---------------|

|    | SRG                               | 7-56          |

|    | XAE                               | 7-57          |

|    | XAX                               | 7-57          |

|    |                                   |               |

|    | XEX                               | 7-58          |

|    | XAA                               | 7-58          |

|    | CCE                               | 7-59          |

|    | ACE                               | 7-59          |

|    | CCA                               | 7-60          |

|    | AEE                               | 7-60          |

|    | CNX                               | 7-61          |

|    | AIE                               | 7-61          |

|    | AAE                               | 7-62          |

| ¥. |                                   |               |

|    | LNE                               | 7-62          |

|    | CNA                               | 7-63          |

|    | СМХ                               | 7-63          |

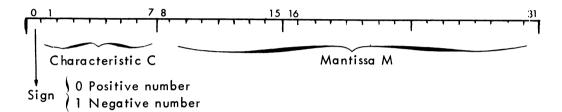

|    | Floating-point arithmetic         | 7-64          |

|    | FAD                               | 7-66          |

|    | FSU                               | 7-67          |

|    | FMU                               |               |

|    | FDV                               | 7-68<br>7-69  |

|    | FDV                               | 7-07          |

|    | Byte string processing            | 7-70          |

|    | M∨S                               | 7-70          |

|    | CPS                               | 7-71          |

|    | TRS                               | 7-72          |

|    | Branch instructions               | 7-73          |

|    | BRU                               | 7-74          |

|    | BRX                               | 7-75          |

|    |                                   |               |

|    | BCT                               | 7-76          |

|    | BOT                               | 7-77          |

|    | BCF                               | 7-78          |

|    | BOF                               | 7-79          |

|    | BAZ                               | 7-80          |

|    | BAN                               | 7-81          |

|    | BE                                | 7-82          |

|    | BZ                                | 7-83          |

|    | BL                                | 7-84          |

|    | BLZ                               | 7 <b>-</b> 85 |

|    |                                   |               |

|    | BNE                               | 7-86          |

|    | BNZ                               | 7-87          |

|    | BGE                               | 7-88          |

|    | BPZ                               | 7-89          |

|    | System communication instructions | 7-90          |

|    | CLS                               | 7-90          |

|    | RTS                               | 7-93          |

|    | CSV                               | 7-94          |

|    | RS∨                               | 7-96          |

|    |                                   |               |

|    |                                   | 7-97          |

|    | DITR                              | 7-100         |

|    | Control instructions              | 7-101         |

|    | TES                               | 7-102         |

|    | STM                               | 7-103         |

|    | CLM                               | 7-103         |

|    |                                   |               |

| 4 | 0 | 5 | 7 |

|---|---|---|---|

|   |   |   |   |

#### Contents

| RD<br>WD<br>LDP                                                                                                                                     | 7-104<br>7-104<br>7-105                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

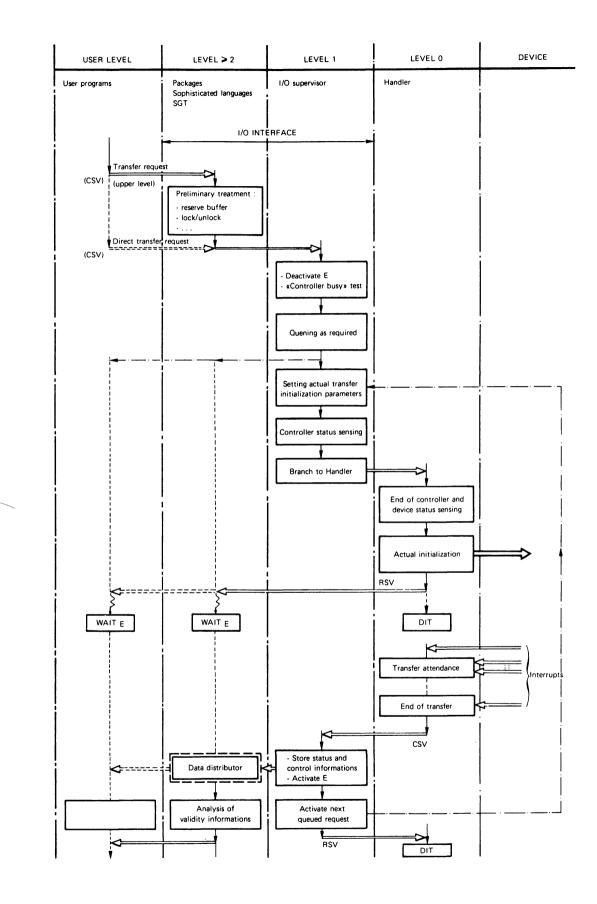

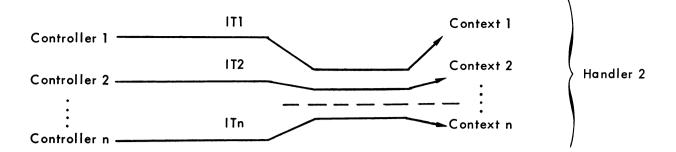

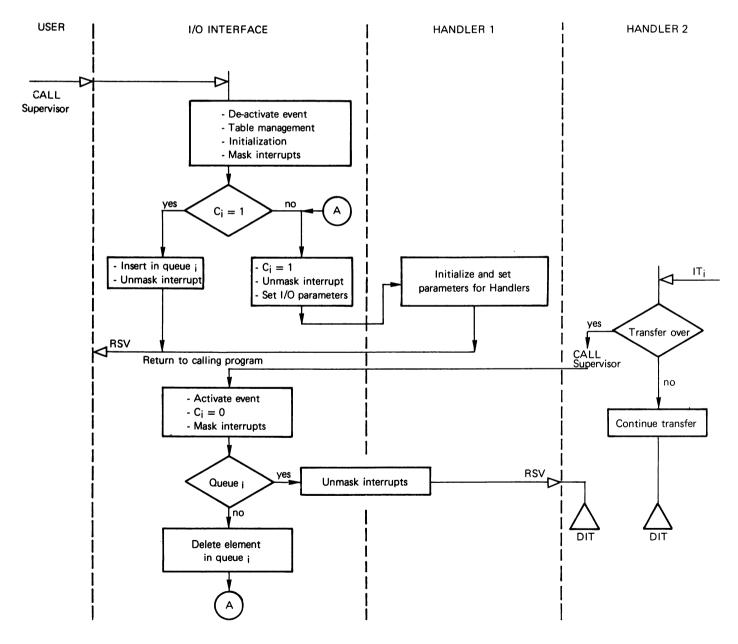

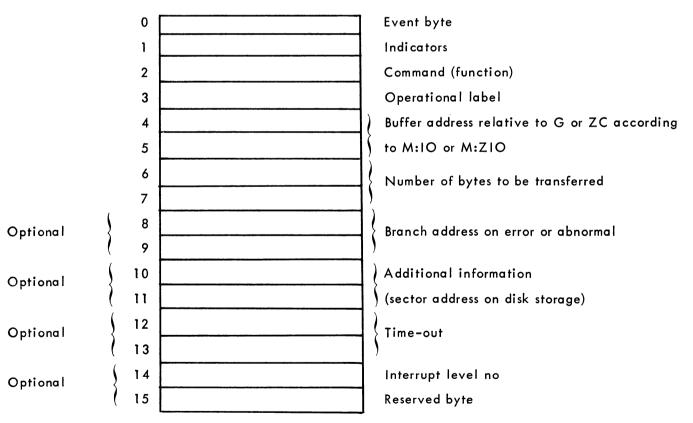

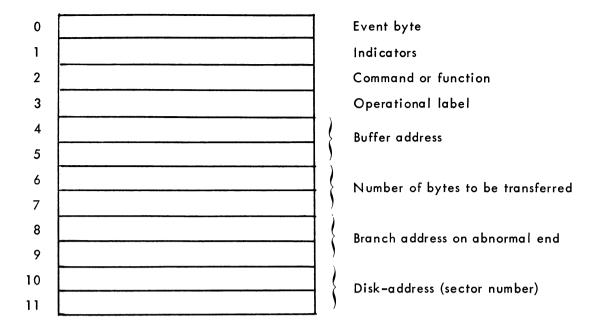

| INPUT/OUTPUT CONTROL SYSTEM<br>Input/output system organization<br>Input/output interface<br>Transfers<br>Operational labels<br>Handler utilization | 8-1<br>8-1<br>8-1<br>8-6<br>8-11<br>8-14 |

| LIST OF PSEUDO-INSTRUCTIONS                                                                                                                         | A-1                                      |

| LIST OF INSTRUCTIONS                                                                                                                                | B-1                                      |

| ADDRESSING MODES                                                                                                                                    | C-1                                      |

| ASSEMBLER OPERATION                                                                                                                                 | D-1                                      |

## 1. General

#### I-1. INTRODUCTION

MITRA 15 is a real time computer relying on a modular design and advanced micro-programmed structure for an efficient approach to numerous application fields, such as process control, scientific computation, remote-processing or transaction management.

The system includes up to four processing units specialized through read-only micro-programmed memories (ROM) and arranged around a planar structure core memory. According to their micro-programs, these units become CPU's, IOP's or special-purpose units. Each processing unit is provided with a "MINIBUS" for connecting a comprehensive range of peripheral units.

MITRA 15 is available in two fully compatible models which only differ by their processing capacity and the range of connectable peripheral units. Thus, each user can select the model and configuration best suited to its specific requirements.

#### I-2. MITRA 15 MAIN FEATURES

#### I-2.1. Core memory

MITRA 15's memory is a lithium-ferrite core random access memory organized in 16-bit words with 2 additional bits, 1 for parity and 1 for protection. The very short 800 nanoseconds word read/write cycle provides an outstanding transfer rate of 2.5 Mbytes per second (millions of bytes/second).

Memory contents are adressable on a byte basis and alterable on a byte, half-word or word basis.

The memory is made up of 4 096-word blocks (i.e. 8 192 bytes) up to a maximum of eight. Its capacity can thus be extended from 4 096 words to 32 768 words per 4 096-word increments.

Dynamic memory protection

This feature provides full protection to any memory area against unwanted attemps to alter its contents. The protection its assigned on a dynamic basis (LDP instruction).

A 1-bit protection "lock" is associated with every memory word. Besides, an indicator of the program status acts as a "key" : when this indicator is set to 1, the program is able to gain access to all memory locations; otherwise the program can only gain access to unprotected areas.

Parity

Full parity ckeck is provided both in the memory an during I/O operations.

#### 1-2.2. Processing units

The functions available in a conventional computer are shared between a wired module, indentical for all processing units, the so-called "micro-processor", and the contents of a ready-only control memory which "specializes" the micro-processor to provide the functions of a CPU, IOP or special-purpose unit.

A processing unit comprises a fast register block, five program indicators, a micro-programmed read-only memory, an operator and an interrupt/suspension system.

#### ■ Fast register memory

This memory is implemented in MSI bipolar integrated circuit registers which are organized in eight 16-bit program-adressable register blocks. The capacity of each processing unit can be extended from two to eight 8-register blocks per 2-block modules. Access time : 60 nanoseconds per word.

In the CPU, the first block (block 0) is assigned to the program context, the remaining blocks being available for peripheral transfers.

Program context

In an IOP, all block are available for peripheral transfers.

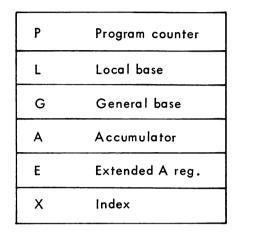

#### Block 0 of CPU

- Program indicators

- C Carry or operation test

- O Overflow or operation test

- MS Mode : master/slave

- MA Interrupt Mask

- PR Memory protection

For detailed description of indicators see chapter II.

Instructions

MITRA 15 has a set of 86 instructions including :

- 40 memory reference instructions,

- 29 register instructions,

- 12 shift instructions,

- 5 special instructions.

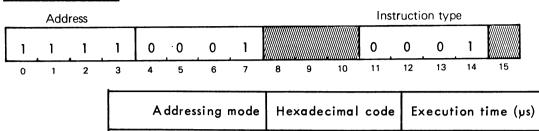

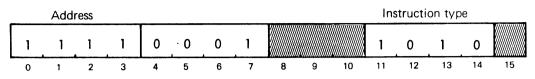

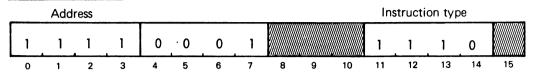

- All instructions have a fixed format :

| 3    | 5        | 8            |

|------|----------|--------------|

| Mode | Function | Displacement |

| 4    | 4        | 8            |

| Mode | Function | Displacement |

They operate on bytes (half-words), words, double-words or unlimited length byte strings.

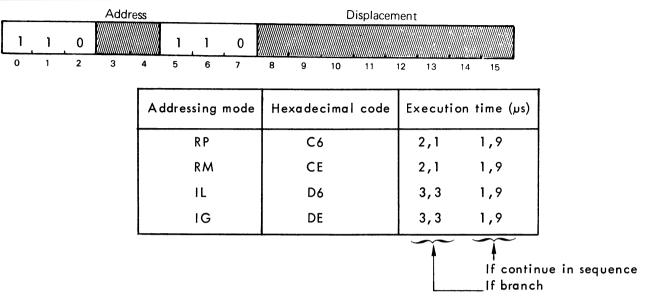

Addressing modes :

- immediate addressing for operands which can be coded in one byte;

- direct, indirect and indexed addressing with respect to the local base;

- direct, indirect and indexed addressing with respect to the general base.

- Micro-programmed read-only memory

This non-destructive read out permanent memory is pre-recorded. Each 16-bit word contains one microinstruction. The memory is implemented in MSI bipolar IC's and its access time is 60 nanoseconds. Its capacity is 512 or 1024 words per processing unit.

Three different versions are available for the following functions :

- MC1 : executes the basic instruction code and the coupling functions for peripherals which are connectable to CPU's Minibus only.

- MC2 : executes the complementary code (optional instructions) and the coupling functions for peripherals which are connectable to the Minibus of either the CPU or an IOP.

- MC3 : executes the coupling for peripherals which are connectable to an IOP's Minibus.

- Interrupts (IT)

32 priority interrupt levels are available which can be armed, masked or triggered by program. They provide up to 112 discrete external interrupts by grouping.

When an interrupt is triggered, the program context is automatically swapped in 30 µs.

For a special high speed interrupt level, this swapping is effected in 5 us only, by register block switching.

Suspensions

MITRA 15 also offers 32 suspension levels organized on a priority basis for micro-program coupling of peripherals requiring urgent or frequent transfers.

The maximum response time is 300 µs.

Minibus

Each processing unit is provided with a Minibus for device controllers connection. This Minibus is implemented as a printed circuit located in the chassis wiring and provides non-specialized plug-in locations for all controller cards.

#### 1-3. MODELS MITRA 15/20, MITRA 15/30

#### MITRA 15/20

- MITRA 15/20 CPU comprising, as standard :

- 512-word micro-programmed ROM (MC1),

- 64 fast access registers,

- Basic code providing for 77 instructions,

- Priority interrupt system.

Core memory

4K to 32K 16-bit words per 4K increments.

- Performance

- Addressing mode : direct, indirect, indexed, relative, immediate, local and general.

- 1 index, 2 bases.

- 77 instructions, including 33 memory reference instructions.

- Load, store or add word in 2.1 µs.

- Main options

- Up to 3 direct memory accesses (DMA)

- Additional micro-programmed ROM (MC2)

- Up to 32 priority interrupt levels per 1 or 4 levels modules.

- Wired MUL/DIV (7 and 8  $\mu s)$  .

- Floating point operator (O $\lor$ F).

- Power failure protection.

- Software

- MITRAS 1 Assembler; MITRAS 2 Extended Assembler; LP 15; BASIC; FORTRAN IV.

- Linkage editor.

- 2 Monitors : Basic Monitor MOB and Real-Time Monitor MTR.

- Libraries.

- Basic peripherals (Range I)

- Console typewriter (with paper tape reader/punch),

- 300 char./sec. paper tape reader,

- 60 char./sec. paper tape punch,

- Logging slow printer (15 char./sec.),

- 2 to 128 16-bit digital input lines for logical levels, or filtered, or relayed,

- 2 to 64 16-bit digital output lines for logical levels or relayed,

- Counter inputs; real-time clock,

- Analog inputs.

4 K 4 K 4 K 4 K 4 K 4 K 4 K 4 K words words words words words words words words DMA CPU DMA DMA CPU MINIBUS ٨U Typewriter DIV Paper Tape reader/punch Logging Real time clock digital inputs digital outputs analog inputs counter inputs interrupts

CORE MEMORY

MITRA 15/20 general layout

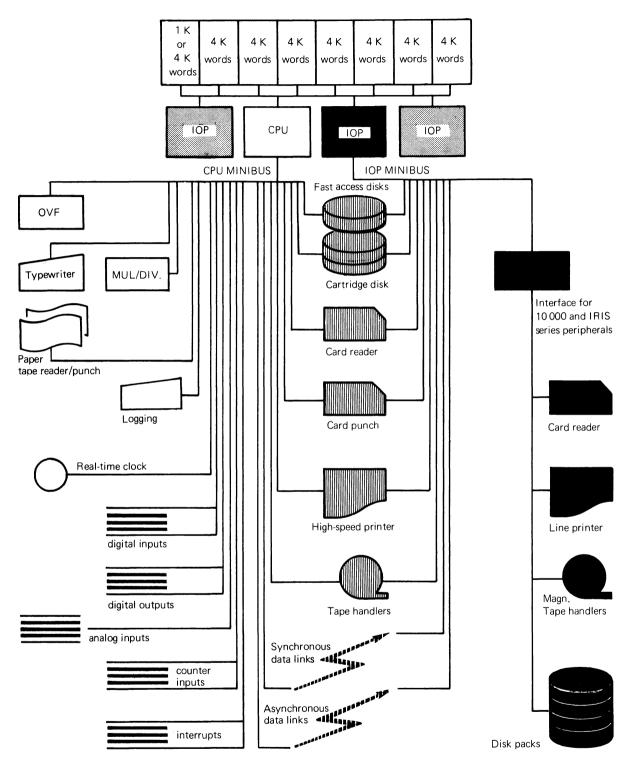

#### MITRA 15/30

- MITRA 15/30 CPU comprising, as standard :

- 1024-word micro-programmed ROM,

- 32 fast access registers,

- Extended operation code for 86 instructions,

- Priority interrupt system,

- Wired MUL/DIV,

- Power failure protection.

- Core memory

4K to 32K 16-bit words per 4K increment

- Performance

- Addressing modes : direct, indirect, indexed, relative, immediate, local and general.

- 1 index, 2 bases

- 86 instructions, including 40 memory reference instructions

- Load, read, write or add word in 2.1 µs

- MUL/DIV in 7 and 8  $\mu s$  , respectively.

- Main options

- Up to 3 direct memory accesses (DMA)

- Up to 3 input/output processors (IOP)

- Extension to 128 fast access registers per processing unit (64-level modules)

- 32 priority interrupt levels per 1 or 4 level modules

- Floating-point operator (OVF)

- 🕿 Software

- MITRAS 1 Assembler; MITRAS 2 Extended Assembler; Macro-generator; LP 15; BASIC; FORTRAN IV; Librarian; File management system.

- 3 Monitors : Basic Monitor MOB; Real-Time Monitor MTR; Disk Real-Time Monitor MTRD.

- Peripherals

- Range I (Model 20)

- Range II :

- One head per track fixed-disks; average access time 10 ms, transfer rate 150 kbyte/sec, capacity 100 to 1600 kbytes.

- Movable head disk-pack units; average access time 60 or 90 ms; transfer rate 100 or 150 kbyte/sec; capacity 2.5 to 5 Mbytes or 6.2 to 24.8 Mbytes.

- Card reader : 200 or 600 cpm.

- Card punch : 20 or 40 cpm.

•

CORE MEMORY

MITRA 15/30 general layout

- Line printers: 132 columns; 200, 400 or 600 lpm.

- Communication controller for 1 synchronous data link, full duplex, 1200/4800 bauds

- Communication controller for 2 asynchronous data links, full duplex, 50 to 1200 bauds.

- Range III :

- OCTET interface for connecting all CII 10 000 or IRIS Series peripherals : (card readers, printers, tape handlers, etc...).

#### 1-4. MITRA 15 OPERATING SYSTEM

Depending on the availability of a fast access disk unit, the software is offered in two different versions : the resident system and the disk system.

- The resident system provides :

- 2 Monitors : the Basic Monitor MOB and the Real-time Monitor MTR

- Assemblers : MITRAS and LP 15; Compilers : BASIC and FORTRAN and a Macro-generator.

- The disk system provides :

- The real-time Monitor MTRD

- The resident system processors, a librarian and a linkage module.

In addition, the software includes :

- Debugging commands available as extension of each monitor.

- A comprehensive library of "real-time" mathematical programs, and a file management system.

- MITRA 15 Simulators available for use on CII 10 070, IRIS 50, IRIS 80, IBM 360, etc.

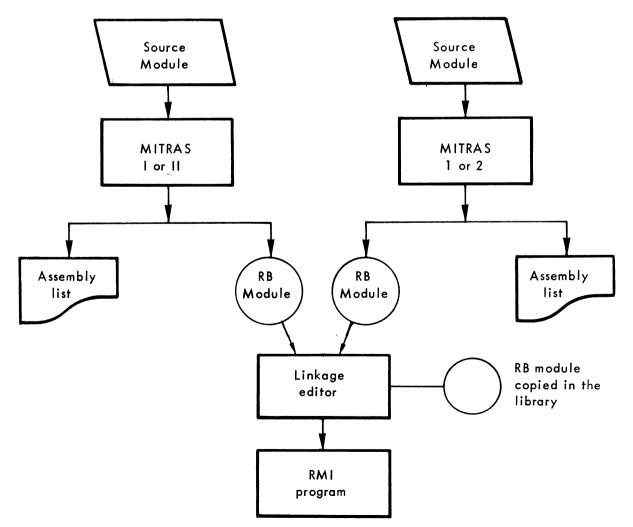

#### MITRAS I Assembler

Translates the symbolic MITRAS language generates in one single pass a relocatable binary object-listing and a list of error diagnostics.

Both source and relocatable binary programs are normally on paper tape; memory requirement : 4K words.

#### MITRAS 2 Extended Assembler

Translates the symbolic MITRAS language; has a larger set of pseudo-instructions than MITRAS I. Memory requirement : 8K words.

#### LINKAGE EDITOR

Operates in two passes for converting binary relocatable programs generated during various assembly or compilation runs, into a relocatable memory image format which can be loaded for execution by the Basic Monitor.

The linkage editor also provides a memory map of the relative location of the various modules and a listing of the common sub-routines which are called. Memory requirement : 4K words.

#### BASIC MONITOR MOB

Perform computer control and handles user's communications with the system and the basic processors. Its main functions are :

- trap processing,

- internal interrupt control,

- program loading,

- input/output control,

- program execution control.

Memory requirement : 4K words.

#### REAL-TIME MONITOR MTR

Handles simultaneously interrupt-dependent batched jobs in core. Controls and supervises all privileged operations, such as I/O handling or memory protection, and provides operator communication. Memory requirement : 8K words.

|                                             | 4 Kwords                                               | 8 Kwords                                                  | 12 Kwords         | 16 Kwords           | Simulation                                             |

|---------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|-------------------|---------------------|--------------------------------------------------------|

| OPERATING<br>SYSTEM<br>resident<br>system   | Basic Monitor<br>MOB                                   | Real-time<br>Monitor MTR                                  |                   |                     | control command<br>analyz <del>er</del><br>interpreter |

| disk<br>system                              |                                                        | disk real-time<br>Monitor MTRD                            | linkage<br>module |                     |                                                        |

| PROGRAM<br>GENERATION<br>resident<br>system | MITRAS I<br>linkage editor<br>loader-editor            | MITRAS 2<br>BASIC                                         | LP 15             | FORTRAN IV          | Assembler<br>linkage editor                            |

| disk<br>system                              |                                                        | MITRAS 2<br>linkage editor<br>BASIC<br>LP 15<br>Librarian | FORTRAN IV        | Macro-<br>generator | LP 15                                                  |

| LIBRARY                                     | Mathematical pro<br>programs commun<br>file management | ication programs                                          |                   |                     |                                                        |

| Structure | of MITRA | 15 standard | software |

|-----------|----------|-------------|----------|

|           | •••••••• |             |          |

#### DISK REAL-TIME MONITOR MTRD

This disk-oriented version of the MTR Monitor has additional capabilities for overlay control and user's libraries management, as well as for automatic linking of batched programs (compile-link, load-and-go); requires 8K words memory and a fast access disk unit.

#### LOADER - LINKAGE EDITOR

Operates in one pass for loading binary relocatable programs for immediate execution.

This processor can only accept binary programs generated by MITRAS I. Memory requirement : 4K words.

#### LP 15

This assembler type language has a syntax which is closely related to that of sophisticated languages such as ALGOL, but with the feature of direct access to MITRA 15's registers.

The binary object programs thus generated have an efficiency which is practically equivalent to that of assembled programs. Memory requirement : 12K words without a disk unit.

#### BASIC

This conversational compiler provides for time-shared operation and alphanumerical data processing. Memory requirement : 8K words.

#### FORTRAN IV

This compiler generates in one single pass a relocatable binary object-program in the format required by the linkage editor. May call sub-routines written in another language and translated in relocatable binary format; compatible with CII 10 020, IRIS 45 and IRIS 50. Memory requirement : 16K words or 12K words with a disk unit.

#### AMAP EXTENSION (DEBUGGING AIDS)

An AMAP extension available with every monitor as a debugging aid and provides instruction execution records, halt on address, memory dumps and contents alteration, through special monitor commands.

#### LINKAGE MODULE

Provides for automatic linking of batched programs in the deffered processing area with concurrent realtime programs.

This processor is controlled by the disk real-time monitor MTRD; requires 12K memory words and a fast access disk unit.

#### MACRO-GENERATOR

Translation program using user-defined procedures. It provides in one pass a program in assembly or compilation language. Memory requirement : 16K words.

#### LIBRARIAN

Provides for handling the system library constitutive files through commands such as : insert, replace, copy, load, dump on external medium... Memory requirement : 8K words and a fast access disk unit.

#### UTILITY PROGRAMS

These programs are available for :

- Updating and correcting source programs on sequential access media (paper tape, magnetic tape, etc.).

- Handling and updating library programs on sequential access media. Memory requirement : 4K words.

#### MITRA 15 SIMULATORS

These simulation programs are available for CII 10 070, IRIS 50, IRIS 80, IBM 360, etc. computers and include :

- a MITRA 15 interpreter,

- MITRAS Assembler and Linkage editor,

- a system generator,

- LP 15 Compiler.

They perform assembly, linkage edition and debugging functions on programs intended for later exploitation on any MITRA 15 configuration.

#### I-5. APPLICATIONS

| LABORATORIES           | Spectrometry<br>Gazeous chromatography<br>Cristallography |  |  |  |

|------------------------|-----------------------------------------------------------|--|--|--|

| MEDECINE               | Chemical analysis                                         |  |  |  |

|                        | Electrocardiography                                       |  |  |  |

| ENGINEERING            | Components testing                                        |  |  |  |

|                        | Seismography                                              |  |  |  |

|                        | Ranging                                                   |  |  |  |

| INDUSTRY               | Chemicals                                                 |  |  |  |

| Monitoring             | Oil and derivates                                         |  |  |  |

| Automation             | Steel industry                                            |  |  |  |

| Process control        | Mechanical engineering, aerospace, etc.                   |  |  |  |

| REMOTE PROCESSING      | Deconcentrated companies                                  |  |  |  |

| Front-end computers    | Public Administrations                                    |  |  |  |

| Satellite stations     | Universities                                              |  |  |  |

| Front ends             |                                                           |  |  |  |

| SCIENTIFIC COMPUTATION | Education                                                 |  |  |  |

| Time-sharing           | Design office                                             |  |  |  |

| Data centers           | Private companies                                         |  |  |  |

| TRANSACTION PROCESSING | Insurance companies                                       |  |  |  |

| Data collection        | Banks                                                     |  |  |  |

| File management        | Public services                                           |  |  |  |

|                        |                                                           |  |  |  |

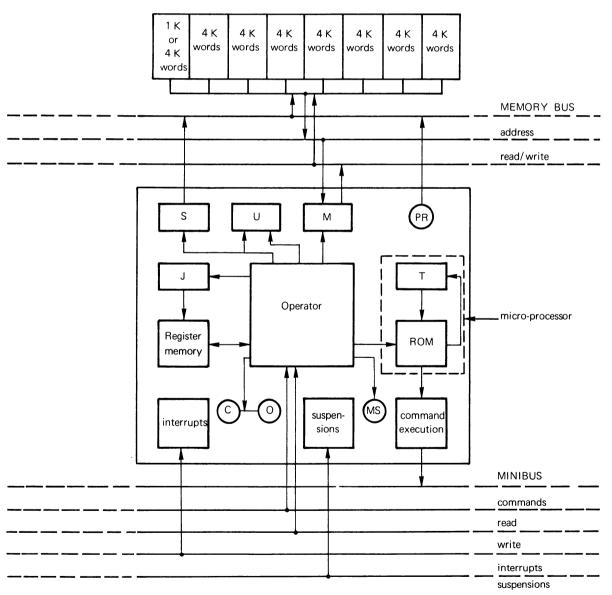

## 2. General layout

MITRA 15 is built around a planar structure core memory the capacity of which can be extended modularly by 4K 16-bit words blocks. This core memory has four access ports for connecting up to four processing units or direct memory access controllers.

Each processing unit includes a micro-programmed read-only memory (ROM); a specific micro-program prerecorded in this memory specializes the associated processing unit for performing the functions of :

- a central processing unit (CPU),

- an input/output processor (IOP), or

- a special-purpose unit for a particular process.

Each processing unit controls a so-called MINIBUS which is a peripheral bus designed for direct connection of peripheral controllers.

#### II-1. CORE MEMORY

The core memory is basically organized in 18-bit words each comprising 16 data bits, 1 parity bit and 1 memory protection bit.

Read/write operations are executed in two separate half-cycles. A read cycle includes a destructive readout half-cycle followed by a rewrite half-cycle. A write cycle includes a clear half-cycle followed by a write half-cycle.

Memory access time is 400 ns (1/2 cycle) and a full read/write cycle lasts 800 ns.

Though memory transfers are performed on a word basis, micro-commands allow the programmer to operate on bytes, i.e. on half-words. Thus, all MITRA 15 addresses point to byte locations, even-numbered addresses corresponding to word locations.

The memory is built up with 4096-word modules, i.e. 8192 bytes. MITRA 15 is designed for a maximum of eigh modules corresponding to a maximum capacity of 32 768 words (or 65 536 bytes).

The control logic supplies the timing signals required for operating the memory proper (half-cycles timing control), and the transfer signals for data exchanges with the processing units; in addition it deals with the four accesses relative priorities.

#### **11-2. PROCESSING UNITS**

The operation of a MITRA 15 processing unit, and more specifically of the CPU, may be described at two fully distinct levels :

A first level corresponding to what may be termed "user-level" and the knowledge of which is sufficient for programming an application on MITRA 15.

It includes the following features :

- the standard instruction set detailed in chapter VII;

- six general registers of block 0;

- the five program indicators;

- the interrupt system.

■ A second level corresponding to what may be termed "micro-processor" level

This micro-processor includes the following features :

- a set of about forty hardware-implemented basic micro-instructions;

- a read-only memory implemented on module boards and which contains the sub-routine set, (also called "micro-programs") defining MITRA 15's standard instructions set and peripheral coupling functions;

- operational registers;

- micro-processor status indicators;

- a so-called "suspension system" corresponding, for the second level, to the interrupt system of the first level.

The following sections describe the various components of a processing unit, viz :

- micro-programmed ROM

- S and M memory transfer registers

- fast-access register blocks

- status indicators

- interrupt and suspension systems.

#### 11-3. MICRO-PROGRAMMED ROM (OR MICRO-PROCESSOR)

This non-destructive ROM is pre-recorded in factory and implemented in integrated circuits (access time : 60 ns per word).

Each memory word is 16 bits long and contains one micro-instruction.

The control ROM of a processing unit contains either 512 words (MC1), or 1024 words (MC1 + MC2).

Any micro-instruction is executed in 300 ns.

The address of the currently executed micro-instruction is contained in a 10-bit register called T-register. A micro-instruction has the following format :

| 0 1 | 2  | 6 | 7 | 9  | 10 |    | 15 |

|-----|----|---|---|----|----|----|----|

| м   | OP |   |   | сс |    | AD |    |

Each micro-instruction has a dual purpose :

1) It controls a number of functions, viz.:

- memory control (2 bits : M-field)

- basic operation code (generally 5 bits : OP-field)

- complementary operation code (3 bits : CC-field) defining for instance a general register address

2) It defines the address of the next micro-instruction (through a 6-bit modifier : AD-field), by updating T-register contents.

In fact, micro-instructions are not stored sequentially.

No indexing adder is associated with T-register, since its contents is not incremented by one unit from a micro-instruction to the next, as in a sequential addressing scheme.

CPU's and IOP's are differenciated by the kind and contents of their respective control memories.

In the CPU, MC1 control memory (512 words) executes the basic operation code and the coupling functions for peripherals which are connectable to its Minibus only (Range I).

MC2 control memory provides for executing the complementary operation code (optional instructions) and the coupling functions for peripherals which are connectable either to the Minibus of the CPU, or to the Minibus of an IOP (Range II).

The CPU's control memory then includes 1024 words (MC1 + MC2).

MC3 control memory executes the coupling functions for peripherals which are connectable to the Minibus of an IOP only (Range III).

CORE MEMORY

Processing unit layout

#### II-4. REGISTERS

#### 11-4.1. Memory transfer registers

S-register is a 15-bit address register, though actual addresses are 16 bits long. The rightmost bit of an address, which specifies the desired byte within the addressed word, is in fact ignored by the memory logic.

M-register is an 18-bit data register receiving the transferred memory words. Two of these bits are reserved for parity and protection tests; the 16 other bits are used for date exchanges with U-register.

#### 11-4.2. Fast-access registers

A standard MITRA 15 processing unit includes eight register blocks each comprising eight 16-bit integrated circuit registers numbered 0 through 7. Eight optional blocks are available on 15/30 model.

These registers have different assignments in the CPU and in an IOP.

In the CPU, the first block (block 0) is reserved for program execution; its first six registers have the following functions :

- A Accumulator,

- E Accumulator extension,

- P Program counter,

- X Index register,

- L Local base register,

- G General base register,

the last two registers, V and W ared used by micro-programs.

The other blocks are normally assigned to peripheral transfers through the suspension system (channel memories).

In an IOP, all register blocks are available for peripheral transfers.

Each register has a unique address form 0 to 63 (or 127). In the micro-programs, a general register address is generated from :

- the contents of the corresponding field of the micro-instruction format (3 bits).

- the contents of J-register.

It will be seen in section II-8. that a high-speed interrupt causes an automatic switching of the register block. In the new block, the registers have then the same assignment as in block 0, but for other programs.

#### 11-5. LOGICAL AND ARITHMETICAL OPERATOR

The logical and arithmetical operator includes a universal register, or U-register, and a dual-input operator. The 16-bit U-register cannot be directly accessed by the instructions, but constitutes an accumulation register for the micro-processor. In this respect it can contain one operand of a micro-instruction and/or store the result. Both operands of a micro-instruction may also be provided by :

- a general register (operand 2)

- M-register in connection with the core memory (operand 1)

- the I/O interface (operand 2)

- the control memory (operand 2)

- the stack (operand 2)

- the indicators (operand 2)

The results of the operation are stored in the following devices :

- U-register (universal)

- M-register (data)

- S-register (address)

for core memory transfers

- a general register

- the indicators

#### **II-6. INDICATORS**

MITRA 15's central processor includes nine indicators :

Four indicators reserved for micro-processor use :

B-indicator : assigned to U-register overflows

Tz-indicator : for a zero micro-instruction result

To-indicator : for the sign of a micro-instruction result

Ao-indicator : address of the processed byte.

Five program-accessible indicators

C = Carry

This indicator has two different meanings according to the last instruction by which it is set.

• Carry/borrow (arithmetic type instruction)

- When a positive number is added (negative number subtracted), if the result is obtained without becoming zero, C is reset (C = 0).

- When a positive number is added (negative number subtracted), if the result is obtained after becoming zero, C is set (C = 1).

- When a negative number is added (positive number subtracted), if the result is obtained without becoming zero, C is set (C = 1).

- When a negative number is added (positive number subtracted), if the result is obtained after becoming zero, C is reset (C = 0).

• For other instructions using C-indicator, the status C-indicator, the status C = 1 after execution denotes a zero value in a register or, in the case of a comparison, equality of two values.

#### O = Overflow

This indicator also has two different meanings according to the last instruction executed.

• For arithmetic type instructions, O-indicator is used for overflow. More precisely, when both operands have the same sign, if the result is of the opposite sign, O is set (O = 1). Otherwise, O is reset (O = 0).

• For other instructions using O-indicator, the status O = 1 after execution denotes a negative value in a register (leftmost bit set) or, in the case of a comparison, that A-register value is less than the addressed word value.

#### MS = Master/Slave mode

For programs executed in Master mode, this indicator is set to 1, otherwise the program is executed in normal or "slave" mode.

See chapter VII "Instructions" for detailed description of the above three indicators for every instruction.

#### MA = Interrupt mask indicator

This indicator is set to 1 for masked interrupts, otherwise MA = 0.

#### PR = Memory protection "key"

When PR = 1, the program is able to gain access to any memory location.

When PR = 0, the program is only allowed to gain access to unprotected memory areas ("protection lock" cleared).

These five indicators are included in the context of a specific program.

#### 11-7. COMMUNICATION WITH THE ENVIRONMENT

The processing unit is coupled to the peripheral controllers via a so-called MINIBUS which is accessible through micro-instructions. The interface includes :

- for data : 16 output bit lines and 16 input bit lines;

- three function bit lines;

- for addresses : 6 bit lines or 10 bit lines in particular cases;

- a sync line;

- a reset line.

The peripheral Minibus, on which the peripheral controllers are connected, includes 16 unidirectional data lines, both for input and output, an address and peripheral control bus, as well as interrupt and suspension lines.

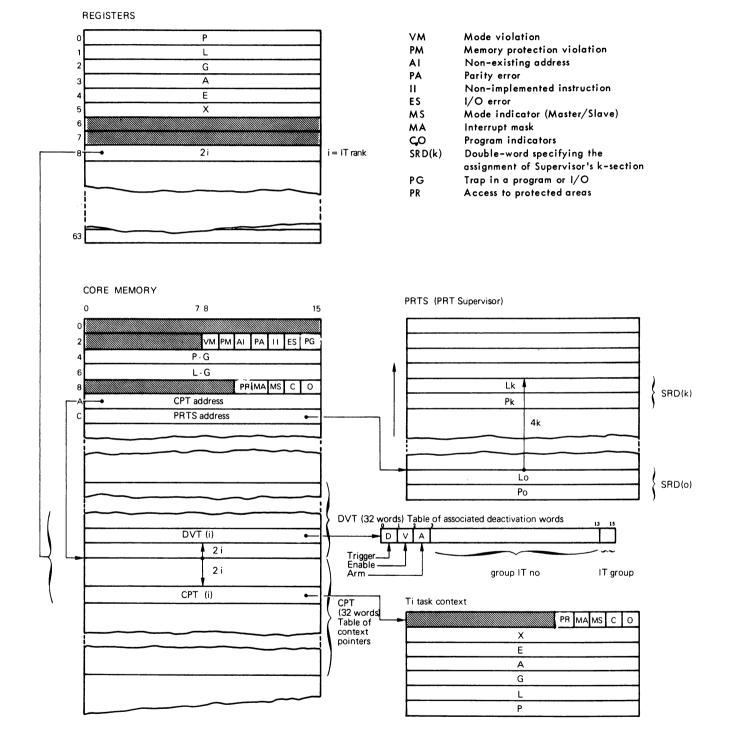

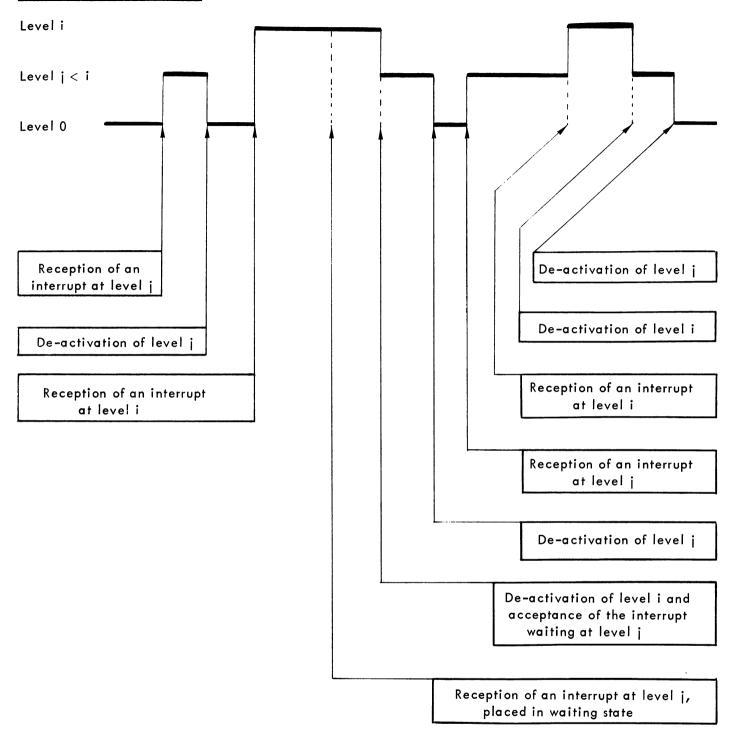

#### II-8. INTERRUPTS - SUSPENSIONS - TRAPS

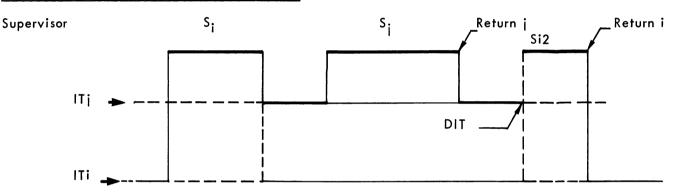

II-8.1. Interrupts

The interrupt system operates when :

- an interrupt signal occurs;

- a special micro-instruction, located by definition at specific "interrupt point", occurs;

- interrupts are unmasked;

- the priority level of the current program is lower than that of the incoming interrupt.

There are 32 interrupt levels (IT levels). Each of these levels has an associated memory address containing the context pointer of a program specifically assigned to this level. These 32 context pointers are stored in a table pointed to by the contents of memory address 10.

When an interrupt condition occurs :

- the condition is stored in a flip-flop (one per signal),

- its IT-level is hardware-coded and compared with that of the task currently processed (register 8),

- if the interrupt is accepted, its specific IT-level (0 through 32) is stored in the hardware of the microprocessor when the interrupt test micro-instruction is executed,

- then, the micro-program performs the following operations :

. Storage of the interrupted task context at an address depending on its rank (the latter being stored in register 8).

. Loading of the interrupting task context from an address depending on its rank.

. Call of the first instruction of the interrupting task. (See "Communication with the micro-processor" page 11-8).

When the task is over or must wait for the occurence of a specific event, it releases the processing unit through an interrupt de-activation and context swapping instruction DIT which :

- acknowledges the interrupt calling for the task,

- stores the task's context, and

- calls for the next task waiting at the same IT-level, or, if there is no such task, for a task waiting at the next lower IT-level.

If no task is waiting, the computer executes a wait loop until an external event occurs at the lowest level.

The total number of interrupt levels is 32, 4 internal and 28 external. Besides, up to 4 interrupts may be on a same level, providing a total number of multiplexed external interrupts equel to 112 (28 × 4).

As a rule, standard peripheral controllers use one interrupt level each.

Internal interrupt levels are assigned to the following tasks :

- operator's console interrupt request,

- power turn on,

- power shut down,

- program (level 0).

#### High-speed interrupt

Optionally, one external IT-level may be of the "high-speed" type, i.e. may call for a task the context of which is stored in a register block other than block 0, which contains the interrupted task context. Consequently, the task switching only requires that the indicators be transferred in block 0; it lasts about 2 µs.

When this "high-speed task" is acknowledged, the control is returned to the interrupted task (the context of which is still in block 0) through a special DITR instruction by-passing the usual context swapping in block 0.

#### 11-8.2. Suspensions

The suspension system is able to interrupt the current micro-program at the end of every micro-instruction, and to launch a special micro-program. The suspension request is either issued by a peripheral or internal to the micro-processor (processing unit).

On occurence of a suspension, the micro-processor's status, i.e. the contents of U-, J-, T-registers and of B, Tz, To, Ao indicators are transferred in a stack. The suspension micro-program is then executed.

At the end of the suspension program, the initial contents of U-, J-, T-... registers are restored from the values previously saved in the stack.

Communication with the micro-processor

The stack has a capacity of four suspensions, i.e. the number of suspension levels is four. The number of suspension signals is 32, or 8 per level, assigned as follows :

- 5 internal suspensions :

. traps (1)

. interrupts (2)

. control panel (1)

. power failure (1)

- 27 external suspensions associated with peripherals.

#### 11-8.3. Traps

The origin of a trap is an abnormal condition detected at the end of a micro-instruction.

The trap processing micro-program :

- protects bytes 4 to 9 of the memory which contain L- and P-register values and the indicators status of the context of the instruction which initiated the trap;

- signals the cause of the trap by setting a bit in memory word 2;

- performs a call to supervisor section 0.

The following abnormal conditions initiate a standard trap :

- non-existing memory address : the user has specified an address exceeding the available memory.

- memory protection violation : the user attempts to write in a protected memory area with a zero PR-key.

- parity fault in core memory read-out signals.

Other traps may be initiated by the following causes :

- operating mode violation : attempt to use priviledged instructions in a slave mode program.

- invalid instruction : incorrect OP-code specified.

- "watch-dog" timer runout.

In all these situations :

- the current instruction is aborted,

- the micro-processor's stack is not triggered,

- a special micro-program generates a supervisor call.

The operations performed by the standard monitors in response to a trap condition are described in the corresponding utilization manuals. The trap status word is described in "Communication with the micro-processor" diagram page 11-8.

#### 11-9. MODE AND PROTECTION

#### 11-9.1. Operating modes

- Normal or "slave" mode.

In this mode, priviledged instructions cannot be executed and any attempt to execute such an instruction causes a "mode violation" trap. MS indicator is reset (MS = 0).

- Priviledged or "master" mode.

In this mode all instructions, whether priviledged or not, are executable. MS indicator is set (MS = 1).

The various supervisor modules are examples of programs which must be executed in master mode. (See CSV and RSV instructions).

It should be noted that addressing modes are different in master and slave modes (see Chapter V "Addressing modes") to provide absolute addressing capability in master mode.

#### 11-9.2. Memory protection system

The protection system becomes operative whenever PM key-switch is turned on the control panel.

The operation is as follows :

- a 1-bit protection "lock" is associated with each memory word and may be set by a LDP instruction (LoaD Protection).

- the program status includes a PR-indicator which acts as a "key".

If key value is 1 (override key), the program may gain access to all memory locations.

If key value is 0, the program may only gain access to memory locations whose lock value is 0.

#### PR-key loading

The PR indicator is loaded with the program context.

It is preserved before being forced to 1 during any supervisor call SVC and restored to its previous value when the supervisor returns the control to the calling program.

#### Protection violation

If a "zero key" program attemps an access to any location having a 1 lock value, the protection system operates and initiates a "protection violation" trap.

Memory protection and operating mode are independent.

## 3. Structure of a program

#### III-1. DEFINITION OF MODULARITY

In programming art, as in other techniques, the modularity consists in breaking down a system in to smaller elements with standard interfaces.

Since the introduction of the "sub-program" concept, modularity is an acomplished fact in programmation. As a main program may also be considered as a module, we rather call them "sections". The following advantages are due to modularity :

- easier system specification,

- easier software writing, by sharing the work between a number of programmers,

- identical sections may be used in different system without rewriting,

- easier debugging and assistance on software products.

#### **III-2. DEFINITION OF A SECTION**

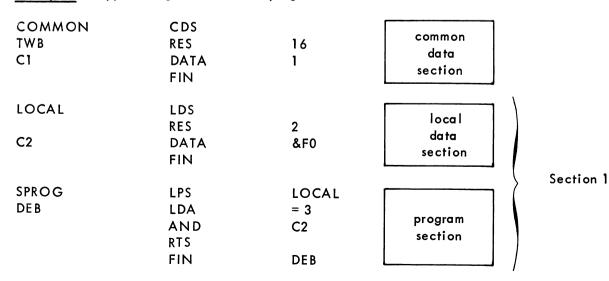

A section mainly comprises an instruction sequence called a program segment. The purpose of these instructions is to process data which are either assigned to the section, or shared between a number of sections.

Data which pertain to a section in proper make up a "local data segment" (LDS).

Data which are common to several sections make up a "common data section" (CDS).

Accordingly a section is either the common data section CDS, or a local data segment (LDS) plus an executable program segment (Local Program Segment = LPS).

The CDS is accessible from any point in the program.

More particularly, the CDS may be accessed from a LDS in general addressing mode (direct, indirect or indexed indirect).

Symbols and labels defined in the CDS are applicable to the whole program.

A LDS is accessed from the associated LPS in local addressing mode (direct, indirect or indexed indirect).

Symbols and labels defined in a LDS are applicable to the section only. Nevertheless, they may be referenced in the CDS. A program segment is exclusively made up of unalterable items (instructions), and this improves relocatability and simplifies writing of re-entrant sub-routines.

#### III-3. SECTION AND SEGMENT BASES

#### • General base G

General base G is uniquely assigned to the program; it constitutes an implicit base to which every address referenced by this program is related. Accordingly, the micro-processor automatically adds this base value to all addresses specified in the instructions.

#### Local base L

Local base L is the implicit base value for all local data contained in a local data segment (LDS).

Program base P

Program base P is assigned to a local program segment (LPS).

Initially, base P is the starting address of the section and from there on acts as a program counter for the currently executed section (see Chapter III-2.).

The actual values of L- and P-bases may be unknown at the time a program is written. At linkage edition time, they are automatically generated in relative value with respect to the general base of the program and stored in the associated PRT.

#### 111-4. CONSEQUENCES OF MODULARITY ON MITRA 15 PROGRAMS

From the hardware viewpoint, modularity implies the existence of special instructions for section calls and returns.

From the software viewpoint, program modularity is a fundamental concept of the assembly language which includes so-called "segmentation" pseudo-instructions :

- CDS : Common Data Section

- LDS : Local Data Segment

- LPS : Local Program Segment

- FIN : End of segment or section (LDS, LPS or CDS)

- IDS : Indirect Data Segment.

We shall call "program module" the result of an assembly or compilation processing. When a module is written in assembly language it is rather called "assembly module". Every assembly module must conclude with an END pseudo-instruction. A program may be built up from modules of various origins (differing by their source language, author, creation date, etc.).

The linkage editor interconnects the various modules into a complete executable program.

Remark :

To facilatate the programming, particularly in the case of re-entrant sub-routines, the assembler recognizes so-called "dummy data segments" which are images of later-defined data or of data belonging to another LDS (or CDS) than the LDS in which the dummy area is defined.

These dummy segments are treated as formal parameters, in particular for defining relative displacements with respect to the beginning of the segment (description of dynamic data blocks, index values, etc.) but generate no object code.

Example 1 : Typical organization of a program

| LOCP  | LDS    |       |         |           |

|-------|--------|-------|---------|-----------|

|       | RES    | 2     |         | ١         |

| U     | DATA,1 | 28    | local   |           |

| V     | DATA,1 | 31    | da ta   |           |

| TAB   | DATA   | ATAB  | section |           |

| ATAB  | RES    | 1024  |         | 1         |

|       | FIN    |       |         |           |

|       |        |       |         | Section 2 |

| PRINC | LPS    | LOCP  |         |           |

| INIT  | LDA    | U     |         |           |

|       | ADD    | = C1  |         |           |

|       | STA    | TAB   | program |           |

|       | CLS    | SPROG | section |           |

|       | CSV    | MEXIT |         |           |

|       | FIN    | INIT  |         | 1         |

|       | END    | PRINC |         |           |

Example 1 : Typical organization of a program (continued)

End of file code (%EOD on card and paper tape).

| PROG | CDS<br>:<br>FIN         |              |                                                                                                                                                                                                 |

|------|-------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPSI | LPS<br>:<br>FIN<br>EN D | PROG<br>LPS1 | This LPS having no associated LDS cannot use<br>the local addressing mode; it must use the<br>general addressing mode                                                                           |

|      | CDS<br>: .<br>FIN       |              |                                                                                                                                                                                                 |

| LDS1 | LDS<br>:<br>FIN         |              |                                                                                                                                                                                                 |

| LPSI | LPS<br>:<br>FIN         | LDSI         | These two LPS are both associated with the<br>same LDS. The local symbols are deleted at<br>the beginning of the next LDS. Nevertheless,                                                        |

| LPS2 | LPS<br>:<br>FIN<br>END  | LDS1         | there are two distinct sections (two items in<br>the PRT).<br>The local base L being initially the same for<br>both sections, no mutual calls are allowed<br>(through CLS pseudo-instructions). |

۲

|      | CDS<br>:<br>FIN        |      |                                                                                                                                         |

|------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| LDS1 | LDS<br>:<br>FIN        |      | This LPS having no associated LPS, it is only accessible through indirect addressing via an item of the CDS.                            |

| LDS2 | LDS<br>:<br>FIN        |      |                                                                                                                                         |

| LPS2 | LPS<br>:<br>FIN<br>END | LPS2 | This LPS cannot refer to the LDS called LDS2,<br>since local symbols are deleted after every<br>occurence of an LDS pseudo-instruction. |

### Example 2 : Other possible special organizations (continued)

Example 3 :

| Fi                                 | st modu                                                 | le                                     | Seco                               | ond mod                                                  | ule                                  | Th                                 | ird mod                                                 | ule          | Remarks                                                                                                                                                                                                                                           |

|------------------------------------|---------------------------------------------------------|----------------------------------------|------------------------------------|----------------------------------------------------------|--------------------------------------|------------------------------------|---------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROG<br>C1<br>C2<br>C3<br>C4<br>C5 | CDS<br>RES<br>DATA<br>RES<br>DATA<br>RES<br>DATA<br>FIN | 4<br>D1<br>2                           | PROG<br>C1<br>C2<br>C3<br>C4<br>C5 | C DS<br>RES<br>DATA<br>RES<br>DATA<br>RES<br>DATA<br>FIN | DUM<br>16<br>2<br>4<br>D1<br>2<br>C2 | PROG<br>C1<br>C2<br>C3<br>C4<br>C5 | CDS<br>RES<br>DATA<br>RES<br>DATA<br>RES<br>DATA<br>FIN | 4<br>D1<br>2 | These CDS reflet each others.<br>The dummy CDS DUM do not<br>generate any object code.<br>They use to satisfy the general<br>addressing modes and the refe-<br>rences. Also they enable each<br>program to have in clear the<br>elements it uses. |

| LDS1<br>D1<br>LPS1<br>DEB1         | LDS<br>RES<br>DATA<br>FIN<br>LDS<br>LDA                 | 2<br>C1<br>LDS1<br>D1                  |                                    |                                                          |                                      |                                    |                                                         |              |                                                                                                                                                                                                                                                   |

|                                    | CLS<br>CLS<br>CSV<br>FIN<br>END                         | LPS2<br>LPS3<br>M:EXIT<br>DEB1<br>LPS1 |                                    |                                                          |                                      |                                    |                                                         |              |                                                                                                                                                                                                                                                   |

| 4057 | U |

|------|---|

|      |   |

#### Example 3 :

| First module | Sec                             | cond ma                                                                                           | odule | T                      | hird mo                                                                                           | dule | Remarks                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|---------------------------------|---------------------------------------------------------------------------------------------------|-------|------------------------|---------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | D2<br>D3<br>D4<br>LPS2<br>DE B2 | LDS<br>RES<br>DATA<br>RES<br>DATA<br>DATA<br>FIN<br>LPS<br>LDA<br>LDX<br>STA<br>RTS<br>FIN<br>END |       | LDS2<br>D2<br>D3<br>D4 | LDS<br>RES<br>DATA<br>RES<br>DATA<br>DATA<br>FIN<br>LDS<br>LDA<br>LDX<br>STA<br>RTS<br>FIN<br>END |      | The two program segments<br>LPS2 and LPS3 are linked to<br>the same data segment LDS2.<br>They are separely assembly,<br>but one of the two references<br>a dummy segment DUM which<br>also uses to satisfy the local<br>addressing modes and allows<br>the programmer to have in<br>clear the elements he uses.<br>The DUM segment do not<br>generate any object code. |

|              |                                 |                                                                                                   |       |                        |                                                                                                   |      |                                                                                                                                                                                                                                                                                                                                                                         |

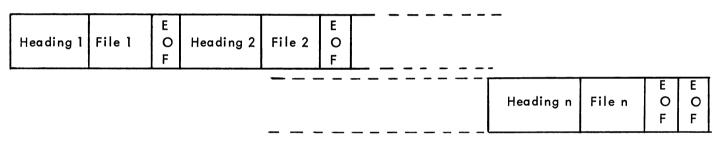

After these three modules be linked, a executable IMT of the following forme will be obtain.

| CDS<br>PROG | LDS<br>LDS1 | LPS<br>LPS1 | LDS<br>LDS2 | LPS<br>LPS2 | LPS<br>LPS3 |

|-------------|-------------|-------------|-------------|-------------|-------------|

| Running     |             |             |             |             |             |

| section     |             |             |             |             |             |

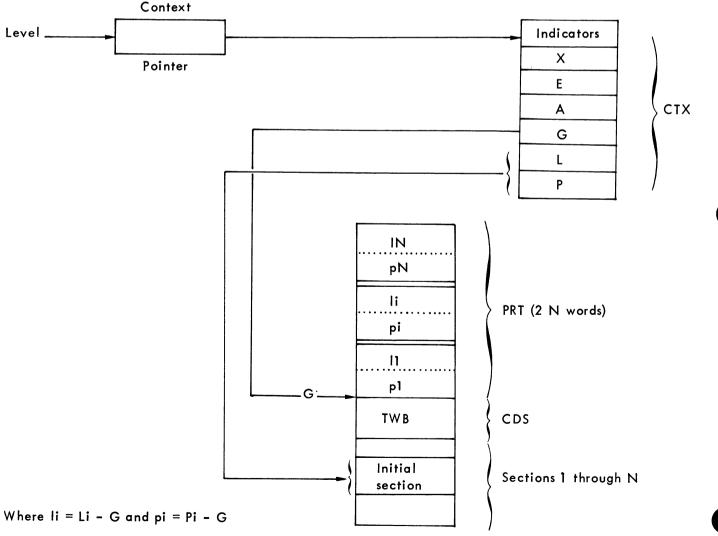

#### 111-5. CONSTITUENTS OF A PROGRAM

#### Task Working Block (TWB)

The first sixteen words of the CDS are called the "Task Working Block" or TWB.

This 16-word area is reserved to the Monitor which may store therein the return address to the calling task, as well as the caller's local data base (L) and the program indicators.

The Monitor may maintain in the TWB a pointer to the system's common data area (ZC).

All programs which require Monitor Calls must reserve 16 words at the beginning of their respective CDS.

This feature allows for monitor sections re-entry, the latters operating in the calling program.

#### Program Relocation Table (PRT)

The sections are assigned through a section relocation double-word (SRD), which contains the initial values of L and P with respect to G :

The PRT is made up of all the SRD of the program sections.

This PRT is stored in the locations immediately preceding G-address, thus the SRD of section no.  $\underline{n}$  has an address given by :

G - 4n

This table is built at linkage edition time.

Note :

The Monitor's PRT is pointed to by the contents of a fixed address as that of the micro-processor (address 12).

The PRT is the communication area between the different sections of a same program or between a program and the Monitor (for the Monitor's PRT).

Structure of a program

Remark :

The CDS, which is accessible from any section of a program, constitutes an implicit communication area between the sections.

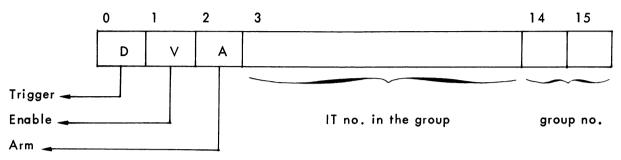

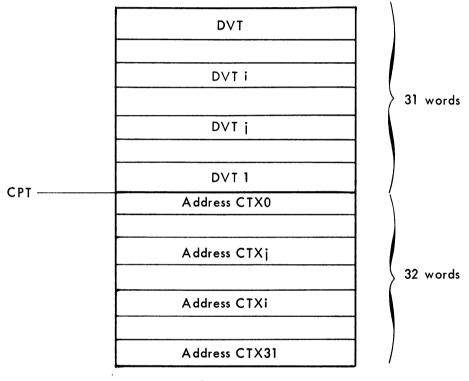

De-activation word table or DeVice Table (DVT)

This 32-word table precedes in core memory the Context Pointer Table (CPT) which is also 32-word long.

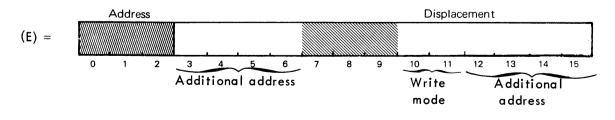

A DVT word has the following format :

Bits 3 to 15 are also called "interrupt configuration".

The interrupt system and the DVT are described in Chapter II.

#### Context (CTX)

The context is the communication area between a priority level and an associated program. It groups seven words :

- Word 1 : Status indicators

- Word 2 : Initial X value

- Word 3 : Initial E value

- Word 4 : Initial A value

- Word 5 : Initial G value

- Word 6 : Initial L value

- Word 7 : Initial P value

The context is used for initializing and restarting a task, and for protecting its status when the corresponding level is activated or de-activated.

When activated, a task level defines in the context table (CTX) the specific pointer fo the associated context. P-, L-, G-, A-, E- and X-registers, as well as the status indicators are loaded from the context area and program execution begins at address P.

Conversely, when a level is interrupted by a higher priority level, or when it is acknowledged, the current contents of P-, L-, G-, A-, E- and X-registers and of the status indicators are stored in the context area.

For further details, see DIT instruction description (Chapter VII).

#### III-6. SECTION CALLS

There are two kinds of sections :

- sections pertaining to a given program, accessible through a CALL SECTION (CLS).

- sections available to all programs : supervisor section or common library section, accessible through a CALL SUPERVISOR (CSV).

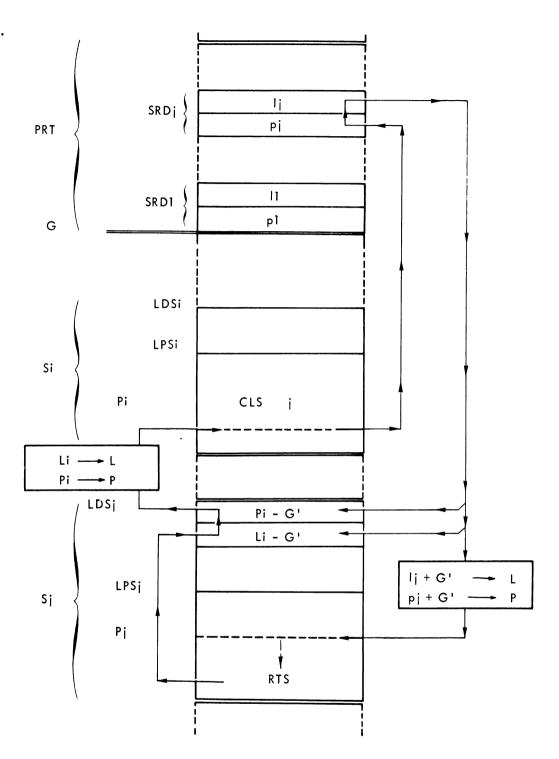

Program section call (CLS instruction)

During the execution of a CLS instruction, the processor :

- stores the contents of P (program address) and L (local data base) in the first two words of the called section's local area (after subtracting G-base). These elements are required for "returning" to the task and therefore must be saved.

- Loads P- and L-registers with the starting address and the local data segment address, respectively, of the called section which may then be executed.

During the execution of a RTS (ReTurn Section), the processor :

- Restores in P- and L-registers the values which had been saved at the beginning of the called section's local segment.

#### Note :

When several sections of a program are separately assembled, if one contains a call to another, it is not necessary to declare that the calling section is external to the module. This declaration is implicit and the linkage editor performs the necessary checks.

The transfer diagram is given in the description of CLS instruction (Chapter VII "Instructions").

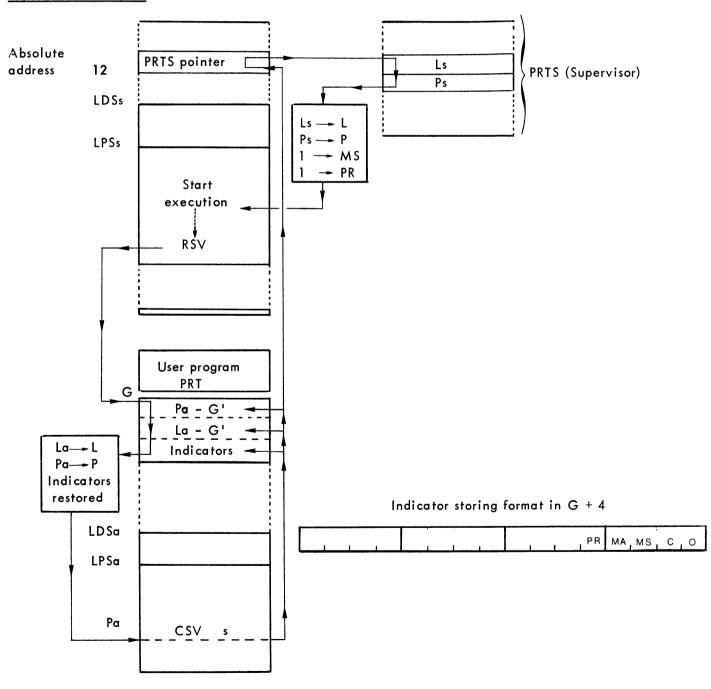

#### Supervisor call (CSV instruction)

The supervisor sections and the sections constitued by common sub-programs make up the "resident operating system".

Hereafter, we shall call "system section" a section of the operating system.

A "system section" :

a) remains at the calling program's priority level;

b) processes both the calling task's data and its own local data;

c) is automatically executed in master mode.

Moreover, since a task is identified by its G-base value it is logical to associate the call with this base rather than L-base.

In the CALL SUPERVISOR, i.e. in a system section, G has the same function as L in the CALL SECTION.

Paragraph (c) above, which is associated with class 0 addressing modes (see chapter V), implies paragraph (b) since a system section may :

- access its own data in LD, LI and LIX addressing modes, it being understood that these data have absolute addresses and, therefore, system sections are resident with an implicit zero local base. (In this respect, the operating system is a single program).

- access the calling task data in GD and GIX addressing modes, since the general base G remains that of the calling task.

When executing a RETURN SUPERVISOR instruction (RSV), the processor restores in L- and P-registers the values which had been previously saved in the calling program's TWB.

The mode of the calling program is automatically re-established by RSV instruction.

The communication diagram of a supervisor call is given in the description of CSV instruction (Chapter VII).

#### Example of re-entrant section programmation

M:MOVE module of MOB Monitor for moving a byte string.

• Main program

| PRINC                                                        | CDS<br>RES<br>FIN                                                  | 16                                                 | <b>TWB</b>                                                                                                                                                                                                   |