#### PREFACE

This manual is for integrators of systems based on Little Board/PLUS. It contains information on hardware requirements and interconnection, and details of how to use the system. There are five chapters, organized as follows:

- Chapter1- GENERAL DESCRIPTION: General information pertaining to the Little Board/PLUS, its major features, and a brief functional description of the board.

- Chapter 2 INTEGRATING A SYSTEM: Descriptions of the external components necessary to construct a CP/M-based system with floppy and hard disk drives. Included are tables listing the pinouts of each of the six board connectors, as well as features and special considerations concerning the board's peripheral interfaces.

- Chapter 3 USING THE SYSTEM: System power-up procedures, and operation with AMPRO's enhanced CP/M operating system and utilities.

- Chapter 4 THEORY OF OPERATION: Detailed technical information on Little Board/PLUS hardware.

- Chapter 5 PROGRAMMER'S REFERENCE: I/O port addresses and programming information regarding custom programming of Little Board/PLUS.

Only brief descriptions and instructions regarding the Little Board/PLUS system software are provided in this manual. For full details on the AMPROsupplied system software, please refer to the Z80 System Software User's Manual (AMPRO part number A74006).

# PLEASE NOTE

Specifications are subject to change without notice. The contents of this document are believed to be accurate. If errors are found, please notify AMPRO COMPUTERS INC., at the address shown on the title page of this document.

The following is a list of trademarks used within this document:

Z80: Zilog, Inc.

CP/M: Digital Research, Inc.

IBM: International Business Machines

ZCPR3: Richard L. Conn

LITTLE BOARD, LITTLE Board/PLUS, SCSI/PLUS: AMPRO Computers, Inc.

No part of this document may be reproduced in any form, for commercial purposes without the express written consent of AMPRO Computers, Inc.

# Copyright (C) 1985, AMPRO COMPUTERS INCORPORATED

# TABLE OF CONTENTS

| CHAPTER 1 - GENERAL DESCRIPTION    |      |

|------------------------------------|------|

| 1.1 Introduction                   | 1-1  |

| 1.2 Features                       | 1-1  |

| 1.3 Functional Description         | 1-2  |

| 1.3.1 CPU, Memory, and Timing      | 1-2  |

| 1.3.2 Serial I/O Ports             | 1-2  |

| 1.3.3 Parallel I/O Port            | 1-2  |

| 1.3.4 Floppy Disk Controller       | 1-3  |

| 1.3.5 SCSI/PLUS Multi-Master Bus   | 1-3  |

| 1.4 Specifications                 | 1-4  |

| -                                  |      |

| CHAPTER 2 - INTEGRATING A SYSTEM   |      |

| 2.1 Introduction                   | 2-1  |

| 2.2 What Is Needed                 | 2-1  |

| 2.2.1 DC Power                     | 2-1  |

| 2.2.2 Reset, Power LED             | 2-3  |

| 2.2.3 Parallel Printer             | 2-3  |

| 2.2.4 Serial Ports                 | 2-3  |

| 2.2.5 Floppy Disk Interface        | 2-3  |

| 2.2.6 SCSI/PLUS Interface          | 2-4  |

| 2.2.7 ID Input Port                | 2-4  |

| 2.3 Board Jumper Configurations    | 2-5  |

| 2.4 Booting the System             | 2-7  |

| 2.5 Troubleshooting                | 2-8  |

|                                    |      |

| CHAPTER 3 - USING THE SYSTEM       |      |

| 3.1 Introduction                   | 3-1  |

| 3.1.1 Software References          | 3-1  |

| 3.1.2 Conventions                  | 3-1  |

| 3.2 First Time Use                 | 3-2  |

| 3.2.1 Making Backup Disks          | 3-2  |

| 3.2.2 Customizing Your System Disk | 3-3  |

| 3.3 Operating System Features      | 3-4  |

| 3.3.1 CP/M 2.2 BDOS                | 3-4  |

| 3.3.2 AMPRO Custom BIOS            | 3-4  |

| 3.3.3 ZCPR3 Command Processor      | 3-5  |

| 3.4 AMPRO-Supplied Utilities       | 3-8  |

| 3.4.1 CP/M Utilitiy Programs       | 3-8  |

| 3.4.2 AMPRO Utilities              | 3-9  |

| 3.4.3 ZCPR3 Utilities              | 3-10 |

| 3.4.4 Public Domain Programs       | 3-11 |

| 3.5 Generating Different Systems   | 3-11 |

|                                    |      |

| CHAPTER 4 - THEORY OF OPERATION    |      |

| 4.1 Introduction                   | 4-1  |

| 4.2 CPU, Memory, and Timing        | 4-1  |

| 4.3 Board Control Register         | 4-2  |

| 4.4 Serial Ports                   | 4-2  |

| 4.5 Parallel Printer Port          | 4-3  |

| 4.6 Floppy Disk Interface          | 4-4  |

| 4.7 SCSI/PLUS Interface            | 4-4  |

| CHAPTER 5 - PROGRAMMERS'    | REFERENCE |     |

|-----------------------------|-----------|-----|

| 5.1 Introduction            |           | 5-1 |

| 5.2 Z80A CPU                |           | 5-1 |

| 5.3 Memory                  |           | 5-1 |

| 5.4 Board Control Register  |           | 5-2 |

| 5.5 Counter/Timer Circuit   |           | 5-3 |

| 5.6 Serial Ports            |           | 5-3 |

| 5.7 Baud Rate Generation    |           | 5-4 |

| 5.8 Floppy Disk Interface   |           | 5-5 |

| 5.9 Parallel Printer Port   |           | 5-5 |

| 5.10 ID Input Port          |           | 5-5 |

| 5.11 SCSI/PLUS Interface    |           | 5-6 |

| 5.11.1 SCSI (SASI) Programm | ning      | 5-6 |

| 5.11.2 Simple Bidirectional | I/O       | 5-7 |

# APPENDIX A - BOARD DIAGRAM, PARTS LIST, AND SCHEMATIC

APPENDIX B - TYPICAL INTERFACE CABLES

APPENDIX C - USER GROUPS

APPENDIX D - COMPONENT DATA SHEETS

### **CHAPTER 1**

# **GENERAL DESCRIPTION**

# **1.1 INTRODUCTION**

This chapter provides an overview and functional description of the AMPRO Little Board/PLUS single board computer. It is intended to provide a basic understanding of the Little Board/PLUS, and how it forms the basis of a compact, powerful computer system.

#### **1.2 FEATURES**

Little Board/PLUS is a complete 8-bit, Z80-based single board microcomputer. It includes all the circuitry, software, and firmware necessary to construct a functional CP/M-based computer system. Some of the main features are:

- 4MHz Z80A 8-bit microprocessor

- 64K bytes dynamic RAM, 4K-32K EPROM

- Two spare counter/timer channels

- Floppy controller capable of controlling from one to four single- or double-sided, single- or double-density, 40- or 80-track mini or micro floppy drives

- Two RS232C serial ports

- One Centronics printer port

- SCSI/PLUS multi-master I/O expansion bus:

- SASI Disk/Tape controller compatible

- ANSC X3T9.2 (SCSI) compatible

- Multiple Little Board networking

- Simple bi-directional I/O (17 lines)

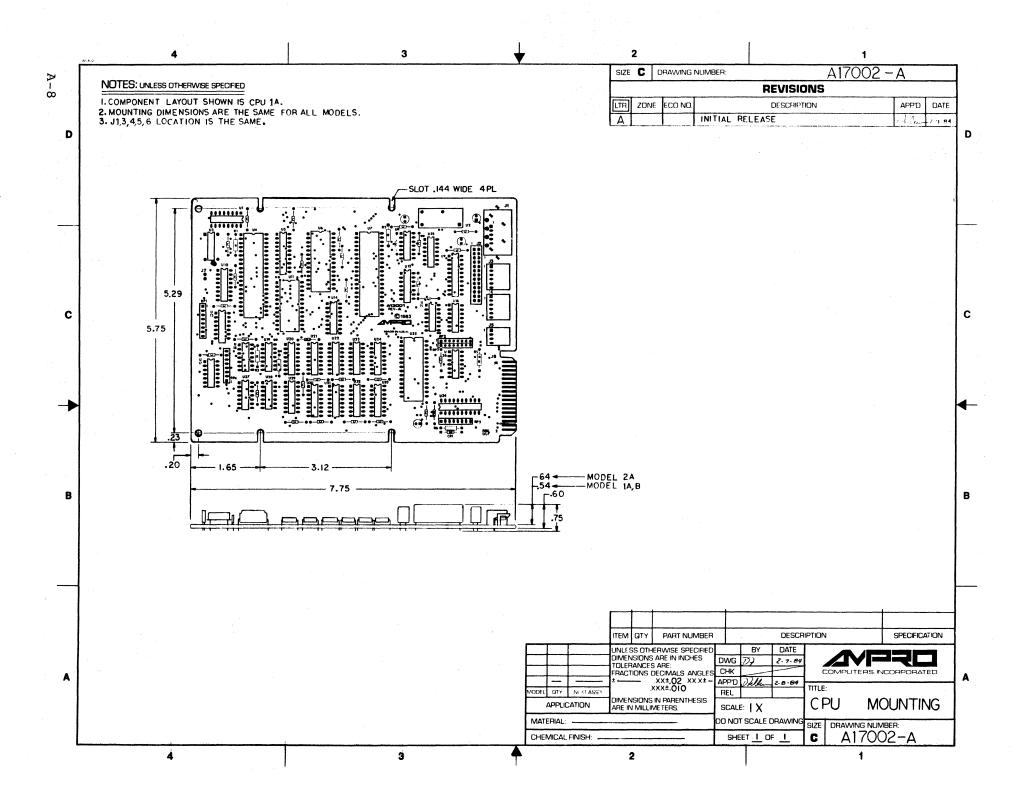

- Mounts directly to a 5-1/4" disk drive

- Minimum external components

- Power connector and voltages compatible with 5-1/4 inch disk drives

# **1.3 FUNCTIONAL DESCRIPTION**

The following paragraphs briefly describe the Little Board/PLUS single board computer. More detailed information can be found in Chapter 4, Theory of Operation.

# 1.3.1 CPU, Memory, and Timing

The heart of the Little Board/PLUS is a Z80A 8-bit microprocessor operating at 4 MHz. All system functions are based on a single 16 MHz master clock. System RESET is provided in two ways: upon power-up and via an external RESET switch.

Two types of memory are present: EPROM and RAM. A single 28-pin EPROM socket provides from 4K to 32K bytes of firmware space. Jumpers are used to program the socket for a 2732, 2764, 27128, or 27256 type EPROM. The EPROM can be enabled and disabled by software.

System RAM consists of eight  $64k \ge 1$  bit dynamic RAM devices. Control circuitry for the RAM memory is entirely digital (no one-shots or R-C components) and provides a high degree of reliability.

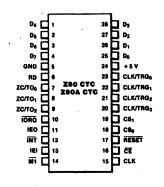

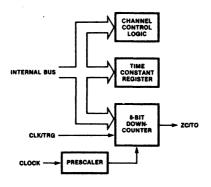

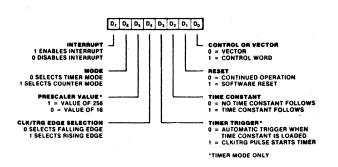

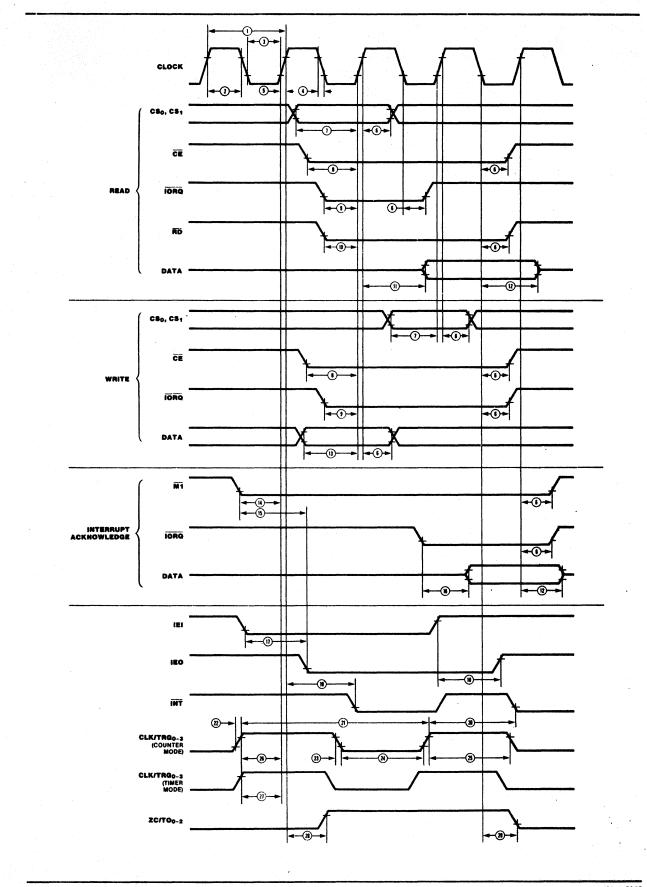

A Z80 Counter Timer Circuit (CTC) provides four programmable counter or timer channels. Two of the CTC channels provide the baud rate clocks used by the two serial I/O ports. The other two CTC channels are available for use as programmable timers in applications programs, for real-time clock functions, etc.

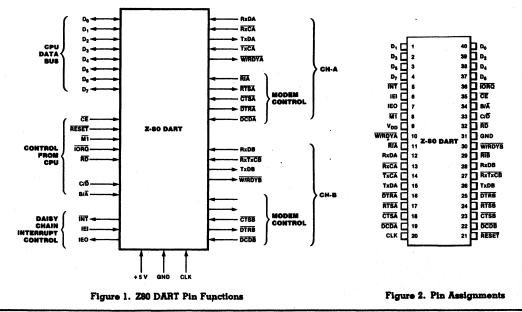

# **1.3.2** Serial Ports

A Z-80 Dual Asynchronous Receiver/Transmitter (DART) provides two fully programmable serial I/O ports. Each channel has four of the standard RS232C signals: TxD, RxD, RTS, and CTS. These signals are sufficient for interfacing most serial printers, modems, and terminals. In those cases where other interface signals are required for one of the serial ports, handshaking signals can be borrowed from the second port (if not needed by that port). Polarity and use of the handshaking signals is defined by the software.

Programmable baud rate clocks are supplied by the CTC for baud rates up to 9600 baud. Additional circuitry provides baud rates of 19.2K and 38.4K baud, for Port A only. Since the two serial ports are otherwise identical, either can be programmed as a terminal, modem, serial printer, or other RS232C interface.

#### **1.3.3** Parallel Printer Port

The parallel printer port provides the 10 essential signals of a Centronicstype printer interface: Data Bits 1-8, Data Strobe, and Busy. Both the Data Strobe (output) and Busy (input) handshake protocols are defined by software.

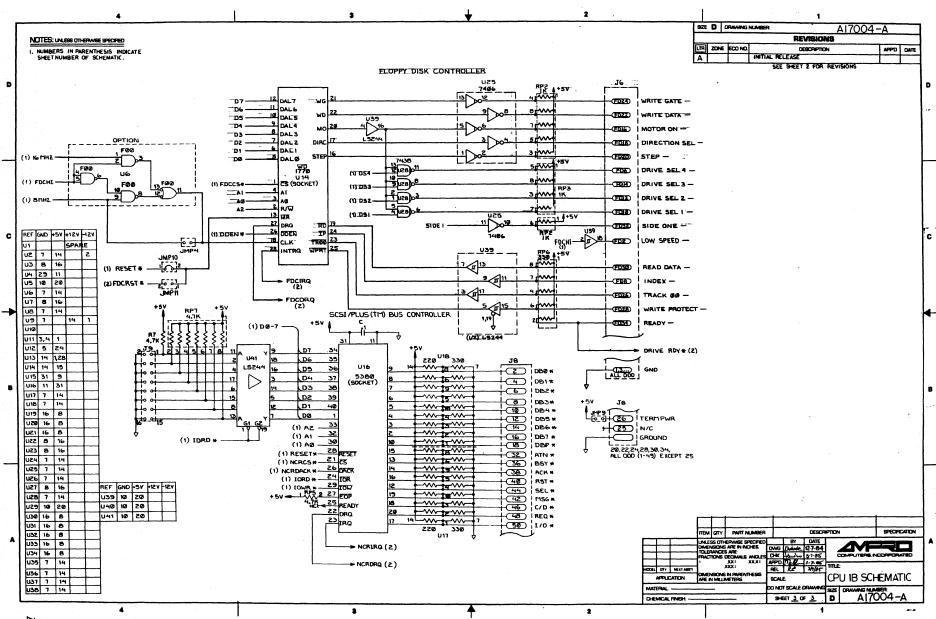

### **1.3.4 Floppy Disk Controller**

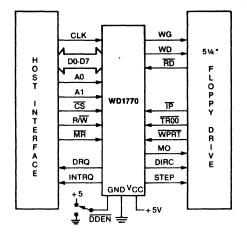

A Western Digital 1772 floppy disk controller device provides all of the functions required to interface with standard 5-1/4 inch "mini" -- and most 3 to 4 inch "micro" -- floppy disk drives. The 1772 includes the following capabilities within a single LSI device:

- Digital phase locked loop

- Digital write precompensation

- Motor on start/stop delay

- Software controlled step rates

Timing for the floppy disk interface is derived directly from the 8 MHz system clock, without delay lines, R-C time constants, or one-shots. This again results in a very high degree of system reliability.

# 1.3.5 SCSI/PLUS Multi-Master Bus

A 50-pin "ribbon cable bus" interface which meets the specifications for the popular Small Computer System Interfaces (SCSI) -- formerly called "SASI" -- provides a general purpose multi-master I/O expansion bus. All SCSI Initiator and Target functions are fully supported, including bus arbitration and disconnect/reselect.

In addition, Little Board/PLUS supports the Initiator function of AMPRO's innovative SCSI/PLUS extension to SCSI. This allows connection of up to 64 SCSI/PLUS Target devices, rather than the usual eight device limit of SCSI.

Applications include both direct and shared use of a wide variety of controllers and devices, as well as tightly coupled Little Board networks. For example, one or more Little Boards, an SCSI Winchester controller, and modules providing calendar/clock, serial port expansion, RAM disk, etc., might all coexist on the same SCSI/PLUS bus.

The 17 bidirectional I/O signals of the SCSI/PLUS interface may also be used as general purpose software-controlled digital I/O lines, without SCSI compatibility. In this case the board's 8-bit SCSI bus ID input register can serve as an additional 8-bit input port.

# **1.4 LITTLE BOARD/PLUS SPECIFICATIONS**

| CPU:            | 4MHz Z80A, 8-bit microprocessor                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMORY:         | 64 kilobytes of dynamic RAM<br>4-32 kilobytes of EPROM                                                                                                                                                                                                                                                                                                                                           |

| TIMER:          | Z80A CTC (4 channels)<br>2 channels not used by AMPRO software                                                                                                                                                                                                                                                                                                                                   |

| SERIAL I/O:     | <ul> <li>Z80A Dual Asynchronous Receiver/Transmitter (DART)</li> <li>Two - RS232C compatible ports: DB-25 female conns.</li> <li>Software-controlled baud rates:</li> <li>Channel A - 75 to 38,400 baud</li> <li>Channel B - 75 to 9600 baud</li> <li>Four standard RS232C signals per port:</li> <li>Data Out</li> <li>Data In</li> <li>Handshake Out</li> </ul>                                |

|                 | Handshake Out<br>Handshake In<br>Two Ground pins                                                                                                                                                                                                                                                                                                                                                 |

| PARALLEL I/O:   | Centronics-compatible printer port<br>10 signals supported:<br>Data Bits 1-8 - output<br>Data Strobe - output<br>Printer Busy - input<br>12 Ground pins                                                                                                                                                                                                                                          |

| DISK I/O:       | No. drives supported: 1 - 4<br>Disk Controller: WD1772<br>Data rate: 250k bps (MFM), 125K bps (FM)<br>Sector size: 128, 256, 512, or 1024 bytes<br>Phase locked loop: digital (8 mHz)<br>Write precompensation: software enabled<br>Drive capacity (formatted):<br>Type 1 (40 track, 1-sided) - 200K bytes<br>Type 2 (40 track, 2-sided) - 400K bytes<br>Type 3 (80 track, 1-sided) - 400K bytes |

| SCSI/PLUS BUS I | NTERFACE: SASI Compatible<br>ANSI X3T9.2 (SCSI) compatible<br>SCSI/PLUS Initiator compatible<br>Uses NCR 5380 SCSI bus controller                                                                                                                                                                                                                                                                |

| POWER:          | Same power connector and voltabes as mini and micro<br>floppy disk drives.<br>Power Requirements: +5VDC at 0.95A<br>+9 to 12VDC at 0.05A                                                                                                                                                                                                                                                         |

| ENVIRONMENT:    | Temperature:0 to 32 degrees C, operatingHumidity:5 to 95%, non-condensingAltitude:0-10,000 feet                                                                                                                                                                                                                                                                                                  |

1-4

| SIZE:        | 7.75 x 5.75 x 0.75 inches                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOFTWARE:    | Boot program in 2732 EPROM<br>CP/M Version 2.2 and BIOS on diskette<br>Little Board/Plus system utilities<br>Option: FRIENDLY Integrated Operating Environment<br>Option: BIOS and Utilities source code |

| DOCUMENTATIO | ON: Little Board/Plus Technical Manual<br>Little Board/Plus Software Manual<br>Option: SCSI/PLUS Technical Specification                                                                                 |

#### **CHAPTER 2**

# INTEGRATING A SYSTEM

# 2.1 INTRODUCTION

This chapter describes what is required to build a floppy or hard disk based computer system using Little Board/PLUS as the heart of the machine. Details are provided concerning external device requirements, the boards connector pinouts, how to prepare the board for use, and connection of peripherals such as terminals, printers, and modems. Refer to Appendix B for tables.

### 2.2 WHAT IS NEEDED

A very minimum number of external parts will turn the Little Board/PLUS circuit board into a very powerful computer system. The items listed in Table 2-1 are easily available components.

| Item                                            | Description                                                                                      |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Floppy drive(s)                                 | 1 to 4 mini or micro floppy drives, 40 or 80 track, single- or double-sided                      |

| SCSI (SASI) hard<br>disk controller<br>(option) | Adaptec ACB-4000 or Xebec 1410(A), or equivalent<br>SCSI (SASI) hard disk controller             |

| Hard disk drive(s)<br>(option)                  | 5 to 20 Megabyte drive(s); must be compatible with your specific SCSI (SASI) controller          |

| Power supply                                    | +12VDC @ 2.0A, +5VDC @ 2.5A (2 floppies);<br>additional power, as required for hard disk options |

| Reset switch                                    | SPST, normally open, w/LED indicator                                                             |

| Cables                                          | Serial (2), parallel, floppy, SCSI, and power cables for Little Board/PLUS and drives            |

| Cabinet                                         | Housing for completed system                                                                     |

| Table 2-1. System Compone | ients |

|---------------------------|-------|

|---------------------------|-------|

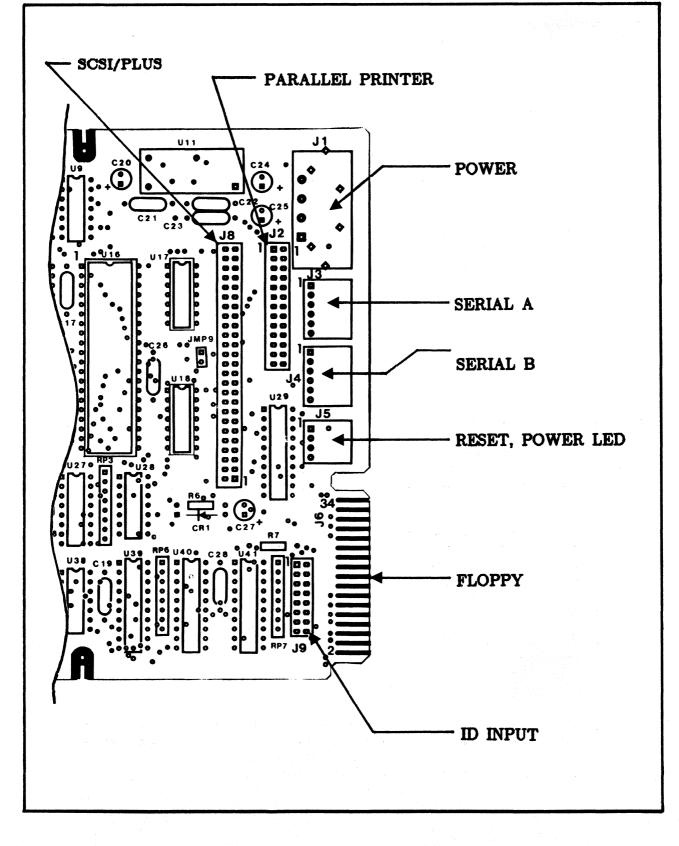

Figure 2-1 shows the Little Board/PLUS interface connectors. All components can be housed in a very small box. The size is determined primarily by the disk drives, and perhaps the power supply. A space of approximately 7 x 8 x 11 inches is adequate for a dual floppy system. Tables 2-2 through 2-7 list the cable connector pinouts for the board's interface connectors. Table 2-2 provides suggested mating connectors and manufacturers' part numbers.

| Board<br>Connector | Function                                        | Part                    | Number                                           |

|--------------------|-------------------------------------------------|-------------------------|--------------------------------------------------|

| J1                 | Power Connector                                 |                         | AMP 1-480424-0<br>AMP 60619-1<br>(4 req.)        |

| J2                 | Parallel Printer,<br>Board end                  | 3M:<br>T&B:<br>Molex:   | 3399-6000<br>609-2601M<br>15-29-8262             |

|                    | Parallel Printer,<br>Printer end                | AMP:<br>3M:<br>T&B:     | 57F-30360<br>3366-1001<br>609-36M                |

| J3,4               | Serial Ports A,B                                |                         | Molex 22-01-2067<br>Molex 08-50-0114<br>(6 req.) |

| J5                 | RESET, Power LED                                | Housing:<br>Contacts:   | Molex 22-01-2047<br>Molex 08-50-0114<br>(4 req.) |

| J6                 | Floppy Disk Interface<br>(Card edge connectors) | 3M:<br>T&B:<br>Molex:   | 3463-0001<br>609-3415M<br>15-29-0341             |

| 18                 | SCSI/PLUS Interface                             | T&B:<br>Molex:<br>Berg: | 609-5000M<br>15-29-8502<br>66902-150             |

# Table 2-2. External Connector Part Numbers

# NOTE

All Little Board/PLUS software is distributed on doublesided 48 tpi AMPRO format mini floppy diskettes. This may be directly read from, or booted, in either a 48 or 96 tpi mini floppy drive. The only special requirement for **first time** booting of the system is that you have a double-sided 48 or 96 tpi mini floppy drive capable of stepping at a 6 mS step rate, and a terminal capable of 9600 baud operation. Once you have initially booted the system, you may then generate a system disk with alternative defaults, e.g., single-sided, micro floppy, 12 mS step rate, 19.2K baud terminal data rate, etc.

Figure 2-1. Little Board/PLUS Connector Locations.

# 2.2.1 DC Power

The power connector (J1) pinout is identical with that of the power connectors on nearly all 5-1/4 inch floppy disk drives. Note that pin 1 on J1 is reversed from the other connectors on the same end of the board. Refer to Table 2-3 for power connections.

#### CAUTION

BE SURE THE POWER PLUG IS CORRECTLY WIRED BEFORE ATTEMPTING TO APPLY POWER TO THE BOARD.

| Pin | Signal Name | Function      |

|-----|-------------|---------------|

| 1   | +12VDC      | +6 to + 15VDC |

| 2   | Ground      | Ground return |

| 3   | Ground      | Ground return |

| 4   | +5VDC       | +5VDC +/- 5%  |

Table 2-3. Power Connections (J1)

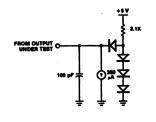

# 2.2.2 RESET, Power LED

This connector is for connection to an external SPST switch, to provide the master RESET signal. In addition, a 15 mA current source provides power to an LED power-on indicator. Refer to Table 2-4 for the pinout of connector J5.

| Pin | Signal Name   | Function                                    |

|-----|---------------|---------------------------------------------|

| 1   | Ground        | To LED Cathode                              |

|     | LED<br>Ground | To LED Anode<br>To one side of RESET switch |

| 4   | RESET         | To other side of RESET switch               |

Table 2-4. RESET, Power LED Connector (J5)

#### 2.2.3 Serial Ports

Table 2-5 lists the connector pinout and signal definitions for each of the two RS232C serial I/O ports. Serial Port A is board connector J3, and Serial Port B is board connector J4. Appendix B gives typical cable wiring for connection to terminals, serial printers, and modems.

| Pin                        | Signal Name                                  | Function                                                                                                       | in/out                     | DB-25 Pin<br>(DCE)          |

|----------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|

| 1<br>2<br>3<br>4<br>5<br>6 | Ground<br>Ground<br>TxD<br>HSO<br>RxD<br>HSI | Protective Ground<br>Signal Ground<br>Data Output<br>Hand Shake Out (RTS)<br>Data Input<br>Hand Shake In (CTS) | <br>out<br>out<br>in<br>in | 1<br>7<br>3<br>5<br>2<br>20 |

Table 2-5.

Serial Connectors (J3/J4)

# 2.2.4 Parallel Printer

The Little Board/PLUS parallel printer connector has a pinout that allows the use of flat ribbon cable between the J2 header and the first 26 lines of a 36 pin male Centronics-type connector at the printer end.

Refer to Table 2-6 for the printer connector's pinout and signal definitions. Note that the pin numbering convention for the board's header connector (J2) differs from that of Centronics connectors, even though the required interconnection cable is straight through. To clarify this, each signal's corresponding Centronics connector pin number has been included in Table 2-6.

| J2<br>Pin | Signal Name | Function            | in/out | Printer<br>Pin |

|-----------|-------------|---------------------|--------|----------------|

| 1         | -DS         | Data Strobe         | out    | 1              |

| 3         | Data 1      | LSB of printer data | out    | 2              |

| 5         | Data 2      | •                   | :      | 3              |

| 7         | Data 3      | •                   | :      | 4              |

| 9         | Data 4      |                     | •      | 5              |

| 11        | Data 5      | :                   | :      | 6              |

| 13        | Data 6      | :                   | :      | 7              |

| 15        | Data 7      | :                   | :      | 8              |

| 17        | Data 8      | MSB of printer data | out    | 9              |

| 19        |             | (Not used)          |        |                |

| 21        | BUSY        | Printer BUSY        | in     | 11             |

| 23        |             | (Not used)          |        |                |

| 25        |             | (Not used)          |        |                |

| 2-22      | (even)      | Signal grounds      | ж      | 19-29          |

| 24,26     |             | (Not used)          |        | 30,31          |

Table 2-6.

Parallel Printer Connector (J2)

Appendix B provides a wiring table for a cable which will work with most Centronics compatible printers. The cable required is identical to that used with the Tandy (Radio Shack) TRS-80 Model 100 portable computer. The Tandy cable part number is 26-1409.

#### 2.2.5 Floppy Disk Interface

Table 2-7 lists the floppy disk drive interface connector (J6) pinout and signals. A single 34-conductor PC edgecard connector goes at the Little Board end, while there can be from 1 to 4 PC card edge connectors for connecting mini floppy disk drives. Micro floppy drives generally use 34-conductor header connectors, instead.

| Pin  | Signal Name    | Function              | in/out |

|------|----------------|-----------------------|--------|

| 2    | -LOW SPEED     | Speed select (option) | out    |

| 4    |                | (Not used)            |        |

| 6    | -DRIVE DEL 4   | Drive Select 4        | out    |

| 8    | -INDEX         | Index pulse           | in     |

| 10   | -DRIVE SEL 1   | Drive Select 1        | out    |

| 12   | -DRIVE SEL 2   | Drive Select 2        | out    |

| 14   | -DRIVE SEL 3   | Drive Select 3        | out    |

| 16   | -MOTOR ON      | Motor on control      | out    |

| 18   | -DIR SEL       | Direction select      | out    |

| 20   | -STEP          | Step                  | out    |

| 22   | -WRITE DATA    | Write data            | out    |

| 24   | -WRITE GATE    | Write gate control    | out    |

| 26   | -TRACK 00      | Track 00              | in     |

| 28   | -WRITE PRT     | Write protect         | in     |

| 30   | -READ DATA     | Read data             | in     |

| 32   | -SIDE ONE      | Side select           | out    |

| 34   | -READY         | Drive ready (option)  | in     |

| 1-33 | (all odd pins) | Signal grounds        |        |

Table 2-7.

Floppy Disk Interface Connector (J6)

Nearly any type of soft-sectored, single- or double-sided, 40- or 80-track, mini (5 1/4") or micro (3" to 4") floppy disk drive is usable with the Little Board. Naturally, the higher the quality of the drives you use, the better your system's reliability. Here are some things that may be helpful for you to know:

- As indicated earlier in this chapter, the default system parameters programmed on the standard Little Board/PLUS system disk, as shipped, require that drive A be a double-sided 48 or 96 tpi mini floppy drive, with 6 mS (or faster) stepping rate. Once you have booted that disk, you can create a new system disk with alternative defaults, allowing you to subsequently boot from any other system-compatible drive.

- The drives used must be compatible with the AMPRO floppy disk interface (see Table 2-7). This interface is generally referred to as SA-450 compatible.

- Use of high quality floppy disk drives is recommended; preferably having DC servo-controlled direct drive motors.

• The drives must be capable of 12 mS (or faster) stepping.

- More than one type of floppy disk drive, up to four, can be present in the system, and in any mix.

- Each disk drive must be jumpered for a specific Drive Select value, 1 through 4. Drive A is 1, B is 2, etc.

- Resistive terminations should be installed only on the drive connected to the last interface cable connector (farthest from the computer).

- When using drives with a Head Load option, jumper the drives for "head load with motor on" rather than "head load with drive select" jumpering.

# 2.2.6 SCSI/PLUS Interface

The SCSI/PLUS interface (J8) uses a 50-pin male header connector to interface with SCSI-compatible peripherals. Table 2-8 shows the signal names and pin numbers for the SCSI/PLUS bus interface connector. Refer to your disk controller documentation, or the ANSI SCSI (X3T9.2) specification, for information on the signal functions.

| Pin      | Signal         | Function             |  |

|----------|----------------|----------------------|--|

| 1 - 49   | (All odd pins) | Signal grounds       |  |

| 2        | -DB0           | Data Bit 0 (LSB)     |  |

| 4        | -DB1           | " " 1                |  |

| 6        | -DB2           | " " 2                |  |

| 8        | -DB3           | " " 3                |  |

| 10       | -DB4           | " " <u>4</u>         |  |

| 12       | -DB5           | " " 5                |  |

| 14       | -DB6           | " " 6                |  |

| 16       | -DB7           | " " 7 (MSB)          |  |

| 18       | -DBP           | Data Parity          |  |

| 20,22,24 | Ground         | Signal Ground        |  |

| 25       |                | (Not used)           |  |

| 26       | TERMPWR        | Termination +5 VDC   |  |

| 28,30    | Ground         | Signal Ground        |  |

| 32       | -ATN           | Attention            |  |

| 34       | Ground         | Signal Ground        |  |

| 36       | -BSY           | Busy                 |  |

| 38       | -ACK           | Transfer Acknowledge |  |

| 40       | -RST           | Reset                |  |

| 42       | -MSG           | Message              |  |

| 44       | -SEL           | Select               |  |

| 46       | -C/D           | Control/Data         |  |

| 48       | REQ            | Transfer Request     |  |

| 50       | -I/O           | Data direction       |  |

Table 2-8. SCSI Interface Connector (J8)

2-7

This interface can serve a variety of purposes, including connection of hard disk controllers, tape controllers, printer and communication servers, etc. In addition, the interface signals may be used as direct input/output lines, allowing the connection of TTL-level interfacing devices and sensors, etc. The output signals are open collector, 48mA drivers, and may be enabled and disabled under software control. On-board removable resistor networks provide bus termination.

# 2.2.7 ID Input Port

Eight pairs of jumper pins (J7) provides an ID Input Port, which can be used by SCSI-related software to determine the board's SCSI bus ID for bus arbitration (or other) purposes. If not required for this purpose the ID Input Port can be used as a general purpose 8-bit input port connector, with a flat ribbon cable connector plugged onto J7. Table 2-9 shows the signal names and pin numbers for J7.

| Pin                                                           | Signal                                                                 | Function                                                                                             |

|---------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| $ \begin{array}{r}1\\3\\5\\7\\9\\11\\13\\15\\2-16\end{array}$ | -ID7<br>-ID6<br>-ID5<br>-ID4<br>-ID3<br>-ID2<br>-ID1<br>-ID0<br>Ground | ID Bit 7 (MSB)<br>" " 6<br>" " 5<br>" " 4<br>" " 3<br>" " 2<br>" " 1<br>" " 0 (LSB)<br>Signal Ground |

Table 2-9. ID Input Port (J7)

# 2.3 BOARD JUMPER CONFIGURATIONS

Little Board/PLUS contains nine sets of jumpers, which may be used to customize the board's operation. The jumper sets consist of either two or three pins, with pin 1 a square pad; each jumper set is outlined with white boxes on the component side of the board. The options available through these jumpers are described in the following paragraphs.

# NOTE

Do not solder wires to the jumper pins, as this may void your board's warranty. Use wire wrap, or shorting plugs instead. For normal operation, no jumper setup is required. All of the jumper settings are factory-set, by means of shorting plugs on the pins, or traces on the bottom side of the board. Use of J7 (SCSI bus ID) varies, according to software requirements. AMPRO's standard hard disk software does not require the use of J7.

# JMP1 - Clock

This jumper, when shorted, connects the system 16 mHz master clock bus to the 16 mHz hybrid oscillator (U2). It is intended for test purposes only.

FACTORY SETTING: shorted

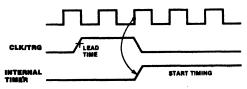

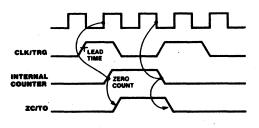

#### JMP2 - CTC CLK/TRG3

This jumper connects the CTC's CLK/TRG3 input (JMP2-2) to either the 1772 FDC's interrupt request output signal (JMP2-3) or to the CTC's ZC/TC2 output signal (JMP2-1).

FACTORY SETTING: both options open

# JMP3 - CTC CLK/TRG2

This jumper, when shorted, connects the 5380 SCSI controller's interrupt request output signal (JMP3-2) to the CTC'S CLK/TRG2 input (JMP3-1).

FACTORY SETTING: open

# JMP4 - U6 Option

This jumper is shorted for 8 mHz-only operation of the 1772 FDC device. NOTE: If this jumper is shorted, the clock multiplexor IC, U6 must not be present; if U6 is present, this jumper must be open.

FACTORY SETTING: open (U6 present)

# JMP5,6 - EPROM Type

These jumpers are used to program the board for various types of EPROM devices. These two jumpers are set as shown in Table 2-10.

| EPROM Type       | JMP5: 1-2 | JMP5: 2-3 | JMP6  |

|------------------|-----------|-----------|-------|

| 2732             | open      | short     | *     |

| 2764             | *         | *         | open  |

| 27128            | short     | open      | open  |

| 27256            | short     | open      | short |

| Factory setting: | open      | short     | open  |

### Table 2-10. EPROM Jumper Configurations

# Notes

- (1) Items indicated by \* can be open or shorted; however do not short both JMP5 options simultaneously.

- (2) When a 2732 24-pin EPROM is used, it must be plugged into the **lower** 24 pins of the 28-pin EPROM socket, so that the 2732's pin 1 plugs into pin 3 of the socket.

# JMP7 - DART RIA

This jumper, when shorted, connects the 1772 FDC's DRQ output singal (JMP7-2) to the DART's RIA input (JMP7-1).

FACTORY SETTING: open

### JMP8 - DART DCDA

This jumper, when shorted, connects the 5380 SCSI controller's DRQ output singal (JMP8-1) to the DART's RIA input (JMP8-2).

FACTORY SETTING: open

# JMP9 - SCSI Termination Power

This jumper, when shorted, connects the board's +5V DC power to the SCSI bus signal line provided for optional external termination.

FACTORY SETTING: open

# JMP10,11 - 1772 Reset

These jumpers provide a choice of hardware or software control of the 1772 FDC's master reset input. Shorting JMP10 connects the board's hardware -RESET signal (JMP10-1) to the 1772's reset input (JMP10-2). Shorting JMP11 connects the DART's DTRB output (JMP11-2) to the 1772's reset input (JMP11-1).

FACTORY SETTING: JMP10 shorted, JMP11 open (hardware RESET)

# U17,22 - SCSI Bus Termination

These two 14-pin sockets contain resistive termination networks for SCSI bus termination. Every SCSI bus should have one set of termination at each end of the bus. These networks should be removed from the board if the bus is terminated by two other devices. If the SCSI interface will not be required, power may be saved by removing these termination networks, along with the 5380 SCSI controller, from the board. For non-SCSI use, the 220/330 termination networks may also be replaced with alternate values.

# NOTE

The on-board resistive termination networks (U17, U22) should be present on two, and only two, SCSI bus devices. Be sure that the board's SCSI bus is terminated in at least one place (generally on the board); a non-terminated SCSI bus may "hang" the system up due to indeterminate signal levels.

#### **2.4 BOOTING THE SYSTEM**

With the system completed, only connection to a terminal and a source of power for the computer are required. Typical cable wirings for connection to terminals, serial printers, and modems appear in Appendix B.

To boot from the standard distribution diskette, set your terminal as follows:

| Baud Rate: | 9600 |

|------------|------|

| Data Bits: | 8    |

| Parity:    | off  |

| Stop Bits: | 1    |

If your terminal provides the choice, set it so that the data bit 8 is transmitted as a 0 ("low" or "space"). Some terminals do not provide such an option, automatically sending a zero for data bit #8 when parity is off. The AMPRO BIOS ordinarily masks the MSB when 8 bit transmission is selected, but you may choose to do otherwise. (Requires BIOS source code, available from AMPRO). Connect the terminal to Serial Port A. If a modem is being connected, use Serial Port B. First time booting of the system requires that you connect a serial terminal capable of meeting the above specifications. As will be explained in Chapter 3, system boot parameters can be customized, but initially the system comes up with Serial Port A set for 9600 baud.

With a terminal connected and turned on, the system is ready to boot. When power is applied, a program in the EPROM will attempt to read the operating system from disk. If no disk is in the drive, the system will wait until a disk is in place, and drive latch closed. The system will then read the CP/M operating system from the disk in drive A.

#### IMPORTANT

See note in Table 2-1 concerning floppy drive requirements for booting the distribution system diskette.

If the drive's LED lights but nothing else happens, try inserting the flipside of the disk and pressing RESET. If this doesn't help, refer to the next section for troubleshooting information.

# **2.5 TROUBLESHOOTING**

It is possible that the completed system does not work the first time. If you have to troubleshoot it, here are some suggestions:

- Recheck all wiring, soldered connections.

- Check that power is available from the power supply.

- Be certain that the drives are working, and are jumpered correctly. NOTE: IBM PC drives are not jumpered in a "standard" manner; the drive cable has swapped drive select wires. For use with Little Board/PLUS, be sure drive A is jumpered as Drive Select 0, B as 1, etc.

- If both drive indicators light during power-up, with drive handles closed (across slot), the drive signal cable is probably reversed on the board's floppy interface connector (J6). Switch the computer OFF and reverse the drive cable connector at the Little Board/PLUS.

- Check the drive termination resistor pack(s) for proper location. Normally, this will be located at the drive connected at the end of the drive cable.

- If you have the debugging Monitor EPROM option, you can verify some of the system functions using the debugger and other tools in the Monitor.

In the event that your system still does not boot after following all of these instructions, contact AMPRO customer service for assistance.

#### CHAPTER 3

#### USING THE SYSTEM

#### **3.1 INTRODUCTION**

Assuming you have successfully booted CP/M as described in Chapter 2, you will probably want to take advantage of the flexibility designed into the Little Board/PLUS CP/M BIOS and utilities to customize your system diskette.

This chapter explains how to install your operating system software for various system configurations, making use of standard CP/M and ZCPR3 utilities and the Little Board/PLUS utilities software supplied on the system software diskette.

### 3.1.1 Software References

Only brief references are made in this manual to the use and operation of the required software utilities. Whenever a software utility is mentioned, it will either be called an AMPRO utility, a CP/M utility, or a ZCPR3 utility. This way you will know where to obtain further information on the program's use.

Full descriptions and operating instructions for the AMPRO software utilities are found in the AMPRO Z80 System Software User's Manual, AMPRO part number A74006.

Some recommended CP/M and ZCPR3 references are:

CP/M Primer, by Stephen M. Murtha and Mitchell Waite (Howard W. Sams)

CP/M Handbook, by Rodnay Zaks (Sybex Inc.)

CP/M Revealed, by Jack D. Dennon (Haydon Publishing)

ZCPR3: The Manual, by R. L. Conn (Echelon Inc. - Phone: 415/948-3820)

# 3.1.2 Conventions

In the descriptions of the use of software utilities, terminal keyboard inputs which you will make to the system are shown underlined. This has been done to make it easy for you to distinguish between the computer's prompts and the operator's keystrokes. For example:

A0>DIR <RETURN>

Also, certain keys on your terminal's keyboard have special uses. The control key, generally labeled CTRL, is meant to be pressed at the same time as one other key. The required control key combination will be represented as follows:  $\langle CTRL-C \rangle = control key pressed along with C key.$

Two other special keys are the "escape" key, indicated by  $\langle ESC \rangle$  and the "return" key (also called the "carriage return" or "enter" key), indicated by  $\langle RETURN \rangle$ . In general, all commands you enter from the CP/M (or ZCPR3) command prompt require you to press  $\langle RETURN \rangle$  key to begin the operation, as in the example above.

# 3.2 FIRST TIME USE

Chapter 2 discussed connecting the completed system to terminal, a modem, and initial power-up. Assuming the computer works, there are two things it is recommended that you do immediately:

- 1. Make a backup copy of the disks included with the Little Board/PLUS.

- 2. Customize your system diskette.

# 3.2.1 Making Backup Disks

It is always a good idea to have at least one backup copy of all floppy disks. This is especially true of your master system disks. The exact procedure you use to make backup disks depends on your system configuration. Here are three methods:

# Method 1: Two identical format types.

When making a backup in which the source and destination disks will be the same floppy format (i.e., 48 to 48 tpi, or 96 to 96 tpi), the backup can easily be made with the Copy function of the AMPRO AMPRODSK utility. The only catch is that AMPRODSK requires the source and destination to be the same floppy format and drive type. One exception is that double-sided drives can be used to copy from or to single-sided floppy formats. The AMPRODSK Copy function even formats the destination disk for you. Simply follow the instructions given by the program when you run it.

#### NOTE

AMPRODSK can not read 48 tpi disks in 96 tpi drives. Use Method 2.

#### Method 2: Two different drive types.

You can backup a source disk onto a different floppy format (e.g. 96 tpi backup of 48 tpi disk or visa versa), as follows:

- 1. Use the AMPRODSK utility's Format function to format a fresh disk having the desired destination format, in the destination drive.

- 2. Use a file copy utility (CP/M PIP, ZCPR3 DISK7, ZCPR3 MCOPY, AMPRO FRIENDLY, etc.) to copy all files from the source to the destination disk.

3. If the source disk is a system disk, use the AMPRO SYSGEN utility to copy the source system tracks to the destination system tracks.

# Method 3: Single-drive Systems.

If you have a system with only one disk drive, you can do nearly anything that can be done with two or more drives. For example, a backup of your system software diskette can be made as follows:

- 1. Use the AMPRO AMPRODSK utility's Format function to format a blank disk. The program will indicate what you need to do.

- 2. Use the AMPRO SWAPCOPY utility to copy all files from the source disk system disk to the backup disk. The required command is:

# A0>SWAPCOPY \*.\* <RETURN>

3. Use the AMPRO SYSGEN utility to copy the system tracks from the source disk to the backup disk. The program will indicate what to do.

#### 3.2.2 Customizing Your System Disk

When using your system for the first time, some of the system initial default values are probably not perfect for your system configuration. The AMPRO CONFIG utility allows you to easily modify the serial port setups (baud rates, handshaking, etc.), printer port assignment (serial or parallel), floppy drive step rates, and automatic powerup/reset command.

#### NOTE

Any modifications to the system parameters should only be performed using your backup disks. **Do not** use the disks shipped with your Little Board/PLUS.

One important parameter to be sure to set correctly is the floppy disk drive step rate. Initially, the system disk is set up for, and boots with, a step rate of 6 mS. Check your drive's step rate specification, and set the default step rate to the one that is closest to the drive's specification. The CONFIG utility will guide you through its use.

You will also want to customize the terminal characteristics definition file, MYTERM.Z3T, so that it matches your terminal. This is done with the ZCPR3 TCSELECT or TCMAKE utilities. The menu which displays when you boot your system will look better, and write to the screen faster, once you have created a MYTERM.Z3T file for your terminal.

# 3.3 OPERATING SYSTEM FEATURES

The operating system included with the Little Board/PLUS is an enhanced version of standard CP/M version 2.2. One major difference is that the user command line interface (Console Command Processor, CCP) is replaced by an enhanced Z80 Command Processor Replacement called ZCPR3. The Little Board/PLUS operating system consists of three portions:

CP/M 2.2 BDOS:Standard CP/M file and device management facilityAMPRO Custom BIOS:Enhanced Basic I/O SystemZCPR3 CCP:Z80 Command Processor Replacement version 3

# 3.3.1 CP/M 2.2 BDOS

The heart of the Little Board/PLUS operating system is the Basic Disk Operating System (BDOS), which is the normal CP/M 2.2 BDOS. This is the part of the operating system that interacts with programs. Because this is completely standard CP/M 2.2, all software programs designed to work with CP/M 2.2 will run without modification, provided they do not contain hardware-dependant routines.

# 3.3.2 AMPRO Custom BIOS

The CP/M Basic I/O System (BIOS) takes care of all hardware-dependant operating system functions. Many features of the Little Board/PLUS CP/M operating system are the result of a highly flexible, sophisticated BIOS implementation. Here are a few:

Automatic Format Sensing - Single- and double-sided, 40- and 80- track disks and drives may be intermixed freely. The BIOS senses what format is present, and adjusts accordingly. 40-track (48 tpi) diskettes may even be read (but not written) in 80-track (96 tpi) drives. NOTE: CP/M requires that you use a <CTRL-C> keystroke when you change diskettes.

Alien Format Support - One disk drive can be assigned as an "emulating" drive, so that you can read from or write to your choice of non-AMPRO format.

**Hard Disk Support** (Optional) - You can add one or more hard disk controllers and drives to your system. The BIOS contains generic SCSI (SASI) support, making it compatible with a wide variety of devices, and has been structured to maximize the flexibility of this function.

**Power-up Port Defaults** - You can easily alter the system power-up I/O port defaults (console baud rate, printer port assignment and setup, etc.) using the AMPRO configuration utility.

**Power-up Auto-Command** - A single command can be specified to run automatically on system power-up or reset. This is one of the options available through the AMPRO configuration utility. **IOBYTE Implementation** - The IOBYTE can be changed by the CP/M STAT utility, to reassign logical I/O devices to physical I/O devices. Table 3-1 lists the standard CP/M logical-to-physical device assignments and choices, as supported in the Little Board/PLUS BIOS.

| Logical Device                                                                         | Physical Device Choices                                               | Default                      |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------|

| CON:<br>RDR:<br>PUN:<br>LST:                                                           | CRT: or TTY:<br>TTY: (input)<br>TTY: (output)<br>CRT: or TTY: or LPT: | CRT:<br>TTY:<br>TTY:<br>LPT: |

| Where:<br>CRT: = Serial Port A<br>TTY: = Serial Port B<br>LPT: = Parallel Printer Port |                                                                       |                              |

Table 3-1. Logical-to-Physical I/O Assignments

As implemented, the IOBYTE allows two choices for console port (Serial Port A or Serial Port B), and two choices for printer port (Serial Port A, Serial Port B, or Parallel Printer Port).

In addition, the AMPRO CONFIG utility program allows you to set the IOBYTE either temporarily, or in the cold-boot defaults on the system tracks of a disk.

## 3.3.3 ZCPR3 Command Processor

The normal CP/M console command processor (CCP) has been replaced with the more powerful Z80 Command Processor Replacement, version 3 (ZCPR3). As indicated in Table 3-2, the ZCPR3 implementation differs slightly from standard CP/M, but can be used in the much same way you would use standard CP/M. If you wish to eliminate the ZCPR3 enhancement, you can do so through the use of the AMPRO MOVCPM utility. (Refer to the AMPRO Z80 System Software User's Manual for information on how to do this.)

Your system software includes only part of the full power of the ZCPR3 System; the full ZCPR3 System occupies several megabytes of disk! The following paragraphs cover the ZCPR3 features that are present in the standard Little Board/PLUS operating system software. Additional ZCPR3 options can be easily added, as discussed in the AMPRO Z80 System Software User's Manual. Contact Echelon Inc. (Phone: 415/948-3820) for additional ZCPR3 information and support. ZCPR3 utilities and information are also available at no charge through many CP/M and ZCPR3 user groups and bulletin board systems (see Appendix C).

| Function                                                                                   | ZCPR3 Command                                                                                    | CCP Command                     |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------|

| Display all files<br>Display files in specific DU                                          | DIR<br>DIR DU:                                                                                   | DIR<br>No equivalent            |

| Erase specified file<br>Erase with verify                                                  | ERA DU:afn<br>ERA DU:afn V                                                                       | ERA D:afn<br>No equivalent      |

| Rename file<br>Rename file over existing file                                              | REN DU:ufn=ufn2<br>REN DU:ufn=ufn2                                                               | REN D:ufn=ufn2<br>No equivalent |

| Print file on console<br>Without paging                                                    | TYPE DU:ufn P                                                                                    | TYPE D:ufn                      |

| Print file on console<br>With paging                                                       | TYPE DU:ufn                                                                                      | No equivalent                   |

| Save memory into file<br>Save memory into file<br>and specify size in hex                  | SAVE n DU:ufn<br>SAVE nH DU:ufn                                                                  | SAVE n D:ufn<br>No equivalent   |

| Save memory into file<br>and specify number of<br>blocks                                   | SAVE n DU:ufn S<br>or<br>SAVE nH DU:ufn S                                                        | No equivalent                   |

| Change disk<br>Change user<br>Change disk and user                                         | D:<br>U:<br>DU:                                                                                  | D:<br>USER n<br>No equivalent   |

| at same time                                                                               |                                                                                                  |                                 |

| DU: - Drive number,User number<br>ufn - Unambiguous file name<br>afn - Ambiguous file name | (e.g., A0:, B15:, C:, 13:)<br>(e.g., MYFILE.TXT, DIR.COM)<br>(e.g., *.COM, MYFILE.*, M??ILE.T?T) |                                 |

# Table 3-2. ZCPR3/CCP Command Comparison

#### **Sub-Directories**

Each floppy disk has a directory of files; each directory can contain up to 16 sub-directories (also called user areas), numbered 0 through 15. Normal CP/M uses the USER command to change between the 16 possible sub-directories, with the default being 0. ZCPR3 uses a directory label formed from the combination of the drive letter (A, B, etc.) and user area (0,1, etc.). This is called a drive-user, or "DU" expression. For example, A0 represents drive A user area 0, while B15 corresponds to drive B user area 15.

Using ZCPR3, the current drive and user area are displayed in the command prompt. Instead of using CP/M's USER command to change user areas, you do it in the same way that you change drives. In addition, whenever you use the DU expression, you may omit either the letter or number portion, if that part of the expression is the same as the current one. For example: A0>B15:<RETURN> B15>0:<RETURN> B0:A:<RETURN> A0>

In addition, functions such as directory (DIR), erase (ERA), rename (REN), etc., allow the DU form as destination and source directory designations.

Another powerful feature of ZCPR3 is the option of "named" sub-directories. When the named directory option is present, a directory name can be substituted for the DU expression in all command line inputs. This feature is not present in the AMPRO system software as shipped, but can be easily added. Please refer to the above-mentioned software references for further information.

#### Directory Utility

In AMPRO's ZCPR3 implementation, the DIR utility is not an "intrinsic" (internal) function, but requires the presence of the ZCPR3 DIR.COM utility on disk. As you will notice as soon as you use this command, the DIR utility has quite a few nice features, such as alphabetical file sorting and direct access to any directory. For example

A0>DIR B5:<RETURN>

displays the directory of drive B, user area 5 (sorted alphabetically!).

Also, since the directory utility is disk-based rather than internal, you can select from a large assortment of public domain directory utilities -- simply rename your favorite one "DIR.COM".

#### Multiple Commands per Line

With ZCPR3, multiple commands may be given on a single command line, with semi-colons (;) used as separators. For example, the sequence

#### A0>DIR;ERA \*.BAK;DIR<RETURN>

runs the directory program, erases all files with the .BAK type, and then runs the directory program a second time.

# Command Search Path

ZCPR3 also uses an automatic command search path. This means that programs referenced on the command line may be located anywhere along a pre-defined command search path. You can be logged onto drive B, and execute a program on drive A, without typing the drive prefix for the program drive. The default search path is: current drive, current user current drive, user 0 drive A, current user drive A, user 0 drive A, user 15 current drive, user 15

Since the search path covers both different drive letters and different user area numbers, you can "hide" programs and utilities in different user areas. This results in cleaner looking directories. A common practice is to "hide" COM files (programs) in user 15. Such files will not be visible from user 0, but will execute from user 0.

### NOTE

Some application programs must be run from the same drive letter and user area as the files they will be used with, or require additional programs, overlays, or files to be present in the same directory (drive and user area) as the program itself.

The ZCPR3 DISK7 and MCOPY, and the AMPRO FRIENDLY utilities can be used to copy files directly between user areas. The ZCPR3 PATH utility allows you to easily change the search path as needed.

#### **Intrinsic Commands**

With the exception of the DIR and USER commands noted above, all standard CP/M version 2.2 intrinsic commands are implemented, as well as some additions. Table 3-2 lists the ZCPR3 commands versus those of the standard CP/M CCP.

#### Aliases

One of the most powerful features of ZCPR3 is the use of aliases. This feature is made possible by the multiple command line capability. An "alias" is a disk-resident multiple command line. The alias has a command file name, such as FUNCTION.COM, but represents a pre-programmed set of commands. Whenever you run the alias, you get the set of commands. It is like a fast, memory-based submit, or batch, facility. By using an alias (usually STARTUP.COM) as the CONFIG auto-command, you can have a complex sequence of functions automatically initialize your system on power-up or reset.

#### Shells

ZCPR3 also provides shell support. A "shell" is a substitute operating environment. Examples of ZCPR3-compatible shells are ZCPR3 MENU, VMENU, and VFILER, and AMPRO FRIENDLY. A shell is a program that always reloads following the execution of any program, rather than returning you to the command prompt. Once a shell is loaded, you might never see the A0> prompt again! ZCPR3 shells provide varying levels of isolation of the user from the operating system, and can even completely replace the CCP interface. The powerful MENU shell program is included on your system diskette.

# Termcap Facility

ZCPR3 adds another powerful feature to CP/M which is lacking in most microcomputer operating systems: a termcap facility. The AMPRO CP/M implementation contains a special buffer area in memory which is used by ZCPR3 to standardize terminal display control codes. This allows application programs to be terminal-independent, providing the software is written to take advantage of the ZCPR3 termcap. The ZCPR3 utilities TCSELECT and TCMAKE are used to create a termcap file, usually called MYTERM.Z3T. The ZCPR3 utility LDR is used to load the appropriate termcap file into memory, for use by compatible programs.

# 3.4 AMPRO-SUPPLIED UTILITIES

A powerful set of software programs is sipplied with the Little Board/PLUS. This section contains brief descriptions of each. They include:

- the standard CP/M 2.2 software set

- the AMPRO Little Board/PLUS utilities

- several key ZCPR3 utilities

- several public domain programs

The programs described below are those included on the Little Board/PLUS system software diskette at the time of this writing (hard disk software is optional). Actual contents may vary. Complete descriptions and operating instructions are provided in the publications listed in the introduction to this chapter. Program and program description updates are available from AMPRO on an on-going basis, at nominal charge. Contact AMPRO for information.

# 3.4.1 CP/M Utility Programs

Included with the Little Board/PLUS are all the standard CP/M utility programs:

**ASM.COM** - Standard assembler for 8080 instructions. May be used to assemble Little Board/PLUS source code.

DDT.COM - Dynamic Debugging Tool: standard CP/M debugger.

**DUMP.COM** - Permits display of a file in hexadecimal values.

**ED.COM** - Standard CP/M line editor. May be used to edit Little Board/PLUS source code.

**LOAD.COM -** Converts .HEX file output of the ASM program to an executable .COM file.

**PIP.COM** - Permits single or multiple disk-to-disk file transfers. Also port-to-port and port-to/from-disk transfers.

**STAT.COM** - Status of disk and other I/O devices. Also may be used to set file attributes.

**SUBMIT.COM** - Permits execution of multiple commands and parameters stored in a disk file.

**XSUB.COM** - For use with SUBMIT.COM, to allow passing of parameters direct to programs.

# 3.4.2 AMPRO Utilities

The following programs are specific to Little Board/PLUS, and used for system customization, disk formatting, disk format translation, etc. Source code is available from AMPRO at nominal cost. The hard disk utilities are available in the optional Z80 Hard Disk Software package.

AMPRODSK.COM - Used to copy, format, and verify AMPRO-format disks.

**CONFIG.COM** - Used to modify or set your system's current or powerup default peripheral port characteristics according to your particular requirements. Lets you set serial port A and B baud rates, data characteristics, and handshaking, floppy drive step rates, printer port choice (serial or parallel), and command for power-up or reset automatic execution.

**DOS.COM** - Used to read and write files on MS-DOS format disks. Also used to read the directory and erase files.

DOSFMT.COM - Used to format MS-DOS disks in all standard formats.

**ESET.COM** - Permits reading and writing of data to and from disk formats other than those available with the MULTIDSK.COM utility. (See MULTIDSK.COM)

**HFORMAT.COM** (optional) - Hard disk formatting program.

HINIT.COM (optional) - Hard disk controller and system initialization utility.

**HPARK.COM** (optional) - Hard disk drive head parking utility. Moves the head to an unused area of the disk drive's surface prior to system shut down, to prevent data loss from head crash.

**MOVCPM.COM** - Configures the operating system for a user-definable memory size. Same as ZMOVCPM.COM, except contains the standard CP/M CCP. Used as part of the procedure for generating a hard disk system, if ZCPR3 is not desired.

**MULTIDSK.COM** - Provides compatibility with other computers' disk formats. After MULTIDSK is run, you can read from or write to the selected alien format by using the drive letter "E" instead of the drive's normal designation (A, B, etc.). **MULTIFMT.COM** - Permits formating (and verifying) disks using non-AMPRO formats.

**SET.COM** - Allows setting of current serial port characteristics (baud rate, data characteristics, hand shaking) and assignment of printer port (serial or parallel). Similar to CONFIG.COM, but all parameters are given from the command line, thus allowing use with ALIASes, MENU lines, etc.

SWAP.COM - Re-assigns CP/M disk drive letters, swapping them in pairs.

**SYSGEN.COM** - Used to write the AMPRO CP/M operating system tracks onto a disk. Allows source of the system tracks to be either another disk's system tracks, a disk file, or a memory image (generally placed in memory by MOVCPM or ZMOVCPM).

**ZMOVCPM.COM** - Configures the operating system for a user-definable memory size. Same as MOVCPM.COM, except contains the standard ZCPR3 CCP replacement. Used as part of the procedure for generating a hard disk system.

# 3.4.3 ZCPR3 Utilities

The following ZCPR3 utilities are included on the Little Board/PLUS system disk. Source code is available from ECHELON Inc. (415/948-3820) at nominal cost.

ALIAS.COM - Used to create or modify multiple command line files (aliases).

**DIR.COM** - Displays contents of disk directories. Allows direct drive/user area (DU) access.

DIFF.COM - File compare utility. Checks two files for differences.

**DISK7.COM** - Easy to use disk file management utility. Includes a menu of single-keystroke commands for Copy, Rename, Delete, Length, and drive Status.

**LDR.COM** - Used to load terminal definition files (e.g. MYTERM.Z3T), system environments, and other system-resident ZCPR3 files.

**MCOPY.COM** - General purpose file copying program. Allows direct file movement between directories (e.g. A0 to B15).

MENU.COM - Powerful system menu shell program.

**PATH.COM** - Modifies command search path.

**TCMAKE.COM** - Used to create non-standard terminal definition files (e.g. MYTERM.Z3T).

**TCSELECT.COM** - Used to select a standard terminal definition file from a menu of standard terminals.

UNERA.COM - Recovers deleted disk files. Inverse of the ERA (erase) command.

**WHEEL.COM** - Sets user privileges. (Required to use PATH.COM to change command search paths.)

**Z3INS.COM** - ZCPR3 installation utility. Installs other ZCPR3 utilities for your operating system configuration. AMPRO-suplied ZCPR3 utilities do not require installation prior to use with the standard AMPRO-supplied operating system.

**ZEX.COM** - Memory-resident submit facility, similar to CP/M's SUBMIT utility, but more powerful.

#### 3.4.4 Public Domain Programs

Several valuable public domain programs have also been included. Source code for these programs is available through CP/M user groups and bulletin board systems (see Appendix C).

**FINDBAD.COM** - Bad sector lockout program for use in mapping out hard disk drive surface defects. Creates a file [UNUSED].BAD containing all bad sectors.

**MDM740.COM** - General purpose, powerful communication program. Modified for use with the Little Board/PLUS serial port B. (AMPRO-specific overlay is contained in the file, M&-LB.ASM.) Allows direct computer-to-computer file transfer over Rs232, or may be used with a modem. Fearures include ASCII transfer or XMODEM protocol, auto dialing, stored phone library, and more.

**SD.COM** - Directory display utility alternative to DIR.COM. Options you may specify in the command line allow printing the directory, creating a file containing the directory, and inclusion of multiple user areas.

**SWAPCOPY.COM** - Single drive disk-to-disk copy utility. Modified for use with AMPRO foreign formats (allows copying from A to A, A to E, and E to A).

# 3.5 GENERATING DIFFERENT SYSTEMS

There are several reasons why you may wish to generate an alternate operating system:

- 1. Use of hard disk drives

- 2. Alternate ZCPR3 system configurations

- 3. Memory requirements of a modified BIOS or custom software

- 4. Substitution of standard CP/M CCP for ZCPR3 CCP

- 5. Generation of a larger TPA system, using the Version 1 BIOS

In the first three cases, additional buffer areas are required in high memory, above the operating system. This requires moving the operating system **down** in memory, and leaving room for the required functions. In the fourth case, the use of CP/M results in less memory required for the operating system, allowing the operating system bo be moved up in memory. In the fifth case, sligntly more program area is made available by using a BIOS with a few less features.

The AMPRO utilities MOVCPM.COM or ZMOVCPM.COM are used to relocate or regenerate the operating system. Refer to the AMPRO Z80 System Software User's Manual for additional information on the generation of alternate CP/M configurations.

#### **CHAPTER 4**

#### THEORY OF OPERATION

#### 4.1 INTRODUCTION

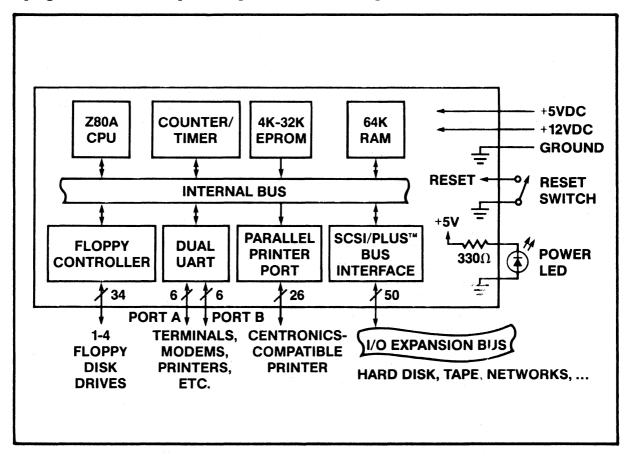

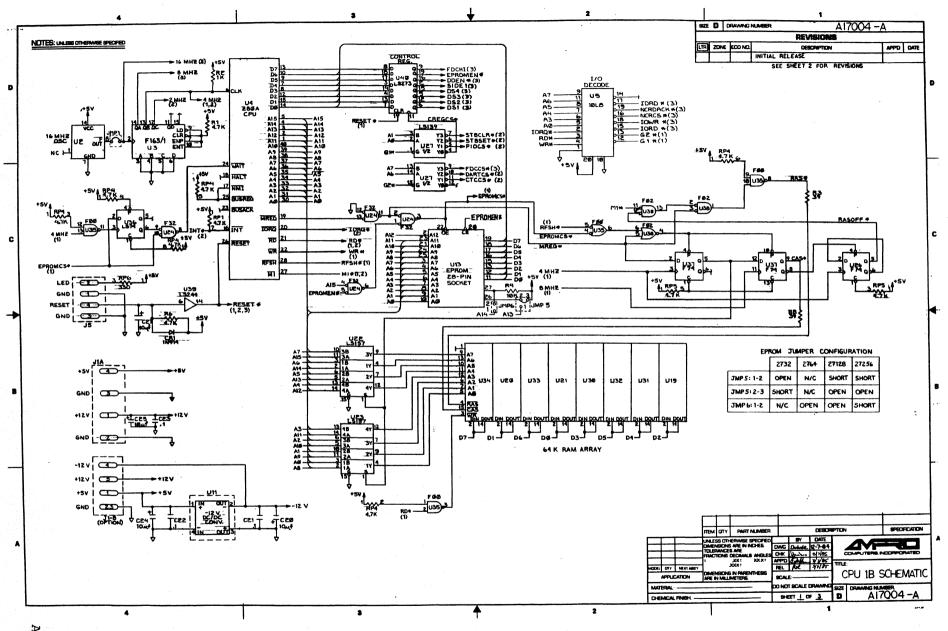

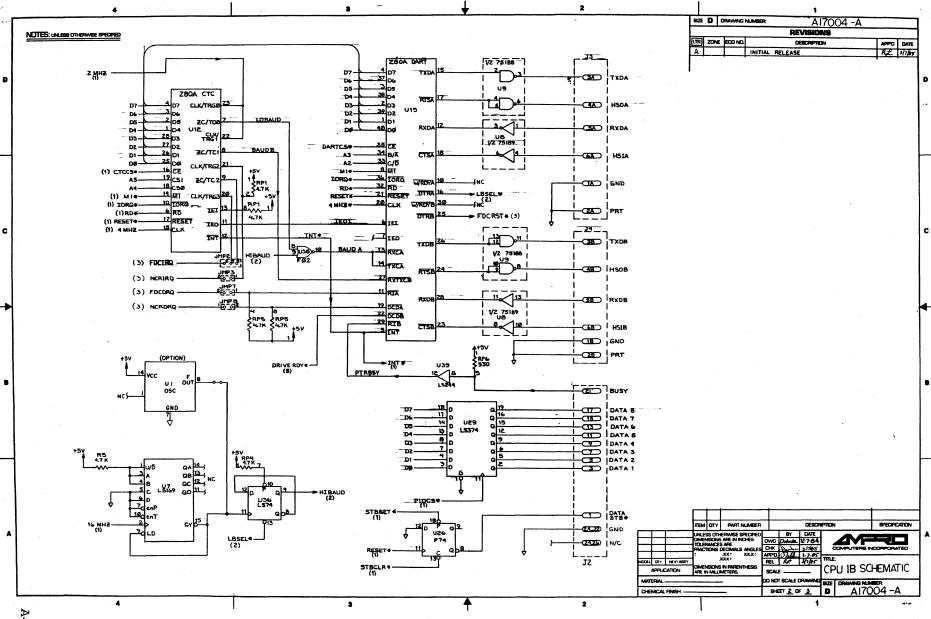

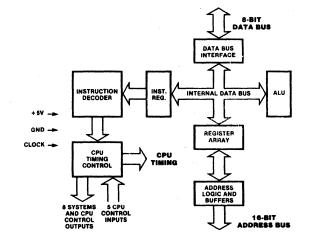

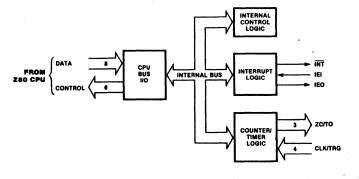

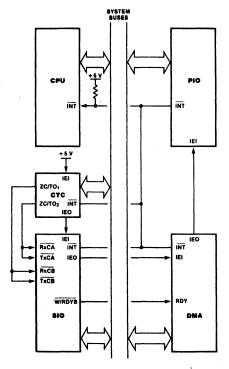

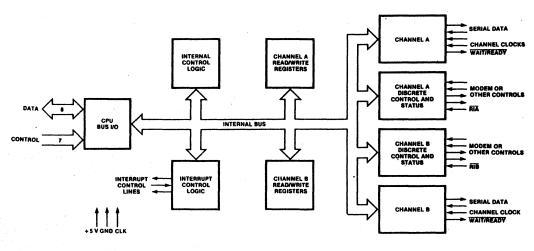

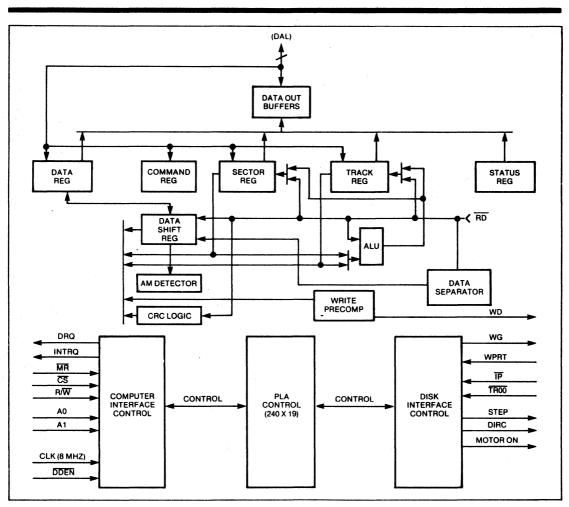

This chapter provides detailed information on the functional operation of Little Board/PLUS. No information on the internal operation of the LSI components is included. Please refer to the manufacturers' data sheets (Appendix D) for specific details. Figure 4-1 is a block diagram of Little Board/PLUS. Chapter 5 contains programming information, and indicates the assignment of programmable device pins to specific hardware signals and functions.

Figure 4-1. Little Board/PLUS Block Diagram

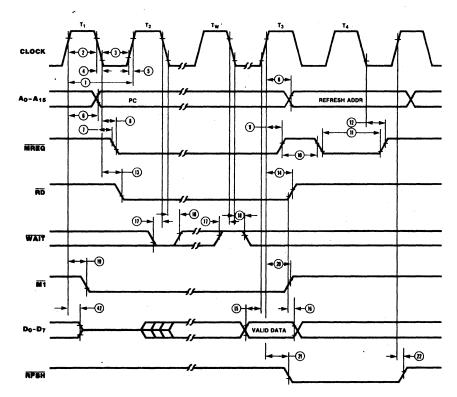

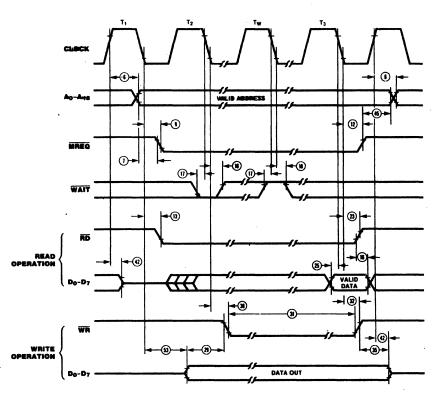

# 4.2 CPU, MEMORY, AND TIMING

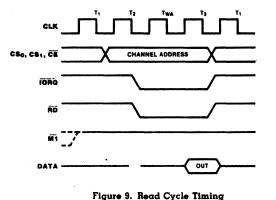

The main system time base is provided by a 16 MHz oscillator module. A binary counter provides three system clocks: 8 MHz, 4 MHz, and 2 MHz. The 4 MHz signal is used by the Z80A, Counter Timer Circuit (CTC), and Dual Asynchronous Receiver/Transmitter (DART) devices. The 8 MHz signal provides the normal clock input to the 1772 Floppy Disk Controller (FDC).

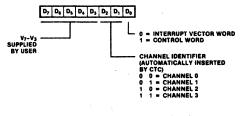

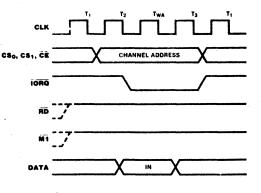

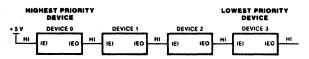

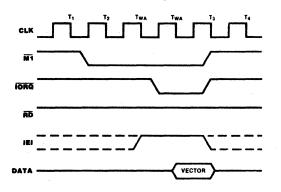

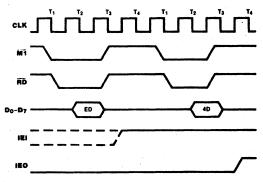

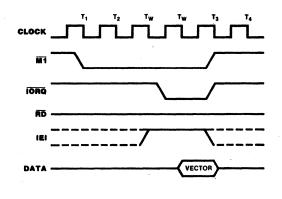

The Z80A interrupt "daisy chain" is implemented in accordance with the standard Zilog protocol, using the peripheral devices' Interrupt Enable Input and Interrupt Enable Output signals. Several of the CTC and DART input lines have jumper options which allow those devices to optionally function as interrupt controllers for a number of floppy and SCSI interface signals. (See the jumpering information in Chapter 2.)

All control signals for the 64K dynamic RAM are derived from the system's 4 and 8 MHz clocks and the Z80A refresh output signal. RAM devices with access times up to 200 nS can be used. The Z80A generates the required 7-bit refresh addresses and timing required by the 64K by 1 bit dynamic RAM devices.

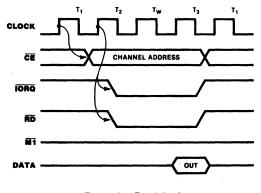

When a memory read or write occurs with address line A15 set to zero, and bit 6 of the Board Control Register is set to zero, memory address decoding logic selects the EPROM rather than RAM. In addition, a wait state generator becomes active whenever the EPROM is selected, permitting the use of EPROM device access times up to 450 nS.

A programmable array logic (PAL) device and a pair of two-to-four decoders generate the device select addresses for all of the Little Board's I/O devices. Table 4-1 shows the device select addresses in binary. Where X's are indicated in the table entries, the corresponding address bit may be a 1 or a 0. I/O address groups indicated as "unused" are available for I/O expansion via the Z80A CPU socket. There are 40 unused I/O addresses. A summary of the I/O ports, addresses and functions, are shown in Table 4-2.

| Device Select              | I/O Address (Binary) |

|----------------------------|----------------------|

| Device Select              | 1/0 Address (Binary) |

| Board Control Register     | 0000 0X00            |

| Parallel Port Data Latch   | 0000 0X01            |

| Parallel Port Strobe Set   | 0000 0X10            |

| Parallel Port Strobe Clear | 0000 0X11            |

| (Unused)                   | 0000 1XXX            |

| (Unused)                   | 0001 XXXX            |

| 5380 Chep Select           | 0010 0XXX            |

| 5380 DMA Acknowledge       | 0010 1XX0            |

| ID Input Port              | 0010 1XX1            |

| (Unused)                   | 0011 XXXX            |

| CTC                        | 01XX XXXX            |

| DART                       | 10XX XXXX            |

| FDC                        | 11XX XXXX            |

Table 4-1.

I/O

Device

Addresses

| Address | Input/Output | Function                           |  |

|---------|--------------|------------------------------------|--|

| 00h     | Output       | Board Control Register             |  |

| 01h     | Output       | Parallel Printer Data Register     |  |

| 02h     | Output       | Parallel Printer Data Strobe Set   |  |

| 03h     | Output       | Parallel Printer Data Strobe Clear |  |

| 20-27h  | I/0          | SCSIControllerInternal Registers   |  |

| 28h     | I/O          | SCSI Controller "DMA" Read/Write   |  |

| 29h     | Input        | ID Input Port                      |  |

| 40h     | I/0          | CTC Channel 0                      |  |

| 50h     | I/O          | CTC Channel 1                      |  |

| 60h     | I/O          | CTC Channel 2                      |  |

| 70h     | I/O          | CTC Channel 3                      |  |

| 80h     | I/O          | DART Channel A Data                |  |

| 84h     | I/O          | DART Channel A Control             |  |

| 88h     | I/O          | DART Channel B Data                |  |

| 8Ch     | I/O          | DART Channel B Control             |  |

| C0h     | Output       | FDC Command Register               |  |

| C1h     | Output       | FDC Track Register                 |  |

| C2h     | Output       | FDC Sector Register                |  |

| C3h     | Output       | FDC Data Register                  |  |

| C4h     | Input        | FDC Status Register                |  |

| C5h     | Input        | FDC Track Register                 |  |

| C6h     | Input        | FDC Sector Register                |  |

| C7h     | Input        | FDC Data Register                  |  |

Table 4-2. Summary of I/O Ports

#### NOTE

The I/O device addresses for these ports are not unabiguously decoded. Refer to Table 4-1.

# 4.3 BOARD CONTROL REGISTER

The Board Control Register (BCR) is a simple octal output latch which controls several board functions. Seven of the eight bits of the BCR control are associated with the floppy disk interface: drive selects (4), side select, density select, and 1772 clock select. These are discussed in the section about the floppy disk interface (below). One bit in the BCR also serves to enable or disable the EPROM device. All outputs of the BCR are cleared (to 0) by the board's RESET signal, selecting the EPROM at power-up or when the RESET signal is active.

#### 4.4 SERIAL PORTS

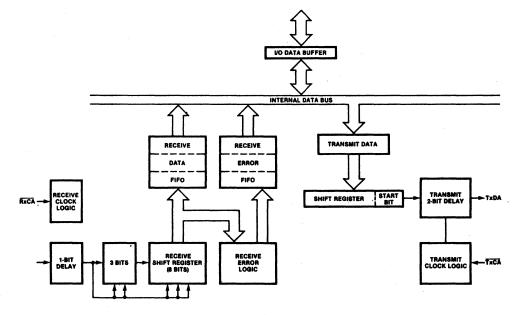

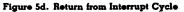

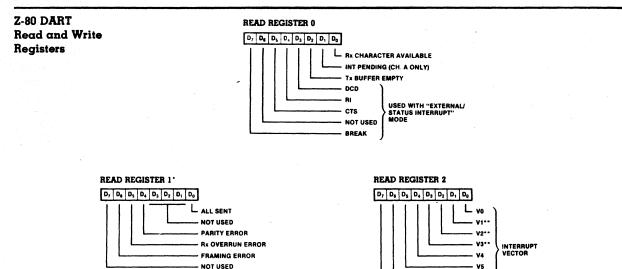

A Z80A dual asynchronous receiver/transmitter (DART) forms the basis of two RS232C serial I/O ports. Baud rates for these ports are generated by the Z80A CTC. Channel A of the DART has an alternate baud rate clock source (614.385kHz), which is obtained by dividing the 16 MHz system clock by 104. This provides serial channel A with two additional baud rates: 19,200 and 38,400 baud, as well as 9600 baud. Baud rate selection is accomplished by programming the CTC time constants, selecting the CTC channel mode (counter or timer), programming the DART prescale factor (16, 32, or 64), and, for serial I/O channel A, selecting either the high or low speed baud rate mode. The high/low baud rate mode of channel A is controlled using the DTRA output of the DART.

DART RTSA and RTSB output signals generate each channel's output handshake signal, while CTSA and CTSB provide the two channels' handshake inputs.

RS232C signal levels are converted to and from TTL levels by a 75188/1488 line driver and 75189/1489 line receiver. An on board -12 volt DC-to-DC converter provides the -12VDC power for the line driver.

Several of the DART's input and output signals are used for purposes not associated with serial communications:

- DCDA and RIA are available as optional interrupt sources

- DCDB is available for reading the optional floppy disk ready signal

- RIB is used to sence the parallel printer Busy signal

# 4.5 PARALLEL PRINTER PORT

An octal D-latch with a 24 mA output current sinking capacity is used to drive the eight parallel printer port data lines. In addition, there are two handshaking signals: Data Strobe (output) and Busy (input).

The Data Strobe output is generated by a flip-flop which is set and reset by software. This permits software controlled timing of data relative to strobe, and strobe polarity. The printer Busy input is sensed by the RIB input of the DART.

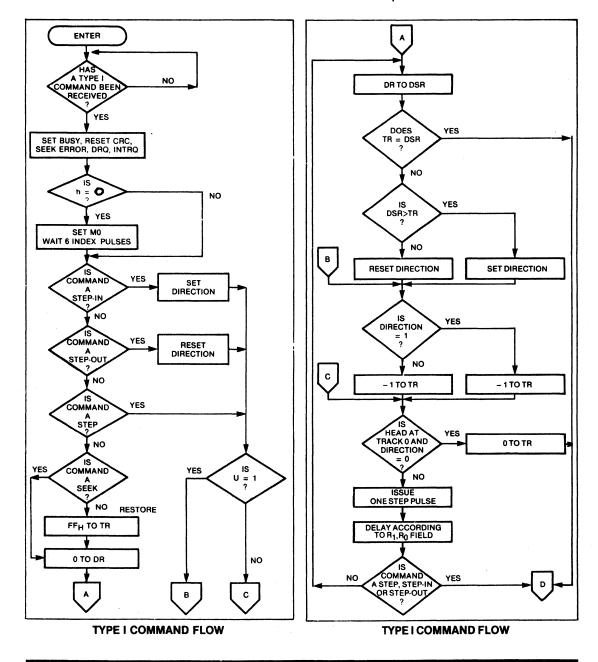

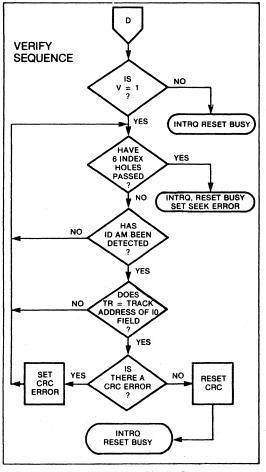

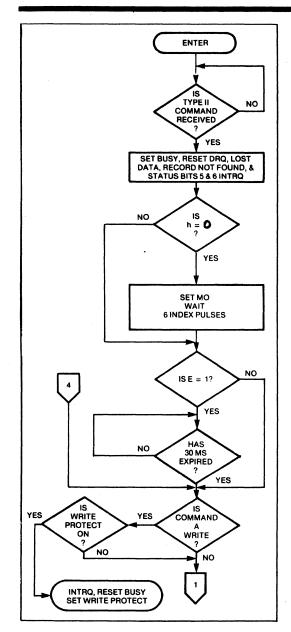

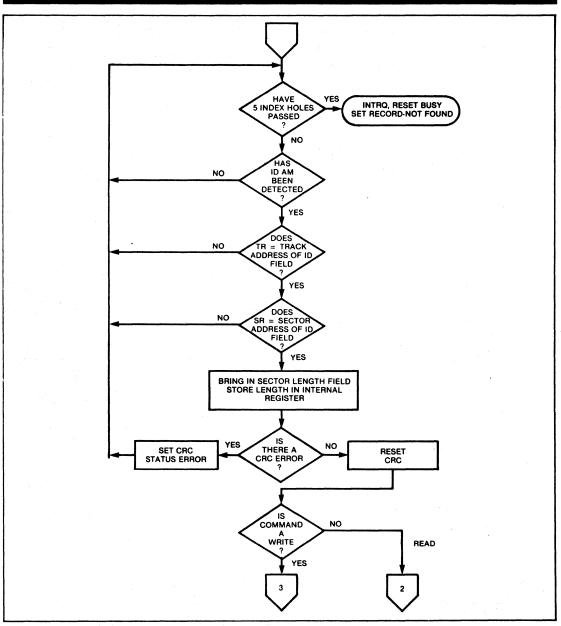

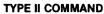

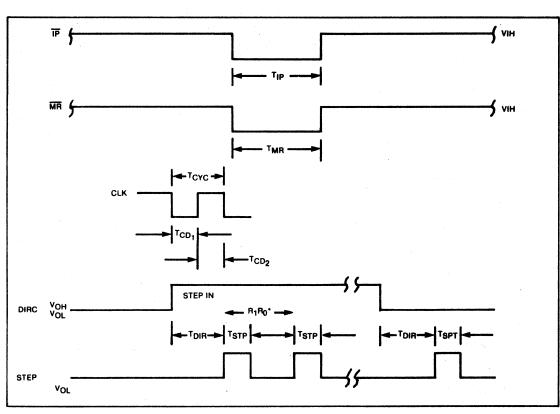

#### 4.6 FLOPPY DISK INTERFACE

Nearly all of the logic required for the floppy disk interface is provided by the Western Digital 1772 Floppy Disk Controller (FDC) device. Only the drive and side-selection and interface input signal buffering require additional devices.

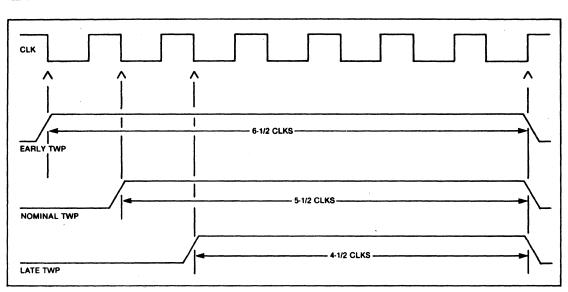

The Board Control Register (BCR) controls the state of the four drive select lines, the side select line, the 1772 density select input, and the 1772 master clock input rate. In principle, by switching the 1772 master clock rate to 16 mHz, single-density eight inch disk drive data rates (250 kbits/sec) are possible. However, the current version of the 1772 is not guaranteed to function properly with a 16 mHz input clock, so the use of this option is not recommended at this time.

The floppy disk interface Ready signal connects to the DART DCDB input signal. This can be optionally used with floppy disk drives which provide this signal. The AMPRO Little Board/PLUS BIOS does not use this option.

# 4.7 SCSI/PLUS INTERFACE

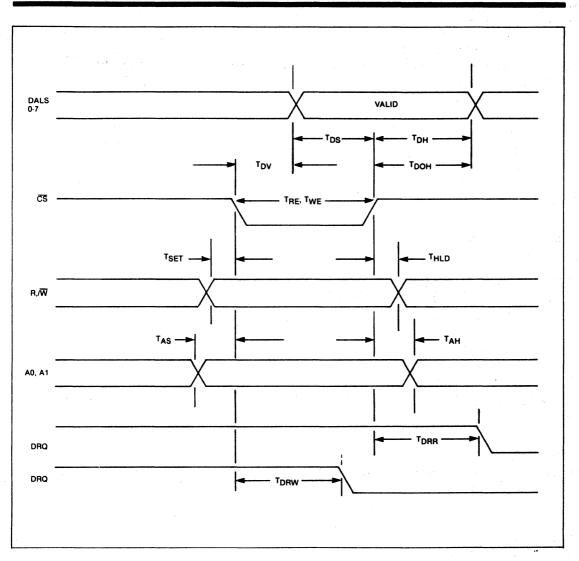

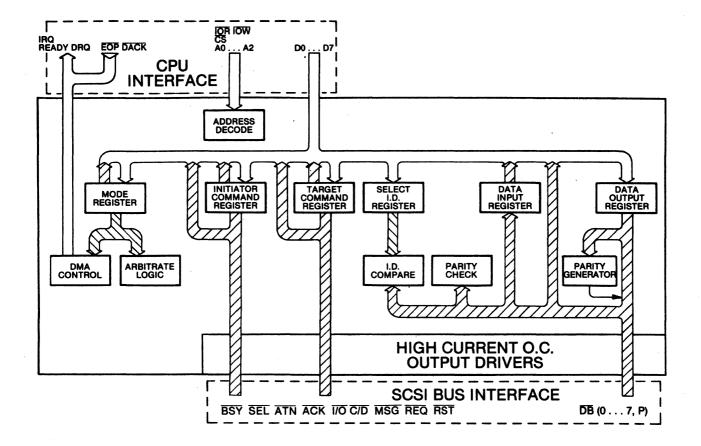

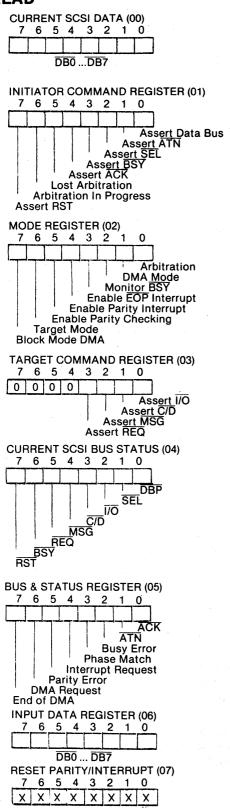

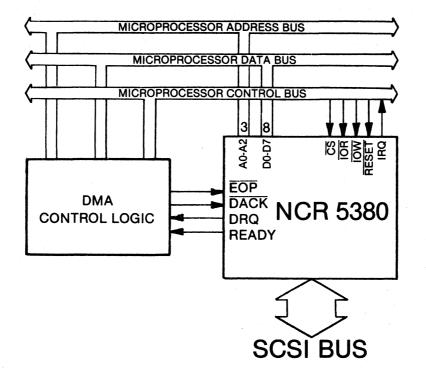

The SCSI/PLUS multi-master bus interface consists of an SCSI bus controller IC (NCR 5380) and an 8-bit jumperable bus ID input port. All of the signals of the SCSI/PLUS expansion bus interface connect directly to pins of the 5380 bus controller IC.

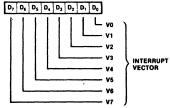

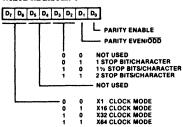

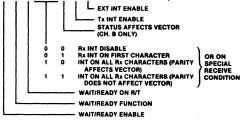

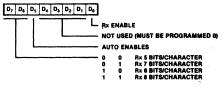

A 74LS244 is used as an ID input port, allowing the state of eight jumpers to be read under software control. Alternatively, this port may be used for general purpose input sensing.