# Product Specification

March 1983

Copyright 1983 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced without the written permission of Zilog, Inc. The information in this publication is subject to change

The information in this publication is subject to change without notice.

# Z8<sup>®</sup> Z8681/82 ROMless Microcomputer

# Zilog

# Product Specification

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | March 1983                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Features               | <ul> <li>Complete microcomputer, 24 I/O lines, and<br/>up to 64K bytes of addressable external<br/>space each for program and data memory.</li> <li>143-byte register file, including 124<br/>general-purpose registers, three I/O port<br/>registers, and 16 status and control<br/>registers.</li> <li>Vectored, priority interrupts for I/O,<br/>counter/timers, and UART.</li> <li>On-chip oscillator that accepts crystal or<br/>external clock drive.</li> </ul>                                                            | <ul> <li>Full-duplex UART and two programmable<br/>8-bit counter/timers, each with a 6-bit pro-<br/>grammable prescaler.</li> <li>Register Pointer so that short, fast instruc-<br/>tions can access any one of the nine<br/>working-register groups.</li> <li>Low-power standby option that retains<br/>contents of general-purpose registers.</li> <li>Single +5 V power supply—all I/O pins<br/>TTL compatible.</li> <li>Available in 8 and 12 MHz versions.</li> </ul> |  |  |  |  |

| General<br>Description | The Z8681and Z8682 are ROMless versions of<br>the Z8 single-chip microcomputer. The Z8682<br>is usually more cost effective. These products<br>differ only slightly and can be used inter-<br>changeably with proper system design to pro-<br>vide maximum flexibility in meeting price and<br>delivery needs. The Z8681/82 offers all the<br>outstanding features of the Z8 family archi-<br>tecture except an on-chip program ROM. Use<br>of external memory rather than a prepro-<br>grammed ROM enables this Z8 microcomputer | to be used in low volume applications or whe<br>code flexibility is required.<br>The Z8681/82 can provide up to 16 output<br>address lines, thus permitting an address<br>space of up to 64K bytes of data or program<br>memory. Eight address outputs ( $AD_0$ - $AD_7$ ) ar<br>provided by a multiplexed, 8-bit, Address/Da<br>bus. The remaining 8 bits can be provided by<br>the software configuration of Port 0 to output<br>address bits $A_8$ - $A_{15}$ .         |  |  |  |  |

|                        | $\begin{array}{c} \textbf{H} \textbf{H} \textbf{H} \textbf{H} \textbf{H} \textbf{H} \textbf{H} H$                                                                                                                                                                                                                                                                                                                                                                                                                                 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

Figure 1. Pin Functions

1

Figure 2. Pin Assignments

**General Description** (Continued) Available address space can be doubled (up to 128K bytes for the Z8681 and 124K bytes for the Z8682) by programming bit 4 of Port 3 (P34) to act as a data memory select output (DM). The two states of DM together with the 16 address outputs can define separate data and memory address spaces of up to 64K/62Kbytes each.

There are 143 bytes of RAM located on-chip and organized as a register file of 124 generalpurpose registers, 16 control and status

Architecture

Z8681/82 architecture is characterized by a flexible I/O scheme, an efficient register and address space structure and a number of ancillary features that are helpful in many applications.

Microcomputer applications demand powerful I/O capabilities. The Z8681/82 fulfills this with 24 pins available for input and output. These lines are grouped into three ports of eight lines each and are configurable under software control to provide timing, status signals, serial or parallel I/O with or without handshake, and an Address bus for interfacing external memory.

Three basic address spaces are available:

registers, and three I/O port registers. This register file can be divided into nine groups of 16 working registers each. Configuring the register file in this manner allows the use of short format instructions; in addition, any of the individual registers may be accessed directly.

The pin functions and the pin assignments of the Z8681/82 40-pin package are illustrated in Figures 1 and 2, respectively.

program memory, data memory and the register file (internal). The 143-byte randomaccess register file is composed of 124 generalpurpose registers, three I/O port registers, and 16 control and status registers.

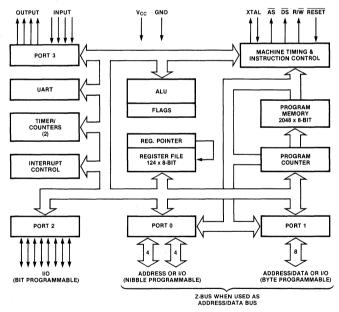

To unburden the program from coping with real-time problems such as serial data communication and counting/timing, an asynchronous receiver/transmitter (UART) and two counter/timers with a large number of userselectable modes are offered on-chip. Hardware support for the UART is minimized because one of the on-chip timers supplies the bit rate. Figure 3 shows the Z8681/82 block diagram.

Figure 3. Functional Block Diagram

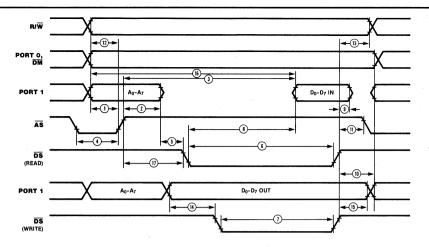

Pin Description **AS.** Address Strobe (output, active Low). Address Strobe is pulsed once at the beginning of each machine cycle. Addresses output via Port 1 for all external program or data memory transfers are valid at the trailing edge of  $\overline{\text{AS}}$ .

**DS.** Data Strobe (output, active Low). Data Strobe is activated once for each external memory transfer.

**P00-P07, P20-P27, P30-P37.** *I/O Port Lines* (input/outputs, TTL-compatible). These 24 lines are divided into three 8-bit I/O ports that can be configured under program control for I/O or external memory interface (Figure 3).

**Pl<sub>0</sub>-Pl<sub>7</sub>.** Address/Data Port (bidirectional). Multiplexed address  $(A_0-A_7)$  and data  $(D_0-D_7)$  lines used to interface with program and data memory. Pin Description (Continued) **RESET.\*** Reset (input, active Low). RESET initializes the Z8681/82. When RESET is deactivated, program execution begins from program location 000C<sub>H</sub> for the Z8681 and 0812<sub>H</sub> for the Z8682.

$\mathbf{R}/\overline{\mathbf{W}}$ . Read/Write (output).  $\mathbf{R}/\overline{\mathbf{W}}$  is Low when

the Z8681/82 is writing to external program or data memory.

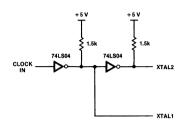

**XTAL1, XTAL2.** Crystal 1, Crystal 2 (time-base input and output). These pins connect a parallel-resonant crystal to the on-chip clock oscillator and buffer.

| Summary of                        | Feature                                                | <b>Z8681</b>                                                       | Z8682                                                                                                       |

|-----------------------------------|--------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Z8681 and<br>Z8682<br>Differences | Address of first instruc-<br>tion executed after Reset | 12                                                                 | 2066                                                                                                        |

| 2                                 | Addressable memory space                               | 0-64K                                                              | 2K-64K                                                                                                      |

|                                   | Address of interrupt<br>vectors                        | 0-11                                                               | 2048-2065                                                                                                   |

|                                   | Reset input high voltage                               | TTL levels*                                                        | 7.35-8.0 V                                                                                                  |

|                                   | Port 0 configuration<br>after Reset                    | Input, float after reset.<br>Can be programmed as<br>Address bits. | Output, configured as Address bits A <sub>8</sub> -A <sub>15</sub> .                                        |

|                                   | External memory timing start-up configurations         | Extended Timing                                                    | Normal Timing                                                                                               |

|                                   | Interrupt vectors                                      | 2 byte vectors point<br>directly to service<br>routines.           | 2 byte vectors in internal<br>ROM point to 3 byte Jump<br>instructions, which point<br>to service routines. |

|                                   | Interrupt response time                                | 26µsec                                                             | 36µsec                                                                                                      |

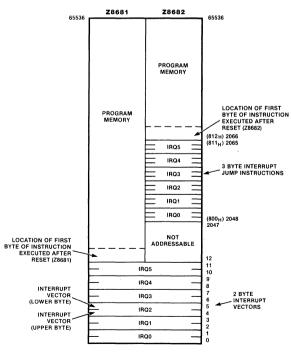

Address Spaces **Program Memory.\*** The Z8681/82 addresses 64K/62K bytes of external program memory space (Figure 4).

For the Z8681, the first 12 bytes of program memory are reserved for the interrupt vectors. These locations contain six 16-bit vectors that

Figure 4. Z8681/82 Program Memory Map

\*This feature differs in the Z8681 and Z8682

Address Spaces (Continued) correspond to the six available interrupts. Program execution begins at location  $000C_{\rm H}$  after a reset.

The Z8682 has six 24-bit interrupt vectors beginning at address  $0800_{\rm H}$ . The vectors consist of Jump Absolute instructions. After a reset, program execution begins at location  $0812_{\rm H}$  for the Z8682.

**Data Memory.\*** The Z8681/82 can address 64K/62K bytes of external data memory. External data memory may be included with or separated from the external program memory space. DM, an optional I/O function that can be programmed to appear on pin P3<sub>4</sub>, is used to distinguish between data and program memory space.

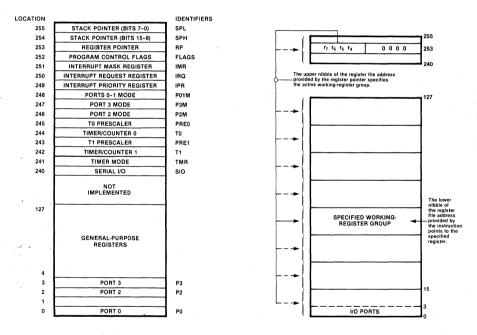

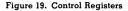

**Register File.** The 143-byte register file includes three I/O port registers (R0, R2, R3), 124 general-purpose registers (R4-R127) and 16 control and status registers (R240-R255). These registers are assigned the address locations shown in Figure 5.

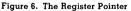

Z8681/82 instructions can access registers directly or indirectly with an 8-bit address field. This also allows short 4-bit register addressing using the Register Pointer (one of the control registers). In the 4-bit mode, the register file is divided into nine workingregister groups, each occupying 16 contiguous locations (Figure 5). The Register Pointer addresses the starting location of the active working-register group (Figure 6).

**Stacks.** Either the internal register file or the external data memory can be used for the stack. A 16-bit Stack Pointer (R254 and R255) is used for the external stack, which can reside anywhere in data memory. An 8-bit Stack Pointer (R255) is used for the internal stack that resides within the 124 general-purpose registers (R4-R127).

Figure 5. The Register File

4

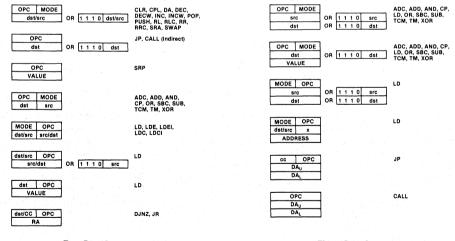

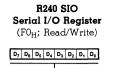

Serial Input/ Output Port 3 lines P3<sub>0</sub> and P3<sub>7</sub> can be programmed as serial I/O lines for full-duplex serial asynchronous receiver/transmitter operation. The bit rate is controlled by Counter/Timer 0, with a maximum rate of 62.5K bits/second at 8 MHz and 93.75K bits/second at 12 MHz.

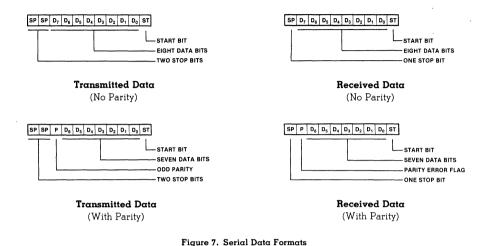

The Z8681/82 automatically adds a start bit and two stop bits to transmitted data (Figure 7). Odd parity is also available as an option. Eight data bits are always transmitted, regardless of parity selection. If parity is enabled, the eighth data bit is used as the odd parity bit. An interrupt request  $(IRQ_4)$  is generated on all transmitted characters.

Received data must have a start bit, eight data bits and at least one stop bit. If parity is on, bit 7 of the received data is replaced by a parity error flag. Received characters generate the IRQ<sub>3</sub> interrupt request.

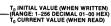

| Counter/<br>Timers | The Z8681/82 contains two 8-bit program-<br>mable counter/timers ( $T_0$ and $T_1$ ), each driven<br>by its own 6-bit programmable prescaler. The<br>$T_1$ prescaler can be driven by internal or ex-<br>ternal clock sources; however, the $T_0$ prescaler<br>is driven by the internal clock only.<br>The 6-bit prescalers can divide the input fre-<br>quency of the clock source by any number<br>from 1 to 64. Each prescaler drives its counter,<br>which decrements the value (1 to 256) that has<br>been loaded into the counter. When the<br>counter reaches the end of count, a timer<br>interrupt request—IRQ <sub>4</sub> ( $T_0$ ) or IRQ <sub>5</sub> ( $T_1$ )—is<br>generated.<br>The counters can be started, stopped,<br>restarted to continue, or restarted from the<br>initial value. The counters can also be pro-<br>grammed to stop upon reaching zero (single- | pass mode) or to automatically reload the initial value and continue counting (modulo-n continuous mode). The counters, but not the prescalers, can be read any time without disturbing their value or count mode. The clock source for $T_1$ is user-definable; it can be either the internal microprocessor clock divided by four, or an external signal input via Port 3. The Timer Mode register configures the external timer input as an external clock, a trigger input that can be retriggerable or non-retriggerable, or as a gate input for the internal clock. The counter/timers can be programmably cascaded by connecting the $T_0$ output to the input of $T_1$ . Port 3 line P3 <sub>6</sub> also serves as a timer output (T <sub>OUT</sub> ) through which $T_0$ , $T_1$ or the internal clock can be output. |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

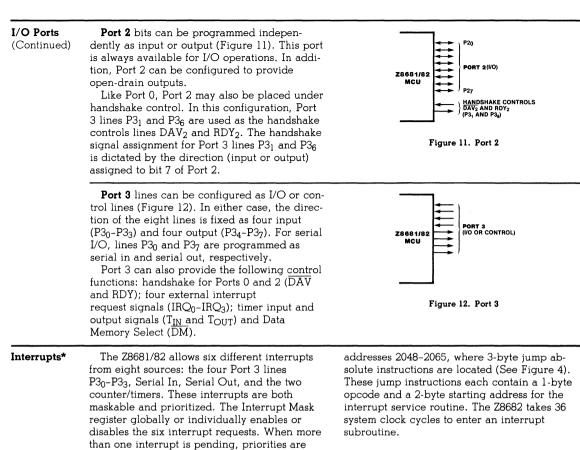

| I/O Ports          | The Z8681/82 has 24 lines available for input<br>and output. These lines are grouped into three<br>ports of eight lines each and are configurable<br>as input, output or address. Under software<br>control, the ports can be programmed to pro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | vide address outputs, timing, status signals,<br>serial I/O, and parallel I/O with or without<br>handshake. All ports have active pull-ups and<br>pull-downs compatible with TTL loads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

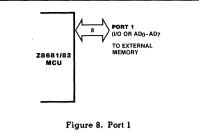

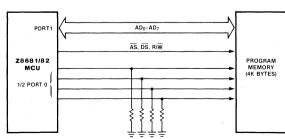

|                    | <b>Port 1</b> is a dedicated Z-BUS compatible<br>memory interface. The operations of Port 1 are<br>supported by the Address Strobe ( $\overline{AS}$ ) and<br>Data Strobe ( $\overline{DS}$ ) lines, and by the Read/Write<br>( $R/\overline{W}$ ) and Data Memory ( $\overline{DM}$ ) control lines.<br>The low-order program and data memory<br>addresses ( $A_0$ - $A_7$ ) are output through Port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (Figure 8) and are multiplexed with data in/out<br>(D <sub>0</sub> -D <sub>7</sub> ). Instruction fetch and data memory<br>read/write operations are done through this<br>port.<br>Port 1 cannot be used as a register nor can a<br>handshake mode be used with this port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

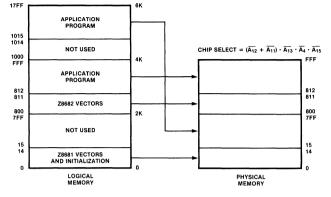

I/O Ports (Continued) Both the Z8681 and Z8682 wake up with the 8 bits of Port 1 configured as address outputs for external memory. If more than eight address line are required with the Z8681, additional lines can be obtained by programming Port 0 bits as address bits. The least-significant four bits of Port 0 can be configured to supply address bits  $A_8$ - $A_{11}$  for 4K byte addressing or both nibbles of Port 0 can be configured to supply address bits  $A_8$ - $A_{15}$  for 64K byte addressing.

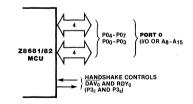

**Port 0\*** can be programmed as a nibble I/O port, or as an address port for interfacing external memory (Figure 9). When used as an I/O port, Port 0 may be placed under handshake control. In this configuration, Port 3 lines P3<sub>2</sub> and P3<sub>5</sub> are used as the handshake controls DAV<sub>0</sub> and RDY<sub>0</sub>. Handshake signal assignment is dictated by the I/O direction of the upper nibble P0<sub>4</sub>-P0<sub>7</sub>.

For external memory references, Port 0 can provide address bits  $A_8-A_{11}$  (lower nibble) or  $A_8-A_{15}$  (lower and upper nibbles) depending on the required address space. If the address range requires 12 bits or less, the upper nibble of Port 0 can be programmed independently as I/O while the lower nibble is used for addressing.

In the Z8681\*, Port 0 lines float after reset; their logic state is unknown until the execution of an initialization routine that configures Port 0.

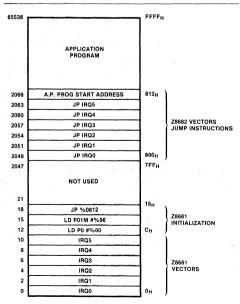

Such an initialization routine must reside within the first 256 bytes of executable code and must be physically mapped into memory by forcing the Port 0 address lines to a known state. See Figure 10. The proper Port initialization sequence is:

- 1. Write initial address (A<sub>8</sub>-A<sub>15</sub>) of initialization routine to Port 0 address lines.

- 2. Configure Port 0 Mode Register to output  $A_8-A_{15}$  (or  $A_8-A_{11}$ ).

To permit the use of slow memory, an automatic wait mode of two oscillator clock cycles is configured for the bus timing of the Z8681 after each reset. The initialization routine could include reconfiguration to

eliminate this extended timing mode.

The following example illustrates the manner in which an initialization routine can be mapped in a Z8681 system with 4K of memory.

Example. In Figure 10, the initialization routine is mapped to the first 256 bytes of program memory. Pull-down resistors maintain the address lines at a logic 0 level when these lines are floating. The leakage current caused by fanout must be taken into consideration when selecting the value of the pulldown resistors. The resistor value must be large enough to allow the Port 0 output driver to pull the line to a logic one. Generally, pulldown resistors are incompatible with TTL loads. If Port 0 drives into TTL input loads (I<sub>LOW</sub> = 1.6 ma) the external resistors should be tied to  $V_{CC}$  and the initialization routine put in address space FF00<sub>H</sub>-FFFF<sub>H</sub>.

In the Z8682<sup>\*</sup>, Port 0 lines are configured as address lines  $A_8$ - $A_{15}$  after a Reset. If one or both nibbles are needed for I/O operation, they must be configured by writing to the Port 0 Mode register. The Z8682 is in the fast memory timing mode after Reset, so the initialization routine must be in fast memory.

Figure 10. Port 0 Address Lines Tied to Logic 0

\*This feature differs in the Z8681 and Z8682

#### Table 1. Z8682 Interrupt Processing

| Address<br>(Hex) | Contains Jump Instruction and<br>Subroutine Address For |

|------------------|---------------------------------------------------------|

| 800-802          | IRQ0                                                    |

| 803-805          | IRQ1                                                    |

| 806-808          | IRQ2                                                    |

| 809-80B          | IRQ3                                                    |

| 80C-80E          | IRQ4                                                    |

| 80F-811          | IRQ5                                                    |

Polled interrupt systems are also supported. To accommodate a polled structure, any or all of the interrupt inputs can be masked and the Interrupt Request register polled to determine which of the interrupt requests needs service.

- AT cut, parallel-resonant

- Fundamental type

- Series resistance,  $R_s \le 100\Omega$

- For Z8681/Z8682, 8 MHz maximum

- For Z8681/Z8682-12, 12 MHz maximum

\*This feature differs in the Z8681 and Z8682

crystal are as follows:

resolved by a programmable priority encoder that is controlled by the Interrupt Priority

All Z8681 and Z8682 interrupts are vectored through locations in program memory. When an interrupt request is granted, an interrupt machine cycle is entered. This disables all subsequent interrupts, saves the Program Counter and status flags, and accesses the program memory vector location reserved for that interrupt. In the Z8681, this memory location and the next byte contain the 16-bit address of the interrupt service routine for that particular

interrupt request. The Z8681 takes 26 system

clock cycles to enter an interrupt subroutine.

The Z8682 has a small internal ROM that

The on-chip oscillator has a high-gain,

(XTAL1 = Input, XTAL2 = Output). The crystal source is connected across

parallel-resonant amplifier for connection to a

crystal or to any suitable external clock source

XTAL1 and XTAL2, using the recommended

capacitance ( $C_L$  = 15 pF maximum) from each pin to ground. The specifications for the

contains six 2-byte interrupt vectors pointing to

register.

7

Power Down Standby Option

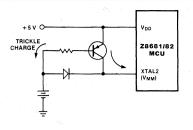

The low-power standby mode allows power to be removed without losing the contents of the 124 general-purpose registers. This mode is available only to the user as a bonding option whereby pin 2 (normally XTAL2) is replaced by the  $V_{MM}$  (standby) power supply input. This necessitates the use of an external clock generator (input = XTAL1) rather than a crystal source.

The removal of power, whether intended or due to power failure, must be preceded by a software routine that stores the appropriate status into the register file. Figure 13 shows the recommended circuit for a battery back-up supply system.

78681/78682 Inter-

Although the Z8681 and Z8682 have minor differences, a system can be designed for comchangeability patibility with both ROMless versions. To achieve interchangeability, the design must take into account the special requirements of each device in the external interface, initialization, and memory mapping.

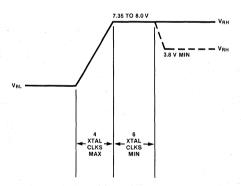

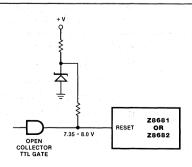

> External Interface. The Z8682 requires a 7.5 V positive logic level on the RESET pin for at least 6 clock periods immediately following reset, as shown in Figure 14. The Z8681 requires a 3.8 V or higher positive logic level, but is compatible with the Z8682 RESET waveform. Figure 15 shows a simple circuit for generating the 7.5 V level.

Figure 14. Z8682 RESET Pin Input Waveform

Figure 15. RESET Circuit

Figure 13, Recommended Driver Circuit for **Power-Down Operation**

Initialization. The Z8681 wakes up after reset with Port 0 configured as an input, which means Port 0 lines are floating in a highimpedance state. Because of this pullup or pulldown, resistors must be attached to Port 0 lines to force them to a valid logic level until Port 0 is configured as an address port.

Port 0 initialization is discussed in the section on ports. An example of an initialization routine for Z8681/Z8682 compatibility is shown in Table 2. Only the Z8681 need execute this program.

#### **Table 2. Initialization Routine**

| Address | Opcodes  | Instruction         | Comments                                                             |

|---------|----------|---------------------|----------------------------------------------------------------------|

| 000C    | E6 00 00 | LD PO #%00          | Set A <sub>8</sub> -A <sub>15</sub> to 0.                            |

| 000F    | E6 F8 96 | LD P01M #%96        | Configure Port 0 as $A_8-A_{15}$ . Eliminate extended memory timing. |

| 0012    | 8D 08 12 | JP START<br>ADDRESS | Execute application program.                                         |

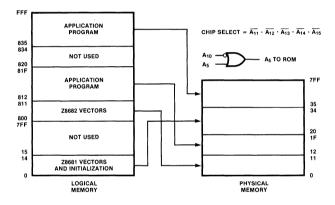

Figure 16. Z8681/82 Logical Program Memory Mapping

Z8681/Z8682 Inter-(Continued)

Memory Mapping. The Z8681 and Z8682 lower memory boundaries are located at 0 and changeability 2048, respectively. A single program ROM can be used with either product if the logical program memory map shown in Figure 16 is followed. The Z8681 vectors and initialization

routine must be starting at address 0 and the Z8682 3-byte vectors (jump instructions) must be at address 2048 and higher. Addresses in the range 21-2047 are not used. Figure 17 shows practical schemes for implementing this memory map using 4K and 2K ROMs.

| Instruction |                                           | essing Modes. The following notation is used scribe the addressing modes and instruction                          | src     | Source location or contents                                                                  |  |  |  |

|-------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------|--|--|--|

| Set         |                                           | ations as shown in the instruction summary.                                                                       | cc      | Condition code (see list)                                                                    |  |  |  |

| Notation    | opera                                     | ations as shown in the instruction summary.                                                                       | @       | Indirect address prefix                                                                      |  |  |  |

|             | IRR                                       | Indirect register pair or indirect working-register                                                               | SP      | Stack pointer (control registers 254–255)                                                    |  |  |  |

|             |                                           | pair address                                                                                                      | PC      | Program counter                                                                              |  |  |  |

|             | Irr                                       | Indirect working-register pair only                                                                               |         | Flag register (control register 252)                                                         |  |  |  |

|             | х                                         | Indexed address                                                                                                   | RP      | Register pointer (control register 253)                                                      |  |  |  |

|             | DĀ                                        | Direct address                                                                                                    | IMR     | Interrupt mask register (control register 251)                                               |  |  |  |

|             | RA                                        | Relative address                                                                                                  | Assi    | gnment of a value is indicated by the symbol                                                 |  |  |  |

|             | IM                                        | Immediate                                                                                                         |         | "←". For example,                                                                            |  |  |  |

|             | R                                         | Register or working-register address                                                                              |         | dst ← dst + src                                                                              |  |  |  |

|             | r                                         | Working-register address only                                                                                     | indica  | tes that the source data is added to the                                                     |  |  |  |

|             | IR                                        | Indirect-register or indirect working-register<br>address                                                         | destin  | ation data and the result is stored in the<br>ation location. The notation "addr(n)" is used |  |  |  |

|             | Ir Indirect working-register address only |                                                                                                                   |         | er to bit "n" of a given location. For example,                                              |  |  |  |

|             | RR                                        | Register pair or working register pair address                                                                    | dst (7) |                                                                                              |  |  |  |

|             |                                           | <b>bols.</b> The following symbols are used in<br>ribing the instruction set.<br>Destination location or contents | refers  | to bit 7 of the destination operand.                                                         |  |  |  |

| Instruction<br>Set<br>Notation<br>(Continued) | six flags:<br>C C<br>Z Z<br>S S<br>V C<br>D D |              | 2        | the following Affe                 | Cleared to ze<br>Set to one | e indicated by:<br>ro<br>d according to operation |  |

|-----------------------------------------------|-----------------------------------------------|--------------|----------|------------------------------------|-----------------------------|---------------------------------------------------|--|

| Condition                                     |                                               | /alue        | Mnemonic | Meaning                            |                             | Flags Set                                         |  |

| Codes                                         |                                               | 1000         |          | Always true                        |                             |                                                   |  |

|                                               |                                               | 0111         | C        | Carry                              |                             | C = 1                                             |  |

|                                               |                                               | 1111         | NC       | No carry                           |                             | C = 0                                             |  |

|                                               |                                               | 0110         | Z        | Zero                               |                             | Z = 1                                             |  |

|                                               |                                               | 1110         | NZ       | Not zero                           |                             | Z = 0                                             |  |

|                                               |                                               | 1101         | PL       | Plus                               |                             | S = 0                                             |  |

|                                               |                                               | 0101         | MI       | Minus                              |                             | S = 1                                             |  |

|                                               |                                               | 0100         | OV       | Overflow                           |                             | V = 1                                             |  |

|                                               |                                               | 1100         | NOV      | No overflow                        |                             | V = 0                                             |  |

|                                               |                                               | 0110         | EQ       | Equal                              |                             | Z = 1                                             |  |

|                                               |                                               | 1110         | NE       | Not equal                          |                             | Z = 0                                             |  |

|                                               |                                               | 1001<br>0001 | GE<br>LT | Greater than or equal<br>Less than |                             | (S XOR V) = 0<br>(S XOR V) = 1                    |  |

|                                               |                                               | 1010         | GT       | Greater than                       |                             | [Z OR (S XOR V)] = 1<br>[Z OR (S XOR V)] = 0      |  |

|                                               |                                               | 010          | LE       | Less than or equal                 |                             | [Z OR (S XOR V)] = 0<br>[Z OR (S XOR V)] = 1      |  |

|                                               |                                               | 1111         | UGE      | Unsigned greater than or equal     | anal .                      | C = 0                                             |  |

|                                               |                                               | 0111         | ULT      | Unsigned less than                 | Juui                        | C = 0                                             |  |

|                                               |                                               | 1011         | UGT      | Unsigned greater than              |                             | (C = 0  AND  Z = 0) = 1                           |  |

|                                               |                                               | 0011         | ULE      | Unsigned less than or equal        |                             | (C = 0  RND  2 = 0) = 1<br>(C OR Z) = 1           |  |

|                                               |                                               | 0000         | 0LL      | Never true                         |                             | (0 01(2) = 1                                      |  |

OPC

dst OPC

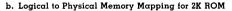

Instruction Formats

ormans

**One-Byte Instruction**

CCF, DI, EI, IRET, NOP, RCF, RET, SCF

INC r

**Two-Byte Instruction**

**Three-Byte Instruction**

Figure 18. Instruction Formats

# Instruction Summary

| Instruction<br>and Operation                                                                                | Addr<br>dst     | Mode<br>src                     | Opcode<br>Byte | Flags Affected |   |   |   |   |   |  |

|-------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------|----------------|----------------|---|---|---|---|---|--|

| ADC dst,src                                                                                                 |                 | te l)                           | (Hex)          | *              | * | * |   | 0 |   |  |

| $\frac{dst - dst + src + C}{dst - dst + src + C}$                                                           |                 |                                 |                |                |   |   |   |   |   |  |

| ADD dst,src<br>dst – dst + src                                                                              | (No             | te 1)                           | 0□             | *              | * | * | * | 0 | * |  |

| AND dst,src<br>dst – dst AND src                                                                            | (No             | tel)                            | 5□             | -              | * | * | 0 | - | _ |  |

| <b>CALL</b> dst<br>SP - SP - 2<br>@SP - PC; PC - d                                                          | DA<br>IRR<br>st |                                 | D6<br>D4       | -              |   | - | - | - | _ |  |

| C - NOT C                                                                                                   |                 |                                 | EF             | *              | - | - | - | - | - |  |

| CLR dst<br>dst - 0                                                                                          | R<br>IR         |                                 | B0<br>B1       | -              | - | - | - | - | - |  |

| <b>COM</b> dst<br>dst – NOT dst                                                                             | R<br>IR         |                                 | 60<br>61       | -              | * | * | 0 | - |   |  |

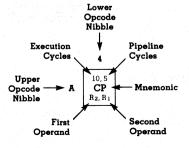

| CP dst,src<br>dst - src                                                                                     | (No             | te l)                           | A□             | *              | * | * | * |   | - |  |

| <b>DA</b> dst<br>dst ← DA dst                                                                               | R<br>IR         |                                 | 40<br>41       | *              | * | * | X | - | - |  |

| <b>DEC</b> dst<br>dst - dst - 1                                                                             | R<br>IR         |                                 | 00<br>01       | -              | * | * | * | - | - |  |

| <b>DECW</b> dst<br>dst - dst - 1                                                                            | RR<br>IR        |                                 | 80<br>81       | -              | * | * | * | - | - |  |

| <b>DI</b><br>IMR (7) ← 0                                                                                    |                 |                                 | 8F             | -              | _ | _ | _ | _ | _ |  |

| <b>DJNZ</b> r,dst<br>$r \leftarrow r - 1$<br>if $r \neq 0$<br>PC $\leftarrow$ PC + dst<br>Range: +127, -128 | RA              |                                 | rA<br>r=0-F    | -              | - | - | - | - | _ |  |

| <b>EI</b><br>IMR (7) ← 1                                                                                    |                 |                                 | 9F             | _              | - | - | _ | - |   |  |

| INC dst<br>dst – dst + 1                                                                                    | r               |                                 | rE<br>r = 0-F  | -              | * | * | * | - | - |  |

|                                                                                                             | R<br>IR         |                                 | 20<br>21       |                |   |   |   |   |   |  |

| INCW dst<br>dst – dst + 1                                                                                   | RR<br>IR        | aras - 1945 - 2 - 2 - 2 - 2 - 2 | A0<br>A1       | -              | * | * | * | - | - |  |

| IRET<br>FLAGS - @SP; SP                                                                                     | SD.             | + 1                             | BF             | *              | * | * | * | * | * |  |

| $PC \leftarrow @SP; SP \leftarrow SI$                                                                       | P + 2;          | IMR (7                          | 7) ← 1         |                |   |   |   |   |   |  |

| <b>JP</b> cc,dst<br>if cc is true                                                                           | DA              |                                 | cD<br>c=0-F    | -              | - | - | - | - | - |  |

| $\frac{PC \leftarrow dst}{JR \ cc, dst}$                                                                    | IRR<br>RA       |                                 | 30<br>cB       | _              | _ |   |   | _ |   |  |

| if cc is true,<br>PC – PC + dst<br>Range: +127, -128                                                        |                 |                                 | c = 0-F        |                |   |   |   |   |   |  |

| LD dst,src<br>dst – src                                                                                     | r<br>r          | Im<br>R                         | rC<br>r8       | -              | - | - | - | - | - |  |

|                                                                                                             | Ř               | r                               | r9<br>r=0-F    |                |   |   |   |   |   |  |

|                                                                                                             | r<br>X          | X<br>r                          | C7<br>D7       |                |   |   |   |   |   |  |

|                                                                                                             | r<br>Ir         | Ir<br>r                         | E3<br>F3       |                |   |   |   |   |   |  |

|                                                                                                             | R<br>R          | R<br>IR                         | E4<br>E5       |                |   |   |   |   |   |  |

|                                                                                                             | R<br>IR<br>IR   | IM<br>IM<br>R                   | E6<br>E7<br>F5 |                |   |   |   |   |   |  |

| LDC dst,src<br>dst - src                                                                                    | r<br>Irr        | Irr<br>r                        | C2<br>D2       |                | - | _ | _ | _ | - |  |

| <b>LDCI</b> dst,src<br>dst $-$ src<br>r $-$ r + 1; rr $-$ rr +                                              | Ir<br>Irr       | Irr<br>Ir                       | C3<br>D3       |                |   |   | - |   | - |  |

| Instruction                                                                                | Addr )    | Mode      | Opcode        | Fle | ag  | s A | ffe | ect | ed |

|--------------------------------------------------------------------------------------------|-----------|-----------|---------------|-----|-----|-----|-----|-----|----|

| and Operation                                                                              | dst       | src       | Byte<br>(Hex) | С   | Z   | S   | V   | D   | н  |

| LDE dst,src<br>dst – src                                                                   | r<br>Irr  | Irr<br>r  | 82<br>92      | -   | -   | -   | -   | -   | -  |

| <b>LDEI</b> dst, src<br>dst $\leftarrow$ src<br>r $\leftarrow$ r + 1; rr $\leftarrow$ rr + | Ir<br>Irr | Irr<br>Ir | 83<br>93      | -   |     | -   | -   | -   | -  |

|                                                                                            |           |           | FF            |     |     | _   | _   |     | _  |

| OR dst,src<br>dst ← dst OR src                                                             | (Note     | ə l)      | 4             | -   | *   | *   | 0   | -   | -  |

| <b>POP</b> dst<br>dst $\leftarrow @ SP$<br>SP $\leftarrow SP + 1$                          | R<br>IR   |           | 50<br>51      | -   | -   | -   | -   |     | -  |

| <b>PUSH</b> src<br>SP - SP - 1; @ SP -                                                     | - src     | R<br>IR   | 70<br>71      | -   | -   | -   | -   | -   | -  |

| <b>RCF</b><br>C - 0                                                                        |           |           | CF            | 0   | -   | -   | -   | -   | -  |

| RET<br>PC - @SP; SP - SI                                                                   | P + 2     |           | AF            | -   | -   | -   | -   | -   | -  |

| RL dst                                                                                     | ] R<br>IR |           | 90<br>91      | *   | *   | *   | *   | -   | -  |

| RLC dst                                                                                    | ] R<br>IR |           | 10<br>11      | *   | *   | *   | *   | -   | -  |

| RR dst                                                                                     | ] R<br>IR |           | E0<br>E1      | *   | *   | *   | *   |     | -  |

| RRC dst [                                                                                  | ] R<br>IR |           | C0<br>C1      | *   | *   | *   | *   |     |    |

| <b>SBC</b> dst,src<br>dst ← dst - src - C                                                  | (Note     | 1)        | 3□            | *   | *   | *   | *   | 1   | *  |

| <b>SCF</b><br>C + 1                                                                        |           |           | DF            | 1   | -   | -   | _   | -   | -  |

| SRA dst                                                                                    | ] R<br>IR |           | D0<br>D1      | *   | *   | *   | 0   | -   | -  |

| <b>SRP</b> src<br>RP - src                                                                 |           | Im        | 31            | -   | - 1 |     | -   | -   | -  |

| <b>SUB</b> dst,src<br>dst ← dst - src                                                      | (Note     | 1)        | 2□            | *   | *   | *   | *   | 1   | *  |

| SWAP dst                                                                                   | R<br>IR   |           | FO<br>Fl      | Х   | *   | *   | х   | -   | -  |

| <b>TCM</b> dst,src<br>(NOT dst) AND src                                                    | (Note     | 1)        | 6□            | -   | *   | *   | 0   |     | -  |

| <b>TM</b> dst, src<br>dst AND src                                                          | (Note     | 1)        | 7□            | -   | *   | *   | 0   | _   | -  |

| <b>XOR</b> dst,src<br>dst – dst XOR src                                                    | (Note     | 1)        | В□            | -   | *   | *   | 0   | -   |    |

## Note 1

These instructions have an identical set of addressing modes, which are encoded for brevity. The first opcode nibble is found in the instruction set table above. The second nibble is expressed symbolically by a  $\Box$  in this behavior. table, and its value is found in the following table to the left of the applicable addressing mode pair. For example, to determine the opcode of an ADC

instruction using the addressing modes r (destination) and Ir (source) is 13.

|   | Addr | Mode | Lower         |  |

|---|------|------|---------------|--|

| _ | dst  | SIC  | Opcode Nibble |  |

|   | r    | r    | 2             |  |

|   | r    | Ir   | 3             |  |

|   | R    | R    | 4             |  |

|   | R    | IR   | 5             |  |

|   | R    | IM   | 6             |  |

|   | IR   | IM   | 7             |  |

----- SERIAL DATA (D<sub>0</sub> = LSB)

# R244 TO Counter/Timer 0 Register (F4<sub>H</sub>; Read/Write)

R242 T1 Counter Timer 1 Register (F2<sub>H</sub>; Read/Write)

R246 P2M Port 2 Mode Register (F6<sub>H</sub>; Write Only)

$D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0$

P20-P27 I/O DEFINITION - 0 DEFINES BIT AS OUTPUT 1 DEFINES BIT AS INPUT

| 81/82<br>code | 2                        |                                            |                                                        |                                                       |                                                        |                                                         | Low                                        | er Nibble                                   | e (Hex)             |                     |                           |                                |                            |                     |                  |                 |

|---------------|--------------------------|--------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------|---------------------------------------------|---------------------|---------------------|---------------------------|--------------------------------|----------------------------|---------------------|------------------|-----------------|

| rp            | 0                        | 1                                          | 2                                                      | 3                                                     | 4                                                      | 5                                                       | 6                                          | 7                                           | 8                   | 9                   | A                         | В                              | С                          | D                   | Е                | F               |

|               |                          |                                            |                                                        |                                                       | 10.5                                                   | 10.5                                                    | 10.7                                       | 10.5                                        | 0.0                 | 0.0                 |                           | 10/10 0                        |                            | 12/10,0             |                  | 1               |

| 0             | 6,5<br>DEC<br>R1         | 6,5<br><b>DEC</b><br>IR1                   | 6,5<br><b>ADD</b><br>11,12                             | 6,5<br><b>ADD</b><br>r1, Ir2                          | 10, 5<br><b>ADD</b><br>R <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>ADD</b><br>IR <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>ĀDD</b><br>R <sub>1</sub> , IM | 10, 5<br><b>ADD</b><br>IR <sub>1</sub> , IM | 6,5<br>LD<br>r1, R2 | 6,5<br>LD<br>12, R1 | 12/10,5<br>DJNZ<br>r1, RA | 12/10,0<br><b>JR</b><br>cc, RA | 6,5<br><b>LD</b><br>r1, IM | <b>JP</b><br>cc, DA | 6,5<br>INC<br>11 |                 |

| 1             | 6,5<br>RLC<br>R1         | 6,5<br><b>RLC</b><br>IR1                   | 6,5<br>ADC<br>11,12                                    | 6,5<br>ADC<br>r1, Ir2                                 | 10,5<br><b>ADC</b><br>R <sub>2</sub> , R <sub>1</sub>  | 10, 5<br><b>ADC</b><br>IR <sub>2</sub> , R <sub>1</sub> | 10,5<br><b>ADC</b><br>R <sub>1</sub> , IM  | 10,5<br><b>ADC</b><br>IR <sub>1</sub> , IM  |                     |                     |                           |                                |                            |                     |                  |                 |

| 2             | 6,5<br>INC<br>R1         | 6,5<br>INC<br>IR1                          | 6,5<br><b>SUB</b><br>11,12                             | 6,5<br><b>SUB</b><br>ri,Ir2                           | 10, 5<br><b>SUB</b><br>R <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>SUB</b><br>IR <sub>2</sub> , R <sub>1</sub> | .10,5<br><b>SUB</b><br>R1,IM               | 10, 5<br><b>SUB</b><br>IR 1, IM             |                     | , 1                 |                           |                                |                            |                     |                  |                 |

| 3             | 8,0<br><b>JP</b><br>IRR1 | 6, 1<br><b>SRP</b><br>IM                   | 6,5<br><b>SBC</b><br>11,12                             | 6,5<br><b>SBC</b><br>r1, Ir2                          | 10,5<br><b>SBC</b><br>R <sub>2</sub> , R <sub>1</sub>  | 10,5<br><b>SBC</b><br>IR <sub>2</sub> , R <sub>1</sub>  | 10,5<br><b>SBC</b><br>R <sub>1</sub> ,IM   | 10, 5<br><b>SBC</b><br>IR <sub>1</sub> , IM |                     |                     |                           |                                |                            | -                   |                  |                 |

| 4             | 8,5<br>DA<br>R1          | 8,5<br><b>DA</b><br>IR1                    | 6,5<br>OR<br>11,12                                     | 6, 5<br>OR<br>r1, Ir2                                 | 10, 5<br>OR<br>R <sub>2</sub> , R <sub>1</sub>         | 10, 5<br><b>OR</b><br>IR <sub>2</sub> , R <sub>1</sub>  | 10, 5<br><b>OR</b><br>R1, IM               | 10, 5<br><b>OR</b><br>IR 1, IM              |                     |                     |                           |                                |                            |                     |                  |                 |

| 5             | 10, 5<br>POP<br>R1       | 10,5<br><b>POP</b><br>IR1                  | 6,5<br><b>AND</b><br>11,12                             | 6,5<br><b>AND</b><br>r1, Ir2                          | 10, 5<br><b>AND</b><br>R <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>AND</b><br>IR <sub>2</sub> , R <sub>1</sub> | 10,5<br><b>AND</b><br>R <sub>1</sub> , IM  | 10,5<br><b>AND</b><br>IR1, IM               |                     |                     |                           |                                |                            |                     |                  |                 |

| 6             | 6,5<br>COM<br>R1         | 6,5<br><b>COM</b><br>IR1                   | 6,5<br><b>TCM</b><br>11,12                             | 6,5<br><b>TCM</b><br>r <sub>1</sub> , Ir <sub>2</sub> | 10,5<br><b>TCM</b><br>R <sub>2</sub> , R <sub>1</sub>  | 10, 5<br><b>TCM</b><br>IR <sub>2</sub> , R <sub>1</sub> | 10,5<br><b>TCM</b><br>R <sub>1</sub> ,IM   | 10, 5<br><b>TCM</b><br>IR 1, IM             |                     |                     |                           |                                |                            |                     |                  |                 |

| 7             | 10/12,1<br>PUSH<br>R2    | 12/14, 1<br><b>PUSH</b><br>IR <sub>2</sub> | 6,5<br><b>TM</b><br>11,12                              | 6,5<br><b>TM</b><br>r1, Ir2                           | 10, 5<br><b>TM</b><br>R <sub>2</sub> , R <sub>1</sub>  | 10, 5<br><b>TM</b><br>IR <sub>2</sub> , R <sub>1</sub>  | 10, 5<br><b>TM</b><br>R <sub>1</sub> , IM  | 10, 5<br><b>TM</b><br>IR 1, IM              |                     |                     |                           |                                |                            |                     |                  |                 |

| 8             | 10, 5<br>DECW<br>RR 1    | 10,5<br><b>DECW</b><br>IR1                 | 12, 0<br>LDE<br>r <sub>1</sub> , Irr <sub>2</sub>      | 18,0<br><b>LDEI</b><br>Ir1, Irr2                      |                                                        | an a                |                                            |                                             |                     |                     |                           |                                |                            |                     |                  | 6,<br>D         |

| 9             | 6,5<br><b>RL</b><br>R1   | 6, 5<br><b>RL</b><br>IR 1                  | 12,0<br><b>LDE</b><br>r <sub>2</sub> ,Irr <sub>1</sub> | 18,0<br><b>LDEI</b><br>Ir2,Irr1                       |                                                        |                                                         |                                            |                                             |                     |                     |                           |                                |                            |                     |                  | 6,<br><b>E</b>  |

| A             | 10, 5<br>INCW<br>RR 1    | 10,5<br>INCW<br>IR1                        | 6,5<br><b>CP</b><br>1,12                               | 6,5<br><b>CP</b><br>r1, Ir2                           | 10,5<br><b>CP</b><br>R <sub>2</sub> , R <sub>1</sub>   | 10, 5<br><b>CP</b><br>IR <sub>2</sub> , R <sub>1</sub>  | 10, 5<br><b>CP</b><br>R <sub>1</sub> , IM  | 10, 5<br><b>CP</b><br>IR 1, IM              |                     |                     |                           |                                |                            |                     |                  | 14,<br>RE       |

| В             | 6,5<br>CLR<br>R1         | 6,5<br><b>CLR</b><br>IR1                   | 6,5<br><b>XOR</b><br>1,12                              | 6,5<br><b>XOR</b><br>r1, Ir2                          | 10,5<br><b>XOR</b><br>R <sub>2</sub> , R <sub>1</sub>  | 10, 5<br><b>XOR</b><br>IR <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>XOR</b><br>R <sub>1</sub> , IM | 10, 5<br><b>XOR</b><br>IR 1, IM             |                     |                     |                           |                                |                            |                     |                  | 16.<br>IRI      |

| С             | 6, 5<br><b>RRC</b><br>R1 | 6,5<br><b>RRC</b><br>IR1                   | 12,0<br>LDC<br>r1, Irr2                                | 18, 0<br><b>LDCI</b><br>Ir1, Irr2                     |                                                        |                                                         |                                            | 10,5<br>LD<br>11, x, R <sub>2</sub>         |                     |                     |                           |                                |                            |                     |                  | 6,<br>RC        |

| D             | 6,5<br><b>SRA</b><br>R1  | 6,5<br><b>SRA</b><br>IR1                   | 12,0<br>LDC<br>12,Irr1                                 | 18,0<br><b>LDCI</b><br>Ir2, Irr1                      | 20,0<br><b>CALL*</b><br>IRR1                           |                                                         | 20,0<br><b>CALL</b><br>DA                  | 10, 5<br>LD<br>12, x, R <sub>1</sub>        |                     |                     |                           |                                |                            |                     |                  | 6,<br><b>SC</b> |

| Е             | 6,5<br><b>RR</b><br>R1   | 6,5<br><b>RR</b><br>IR1                    |                                                        | 6,5<br>LD<br>11,IR2                                   | 10, 5<br><b>LD</b><br>R <sub>2</sub> , R <sub>1</sub>  | 10, 5<br>LD<br>IR <sub>2</sub> , R <sub>1</sub>         | 10, 5<br><b>LD</b><br>R <sub>1</sub> , IM  | 10, 5<br><b>LD</b><br>IR <sub>1</sub> , IM  |                     |                     |                           |                                |                            |                     |                  | 6,<br>CC        |

| F             | 8,5<br>SWAP<br>R1        | 8,5<br><b>SWAP</b><br>IR1                  |                                                        | 6, 5<br>LD<br>Ir1, r2                                 |                                                        | 10, 5<br><b>LD</b><br>R <sub>2</sub> , IR <sub>1</sub>  |                                            |                                             | •                   |                     |                           |                                |                            |                     |                  | 6,<br>NC        |

|               |                          |                                            |                                                        |                                                       | 1                                                      |                                                         |                                            |                                             |                     |                     |                           |                                |                            |                     |                  |                 |

## Legend:

R = 8-Bit Address r = 4-Bit Address  $R_1 \text{ or } r_1 = Dst Address$   $R_2 \text{ or } r_2 = Src Address$

## Sequence:

Opcode, First Operand, Second Operand

Note: The blank areas are not defined.

\*2-byte instruction; fetch cycle appears as a 3-byte instruction

| Absolute<br>Maximum<br>Ratings | Voltages on all pins*<br>with respect to GND0.3 V to +7.0 V |

|--------------------------------|-------------------------------------------------------------|

| nunngs                         | Operating Ambient<br>Temperature See Ordering Information   |

|                                | Storage Temperature65 °C to +150 °C                         |

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only: operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

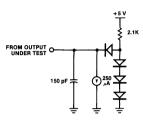

Standard Test Conditions The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the reference pin. Standard conditions are as follows:

$\blacksquare +4.75 \text{ V} \leq \text{V}_{\text{CC}} \leq +5.25 \text{ V}$

Figure 20. Test Load 1

$\blacksquare$  GND = 0 V

- 0°C ≤ T<sub>Å</sub> ≤ +70°C for S (Standard temperature)

- $-40^{\circ}C \le T_A \le +85^{\circ}C$  for E (Extended temperature)

Figure 21. External Clock Interface Circuit

| C                 | Symb            | ool Parameter                  | Min  | Max             | Unit | Condition                                                    |

|-------------------|-----------------|--------------------------------|------|-----------------|------|--------------------------------------------------------------|

| haracter-<br>tics | V <sub>CH</sub> | Clock Input High Voltage       | 3.8  | V <sub>CC</sub> | V    | Driven by External Clock Generator                           |

|                   | V <sub>CL</sub> | Clock Input Low Voltage        | -0.3 | 0.8             | v    | Driven by External Clock Generator                           |

|                   | V <sub>IH</sub> | Input High Voltage             | 2.0  | V <sub>CC</sub> | v    |                                                              |

|                   | V <sub>IL</sub> | Input Low Voltage              | -0.3 | 0.8             | v    |                                                              |

|                   | V <sub>RH</sub> | Reset Input High Voltage       | 3.8  | V <sub>CC</sub> | ý    | See Note                                                     |

|                   | V <sub>RL</sub> | Reset Input Low Voltage        | -0.3 | 0.8             | v    |                                                              |

|                   | V <sub>OH</sub> | Output High Voltage            | 2.4  |                 | V    | $I_{OH} = -250 \ \mu \text{A}$                               |

|                   | V <sub>OL</sub> | Output Low Voltage             |      | 0.4             | V    | $I_{OL} = +2.0 \text{ mA}$                                   |

|                   | I <sub>IL</sub> | Input Leakage                  | -10  | 10              | μA   | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq +5.25 \text{ V}$ |

|                   | I <sub>OL</sub> | Output Leakage                 | -10  | 10              | μA   | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq +5.25 \text{ V}$ |

|                   | I <sub>IR</sub> | Reset Input Current            |      | -50             | μA   | $V_{\rm CC}$ = +5.25 V, $V_{\rm RL}$ = 0 V                   |

|                   | I <sub>CC</sub> | V <sub>CC</sub> Supply Current |      | 180             | mA   |                                                              |

|                   | I <sub>MM</sub> | V <sub>MM</sub> Supply Current |      | 10              | mÅ   | Power Down Mode                                              |

|                   | V <sub>MM</sub> | Backup Supply Voltage          | 3    | V <sub>CC</sub> | V    | Power Down                                                   |

|                   | NOTE            |                                |      |                 |      |                                                              |

NOTE:

The Reset line (pin 6) is used to place the Z8682 in external memory mode. This is accomplished as shown in Figure 14.

15

# External I/O or Memory Read and Write Timing

Figure 22. External I/O or Memory Read/Write Timing

|     |            |                                                             |     | Z8681/82<br>8 MHz |     | Z8681/82<br>12 MHz |         |

|-----|------------|-------------------------------------------------------------|-----|-------------------|-----|--------------------|---------|

| No. | Symbol     | Parameter                                                   | Min | Μαχ               | Min | Μαχ                | Notes*† |

| 1   | TdA(AS)    | Address Valid to $\overline{\mathrm{AS}}$ † Delay           | 50  |                   | 35  |                    | 1,2,3   |

| 2   | TdAS(A)    | AS 1 to Address Float Delay                                 | 70  |                   | 45  |                    | 1,2,3   |

| 3   | TdAS(DR)   | ĀS † to Read Data Required Valid                            |     | 360               |     | 220                | 1,2,3,4 |

| 4   | TwAS       | AS Low Width                                                | 80  |                   | 55  |                    | 1,2,3   |

| 5   | TdAz(DS)   | Address Float to DS 4                                       | 0   |                   | 0   |                    | 1       |

| 6—  | -TwDSR     | — DS (Read) Low Width — — — — — — — — — — — — — — — — — — — | 250 |                   |     |                    | 1,2,3,4 |

| 7   | TwDSW      | DS (Write) Low Width                                        | 160 |                   | 110 |                    | 1,2,3,4 |

| 8   | TdDSR(DR)  | DS ↓ to Read Data Required Valid                            |     | 200               |     | 130                | 1,2,3,4 |

| 9   | ThDR(DS)   | Read Data to $\overline{\mathrm{DS}}$ † Hold Time           | 0   |                   | 0   |                    | 1       |

| 10  | TdDS(A)    | DS † to Address Active Delay                                | 70  |                   | 45  |                    | 1,2,3   |

| 11  | TdDS(AS)   | DS ↑ to AS ↓ Delay                                          | 70  |                   | 55  |                    | 1,2,3   |

| 12— | -TdR/W(AS) | —R/W Valid to AS 1 Delay———                                 | 50  |                   |     |                    | l,2,3   |

| 13  | TdDS(R/W)  | DS 1 to R/W Not Valid                                       | 60  |                   | 35  |                    | 1,2,3   |

| 14  | TdDW(DSW)  | Write Data Valid to DS (Write) ↓ Delay                      | 50  |                   | 35  |                    | 1,2,3   |

| 15  | TdDS(DW)   | DS 1 to Write Data Not Valid Delay                          | 70  |                   | 45  |                    | 1,2,3   |

| 16  | TdA(DR)    | Address Valid to Read Data Required Valid                   |     | 410               |     | 255                | 1,2,3,4 |

| 17  | TdAS(DS)   | ĀS ↑ to DS ↓ Delay                                          | 80  |                   | 55  |                    | 1,2,3   |

NOTES:

Test Load 1

Timing numbers given are for minimum TpC.

Also see clock cycle time dependent characteristics table.

When using extended memory timing add 2 TpC.

5. All timing references use 2.0 V for a logic "1" and 0.8 V for a logic "0".

\* All units in nanoseconds (ns).

† Timings are preliminary and subject to change.

# Additional Timing Table

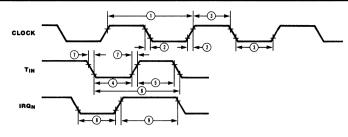

# Figure 23. Additional Timing

| No. |             |                                   | Z868<br>8 M            | Z8681/82<br>12 MHz |                 |      |         |

|-----|-------------|-----------------------------------|------------------------|--------------------|-----------------|------|---------|

|     | Symbol      | Parameter                         | Min                    | Μαχ                | Min             | Max  | Notes*‡ |

| 1   | TpC         | Input Clock Period                | 125                    | 1000               | 83              | 1000 | 1       |

| 2   | TrC,TfC     | Clock Input Rise And Fall Times   |                        |                    | 15              | 1    |         |

| 3   | TwC         | Input Clock Width                 | 37                     | 26                 |                 | 1    |         |

| 4   | TwTinL      | Timer Input Low Width             | 100                    |                    | 70              |      | 2       |

| 5—  | -TwTinH     |                                   | 3TpC                   |                    | — ЗТрС-         | an   | 2       |

| 6   | TpTin       | Timer Input Period                | $\frac{\text{TpC}}{8}$ |                    | $\frac{TpC}{8}$ |      | 2       |

| 7   | TrTin,TfTin | Timer Input Rise And Fall Times   |                        | 100                |                 | 100  | 2       |

| 8   | TwIL        | Interrupt Request Input Low Time  | 100                    |                    | 70              |      | 2,3     |

| 9   | TwIH        | Interrupt Request Input High Time | 3TpC                   |                    | 3TpC            |      | 2,3     |

NOTES: 1. Clock timing references uses 3.8 V for a logic "1" and 0.8 V for a logic "0". 2. Timing reference uses 2.0 V for a logic "1" and 0.8 V for a logic "0".

3. Interrupt request via Port 3.

\* Units in nanoseconds (ns).

† Timings are preliminary and subject to change.

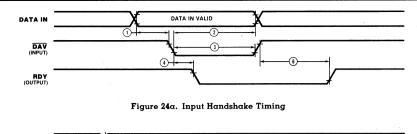

# Handshake Timing

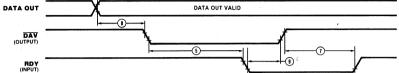

| Figure | 24h          | Output | Handshake | Timing |

|--------|--------------|--------|-----------|--------|

| riguie | <b>44</b> D. | Output | nunusnuke | rimmy  |

\* Units in nanoseconds (ns). † Timings are preliminary and subject to change.

|             |               |                             | Z868<br>8 N | Z8681/82<br>12 MHz |     |     |         |

|-------------|---------------|-----------------------------|-------------|--------------------|-----|-----|---------|

| No.         | Symbol        | Parameter                   | Min         | Μαχ                | Min | Μαχ | Notes*† |

| l TsDI(DAV) |               | Data In Setup Time          | 0           |                    | 0   |     |         |

| 2           | ThDI(DAV)     | Data In Hold Time           | 230         |                    | 160 |     |         |

| 3           | TwDAV         | Data Available Width        | 175         |                    | 120 |     |         |

| 4           | TdDAVIf(RDY)  | DAV ↓ Input to RDY ↓ Delay  |             | 175                |     | 120 | 1,2     |

| 5—          | -TdDAVOf(RDY) |                             | 0           |                    |     |     | 1,3     |

| 6           | TdDAVIr(RDY)  | DAV † Input to RDY † Delay  |             | 175                |     | 120 | 1,2     |

| 7           | TdDAV0rRDY)   | DAV 1 Output to RDY 1 Delay | 0           |                    | 0   |     | 1,3     |

| 8           | TdDO(DAV)     | Data Out to DAV ↓ Delay     | 50          |                    | 30  |     | 1       |

| 9           | TdRDY(DAV)    | Rdy ↓ Input to DAV † Delay  | 0           | 200                | 0   | 140 | 1       |

NOTES: 1. Test load 1 2. Input handshake 3. Output handshake 4. All timing regerences use 2.0 V for a logic "1" and 0.8 V for a logic "0".

| Clock-<br>Cycle-Time-<br>Dependent | Number | Symbol    | Z8681/82<br>8 MHz<br>Equation | <b>Z868</b> 1/82<br>12 MHz<br>Equation |