MANUAL

-

8861

4416

## TOSHIBA

16-BIT MICROPROCESSOR

# TLCS-68000

# **USERS MANUAL**

AUGUST 1988

TOSHIBA CORPORATION

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

The products described in this document are strategic products subject to COCOM regulations. They should not be exported without authorization from the appropriate governmental authorities.

The products described in this document contain components made in the United States and subject to export control of the U.S. authorities. Diversion contrary to the U.S. law is prohibited.

"M68000 16/32 BIT MICROPROCESSOR PROGRAMMER'S REFERENCE MANUAL" is the original of this manual and is issued by Motorola Inc., through Prentice-Hall. The publishing of this manual is permitted by Motorola Inc. No part of this manual may be transferred or reproduced without prior permission of Toshiba Corporation.

Copyright 1988 by TOSHIBA CORPORATION June 1988 •

#### TOSHIBA

#### Preface

Thank you very much for making use of TOSHIBA microcomputer LSIs and development systems.

The TLCS-68000 family, including the TMP68000, is the general-purpose 16/32-bit microprocessor family which is developed by technical cooperation with Motorola Inc., and is compatible with the Motorola M68000 family. The TMP68000/10/08 have various features such as the general purpose 32-bit register set, the large linear address space, the powerful instruction set, and flexible addressing modes. The common 32-bit internal architecture is upward compatible with all the family MPUs. This manual describes overview of the architecture and function of each instruction set, which are requires for software development for each MPU (TMP68000/10/08) of TLCS-68000 family. Toshiba provides various microcomputer LSIs and its development system for wide range of application.

No part of this manual may be transferred or reproduces without prior permission of Toshiba corporation.

#### TOSHIBA

TLCS-68000

### **16-Bit Microprocessors**

User's Manual

TOSHIBA CORPORATION

#### CONTENTS

| 1. ARCHITECTURAL DESCRIPTION                          |                                                  |      |   |    |  |  |  |  |

|-------------------------------------------------------|--------------------------------------------------|------|---|----|--|--|--|--|

| 1.1 I                                                 | 1 INTRODUCTION                                   |      |   |    |  |  |  |  |

| 1.2 F                                                 | PROGRAMMER'S MODEL                               |      |   |    |  |  |  |  |

| 1.3 S                                                 | SOFTWARE DEVELOPMENT                             |      |   |    |  |  |  |  |

| 1.3.1                                                 | Consistent Structure                             | VMPU | - | 5  |  |  |  |  |

| 1.3.2                                                 | Structured Modular Programming                   | VMPU | - | 9  |  |  |  |  |

| 1.3.3                                                 | Improved Software Testability                    | VMPU | - | 9  |  |  |  |  |

| 1.4 V                                                 | VIRTUAL MEMORY/MACHINE CONCEPTS                  | VMPU | - | 10 |  |  |  |  |

| 1.4.1                                                 | Virtual Memory                                   | VMPU | - | 11 |  |  |  |  |

| 1.4.2                                                 | Virtual Machine                                  | VMPU | - | 12 |  |  |  |  |

|                                                       |                                                  |      |   |    |  |  |  |  |

| 2. DAT                                                | A ORGANIZATION AND ADDRESSING                    |      |   |    |  |  |  |  |

| CAP.                                                  | ABILITIES                                        | VMPU | - | 13 |  |  |  |  |

| 2.1 I                                                 | NTRODUCTION                                      | VMPU | - | 13 |  |  |  |  |

| 2.2 (                                                 | OPERAND SIZE                                     | VMPU | - | 13 |  |  |  |  |

| 2.3 I                                                 | DATA ORGANIZATION IN REGISTERS                   | VMPU | - | 13 |  |  |  |  |

| 2.3.1                                                 | Data Registers                                   | VMPU | - | 13 |  |  |  |  |

| 2.3.2                                                 | 2.3.2 Address Registers                          |      |   |    |  |  |  |  |

| 2.4 I                                                 | DATA ORGANIZATION IN MEMORY                      | VMPU | - | 14 |  |  |  |  |

| 2.5 A                                                 | ADDRESSING                                       | VMPU | - | 17 |  |  |  |  |

| 2.6 I                                                 | NSTRUCTION FORMAT                                | VMPU | - | 17 |  |  |  |  |

| 2.7 I                                                 | .7 PROGRAM/DATA REFERENCES                       |      |   |    |  |  |  |  |

| 2.8 I                                                 | REGISTER NOTATION                                | VMPU | - | 18 |  |  |  |  |

| 2.9 A                                                 | 2.9 ADDRESS REGISTER INDIRECT NOTATION           |      |   |    |  |  |  |  |

| 2.10 H                                                | 2.10 REGISTER SPECIFICATION                      |      |   |    |  |  |  |  |

| 2.11 EFFECTIVE ADDRESS                                |                                                  |      |   |    |  |  |  |  |

| 2.11.1 Register Direct Modes                          |                                                  |      |   | 19 |  |  |  |  |

| 2.11.1.1 Data Register Direct                         |                                                  | VMPU | - | 19 |  |  |  |  |

| 2.11.1.2 Address Register Direct                      |                                                  | VMPU | - | 19 |  |  |  |  |

| 2.11.2 Memory Address Modes                           |                                                  | VMPU | - | 19 |  |  |  |  |

| 2.11                                                  | .2.1 Address Register Indirect                   | VMPU | - | 20 |  |  |  |  |

| 2.11.2.2 Address Register Indirect with Postincrement |                                                  | VMPU | - | 20 |  |  |  |  |

| 2.11                                                  | .2.3 Address Register Indirect with Predecrement | VMPU | - | 20 |  |  |  |  |

| 2.1    | 2.11.2.4 Address Register Indirect with Displacement |                        |  |  |  |  |  |

|--------|------------------------------------------------------|------------------------|--|--|--|--|--|

| 2.1    | 2.11.2.5 Address Register Inderect with Index        |                        |  |  |  |  |  |

| 2.11.  | 2.11.3 Special Address Modes                         |                        |  |  |  |  |  |

| 2.1    | 1.3.1 Absolute Short Address                         | VMPU - 22              |  |  |  |  |  |

| 2.1    | 1.3.2 Absolute Long Address                          | VMPU - 23              |  |  |  |  |  |

| 2.1    | 1.3.3 Program Counter with Displacement              | VMPU - 23              |  |  |  |  |  |

| 2.1    | 1.3.4 Program Counter with Index                     | VMPU - 24              |  |  |  |  |  |

| 2.1    | 1.3.5 Immediate Data                                 | VMPU - 24              |  |  |  |  |  |

| 2.11.4 | 4 Effective Address Encoding Summary                 | VMPU - 25              |  |  |  |  |  |

| 2.12   | IMPLICIT REFERENCE                                   | VMPU - 26              |  |  |  |  |  |

| 2.13   | STACK AND QUEUES                                     | VMPU - 27              |  |  |  |  |  |

| 2.13.  | 1 System Stack                                       | VMPU - 27              |  |  |  |  |  |

| 2.13.1 | 2 User Stacks                                        | VMPU - 27              |  |  |  |  |  |

| 2.13.5 | 3 Queues                                             | VMPU - 29              |  |  |  |  |  |

|        |                                                      |                        |  |  |  |  |  |

| 3. INS | TRUCTION SET SUMMARY                                 | VMPU - 31              |  |  |  |  |  |

| 3.1    | INTRODUCTION                                         | VMPU - 31              |  |  |  |  |  |

| 3.2    | DATA MOVEMENT OPERATIONS                             | VMPU - 32              |  |  |  |  |  |

| 3.3    | INTEGER ARITHMETIC OPERATIONS                        | VMPU - 33              |  |  |  |  |  |

| 3.4    | LOGICAL OPERATIONS                                   | VMPU - 35              |  |  |  |  |  |

| 3.5    | SHIFT AND ROTATE OPERATIONS                          | VMPU - 35              |  |  |  |  |  |

| 3.6    | BIT MANIPULATION OPERATIONS                          | VMPU - 36              |  |  |  |  |  |

| 3.7    | BINARY CODED DECIMAL OPERATIONS                      | VMPU - 37              |  |  |  |  |  |

| 3.8    | PROGRAM CONTROL OPERTIONS                            | VMPU - 37              |  |  |  |  |  |

| 3.9    | SYSTEM CONTROL OPERATIONS                            | VMPU - 38              |  |  |  |  |  |

| 3.10   | MULTIPROCESSOR OPERATIONS                            | VMPU - 40              |  |  |  |  |  |

|        |                                                      |                        |  |  |  |  |  |

|        | CEPTION PROCESSING                                   | VMPU - 41              |  |  |  |  |  |

| 4.1    | INTRODUCTION                                         | VMPU - 41              |  |  |  |  |  |

| 4.2    | PRIVILEGE STATES                                     | VMPU - 41              |  |  |  |  |  |

| 4.2.1  | Supervisor State                                     | VMPU - 42              |  |  |  |  |  |

| 4.2.2  |                                                      | VMPU - 42              |  |  |  |  |  |

| 4.2.3  |                                                      | VMPU - 43<br>VMPU - 43 |  |  |  |  |  |

| 4.2.4  | 4.2.4 Reference Classification                       |                        |  |  |  |  |  |

| 4.3    | EXCEPTION PROCESSING                                 | VMPU - 44              |  |  |  |  |  |

| 4.3.1  | Exception Vectors                                    | VMPU - 44              |  |  |  |  |  |

#### TOSHIBA

#### CONTENTS

| 4.3.3 Multiple Exceptions                    | VMPU - 47   |

|----------------------------------------------|-------------|

|                                              |             |

| 4.3.4 Exception Stack Frames                 | VMPU - 48   |

| 4.3.5 Exception Processing Sequence          | VMPU - 50   |

| 4.4 EXCEPTION PROCESSING DETAILED DISCUSSION | . VMPU - 50 |

| 4.4.1 Reset                                  | VMPU - 51   |

| 4.4.2 Interrupts                             | VMPU - 51   |

| 4.4.3 Uninitialized Interrupt                | VMPU - 52   |

| 4.4.4 Spurious Interrupt                     | VMPU - 52   |

| 4.4.5 Instruction Traps                      | VMPU - 53   |

| 4.4.6 Illegal and Unimplemented Instructions | . VMPU - 53 |

| 4.4.7 Privilege Violations                   | VMPU - 54   |

| 4.4.8 Tracing                                | VMPU - 54   |

| 4.4.9 Bus Error                              | VMPU - 55   |

| 4.4.9.1 Bus Error (TMP68000/TMP68008)        | . VMPU - 56 |

| 4.4.9.2 BUS ERROR (TMP68010)                 | VMPU - 57   |

| 4.4.10 Address Error                         | VMPU - 60   |

| 4.5 RETURN FROM EXCEPTION (TMP68010)         | . VMPU - 60 |

| 4.5.1 Determine The Stack Format             | VMPU - 60   |

| 4.5.2 Determine Data Validity                | VMPU - 61   |

| 4.5.3 Determine Data Accessibility           | VMPU - 61   |

| APPENDIX A                                   |             |

| CONDITION CODES COMPUTATION                  | . VMPU - 62 |

| A.1 INTRODUCTION                             | VMPU - 62   |

| A.2 CONDITION CODE REGISTER                  | . VMPU - 62 |

| A.3 CONDITION CODE REGISTER NOTATION         | . VMPU - 62 |

| A.4 CONDITION CODE COMPUTATION               | . VMPU - 63 |

| A.5 CONDITION TESTS                          | VMPU - 65   |

| APPENDIX B INSTRUCTION SET DETAILS           | . VMPU - 66 |

| B.1 INTRODUCTION                             | VMPU - 66   |

| B.2 ADDRESSING CATEGORIES                    | . VMPU - 66 |

| B.3 INSTRUCTION DESCRIPTION                  | . VMPU - 68 |

| B.4 OPERATION DESCRIPTION DEFINITIONS        | . VMPU - 69 |

#### TOSHIBA

| APPE           | NDIX C                                       |           |

|----------------|----------------------------------------------|-----------|

| INST           | TRUCTION FORMAT SUMMARY                      | VMPU -206 |

| C.1            | INSTRODUCTION                                | VMPU -206 |

|                |                                              |           |

| APPE           | NDIX D                                       |           |

| $\mathrm{TMP}$ | 68000 INSTRUCTION EXECUTION TIMES            | VMPU -227 |

| D.1            | INTRODUCTION                                 | VMPU -227 |

| D.2            | OPERAND EFFECTIVE ADDRESS CALCULATION TIMES  | VMPU -227 |

| D.3            | MOVE INSTRUCTION EXECUTION TIMES             | VMPU -228 |

| D.4            | STANDARD INSTRUCTION EXECUTION TIMES         | VMPU -230 |

| D.5            | IMMEDIATE INSTRUCTION EXECUTION TIMES        | VMPU -231 |

| D.6            | SINGLE OPERAND INSTRUCTION EXECUTION TIMES   | VMPU -231 |

| D.7            | SHIFT/ROTATE INSTRUCTION EXECUTION TIMES     | VMPU -232 |

| D.8            | BIT MANIPULATION INSTRUCTION EXECUTION TIMES | VMPU -233 |

| D.9            | CONDITIONAL INSTRUCTION EXECUTION TIMES      | VMPU -233 |

| D.10           | JMP, JSR, LEA, PEA, AND                      |           |

|                | MOVEM INSTRUCTION EXECUTIONTIMES             | VMPU -234 |

| D.11           | MULTI-PRECISION INSTRUCTION EXECUTION TIMES  | VMPU -234 |

| D.12           | MISCELLANEOUS INSTRUCTION EXECUTION TIMES    | VMPU -235 |

| D.13           | EXCEPTION PROCESSING EXECUTION TIMES         | VMPU236   |

|                |                                              |           |

|                | NDIX E                                       |           |

| TMF            | 68008 INSTRUCTION EXECUTION TIMES            | VMPU -237 |

| E.1            | INTRODUCTION                                 | VMPU -237 |

| E.2            | OPERAND EFFECTIVE ADDRESS CALCULATION TIMES  | VMPU -238 |

| E.3            | MOVE INSTRUCTION EXECUTION TIMES             | VMPU -239 |

| E.4            | STANDARD INSTRUCTION EXECUTION TIMES         | VMPU -240 |

| E.5            | IMMEDIATE INSTRUCTION EXECUTION TIMES        | VMPU -242 |

| E.6            | SINGLE OPERAND INSTRUCTION EXECUTION TIMES   | VMPU -243 |

| E.7            | SHIFT/ROTATE INSTRUCTION EXECUTION TIMES     | VMPU -244 |

| E.8            | BIT MANIPULATION INSTRUCTION EXECUTION TIMES | VMPU -244 |

| E.9            | CONDITIONAL INSTRUCTION EXECUTION TIMES      | VMPU -245 |

| E.10           | JMP, JSR, LEA, PEA, AND MOVEM INSTRUCTION    |           |

|                | EXECUTION TIMES                              | VMPU -246 |

| E11            | MULTI-PRECISION INSTRUCTION EXECUTION TIMES  | VMPU -247 |

| E.12           | MISCELLANEOUS INSTRUCTION EXECUTION TIMES    | VMPU -248 |

| E.13        | EXCEPTION PROCESSING EXECUTION TIMES         | VMPU -249 |

|-------------|----------------------------------------------|-----------|

| APPE        | NDIX F                                       |           |

| TMP         | 68010 INSTRUCTION EXECUTION TIMES            | VMPU -250 |

| F.1         | INTRODUCTION                                 | VMPU -250 |

| F.2         | OPERAND EFFECTIVE ADDRESS CALCULATION TIMES  | VMPU -250 |

| F.3         | MOVE INSTRUCTION EXECUTION TIMES             | VMPU -251 |

| F.4         | STANDARD INSTRUCTION EXECUTION TIMES         | VMPU -253 |

| F.5         | IMMEDIATE INSTRUCTION EXECUTION TIMES        | VMPU -254 |

| F.6         | SINGLE OPERAND INSTRUCTION EXECUTION TIMES   | VMPU -255 |

| <b>F.</b> 7 | SHIFT/ROTATE INSTRUCTION EXECUTION TIMES     | VMPU -257 |

| F.8         | BIT MANIPULATION INSTRUCTION EXECUTION TIMES | VMPU -257 |

| F.9         | CONDITIONAL INSTRUCTION EXECUTION TIMES      | VMPU -258 |

| F.10        | JMP, JSR, LEA, PEA, AND MOVEMINSTRUCTION     |           |

|             | EXECUTION TIMES                              | VMPU -259 |

| F.11        | MULTI-PRECISION INSTRUCTION EXECUTION TIMES  | VMPU -259 |

| F.12        | MISCELLANEOUS INSTRUCTION EXECUTION TIMES    | VMPU -260 |

| F.13        | EXCEPTION PROCESSING EXECUTION TIMES         | VMPU -262 |

|             | NDIV C                                       |           |

#### APPENDIX G

| TMP68010 LOOP MODE OPERATION | VMPU -263 |

|------------------------------|-----------|

|------------------------------|-----------|

#### 1. ARCHITECTURAL DESCRIPTION

#### 1.1 INTRODUCTION

The TMP68000, with a 16-bit data bus and 24-bit address bus, was only the first in a family of processors which implement a comprehensive, extensible computer architecture. It was soon followed by the TMP68008, with an 8-bit data bus and 20-bit address bus, by the TMP68010, which introduced the virtual machine aspects of the TLCS-68000 architecture.

This manual is intended to serve as a programmer's reference for both systems and applications programmers for four of the current implementations of the TLCS-68000 - the TMP68000, the TMP68008, the TMP68010. The hardware system design aspects of these processors, such as bus structure and control, are presented in the respective advance information data sheets for each device.

The TMP68000 and the TMP68008 are identical from the view of the programmer, with the exception that the TMP68000 can directly access 16 megabytes (24 bits of address) and the TMP68008 can directly access 1 megabyte (20 bits of address). The TMP68010 have much in common with the first two devices but also possess some additional instructions and registers as well as full virtual machine/memory capability. Since the processors are so similar to the programmer, only the differences are highlighted. When the TLCS-68000 is referenced, the feature described is common to all. If a particular feature is applicable only to one processor, the TMP part number will be referenced.

#### 1.2 PROGRAMMER'S MODEL

The TLCS-68000 executes instructions in one of two modes - user mode or supervisor mode. The user mode is intended to provide the execution environment for the majority of application programs. The supervisor mode allows some additional instructions and privileges and is intended for use by the operating system and other system software. See "4. EXCEPTION PROCESING" for further details.

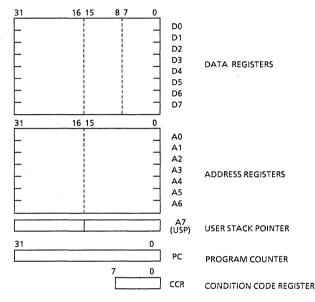

To provide for the upward compatibility of code written for a specific implementation of the TLCS-68000, the user programmer's model is common to all implementations. The user programmer's model is shown in Figure 1.1. As shown in the user programmer's model, the TLCS-68000 offers 16 32-bit general purpose registers (D0~D7, A0~A7), a 32-bit program counter, and an 8-bit condition code register. The first eight registers (D0~D7) are used as data registers for byte (8-bit), word (16-bit), and long word (32-bit) operations. The second set of seven registers (A0~A6) and the stack pointer (USP) may be used as software stack pointers and base address registers. In addition, the address registers may be used for word and long word operations. All of the 16 registers may be used as index registers.

Figure 1.1 User Programmer's Model (TMP68000/TMP68008/TMP68010)

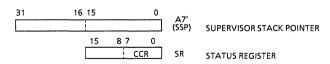

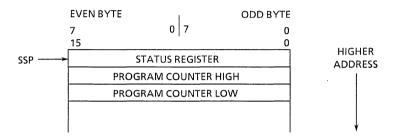

The supervisor programmer's model includes some supplementary registers in addition to the above mentioned registers. The TMP68000 and the TMP68008 contain identical supervisor mode register resources. These are shown in Figure 1.2 and include the status register (high order byte) and the supervisor stack pointer (A7').

Figure 1.2 Supervisor Programmer's Model Supplement (TMP68000/TMP68008)

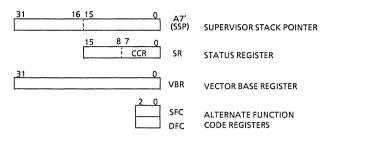

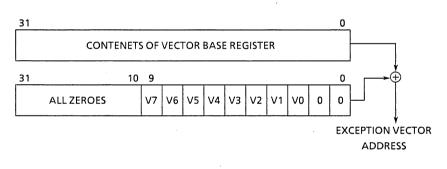

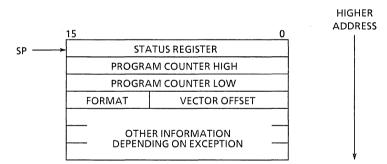

The supervisor programming model supplement of the TMP68010 is shown in Figure 1.3. In addition to the supervisor stack pointer and status register, it includes the vector base register and the alternate function code registers.

The vector base register is used to determine the location of the exception vector table in memory to support multiple vector tables. The alternate function code registers allow the supervisor to access user data space or emulate CPU space cycles.

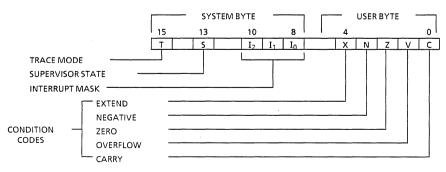

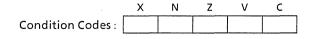

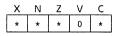

The status register, shown in Figure 1.4, contains the interrupt mask (eight levels available) as well as the condition codes: overflow (V), zero (Z), negative (N), carry(C), and extend (X). Additional status bits indicate that the processor is in a trace (T) mode and/or in a supervisor (S) state.

Five basic data types are supported. These data types are:

- Bits

- BCD Digits (4 Bits)

- Bytes (8 Bits)

- Words (16 Bits)

- Long Words (32 Bits)

In addition, operations on other data types such as memory addresses, status word data, etc. are provided for in the instruction set.

Figure 1.4 Status Register

VMPU-3

The 14 flexibe addressing modes, shown in Table 1.1, include six basic types:

- Register Direct

- Register Indirect

- Absolute

- Immediate

- Program Counter Relative

- Implied

Included in the register indirect addressing modes is the capability to do postincrementing, predecrementing, offsetting, and indexing. Program counter relative mode can also be modified via indexing and offsetting.

|                                             | Mode                                                                                                                                    | Generation                                                                                                                      |                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Data Re                                     | rect Addressing<br>gister Direct<br>Register Direct                                                                                     | EA = Dn<br>EA = An                                                                                                              |                                                                                                                                                                                                                                                                                                   |  |  |  |

| Absolute d<br>Absolut<br>Absolut            |                                                                                                                                         | EA = (Next Word)<br>EA = (Next Two Words)                                                                                       |                                                                                                                                                                                                                                                                                                   |  |  |  |

| Relative                                    | ounter Relative Addre<br>with Offset<br>with Index and Offse                                                                            | EA = (PC) + d16<br>EA = (PC) + (Xn) + d8                                                                                        |                                                                                                                                                                                                                                                                                                   |  |  |  |

| Register<br>Postincr<br>Predecr<br>Register | direct Addresssing<br>r Indirect<br>rement Register Indir<br>ement Register Indire<br>r Indirect with Offset<br>I Register Indirect wit | EA = (An)<br>$EA = (An), An \leftarrow An + N$<br>$An \leftarrow An - N, EA = (An)$<br>EA = (An) + d16<br>EA = (An) + (Xn) + d8 |                                                                                                                                                                                                                                                                                                   |  |  |  |

| Immedi                                      | Data Addressing<br>ate<br>nmediate                                                                                                      |                                                                                                                                 | DATA = Next Word(s)<br>Inherent Data                                                                                                                                                                                                                                                              |  |  |  |

| Implied Ad<br>Implied                       | dressing<br>Register                                                                                                                    |                                                                                                                                 | EA = SR, USP, SSP, PC,<br>VBR, SFC, DFC                                                                                                                                                                                                                                                           |  |  |  |

| An = Dn =                                   | Effective Address<br>Address Register<br>Data Register<br>Address or Data Registe<br>used as Index Register                             | SR = Status Register<br>PC = Program Counter<br>( ) = Contents of<br>PT                                                         | <ul> <li>d8 = 8-bit Offset (Displacement)</li> <li>d16 = 16-bit Offset (Displacement)</li> <li>N = 1 for byte, 2 for word, and 4 for long word</li> <li>If An is the stack pointer and the operand size is byte, N = 2 to keep the stack pointer word boundary.</li> <li>← =: Replaces</li> </ul> |  |  |  |

Table 1.1 Data Addressing Modes

The TLCS-68000 instruction set is shown in Table 1.2. Some additional instructions are variations or subsets of these and they appear in Table 1.3. Special emphasis has been given to the instruction set's support of structured high-level languages to facilitate ease of programming. Each instruction, with a few exceptions, operates on bytes, words, and long words and most instructions can use any of the 14 addressing modes. Combining instruction types, data types, and addressing modes, over 1000 useful instructions are provided. These instructions include signed and unsigned multiply and divide, "quick" arithmetic operations, BCD arithmetic, and expanded operations (through traps). Additionally, its high-symmetric, proprietary microcoded structure provides a sound, flexible base for the future.

#### 1.3 SOFTWARE DEVELOPMENT

Many innovative features have been incorporated to make programming easier, faster, and more reliable.

#### 1.3.1 Consistent Structure

The highly regular structure of the TLCS-68000 greatly simplifies the effort required to write programs in assembly language as well as high-level languages. Operations on integer data in registers and memory are independent of the data. Separate special instructions that operate on byte (8 bit), word (16 bit), and long word (32 bit) integers are not necessary. The programmer need only remember one mnemonic for each type of operation and then specify data size, source addressing mode, and destination addressing mode. This has helped keep the total number of instructions small.

The dual operand nature of many of the instructions significantly increases the flexibility and power of the TLCS-68000. Consistency is again maintained since all data registers and memory locations may be either a source or destination for most operations on integer data.

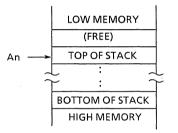

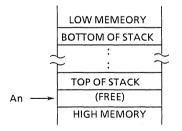

The addressing modes have been kept simple without sacrificing efficiency. All fourteen addressing modes operate consistently and are independent of the instruction operation itself. Additionally, all address registers may be used for the direct, register indirect, and indexed addressing modes (immediate, program counter relative, and absolute addressing by definition do not use address registers). For increased flexibility, any address or data register may be used as an index register. Address register consistency is maintained for stacking operations since any of the eight address registers may be utilized as user program stack pointers with the register indirect postincrement/predecrement addressing modes. Address register A7, however, is a special register that, in addition to is normal addressing capability, functions as the system stack pointer for stacking the program counter for subroutine calls as well as stacking the program counter and status register for traps and interrupts (while in the supervisor state).

| Mnemonic | Description                        |

|----------|------------------------------------|

| ABCD*    | Add Decimal with Extned            |

| ADD*     | Add                                |

| AND*     | Logical AND                        |

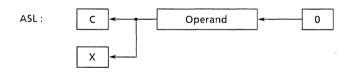

| ASL*     | Arithmetic Shift Left              |

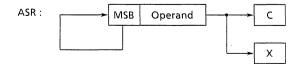

| ASR*     | Arithmetic Shift Right             |

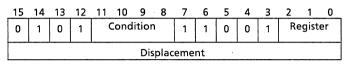

| BCC      | Branch Conditionally               |

| BCHG     | Bit Test and Change                |

| BCLR     | Bit Test and Clear                 |

| BKPT     | Breakpoint                         |

| BRA      | Branch Always                      |

| BSET     | Bit Test and Set                   |

| BSR      | Branch to Subroutine               |

| BTST     | Bit Test                           |

| CHK      | Check Register Against Bounds      |

| CLR*     | Clear Operand                      |

| CMP*     | Compare                            |

| DBcc     | Decrement and Branch Conditionally |

| DIVS     | Signed Divide                      |

| DIVU     | Unsigend Divide                    |

| EOR*     | Exclusive OR                       |

| EXG      | Exchange Registers                 |

| EXT      | Sign Extend                        |

| JMP      | Jump                               |

| JSR      | Jump to Subroutine                 |

| LEA      | Load Effective Address             |

| LINK     | Link Stack                         |

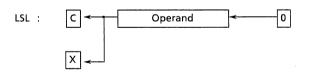

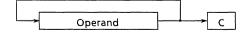

| LSL*     | Logical Shift Left                 |

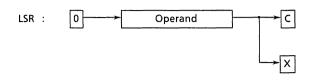

| LSR*     | Logical Shift Right                |

Table 1.2 Instruction Set Summary (1/2)

\*: These instructions available in loop mode on TMP68010. See "APPENDIX G TMP68010 LOOP MODE OPERATIONS".

| Mnemonic | Description                  |

|----------|------------------------------|

| MOVE*    | Move Source to Destination   |

| MULS     | Signed Multiply              |

| MULU     | Unsigned Multiply            |

| NBCD*    | Negate Decimal with Extend   |

| NEG*     | Negate                       |

| NOP      | No Operation                 |

| NOT*     | One's Complement             |

| OR*      | logical OR                   |

| PEA      | Push Effective Address       |

| RESET    | Reset External Devices       |

| ROL*     | Rotate Left without Extend   |

| ROR*     | Rotate Right without Extend  |

| ROXL*    | Rotate Left with Extend      |

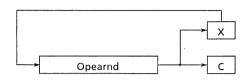

| ROXR*    | Rotate Right with Extend     |

| RTD      | Return and Deallocate        |

| RTE      | Return from Exception        |

| RTR      | Return and Restore           |

| RTS      | Return from Subroutine       |

| SBCD*    | Subtract Decimal with Extend |

| Scc      | Set Conditional              |

| STOP     | Stop                         |

| SUB*     | Subtract                     |

| SWAP     | Swap Data Register Halves    |

| TAS      | Test and Set Operand         |

| TRAP     | Тгар                         |

| TRAPV    | Trap on Overflow             |

| TST*     | Test                         |

| UNLK     | Unlink                       |

Table 1.2 Instruction Set Summary (2/2)

· · · ·

I

I

| Instruction<br>Type | Variation                                                                                                                              | Description                                                                                                                                                                                                                                                                                                   |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD                 | ADD*<br>ADDA*<br>ADDQ<br>ADDI<br>ADDX*                                                                                                 | Add<br>Add Address<br>Add Quick<br>Add Immediate<br>Add with extend                                                                                                                                                                                                                                           |

| AND                 | AND*<br>ANDI<br>ANDI to CCR<br>ANDI to SR                                                                                              | Logical AND<br>AND Immediate<br>AND Immediate to Condition Codes<br>AND Immediate to Status Regitster                                                                                                                                                                                                         |

| СМР                 | CMP*<br>CMPA*<br>CMPM*<br>CMPI                                                                                                         | Compare<br>Compare Address<br>Compare Memory<br>Compare Immediate                                                                                                                                                                                                                                             |

| EOR                 | EOR*<br>EORI<br>EORI to CCR<br>EORI to SR                                                                                              | Exclusive OR<br>Exclusive OR Immediate<br>Exclusive OR Immediate to Condition Codes<br>Exclusive OR Immediate to Status Register                                                                                                                                                                              |

| MOVE                | MOVE*<br>MOVEA*<br>MOVEC<br>MOVEM<br>MOVEP<br>MOVEQ<br>MOVES<br>MOVE from SR<br>MOVE to SR<br>MOVE to SR<br>MOVE to CCR<br>MOVE to CCR | Move Source to Destination<br>Move Address<br>Move Control Register<br>Move Multiple Registers<br>Move Peripheral Data<br>Move Quick<br>Move Alternate Address Space<br>Move from Status Register<br>Move to Status Register<br>Move to Condition Codes<br>Move to Condition Codes<br>Move User Stack Pointer |

| NEG                 | NEG*<br>NEGX*                                                                                                                          | Negate<br>Negate with Extend                                                                                                                                                                                                                                                                                  |

| OR                  | OR*<br>ORI<br>ORI to CCR<br>ORI to SR                                                                                                  | Logical OR<br>OR Immediate<br>OR Immediate to Condition Codes<br>OR Immediate to Status Register                                                                                                                                                                                                              |

| SUB                 | SUB*<br>SUBA*<br>SUBI<br>SUBQ<br>SUBX*                                                                                                 | Subtract<br>Subtract Addres<br>Subtract Immediate<br>Subtract Quick<br>Subtract with Extend                                                                                                                                                                                                                   |

Table 1.3

Variations of Instruction Types

\* These instructions available in loop mode on TMP68010. See "APPENDIX G TMP68010 LOOP MODE OPERATIONS".

#### 1.3.2 Structured Modular Programming

The art of programming microprocessors has evolved rapidly in the past few years. Numerous advanced techniques have been developed to allow easier, more consistent and reliable generation of software. In general, these techniques require that the programmer be more disciplined in observing a defined programming structure such as modular programming. Modular programming allows a required function or process to be broken down in short modules or subroutines that are concisely defined and easily programmed and tested. Such a technique is greatly simplified by the availability of advanced structured assemblers and block structured high-level languages such as Pascal. Such concepts are virtually useless, however, unless parameters are easily transferred between and within software modules that operate on a reentrant and recursive basis. (To be reentrant a routine must be usable by interrupt and noninterrupt driven programs without the loss of data. A recursive routine is one that may call or use itself.) The TLCS-68000 provides the necessary architectural features to allow efficient reentrant modular programming. The LINK and UNLK instructions reduce subroutine call overhead in two complementary instructions by allowing the manipulation of linked lists of data areas on the stack. The MOVEM (Move Multiple Register) instruction also reduces subroutine call programming overhead. This allows moving, via an effective address, multiple registers that are specified by the programmer. Sixteen software trap vector are provided with the TRAP instruction and are useful in operating system call routines or user generated macro routines. Other instructions that support modern structured programming techniques are PEA (Push Effective Address), LEA (Load Effective Address), RTR (Return and Restore), RTE (Return from Exception) as well as JSR (Jump to Subroutine), BSR (Branch to Subroutine), and RTS (Return from Subroutine).

The powerful vectored priority interrupt structure of the microprocessor allows straight-foward generation of reentrant modular input/output routines. Seven maskable levels of priority with 192 vector locations and seven autovector locations provide maximum flexibility for I/O control (a total of 255 vector locations are available for interrupts, hardware traps, and software traps).

#### 1.3.3 Improved Software Testability

The TLCS-68000 incorporates several features that reduce the chance for errors. Some of these features, such as consistent architecture and the structured modular programming capability, have already been discussed.

Of major importance to the system programmer are features that have been incorporated specifically to detect the occurrence of programming errors or bugs. Several hardware traps, provided to indicate abnormal internal conditions, detect the following error conditions:

- Word Access with an Odd Address

- Illegal Instructions

- Unimplemented Instructions

- Illegal Memory Access (Bus Error)

- Divide by Zero

- Overflow Condition Code (Separate Instruction TRAPV)

- Register Out of Bounds (CHK Instruction)

- Spurious Interrupt

Additionally, the sixteen software TRAP instructions may utilized by the programmer to provide applications-oriented error detection or correction routines.

An additional error detection tool is the CHK (Check Register Against Bounds) instruction used for array bound checking by verifying that a data register contains a valid subscript. A trap occurs if the register contents are negative or greater than a limit.

Finally, the TLCS-68000 includes a facility that allows instruction-by-instruction tracing of a program being debugged. This trace mode results in a trap being made to a tracing routine after each instruction executed. The trace mode is available to the programmer when the microprocessor is in the supervisor state as well as the user state but may only be entered while in the supervisor state. The supervisor/user states provide an additional degree of error protection for the microprocessor by allowing memory protection of selected areas of memory when an external memory management device is used.

#### 1.4 VIRTUAL MEMORY/MACHINE CONCEPTS

The TMP68010 introduced the virtual memory/machine concept of the TLCS-68000 architecture.

In most systems using the TMP68010 as the central processor, only a franction of the 16 megabyte address space will actually contain physical memory. However, by using virtual memory techniques the system can be made to appear to the user to have 16 megabytes of physical memory available. These techniqes have been used for several years in large mainframe computers and more recently in minicomputers and now, with the TMP68010, can be fully supported in microprocessor-based systems. In a virtual memory system, a user program can be written as though it has a large amount of memory available to it when only a small amount of memory is physically present in the system. In a similar fashion, a system can be designed in such a manner as to allow user programs to access other types of devices that are not physically present in the system such as type drives, disk drives, printers, or CRTs. With proper software emulation, a physical system can be made to appear to a user program as any other computer system and the program may be given full access to all of the resources of that emulated system. Such an emulated system is called a virtual machine.

#### 1.4.1 Virtual Memory

The basic mechanism for supporting virtual memory in computers is to provide only a limited amount of high-speed physical memory that can be accessed directly by the processor while maintaining an image of a much larger "virtual" memory on secondary storage devices such as large capacity disk drives. When the processor attempts to access a location in the virtual memory map that is not currently residing in physical memory (referred to as a page fault), the access to that location is temporarily suspended while the necessary data is fetched from the secondary storage and placed in physical memory; the suspended access is then completed. The TMP68010 provides hardware support for virtual memory with the capability of suspending an instruction's execution when a bus error is signaled and then completing the instruction after the physical memory has been updated as necessary.

The TMP68010 uses instruction continuation rather than instruction restart to support virtual memory. With instruction restart, the processor must remember the exact state of the system before each instruction is started in order to restore that state if a page fault occurs during its execution. Then, after the page fault has been repaired, the entire instruction that cauesd the fault is reexecuted. With instruction continuation, when a page fault occurs the processor stores its internal state and then after the page fault is repaired, restores that internal state and continues execution of the instruction. In order for the TMP68010 to utilize instruction continuation, it stores its internal state on the supervisor stack when a bus cycle is terminated with a bus error signal. It then loads the program counter from vector table entry number two (offset \$008) and resumes program execution at that new address. When the bus error exception handler routine has completed execution, an RTE instruction is executed which reloads the TMP68010 with the internal state stored on the stack, re-runs the faulted bus cycle, and continues the suspended instruction. Instruction continuation has the additional advantage of allowing hardware support for virtual I/O devices. Since virtual registers may be simulated in the memory map, an access to such a register will cause a fault and the function of the register can be emulated by software.

#### 1.4.2 Virtual Machine

One typical use for a virtual machine system is in the development of software such as an operating system for another machine with hardware also under development and not available for programming use. In such a system, the governing operating system emulates the hardware of the new system and allows the operating system to be executed and debugged as though it were running on the new hardware. Since the new operating system is controlled by the governing operating system, the new one must execute at a lower privilege level than the governing operating system, so that any attempts by the new operating system to use virtual resources that are not physically present, and should be emulated, will be trapped by the governing operating system and handled in software. In the TMP68010, a virtual machine may be fully supported by running the new operating system in the user mode and the governing operating system in the supervisor mode so that any attempts to access supervisor resources or execute privileged instructions by the new operating system will cause a trap to the governing operating system.

In order to fully support a virtual machine, the TMP68010 must protect the supervisor resources from access by user programs. The one supervisor resource that is not fully protected in the TMP68000 is the system byte of the status register. In the TMP68000 and TMP68008, the MOVE from SR instruction allows user programs to test the S bit (in addition to the T bit and interrupt mask) and thus determine that they are running in the user mode. For full virtual machine support, a new operating system must not be aware of the fact that it is running in the user mode and thus should not be allowed to access the S bit. For this reason, the MOVE from SR instruction has been added to allow user program unhindered access to the condition codes. By making the MOVE from SR instruction privileged, when the new operating system attempts to access the S bit, a trap to the governing operating system will occur, and the SR image passed to the new operating system by the governing operating system will have the S bit set.

#### 2. DATA ORGANIZATION AND ADDRESSING CAPABILITIES

#### 2.1 INTRODUCTION

This section describes the data organization and addressing capabilities of the TLCS-68000 architecture.

#### 2.2 OPERAND SIZE

Operand sizes are defined as follows: a byte equals 8 bits, a word equals 16 bits, and a long word equals 32 bits. The operand size for each instruction is either explicitly encoded in the instruction or implicitly defined by the instruction operation. All explicit instructions support byte, word, or long word operands. Implicit instructions support some subset of all three sizes.

#### 2.3 DATA ORGANIZATION IN REGISTERS

The eight data registers support data operands of 1, 8, 16, or 32 bits. The seven address registers together with the active stack pointer support address operands of 32 bits.

#### 2.3.1 Data Registers

Each data register is 32 bits wide. Byte operands occupy the low order 8 bits, word operands the low order 16 bits, and long word operands the entire 32 bits. The least significant bit is addressed as bit zero; the most significant bit is addressed as bit 31.

When a data register is used as either a source or destination operand, only the appropriate low order portion is changed; the remaining high-order portion is neither used nor changed.

#### 2.3.2 Address Registers

Each address register and the stack pointer is 32-bits wide and holds a full 32 bit address. Address registers do not support byte sized operands. Therefore, when an address register is used as a source operand, either the low order word or the entire long word operand is used depending upon the operation size. When an address register is used as the destination operand, the entire register is affected regardless of the operation size. If the operation size is word, any other operands are sign extended to 32 bits before the operation is performed.

#### 2.4 DATA ORGANIZATION IN MEMORY

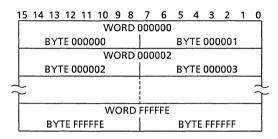

Bytes are individually addressable with the high order byte having an even address the same as the word as shown in Figure 2.1. The low order byte has an odd address that is one count higher than the word address. Instructions and multibyte data are accessed only on word (even byte) boundaries. If a long word datum is located at address n(neven), then the second word of that datum is located at address n + 2.

Figure 2.1 Word Organization in Memory

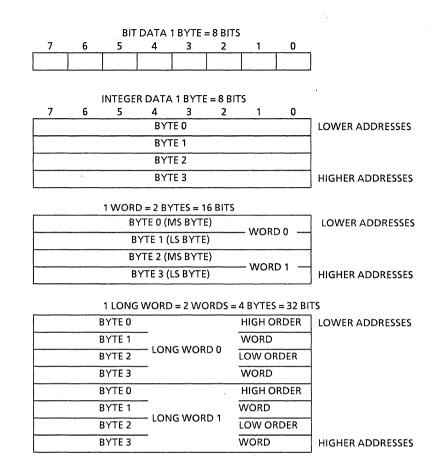

The data types supported by the TLCS-68000 are: bit data, integer data of 8, 16, and 32-bit addresses, and binary coded decimal data. Each of these data types is put in memory as shown in Figure 2.2. The numbers indicate the order in which the data would be accessed from the processor. For convenience, the organization of data in memory for the TMP68008 is shown in Figure 2-3. The appearance to the programmer, however, is identical to the TMP68000, and TMP68010.

|                     |    |          |       |       |         |                   | T DA<br>TE = | TA<br>8 BIT   | 5   |     |        |          |       |       |    |

|---------------------|----|----------|-------|-------|---------|-------------------|--------------|---------------|-----|-----|--------|----------|-------|-------|----|

|                     |    |          | 7     | 6     | 5       | 4                 |              | 3             | -   | 2   | 1      | 0        | _     |       |    |

|                     |    |          |       |       |         |                   |              |               |     |     |        |          |       |       |    |

|                     |    |          |       |       |         | EGER [<br>YTE = 8 |              |               |     |     |        |          | _     |       |    |

| 15 1                | 4  | 13       | 12    | 11    | 10      | 9 8               | 3            | 7             | 6   | 5   | 4      | 3        | 2     | 1     | 0  |

| MSB                 |    |          | BYT   | E 0   |         | LS                | B            |               | _   |     | BYT    | E 1      |       |       |    |

|                     |    |          | BYT   | E 2   |         |                   |              |               |     |     | BYT    | E 3      |       |       |    |

|                     |    |          |       |       | 1 WC    | DRD = '           | 16 BI        | TS            |     |     |        |          |       |       |    |

| 15 1                | 4  | 13       | 12    | 11    | 10      | 9 8               | 8            | 7             | 6   | 5   | 4      | 3        | 2     | 1     | 0  |

| MSB                 |    |          |       |       |         | N                 | /ORE         | 0             |     |     |        |          |       | L     | SB |

|                     |    |          |       |       |         | W                 | ORD          | ) 1           |     |     |        |          |       |       |    |

|                     |    |          |       |       |         | W                 | ORD          | 2             |     |     |        |          |       |       |    |

| EV                  | ΕN | BYTES    |       |       |         |                   |              |               |     |     |        | (        | DDD B | YTES  |    |

| 76                  | 5  | 5        | 4     | 3     | 2       | 1 (               | 5            | 7             | 6   | 5   | 4      | 3        | 2     | 1     | 0  |

|                     |    |          |       |       | 1 LON   |                   |              |               |     |     |        |          |       |       |    |

|                     | 4  | 13       | 12    | 11    | 10      | 9 8               | B            | 7             | 6   | 5   | 4      | 3        | 2     | 1     |    |

| MSB                 |    | LONG     | WOR   | DO    |         |                   |              | HOR           |     |     |        |          |       |       |    |

|                     |    |          |       |       |         |                   | LOV          | VORI          | DER |     |        |          |       | L     | SB |

|                     |    | LONG     |       |       |         |                   |              |               |     |     |        |          |       |       |    |

| I                   |    |          |       |       |         | DDRES             |              | RITS          |     |     |        |          |       |       |    |

| 15 1                | 4  | 13       | 12    | 11    | 10      |                   |              | 7             | 6   | 5   | 4      | 3        | 2     | 1     | 0  |

| MSB                 |    |          |       |       |         |                   | HIG          | H OR          | DER |     |        | 11 and 1 |       |       |    |

| +                   |    | ADI      | ORESS | 50    |         |                   | LOV          | VOR           | DER |     |        |          |       | <br>I | SB |

|                     |    | ADI      | ORESS | 5 1   |         |                   |              |               |     |     |        |          |       |       |    |

|                     |    | ADI      | ORESS | 52    |         |                   |              |               |     |     |        |          |       |       |    |

| MSB = M<br>LSB = LE |    |          |       |       | 2 BINAI | RY COI            |              | IMAL<br>DECII |     |     | TS = 1 | BYTE     |       |       |    |

| 15 1                | 4  | 13       | 12    | 11    | 10      | 9                 | 8            | 7             | 6   | 5   | 4      | 3        | 2     | 1     | 0  |

| MSD                 |    | BCDO     |       |       | BCD1    | L                 | SD           |               | B   | CD2 |        |          | BCD   | )3    |    |

|                     |    | BCD4     |       |       | BCD5    |                   |              |               | B   | CD6 |        |          | BCD   | )7    |    |

| MSD = M             | OS | T SIGNIF | ICANT | DIGIT |         |                   |              |               |     |     |        |          |       |       |    |

MSD = MOST SIGNIFICANT DIGIT LSD = LEAST SIGNIFICANT DIGIT

#### Figure 2.2 Data Organization In Memory

Figure 2.3 Memory Data Organization of the TMP68008

#### 2.5 ADDRESSING

Instructions for the TLCS-68000 contain two kinds of information: the type of function to be performed and the location of the operand(s) on which to perform that function. The methods used to locate (address) the operand(s) are explained in the following paragraphs.

Instructions specify an operand location in one of three ways:

| • | Register Specification | - | the number of the register is given in the register field of the instruction. |

|---|------------------------|---|-------------------------------------------------------------------------------|

|   | Effective Address      |   | use of the different effective address modes.                                 |

• Implicit Reference - the definition of certain instructions implies the use of specific registers.

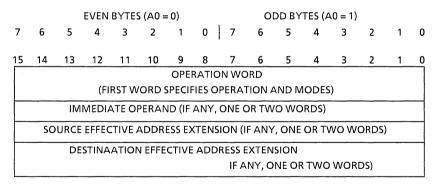

#### 2.6 INSTRUCTION FORMAT

Instruction are from one to five words in length as shown in Figure 2.4. The length of the instruction and the operation to be performed is specified by the first word of the instruction which is called the operation word. The remaining words further specify the operands. These words are either immediate operands or extensions to the effective addres mode specified in the operation word.

Figure 2.4 Instruction Format

#### 2.7 PROGRAM/DATA REFERENCES

The TLCS-68000 separates memory references into two classes: program references and data references. Program references, as the name implies, are references to that section of memory that contains the program being executed. Data references refer to that section of memory that contains data. Generally, operand reads are from the data space. All operand writes are to the data space.

#### 2.8 <u>REGISTER NOTATION</u>

Appendix B contains a description of each instruction operation and identifies the registers using the following mnemonics:

- An Address Register (n specifies the register number)

- Dn Data Register (n specifies the register number)

- Xn Any Register, Address or Data (n specifies the register number)

- PC Program Counter

- SR Status Register

- CCR Condition Code Half of the Status Register

- SP The Active Stack Pointer (either user or supervisor)

- USP User Stack Pointer

- SSP Supervisor Stack Pointer

- d8 8-bit Displacement Value

- d16 16-bit Displacement Value

- disp Displacement Value (d8 or d16)

- N Operand Size in Bytes (1, 2, 4)

- SFC, DFC Source/Destination Function Code Register

- VBR Vector Base Register

#### 2.9 ADDRESS REGISTER INDIRECT NOTATION

When an address register is used to point to a memory location, the addressing mode is called address register indirect. The term indirect is used because the operation of the instruction is not directed to the address itself, but to the memory location pointed to by the address register. The descriptive symbol for the indirect mode is an address register designation in parenthesis, i. e., (An).

#### 2.10 <u>REGISTER SPECIFICATION</u>

The register field within an instruction specifies the register to be used. Other fields within the instruction specify whether the register selected is an address or data register and how the register is to be used.

#### 2.11 EFFECTIVE ADDRESS

Most instructions specify the location of an operand by using the effective address field in the operation word. For example, Figure 2.5 shows the general format of the single effective address instruction operation word. The effective address is composed of two 3-bit fields: the mode field and the register field. The value in the mode field selects the different address modes. The register field contains the number of a register. The effective address field may require additional information to fully specify the operand. This additional information, called the effective address extension, is contained in a following word or words and is considered part of the instruction as shown in Figure 2.4. The effective address modes are grouped into three categories: register direct, memory addressing, and special.

|    |    | E١ | /EN B` | ΥTE |    |   |   | 1 | 0 | DD BYT | E   |          |        |       |     | I |

|----|----|----|--------|-----|----|---|---|---|---|--------|-----|----------|--------|-------|-----|---|

| 7  | 6  | 5  | 4      | 3   | 2  | 1 | 0 | 7 | 6 | 5      | 4   | 3        | 2      | 1     | 0   | 1 |

| 15 | 14 | 13 | 12     | 11  | 10 | 9 | 8 | 7 | 6 | . 5    | 4   | 3        | 2      | 1     | 0   |   |

| ×  | ×  | ×  | ×      | ×   | ×  | × | × | × | × | MODE   | EFF | ECTIVE A | DDRESS | REGIS | TER |   |

Figure 2.5 Single-Effective-Address-Instruction Operation - General Format

2.11.1 Register Direct Modes

These effective addressing modes specify that the operand is in one of the 16 multifunction registers.

#### 2.11.1.1 Data Register Direct

The operand is in the data register specified by the effective address register field.

| GENERATION :       | EA = Dn |                  |         |   |

|--------------------|---------|------------------|---------|---|

| ASSEMBLER SYNTAX : | Dn      |                  |         |   |

| MODE :             | 000     |                  | 31      | 0 |

| REGISTER :         | n       | DATA REGISTER Dn | OPERAND |   |

#### 2.11.1.2 Address Register Direct

The operand is in the address register specified by the effective address register field.

| GENERATION :       | EA = An |                     |         |   |

|--------------------|---------|---------------------|---------|---|

| ASSEMBLER SYNTAX : | An      |                     |         |   |

| MODE :             | 001     |                     | 31      | 0 |

| REGISTER :         | n       | ADDRESS REGISTER An | OPERAND |   |

#### 2.11.2 Memory Address Modes

These effective addressing modes specify that the operand is in memory and provide the sepcific address of the operand.

2.11.2.1 Address Register Indirect

The address of the operand is in the address register specified by the register field. The reference is classified as a data reference with the exception of the jump and jump to subroutine instructions.

| GENERATION :<br>ASSEMBLER SYNTAX : | EA = (An)<br>(An) |                     |                        |

|------------------------------------|-------------------|---------------------|------------------------|

| MODE :                             | 010               |                     |                        |

| REGISTER :                         | n                 | ADDRESS REGISTER An | 31 0<br>MEMORY ADDRESS |

|                                    |                   | MEMORY ADDRESS      | OPERAND                |

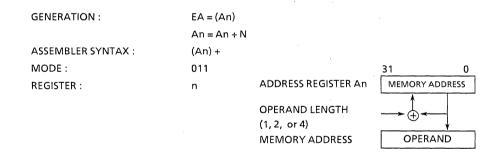

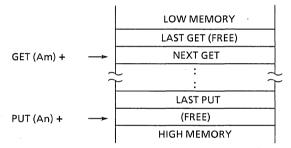

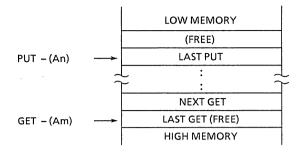

2.11.2.2 Address Register Indirect with Postincrement

The address of the operand is in the address register specified by the register field. After the operand address is used, it is incremented by one, two, or four depending upon whether the size of the operand is byte, word, or long word. If the address register is the stack pointer and the operand size is byte, the address is incremented by two rather than one to keep the stack pointer on a word boundary. The reference is classified as a data reference.

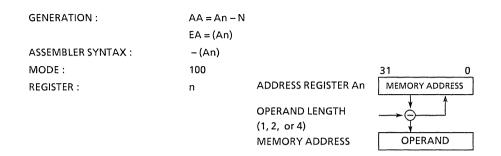

#### 2.11.2.3 Address Register Indirect with Predecrement

The address of the operand is in the address register specified by the register field. Before the operand address is used, it is decremented by one, two, or four depending upon whether the operand size is byte, word, or long word. If the address register is the stack pointer and the operand size is byte, the address is decremented by two rather than one to keep the stack pointer on a word boundary. The reference is classified as a data reference.

1

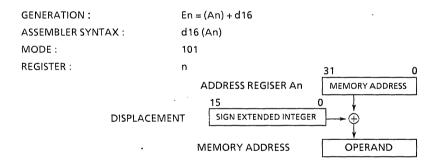

#### 2.11.2.4 Address Register Indirect with Displacement

This address mode requires one word of extension. The address of the operand is the sum of the address in the address register and the sign-extended 16-bit displacement integer in the extension word. The reference is classified as a data reference with the exception of the jump and jump to subroutine instructions.

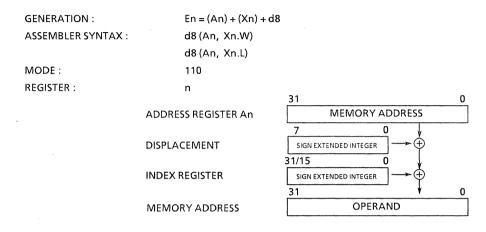

#### 2.11.2.5 Address Register Inderect with Index

This address mode requires one word of extension formatted as shown below.

|     |                      | E١                         | /EN B`             | YTE                                |    |                                   | ODD BYTE        |      |            |         |        |        |   |   |   |

|-----|----------------------|----------------------------|--------------------|------------------------------------|----|-----------------------------------|-----------------|------|------------|---------|--------|--------|---|---|---|

| 7   | 6                    | 5                          | 4                  | 3                                  | 2  | 1                                 | 0               | 7    | 6          | 5       | 4      | 3      | 2 | 1 | 0 |

| 15  | 14                   | 13                         | 12                 | 11                                 | 10 | 9                                 | 8               | 7    | 6          | 5       | 4      | 3      | 2 | 1 | 0 |

| D/A | D/A REGISTER W/L 0 0 |                            |                    |                                    |    | 0 DISPLACEMENT INTEGER            |                 |      |            |         |        |        |   |   |   |

|     |                      | Bit 19<br>Bit 14<br>Bit 17 | 0 -<br>1 -<br>4~12 | Data<br>Add<br>– I<br>Inde<br>Sigr |    | ster<br>egiste<br>regist<br>nded, | er nur<br>Iow c | nber | ntege<br>r | r in in | dex re | gister |   |   |   |

The address of the operand is the sum of the address in the address register, the signextended displacement integer in the low order eight bits of the extension word, and the contents of the index register. The reference is classified as a data reference with the exception of the jump and jump to subroutine instructions. The size of the index register does not affect the execution time of the instructions.

2.11.3 Special Address Modes

The special address modes use the effective address register field to specify the special addressing mode instead of a register number.

#### 2.11.3.1 Absolute Short Address

This address mode requires one word of extension. The address of the operand is in the extension word. The 16-bit address is sign extended before it is used. The reference is classified as a reference with the exception of the jump and jump to subroutine instructions.

| GENERATION :       | EA GIVEN       |                              |

|--------------------|----------------|------------------------------|

| ASSEMBLER SYNTAX : | Abs.W          |                              |

| MODE :             | 111            |                              |

| REGISTER :         | 000            |                              |

|                    |                | 15 0                         |

|                    | EXTENSION      | SIGN-EXTENDED MEMORY ADDRESS |

|                    | WORD           |                              |

|                    | MEMORY ADDRESS | OPERAND                      |

|                    | WORD           |                              |

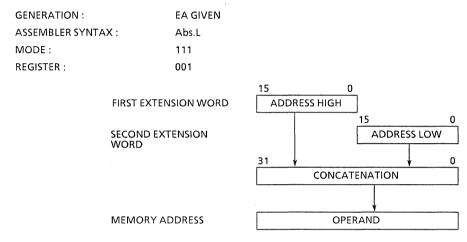

#### 2.11.3.2 Absolute Long Address

The address mode requires two words of extension. The address of the operand is developed by the concatenation of the extension words. The high-order part of the address is the first extension word; the low order part of the address is the second extension word. The reference is classified as a data reference with the exception of the jump and jump to subroutine instructions.

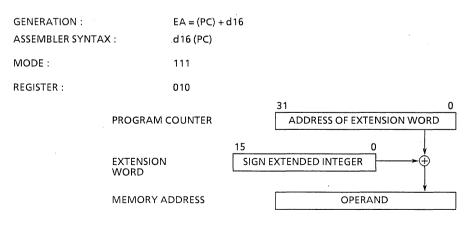

#### 2.11.3.3 Program Counter with Displacement

This address mode requires one word of extension. The address of the operand is the sum of the address in the program counter and the sign-extended 16-bit displacement integer in the extension word. The value in the program counter is the address of the extension word. The reference is classified as a program reference.

## 2.11.3.4 Program Counter with Index

This address mode requires one word of extension formatted as shown below.

| I | EVEN BYTE                                                                                                                                                                                                                                        |    |    |    |    |    |   |   | ł | OD | D BYI | E    |        |      |   |   |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|----|---|---|---|----|-------|------|--------|------|---|---|

|   | 7                                                                                                                                                                                                                                                | 6  | 5  | 4  | 3  | 2  | 1 | 0 | 7 | 6  | 5     | 4    | 3      | 2    | 1 | 0 |

|   | 15                                                                                                                                                                                                                                               | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6  | 5     | 4    | 3      | 2    | 1 | 0 |

|   | D/A REGISTER W/L 0 0                                                                                                                                                                                                                             |    |    |    |    |    | 0 | 0 |   | DI | SPLAC | EMEN | NT INT | EGER |   |   |

|   | Bit 15 – Index register indicator<br>0 – Data register<br>1 – Address register<br>Bit 14 through 12 – Index register number<br>Bit 11 – Index size<br>0 – Sign-extended, low order integer in index register<br>1 – Long value in index register |    |    |    |    |    |   |   |   |    |       |      |        |      |   |   |

The address is the sum of the address in the program counter, the sign-extended displacement integer in the lower eight bits of the extension word, and the contents of the index register. The value in the program counter is the address of the extension word. This reference is classified as a program reference. The size of the index register does not affect the execution time of the instruction.

| GENERATION :       | En = (PC) + (Xn) + d8 |                                                                                                                             |

|--------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| ASSEMBLER SYNTAX : | d8 (PC, Xn.W)         |                                                                                                                             |

|                    | d8 (PC, Xn.L)         |                                                                                                                             |

| MODE :             | 111                   |                                                                                                                             |

| REGISTER :         | 011                   |                                                                                                                             |

|                    |                       | 31 0                                                                                                                        |

|                    | PROGRAM COUNTER       | MEMORY ADDRESS                                                                                                              |

|                    | EXTENSION WORD        | 7 0<br>SIGN EXTENDED INTEGER                                                                                                |

|                    | INDEX REGISTER        | $\begin{array}{ccc} 31/15 & 0 \\ \hline \\ \hline \\ \text{SIGN EXTENDED INTEGER} \\ 31 &                                 $ |

|                    | MEMORY ADDRESS        | OPERAND                                                                                                                     |

|                    |                       |                                                                                                                             |

#### 2.11.3.5 Immediate Data

This address mode requires either one or two words of extension depending on the size of the operation.

Byte Operation - operand is low order byte of extension word

Word Operation - operand is extension word

Long Word Operation - operand is in the two extension words, high order 16-bits are in the first extension word, low order 16 bits are in the second extension word.

|                    |                 | I |

|--------------------|-----------------|---|

| GENERATION :       | OPERAND GIVEN   | I |

| ASSEMBLER SYNTAX : | # <data></data> | I |

| MODE :             | 111             |   |

| REGISTER :         | 100             |   |

|                    |                 | 1 |

The extension word formats are shown below:

| EVEN BYTE |           |    |    |    |    |   |       | ł  | OD | D BY1 | ΓE  |   |   |   |   |

|-----------|-----------|----|----|----|----|---|-------|----|----|-------|-----|---|---|---|---|

| 7         | 6         | 5  | 4  | 3  | 2  | 1 | 0     | 7  | 6  | 5     | 4   | 3 | 2 | 1 | 0 |

| 15        | 14        | 13 | 12 | 11 | 10 | 9 | 8     | 7  | 6  | 5     | 4   | 3 | 2 | 1 | 0 |

| 0         | 0         | 0  | 0  | 0  | 0  | 0 | 0     |    |    |       | BYT | E |   |   |   |

| OR        |           |    |    |    |    |   |       |    |    |       |     |   |   |   |   |

|           |           |    |    |    |    |   | WOF   | RD |    |       |     |   |   |   |   |

| OR        | OR        |    |    |    |    |   |       |    |    |       |     |   |   |   |   |

| LONG WORD |           |    |    |    |    |   |       |    | ]  |       |     |   |   |   |   |

|           | LONG WORD |    |    |    |    |   | / ORD | ER |    |       |     |   |   |   |   |

# 2.11.4 Effective Address Encoding Summary

Table 2.1 is a summary of the effective addressing modes discussed in the previous paragraphs.

Table 2.1

Effective Address Encoding Summary

| Addressing Mode                              | Mode | Register        |

|----------------------------------------------|------|-----------------|

| Data Regiser Direct                          | 000  | Register Number |

| Address Register Direct                      | 001  | Register Number |

| Address Register Indirect                    | 010  | Register Number |

| Address Register Indirect with Postincrement | 011  | Register Number |

| Address Register Indirect with Predecrement  | 100  | Register Number |

| Address Register Indirect with Displacement  | 101  | Register Number |

| Address Register Indirect with Index         | 110  | Register Number |

| Absolute Short                               | 111  | 000             |

| Absolute Long                                | 111  | 001             |

| Program Counter with Displacement            | 111  | 010             |

| Program Counter wiht Index                   | 111  | 011             |

| Immediate                                    | 111  | 100             |

# 2.12 IMPLICIT REFERENCE

Some instructions make implicit reference to the program counter (PC), the system stack pointer (SP), the supervisor stack pointer (SSP), the user stack pointer (USP), or the status register (SR). Table 2.2 provides a list of these instructions and the registers implied.

| Instruction                                   | Implied Register(s) |

|-----------------------------------------------|---------------------|

| Branch Conditional (Bcc), Branch Always (BRA) | РС                  |

| Branch to Subroutine (BSR)                    | PC, SP              |

| Check Register Against Bounds (CHK)           | SSP, SR             |