#### FEATURES

- Two Clock Generators

- Π Eight pre-programmed pin selected pixel clock frequencies One pre-programmed memory  $\square$

- clock frequency

- □ Programmable pixel clock and memory clock frequencies

#### **GENERAL DESCRIPTION**

The SC11412 contains two digitally controlled clock generators capable of generating two independent clock frequencies. The two clock generator outputs may be used to drive the pixel (video dot) clock and memory clock inputs of a typical VGA controller chip. A single crystal or an externally generated system bus clock (14.318MHz) may be used as the input reference frequency.

On power-on reset, the two :lock generators default to preprogrammed clock frequencies. The default frequency for Clock Generator No.1 (Pixel Clock) will ve one of eight pre-programmed requencies determined by the coniguration of the frequency select

#### LOCK DIAGRAM

- □ Power-Down modes for

- notebook computers

- On-chip loop filters

- Maximum frequency-100 MHz Low power CMOS technology

- IBM VGA Compatible No

- additional logic required

pins FS[2:0]. Clock Generator No. 2 (Memory Clock) defaults to a single pre-programmed frequency of 32MHz. In addition to the preprogrammed frequencies, each clock generator can be programmed by the VGA controller, using the serial programming interface, to generate any desired frequency within the VCO frequency range.

Serial programming of the SC11412 by a VGA controller can be accomplished using the VGA controller's three clock select output signals with minimal modification of the Video BIOS routines. Sierra Semiconductor will provide information, including sample routines, to support the modification of the BIOS for programming user

Dual Programmable Video Clock Generator

SC11412

with Power Down

advanced epi based, double poly, low power CMOS technology. The SC11412 offers a cost effective solution for generating a wide range of pixel and memory clock frequencies. The frequency outputs are compatible with Super VGA, VGA, EGA, MCGA, CGA, MDA and higher frequency applications.

# SC11412

| PIN NAME              | PIN NUMBER | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>GND</sub>      | 16         | Analog ground.                                                                                                                                                                                                                                                                                                                                                     |

| AV <sub>DD</sub>      | 11         | Analog +5V supply.                                                                                                                                                                                                                                                                                                                                                 |

| D <sub>GND1</sub>     | 5          | Digital ground for Clock Generator No.1.                                                                                                                                                                                                                                                                                                                           |

| D <sub>GND2</sub>     | 12         | Digital ground for Clock Generator No.2.                                                                                                                                                                                                                                                                                                                           |

| DV <sub>DD1</sub>     | 7          | Digital +5V supply for Clock Generator No.1.                                                                                                                                                                                                                                                                                                                       |

| DV <sub>DD2</sub>     | 4          | Digital +5V supply for Clock Generator No.2.                                                                                                                                                                                                                                                                                                                       |

| FS <sub>0</sub> /DATA | 9          | Frequency Select/Data input (TTL compatible). This is a dual purpose pin. When LE/<br>PR is a logic zero, the pin is the FS0 input for Clock Generator No. 1. When LE/PR is a<br>logic one, the pin is the DATA input to the serial programming shift register. Data is<br>shifted into the serial programming shift register on the rising edge of the WR signal. |

| $FS_1/\overline{WR}$  | 13         | Frequency Select/ $\overline{WR}$ input (TTL compatible). This is a dual purpose pin. When LE/<br>PR is a logic zero, the pin is the FS1 input for Clock Generator No. 1.                                                                                                                                                                                          |

|                       |            | When LE/PR is a logic one, the pin is the $\overline{WR}$ input. The rising edge of $\overline{WR}$ is used to shift DATA into the serial programming shift register.                                                                                                                                                                                              |

| FS <sub>2</sub>       | 14         | Frequency Select input (TTL compatible). This pin is the third frequency select input for Clock Generator No. 1.                                                                                                                                                                                                                                                   |

| LE/PR                 | 3          | Latch Enable/Pointer Reset (TTL compatible). This is a multi-purpose pin that controls<br>the Frequency Select (FS) and Programming (P) latches as well as the Pointer Reset of<br>the serial programming shift register.                                                                                                                                          |

|                       |            | When LE/PR is a logic zero, the FS latch is transparent and the P latch is closed. This allows the frequency select inputs FS[2:0] to select one of Clock Generator No.1's eight pre-programmed pixel clock frequencies.                                                                                                                                           |

|                       |            | When LE/PR is a logic one, the FS latch is closed and the P latch is transparent. This allows the FS0/DATA and FS1/ $\overline{\text{WR}}$ pins to be used for loading new frequencies into the SC11412.                                                                                                                                                           |

|                       |            | The LE/PR pin is also used to initialize the serial programming pointer (Pointer Reset).<br>Any write operation to the 20-bit serial programming shift register should be preceded<br>by a Pointer Reset. A LOW-to-HIGH transition on the LE/PR pin causes the pointer to<br>be reset to zero.                                                                     |

| MCLK                  | 8          | Memory Clock output. VCO output of Clock Generator No. 2.                                                                                                                                                                                                                                                                                                          |

| N/C                   | 2, 15      | Not connected. These pins should be left unconnected (floating).                                                                                                                                                                                                                                                                                                   |

| PCLK                  | 6          | Pixel Clock output. VCO output of Clock Generator No.1.                                                                                                                                                                                                                                                                                                            |

| XTAL <sub>IN</sub>    | 11         | Crystal oscillator input (AC coupled TTL, or a CMOS level signal can be applied). The signal applied to this pin serves as the input reference frequency to the two clock generators. A single crystal or an externally generated system bus clock (14.318 MHz) may be used.                                                                                       |

| XTALOUT               | 10         | Crystal oscillator output. If a crystal oscillator is used this output should be connected to the crystal through a series damping resistor.                                                                                                                                                                                                                       |

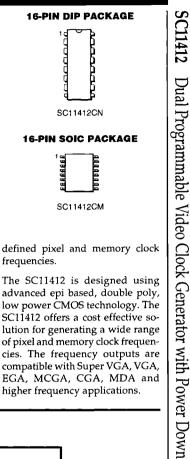

#### CONNECTION DIAGRAMS

| Г                 |             |      |          |                   | <b></b> |         |                         |  |

|-------------------|-------------|------|----------|-------------------|---------|---------|-------------------------|--|

| AV <sub>DD</sub>  | 1           | 16   | AGND     |                   | 1       |         | 16 AGND                 |  |

| N/C 🗋             | 2           | 15 🗖 | N/C      | N/C               | 2       |         | 15 N/C                  |  |

| LE/PR             | 3 PDIP      | 14 🗔 | FS2      | LE/PR             | 3       | SOIC    | 14 52                   |  |

|                   | 4           | 13 🗌 | FS1/WR   | DV <sub>DD2</sub> | 4       |         | 13                      |  |

| D <sub>GND1</sub> | 5 SC11412CN | 12 🗆 | DGND2    | DGND1             | 5 SC    | 11412CM | 12 D <sub>GND2</sub>    |  |

| PCLK              | 6           | 11   | XTALIN   | PCLK              | 6       |         | 11 XTALIN               |  |

|                   | 7           | 10 🗆 | XTALOUT  | DVDD1             | 7       |         | 10 XTALOUT              |  |

| MCLK [            | 8           | 9 🗆  | FS0/DATA | MCLK              | 8       |         | 9 FS <sub>0</sub> /DATA |  |

| -                 |             | 5015 | 02       |                   |         |         | 5015 03                 |  |

3-34

•

#### FUNCTIONAL DESCRIPTION

The SC11412 consists of a crystal oscillator, a serial interface unit and two clock generator blocks (see Figure 1). The two clock generators share a common input reference frequency. Each clock generator block contains two programmable 7-bit dividers and a phase-locked loop circuit.

The output clock frequency is determined by the following equation:

PCLK = (Ni/(Mi\*Pi)) \* Fosc and MCLK = (Ni/(Mi\*Pi)) \* Fosc

where Mi, Ni, and Pi are the divider values for Clock Generator i, (i=1 for PCLK and i=2 for MCLK) and Fosc = Input Reference Frequency (at  $XTAL_{IN}$ )

Pi = 1, 2, 4, 8 Mi = 1 to 127 Ni = 1 to 127

## NOTE: For Mi and Ni divide ratios of 0 and 1 are divide by 1.

The on-chip loop filters optimize each clock generator for their specified frequency range and eliminate the need for external loop filter components. The on-chip loop filters also increase noise immunity and simplify board layout.

Clock Generator No. 1 is optimized for generating PCLK (pixel clock) frequencies in the range of 45 to 100 MHz. The post scaler divider must be used if an output frequency below 45 MHz is required.

Clock Generator No. 2 is optimized for generating MCLK (memory clock) output frequencies in the range of 32 to 70 MHz. The post scaler divider must be used if any output frequency below 32 MHz is required.

#### **Frequency Selection**

The SC11412 supports two frequency program modes: the interial frequency selection mode and he external frequency program node. In the internal frequency selection mode, the clock generator generates a frequency using preprogrammed M, N, and P values from the SC11412's mask ROM. Clock Generator No. 1 generates one of eight pre-programmed frequencies. This frequency is controlled by the state of frequency select inputs FS[2:0]. Clock Generator No.2 generates a single preprogrammed frequency. The default frequencies for the two clock generators are given in Table 1 assuming a 14.31818 MHz reference input frequency. The set of default frequencies can be altered by a single metal mask option.

In the external frequency program mode, the two clock generators can be programmed independently through the serial programming interface to generate any desired frequency within the VCO range. The external frequency mode is enabled by setting the VCO1 or VCO2 mode control bit (DS3) to a logic zero. Clock Generator No.1's external frequency program mode is selected by setting  $FS_0 = FS_2 = 0$ ,  $FS_1 = 1$  and  $LE/\overline{PR} = 1$ . Other combinations of the frequency select inputs FS[2:0] will select from the seven pre-programmed frequencies shown in Table 1. The pre-programmed frequency for  $FS_0 = FS_2 =$  $0, FS_1 = 1$  on Clock Generator No.1 is not available in the external frequency program mode (LE/ $\overline{PR}$  = 1). In external frequency program mode the user programmed frequency for Clock Generator No.2 is always selected.

A power on reset causes both clock generators to default to the internal frequency selection mode. To ensure that Clock Generator No. 1 is initialized to the desired default frequency, LE/PR should be held at a logic zero during power on reset so that the FS latch is transparent.

#### **Power Down Modes**

The SC11412 has two power down modes for each clock generator. Each clock generator has the ability to tristate its output and power down its VCO. These features are controlled by bits DSO–DS3 of the serial programming shift register (see Table 2). Power savings are dependent on the operating frequency and the output load. The power dissipation can be estimated using the following formula:

$P = C \times V^2 \times F$ , where:

P is the power in watts V is the operating voltage in watts F is the output frequency in Hz

#### Serial Programming Interface

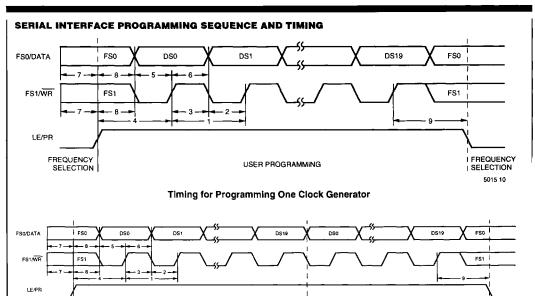

The serial programming interface allows the user to program the pixel and memory clock frequencies and to select the clock generator and VCO modes. The serial programming interface consists of a 20-bit serial shift register DS[19:0], and the control signals FS<sub>1</sub>/WR, FS<sub>0</sub>/ DATA, and LE/PR.

Each clock generator can be programmed to generate a desired fre-

| FS <sub>2</sub> | FS <sub>1</sub> | FS <sub>0</sub> | Clock Generator No.1<br>PCLK (MHz) | Clock Generator No. 2<br>MCLK (MHz) |

|-----------------|-----------------|-----------------|------------------------------------|-------------------------------------|

| 0               | 0               | 0               | 25.175                             | 32.000                              |

| 0               | 0               | 1               | 28.321                             | 32.000                              |

| 0               | 1               | 0               | 40.000                             | 32.000                              |

| 0               | 1               | 1               | 65.000                             | 32.000                              |

| 1               | 0               | 0               | 50.000                             | 32.000                              |

| 1               | 0               | 1               | 44.900                             | 32.000                              |

| 1               | 1               | 0               | 56.000                             | 32.000                              |

| 1               | 1               | 1               | 80.000                             | 32.000                              |

**Table 1. Default Clock Generator Frequencies**

quency within the VCO's frequency range. The frequency range for VCO 1 is 45 to 100 MHz. The range for VCO2 is 32 to 70 MHz.

SC11412

A write to the serial programming shift register should be preceded by a pointer reset. The pointer is reset to zero on the rising edge of

#### SERIAL PROGRAMMING SHIFT REGISTER

SHIFTED IN LAST

The pointer is then automatically reset to zero so that the other clock generator may be programmed if necessary.

The 20-bits of the Serial Programming Shift Register are defined as follows:

| •       |            |         |         |           |       |                  |     |                      |

|---------|------------|---------|---------|-----------|-------|------------------|-----|----------------------|

| DS19    | • • •      | DS13    | DS12    | • • •     | DS6   | DS5              | DS4 | DS3                  |

| M1 OR M | 12 CLOCK C | DIVIDER | N1 OR N | 2 CLOCK E | NUDER | VCO1 O<br>POST S |     | VCO1 OR VCO2<br>MODE |

the LE/PR signal; then one bit of

DATA is shifted into the register

on every rising edge of  $\overline{WR}$  pulse.

After the 20-bits are shifted into

the serial programming shift regis-

ter, the data is automatically loaded

into the clock generator selected by

clock generator address bit (DS0).

| DS2                     | DS1                       | DS0                        | SHIFTED IN FIRST |   |

|-------------------------|---------------------------|----------------------------|------------------|---|

| VCO1 OR VCO2<br>DISABLE | PCLK OR MCLK<br>TRI-STATE | CLOCK GENERATOR<br>ADDRESS |                  | 5 |

5015 04

| NAME                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| DS <sub>0</sub>                   | Clock Generator Address bit.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                                   | $DS_0 = 1$ Clock Generator 1 is selected for programming.<br>$DS_0 = 0$ Clock Generator 2 is selected for programming.                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| DS <sub>1</sub>                   | PCLK or MCLK Tri-state bit.                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                                   | $DS_1 = 1$ Tri-states the PCLK or MCLK output driver for the selected clock generator.<br>$DS_1 = 0$ Enables the PCLK or MCLK output driver for the selected clock generator.                                                                                                                                                                             |  |  |  |  |  |  |

|                                   | At power on reset both the clock output drivers are enabled.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| DS <sub>2</sub>                   | VCO1 or VCO2 Disable bit.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                   | $DS_2 \approx 1$ Disables the VCO for the selected clock generator.<br>$DS_2 \approx 0$ Enables the VCO for the selected clock generator.                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                   | At power on reset, both VCOs are enabled. When the VCO is disabled and DS1 $\approx$ 0, the clock output is HIGH.                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| DS <sub>3</sub>                   | VCO1 or VCO2 Mode bit.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                                   | $DS_3 = 1$ Enables internal frequency selection mode for the selected clock generator.<br>$DS_3 = 0$ Enables external frequency program mode for the selected clock generator.                                                                                                                                                                            |  |  |  |  |  |  |

|                                   | For VCO1, external mode is selected only if $DS_3 = 0$ and $FS_0 = 0$ , $FS_1 = 1$ , $FS_2 = 0$ .<br>For VCO2, the values of $FS_0$ , $FS_1$ and $FS_2$ do not affect the mode selection.                                                                                                                                                                 |  |  |  |  |  |  |

|                                   | At power on reset, the internal frequency selection mode is selected for both clock generators.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| DS5-DS4                           | VCO1 or VCO2 output auxiliary divider (P).                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                                   | Divides the VCO output of the selected clock generator.                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                   | DS5 DS4 PCLK or MCLK                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                   | 0         0         VCO <sub>OUT1</sub> or         VCO <sub>OUT2</sub> 0         1         VCO <sub>OUT1</sub> /2         or         VCO <sub>OUT2</sub> /2           1         0         VCO <sub>OUT1</sub> /4         or         VCO <sub>OUT2</sub> /4           1         1         VCO <sub>OUT1</sub> /8         or         VCO <sub>OUT2</sub> /8 |  |  |  |  |  |  |

| DS <sub>12</sub> -DS <sub>6</sub> | VCO1 or VCO2 clock divider control word (N).                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| DS13-DS19                         | Clock Generator No.1 or Clock Generator No.2 reference clock divider control word (M).                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

#### INTERFACING THE SC11412 TO VGA CONTROLLERS

The SC11412 is designed to easily interface with standard (IBM compatible) VGA controllers without additional logic components. The interface allows users to program the chip to any desired frequency while maintaining full compatibility with the IBM VGA standard.

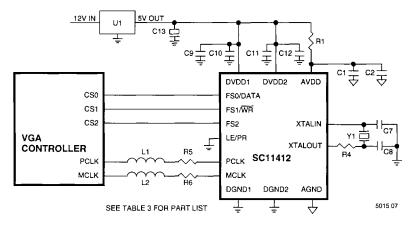

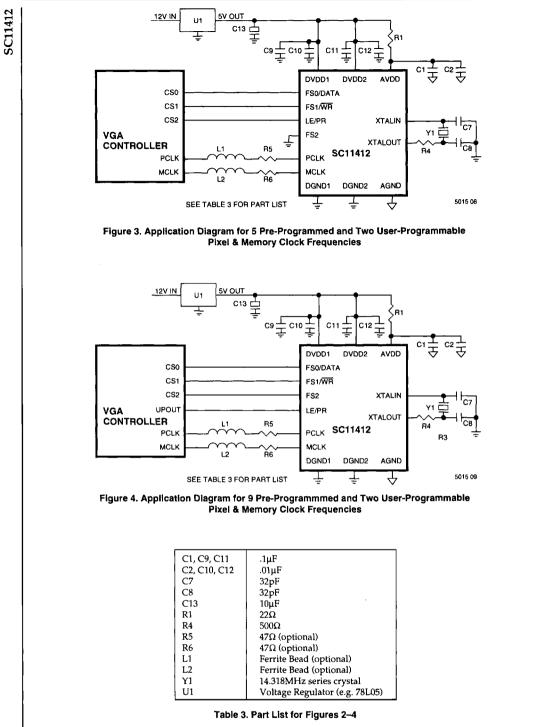

The interface to the VGA controller uses the  $FS_0/DATA$ ,  $FS_1/WR$ ,  $FS_2$ , and LE/PR pins of the SC11412 and the three clock select pins of the VGA controller (eg. CS[2:0]). If other user programmable outputs (eg. UPOUT) are available from the VGA controller, they may be used to program the SC11412. Figures 2–4 illustrate three possible ways of configuring the SC11412 with a VGA controller.

**Configuration 1:** In this configuration (Figure 2), LE/PR is tied to a logic zero, and the FS<sub>0</sub>/DATA, FS<sub>1</sub>/ WR, FS<sub>2</sub> pins are tied to the VGA controller's three clock select pins, CS0, CS1, and CS2. There are nine pre-programmed frequencies available in this configuration, eight for the pixel clock and one for the memory clock.

**Configuration 2:** Configuration 2 (Figure 3) can access five pre-programmed frequencies and two user-programmable frequencies. In this configuration, FS<sub>2</sub> is tied to a logic zero, and FS<sub>0</sub>/DATA, FS<sub>1</sub>/ WR, LE/PR pins are tied to the VGA controller clock select pins, CS0, CS1, and CS2. Five preprogrammed frequencies (four for pixel clock and one for memory clock) and two user-programmable frequencies (one for pixel clock and one for memory clock) are available in this configuration. SC11412

Configuration 3: This configuration (Figure 4) is applicable only if an additional programmable output pin (eg. UPOUT) is available from the VGA controller. In this configuration, LE/PR is tied to UPOUT, and the  $FS_0/DATA$ ,  $FS_1/\overline{WR}$ ,  $FS_2$ pins are tied to the VGA controller  ${

m clock}$  select pins, CS0, CS1, and CS2. Nine pre-programmed frequencies (eight for pixel clock and one for memory clock) and two userprogrammable frequencies (one for pixel clock and one for memory clock) are available in this configuration.

Figure 2. Application Diagram for 9 Pre-Programmed Pixel & Memory Clock Frequencies

3

.

## ABSOLUTE MAXIMUM RATINGS (NOTES 1-3)

| ABSOLUTE MAXIMUM RATINGS (NOTES 1-3)                |                                      |

|-----------------------------------------------------|--------------------------------------|

| Supply Voltage, AV <sub>DD</sub> , DV <sub>DD</sub> | 6 V                                  |

| DC Input Voltage                                    | GND ~ 0.5 to V <sub>CC</sub> + 0.5 V |

| Storage Temperature Range                           | 65 to 150°C                          |

| Power Dissipation (Note 3)                          | 500 mW                               |

| Lead Temperature (Soldering 10 Sec.)                | 300°C                                |

#### **OPERATING CONDITIONS**

| PARAMETER                       | DESCRIPTION             | CONDITIONS | MIN | ТҮР    | MAX | UNITS |

|---------------------------------|-------------------------|------------|-----|--------|-----|-------|

| T <sub>A</sub>                  | Ambient Temperature     |            | 0   |        | 70  | °C    |

| V <sub>CC</sub>                 | Positive Supply Voltage |            | 4.5 | 5.0    | 5.5 | v     |

| GND                             | Ground                  |            |     | 0      |     | v     |

| XTLIN,<br>XTLOUT                | Crystal Frequency       |            |     | 14.318 | 30  | MHz   |

| T <sub>R</sub> , T <sub>F</sub> | Input Rise or Fall Time |            |     |        | 50  | ns    |

NOTE 1: Absolute maximum ratings are those values beyond which damage to the device may occur.

NOTE 2: Unless otherwise specified, all voltages are referenced to ground.

NOTE 3: Power dissipation temperature derating-Plastic package: -12 mW/C from 65°C to 85°C.

| PARAMETER       | DESCRIPTION                                                                                                              | CONDITIONS                    | MIN        | ТҮР | MAX        | UNITS  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|-----|------------|--------|

| I <sub>DD</sub> | AV <sub>DD</sub> & DV <sub>DD</sub>                                                                                      | Normal                        |            | 50  |            | mA     |

|                 | Quiescent Current                                                                                                        | VCO1 and VCO2<br>Powered Down |            | 6   |            | mA     |

| V <sub>IH</sub> | High Level Input Voltage, All Inputs                                                                                     |                               | 2.4        |     |            | V      |

| V <sub>IL</sub> | Low Level Input Voltage, All Inputs                                                                                      |                               |            |     | 0.8        | V      |

| V <sub>OH</sub> | High Level Output, All Outputs<br>Except $XTL_{OUT}$<br>( $I_{OH} = 0.5 \text{ mA}$ )<br>( $I_{OH} = 100 \mu \text{A}$ ) |                               | 2.4<br>4.5 |     |            | V<br>V |

| V <sub>OL</sub> | Low Level Output, All Outputs<br>Except $XTL_{OUT}$<br>( $I_{OL} = 1.6 \text{ mA}$ )<br>( $I_{OL} = 100 \mu\text{A}$ )   |                               |            |     | 0.6<br>0.2 | V<br>V |

| V <sub>OH</sub> | High Level Output $XTL_{OUT}$<br>( $l_{OH} = 20 \ \mu A$ )                                                               |                               | 4          |     |            | v      |

| V <sub>OL</sub> | Low Level Output $XTL_{OUT}$<br>(I <sub>OL</sub> = 20 µA)                                                                |                               |            |     | 0.2        | v      |

## DC ELECTRICAL CHARACTERISTICS (T\_A = 0 to 70°C, V\_{CC} = +5 V $\pm$ 10%)

SC11412

#### Timing for Programming Two Clock Generators

USER PROGRAMMING, FIRST VCD

FREQUENCY

5015 11

USER PROGRAMMING, SECOND VCO

| NO. | SYMBOL           | PARAMETER                                                             | MIN | MAX | UNIT |

|-----|------------------|-----------------------------------------------------------------------|-----|-----|------|

| 1   | t <sub>WC</sub>  | Write Cycle Time                                                      | 100 |     | ns   |

| 2   | t <sub>WP</sub>  | Write Pulse Width                                                     | 50  |     | ns   |

| 3   | t <sub>WR</sub>  | Write Recovery Time                                                   | 50  |     | ns   |

| 4   | t <sub>PS</sub>  | Point-Reset SetupTime to Rising Edge of WR                            | 50  |     | ns   |

| 5   | t <sub>DS</sub>  | DATA Setup Time to Rising Edge of WR                                  | 20  |     | ns   |

| 6   | t <sub>DH</sub>  | DATA Hold Time from Rising Edge of WR                                 | 20  |     | ns   |

| 7   | t <sub>DSL</sub> | FS <sub>0</sub> , FS <sub>1</sub> Setup time to Rising Edge of LE/PR  | 30  |     | ns   |

| 8   | t <sub>DHL</sub> | FS <sub>0</sub> , FS <sub>1</sub> Hold Time from Rising Edge of LE/PR | 20  |     | ns   |

| 9   | t <sub>PH</sub>  | LE/PR Hold Time from Rising Edge of WR                                | 50  |     | ns   |

3-40

FREQUENCY SELECTION