# 82C575 COMMUNICATION MICROCHANNEL™ INTERFACE CHIP

- Compatible with IBM Microchannel<sup>™</sup> specifications

- Provides highly integrated Microchannel™ compatible interface solution for most communication adapter applications

- Suitable for most 8 bit slave IO peripheral applications

- Unique and flexible Card ID assignment

- Supports POS registers

- Four POS register bit outputs for system configuration

The 82C575 is a highly integrated Microchannel™ compatible interface chip for use in personal computer applications compatible with the IBM PS/2 standard. It supports the Microchannel™ compatible interface to most of the 8 bit IO slave devices. The adapter IO address can be programed during the setup procedure, this resource relocation capability avoids adapter address conflicts. The interrupt level can also be selected via software. The on-chip wait state generator allows the user to optimize the system bus timing to his/her specific needs. A unique Card ID generator does not require any external components.

- Resource relocation capability to avoid address conflict

- Dual resource relocators to support multiple peripherals per card

- Sophisticated Card Channel Ready signal generator

- On chip system wait state generator

- **Low power CMOS technology**

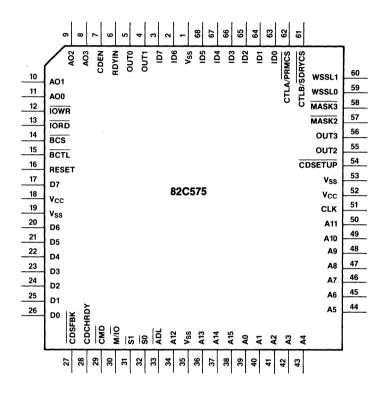

- 68 pins PLCC package

All these features greatly simplify the design of a circuit to interface to the Microchannel™ compatible bus.

The 82C575 supports application markets such as intelligent Modems, SDLC/BISYNC/UART adapter card applications, instrumentation, etc. The dual resource relocater provides the capability to support multiple peripheral system with a maximum of 32 IO address space. The 82C575 is fabricated using advanced CMOS technology and is packaged in a 68 pin PLCC.

\* IBM is a trademark of International Business Machine corporation.

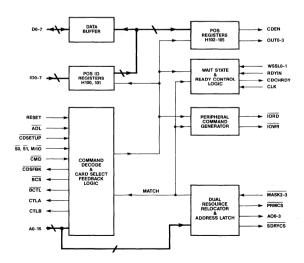

Figure 1. 82C575 Functional Block Diagram

3/88 REV 0

## 82C575 Pin Description

| Pin<br>No.   | Pin<br>Type | Symbol           | Description                                                                                                                                                                                                                                                                                               |

|--------------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63-68<br>2-3 | 1           | ID0-5<br>ID6-7   | Adapter Identification bits 0 to 7 for both low byte (Register 100) and high byte (Register 101). ID0 is the least significant bit (LSB) and ID7 is the most significant bit (MSB). The individual multiplexed ID bit can be tied to $V_{CC}$ , $V_{SS}$ , CTLA or CTLB according to the following table: |

|              |             |                  | $V_{CC}$ : IF both high and low byte bits are "1". $V_{SS}$ : If both high and low byte bits are "0". CTLA: If high byte bit is "0" and low byte bit is "1". CTLB: If high byte bit is "1" and low byte bit is "0".                                                                                       |

|              |             |                  | The values of these pins are returned by executing a READ ID command during the adapter setup operation. The input buffers have internal pullup resistors. They can be left floating instead of being tied to $V_{\rm CC}$ .                                                                              |

| 5-4<br>55-56 | 0           | OUT0-1<br>OUT2-3 | Outputs from POS register 102 bits 1 to 4. They can be used as the general purpose control signals for the system configuration, such as interrupt level selection.                                                                                                                                       |

| 6            | I           | RDYIN            | Active high Ready Input from a slow IO device. For external asynchronous extended channel cycle operation, CDCHRDY goes inactive at the begining of the cycle and stays inactive until a low to high transition is detected on RDYIN pin.                                                                 |

| 7            | 0           | CDEN             | Active high Card Enable. It is the output of POS register 102 bit 0.                                                                                                                                                                                                                                      |

| 8-11         | 0           | AO3-0            | Latched Address Output 3 to 0. These bits are latched by ADL and are used by the peripheral device to address the 82C575 internal registers.                                                                                                                                                              |

| 12           | 0           | IOWR             | Active low IO write strobe. It is the decoded command from CPU to load the information into the the registers of the externally addressed IO slave device. It goes active only when the IO address matches the primary or secondary resource relocater address.                                           |

| 13           | 0           | IORD             | Active low IO read strobe. It is the decoded command from CPU to read the device registers. It goes active only when the IO address matches the primary or secondary resource relocater address.                                                                                                          |

| 14           | 0           | BCS              | Active low 74LS245 buffer chip enable. It goes active if the internal POS registers or external IO device is addressed. (Either read or write operation.)                                                                                                                                                 |

| 15           | 0           | BCTL             | Active low external 74LS245 buffer transfer direction control signal. It becomes active during an IO READ operation if the POS registers or external IO device is addressed.                                                                                                                              |

# 82C575 Pin Description (Continued)

| Pin<br>No.           | Pin<br>Type | Symbol                 | Descri                                                                                                                                                                             | ption                                                                                                                                                                                                                                                      |           |                                                                                                         |  |  |

|----------------------|-------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------|--|--|

| 16                   | ı           | RESET                  |                                                                                                                                                                                    |                                                                                                                                                                                                                                                            |           | re reset signal to initialize the chip. It a minimum period of 500 ns.                                  |  |  |

| 17<br>20-26          | B<br>B      | D7<br>D6-0             | data to                                                                                                                                                                            | and fro                                                                                                                                                                                                                                                    | m the     | o 0. These bits are used to transfer the CPU data bus during the configuration ate bidirectional lines. |  |  |

| 27                   | 0           | CDSFBK                 | when a                                                                                                                                                                             | n IO s                                                                                                                                                                                                                                                     | lave p    | ect Feedback. This signal goes active eripheral is addressed by the host. It g a setup cycle.           |  |  |

| 28                   | 0           | CDCHRDY                | slow pe<br>the set<br>bus cyc                                                                                                                                                      | Card Channel Ready. This signal is used by an external slow peripheral device to extend the channel cycle. During the setup operation, CDCHRDY always stays active and bus cycle is not extended. The maximum time CDCHRDY can stay inactive is 3 $\mu$ s. |           |                                                                                                         |  |  |

| 29                   | I           | CMD                    | Active low Command signal to define when data is valid on the data bus. It is used to generate the IO/memory read and write commands and is also used to latch the status signals. |                                                                                                                                                                                                                                                            |           |                                                                                                         |  |  |

| 30                   | I           | M/IO                   | Memory/Input Output. If M/IO is high, it indicates a memory cycle. If it is low, it indicates an IO cycle.                                                                         |                                                                                                                                                                                                                                                            |           |                                                                                                         |  |  |

| 31<br>32             | l<br>I      | <u>S1</u><br>S0        | type of                                                                                                                                                                            | chann                                                                                                                                                                                                                                                      | el cycl   | These signals indicate the start and the e. It is used with M/IO to generate the and write commands.    |  |  |

|                      |             |                        | M/IO                                                                                                                                                                               | <b>S</b> 0                                                                                                                                                                                                                                                 | <b>S1</b> | Function                                                                                                |  |  |

|                      |             |                        | 0                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                          | 0         | Reserved                                                                                                |  |  |

|                      |             |                        | 0                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                          | 1         | IO Write                                                                                                |  |  |

|                      |             |                        | 0                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                          | 0         | IO Read                                                                                                 |  |  |

|                      |             |                        | 0                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                          | 1         | Reserved                                                                                                |  |  |

|                      |             |                        | 1                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                          | 0         | Reserved                                                                                                |  |  |

|                      |             |                        | 1                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                          | 1         | Memory Write                                                                                            |  |  |

|                      |             |                        | 1                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                          | 0         | Memory Read                                                                                             |  |  |

|                      |             |                        | 1                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                          | 1         | Reserved                                                                                                |  |  |

| 33                   | ı           | ADL                    | Active<br>A0-3 ac                                                                                                                                                                  |                                                                                                                                                                                                                                                            |           | Decode Latch. It is used to latch the                                                                   |  |  |

| 34<br>36-38<br>39-50 | <br> <br>   | A12<br>A13-15<br>A0-11 | address                                                                                                                                                                            | s deco                                                                                                                                                                                                                                                     | ding of   | s 15 to 0. These bits are used for the fithe external IO device. They are also POS registers.           |  |  |

| 51                   | ı           | CLK                    | 14.3 MI<br>wait sta                                                                                                                                                                |                                                                                                                                                                                                                                                            | tem C     | lock. It is used to generate a system                                                                   |  |  |

# 82C575 Pin Description (Continued)

| Pin<br>No.     | Pin<br>Type | Symbol                    | Descrip                                                 | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                 |

|----------------|-------------|---------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 54             | I           | CDSETUP                   | and erro                                                | r recover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Setup enable signal. During configuration by procedures, CDSETUP becomes active ead/Write commands to access the POS                                                                                                                                            |

| 57<br>58       | 1           | MASK2<br>MASK3            | and sec<br>compari<br>with the<br>input bu              | ondary in son of the relocate in the son of | bits for the comparators of both primary relocaters. When a mask bit is low, the he corresponding address input (A2-3) or address bits 2 to 3 is bypassed. The re internal pull up resistors. They can be "1" value.                                            |

| 59<br>60       | 1           | WSSL0<br>WSSL1            |                                                         | te Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ion signals. They are used to control the                                                                                                                                                                                                                       |

|                |             |                           | WSSL1                                                   | WSSL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Function                                                                                                                                                                                                                                                        |

|                |             |                           | 0                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Synchronous Extented bus cycle                                                                                                                                                                                                                                  |

|                |             |                           | 0                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Synchronous Wait State 1                                                                                                                                                                                                                                        |

|                |             |                           | 1                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Synchronous Wait State 2                                                                                                                                                                                                                                        |

|                |             |                           | 1                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | External asynchronous Extented bus cycle                                                                                                                                                                                                                        |

|                |             |                           | read acc<br>for the 2<br>nous Wa<br>peripher<br>is used | cess time<br>50 ns (M<br>ait State<br>al. The E<br>to exter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | tended bus cycle is used for 120 ns (Max) a peripheral. Synchronous Wait State 1 is ax) Read delay time device and Synchro-2 for the 460 ns (Max) read delay time xternal asynchronous Extended bus cycle and the system bus cycle by using the control signal. |

| 62<br>61       | 0           | CTLA/PRMCS<br>CTLB/SDRYCS | adapter<br>reading                                      | identification the low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | they are Control Output signals for the ation bits. CTLA goes active high while byte ID (Register 100). CTLB becomes ing the high byte ID (Register 101).                                                                                                       |

|                |             |                           | Chip Se<br>address<br>SDRYCS                            | lect signa<br>matches<br>goes a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | tion cycle, those two pins are Peripheral als. PRMCS goes active low when the IO the primary resource relocater address. ctive low when IO address matches the rece relocater.                                                                                  |

| 18,52          | ı           | V <sub>CC</sub>           | 5V Powe                                                 | er Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                 |

| 1,19,<br>35,53 | ı           | V <sub>SS</sub>           | Power S                                                 | Supply Gi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | round.                                                                                                                                                                                                                                                          |

Note: I = Input O = Output B = Bidirectional

#### **82C575 Functional Description**

The 82C575 block diagram is illustrated in Fig 1. The chip consists of the following functional blocks:

- POS Registers

- Peripheral Commands and Card Select Feedback Generator

- Dual Resource Relocator Logic

- Wait state and Card Channel Ready Signal Generator

#### **POS Registers**

A total of 6 POS registers are supported by 82C575. These registers can be accessed only during configuration cycle by activating CDSETUP, M/IO to low. The description of each register are as follows:

1. 100H: Low Byte ID Register.

| Bit | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|     | ID7 | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 |

This register is a read only register. The reading of this register returns the contents of pins ID7-ID0.

2. 101H: High Byte ID Register.

| Bit | 7    | 6    | 5    | 4    | 3    | 2    | 1   | 0   |

|-----|------|------|------|------|------|------|-----|-----|

|     | ID15 | ID14 | ID13 | ID12 | ID11 | ID10 | ID9 | ID8 |

This register is a read only register. The reading of this register returns the contents of pins ID7-ID0.

The ID7 to 0 are the multiplexed pins for both low and high ID bytes. Each individual bit can be tied to  $V_{\rm CC},~V_{\rm SS},~{\rm CTLA}$  or CTLB depending on the bit value in the high and low byte register as described in the pin description. For example if 100 low byte ID is "00110110" and 101 high byte ID is "01011010" starting with MSB, ID7 should be tied to  $V_{\rm SS},~{\rm ID6}$  to CTLB, ID5 to CTLA, ID4 to  $V_{\rm CC},~{\rm ID3}$  to CTLB, ID2 to CTLA, ID1 to  $V_{\rm CC}$  and ID0 to  $V_{\rm SS}.$

3. 102H: Control Register.

| Bit | 7      | 6      | 5      | 4    | 3    | 2    | 1    | 0    |  |

|-----|--------|--------|--------|------|------|------|------|------|--|

|     | SADR15 | SADR14 | SRDYEN | OUT3 | OUT2 | OUT1 | OUTO | CDEN |  |

Bits 1 to 4 are brought out to OUT0-3 pins. They can be used for system configuration.

Bits 5, 6 and 7 are used with registers 0103H, 0104H and 0105H and are described below.

Register 102H is readable and writable. All the bits are reset to "0" by RESET signal.

103H: Low Byte Primary Card Address and Secondary Card Address Register.

| Bit | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-----|-------|-------|-------|-------|-------|-------|-------|-------|

|     | PADR7 | PADR6 | PADR5 | PADR4 | PADR3 | PADR2 | SADR8 | SADR3 |

104H: High Byte Primary Card Address Register.

| Bit | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|-----|--------|--------|--------|--------|--------|--------|-------|-------|

|     | PADR15 | PADR14 | PADR13 | PADR12 | PADR11 | PADR10 | PADR9 | PADR8 |

The Card Address registers are read/write registers. They are used for resource relocation to avoid adapter conflicts. In case of the same adapter address, the host can reassign the board address. There are two sets of adapter address: Primary and Secondary. For Primary relocator, address bits 15 to 2 are programmable. For Secondary relocater, only bits 15 to 12, bit 8, bits 7 to 3 are programmable. SRDYEN (0102H bit 5) is used to enable the secondary address relocation feature: a zero enables the secondary address relocation registers. Bits 6 and 7 of 0105H are not used and will be read as one's. The unprogrammed bits in the Secondary relocater (SADR11-9, SADR2) are the same value as the Primary address register bits.

To generate IO read/write commands for the peripheral, or to activate the CDSFBK, or inactivate the CDCHRDY signals, the address from host A15 to A4 have to match the Primary or the Secondary address register bits. A3 or A2 may bypass the comparison if the individual mask bit is activated by forcing MASK3-2 pins to VSS. A1 to A0 will always bypass the

comparison. The PRMCS signal goes active low if the IO address matches the Primary address register. It can be used as the chip enable signal for the primary peripheral. The SDRYCS signal goes active low when IO address matches the secondary address register and SRDYEN = 0, and can be used as the chip enable for a secondary peripheral. In case only the primary peripheral is used in a system, disable secondary address relocation (SRDYEN = 1).

# Peripheral Commands and Card Select Feedback Generator

The peripheral read/write command is generated by decoding the IO or memory address, M/IO, S0, S1, status and gating with CMD signal.

To generate IO read/write commands, the address from host needs to match the dual relocator card address as programmed in the POS registers.(A2-A3 comparison can be bypassed by activating MASK3 to MASK2 individually.)

The Card Select Feedback (CDSFBK) is used to inform the host that the adapter is selected. It stays inactive during a setup cycle. It is generated by decoding the IO address space and SO, S1 status. It should go active within 50 ns after Address and M/IO become valid and within 25 ns from the time status becomes active.

#### **Dual Resource Relocator Logic**

Two sets of the resource relocator address registers are supported in this chip. The operation of this block is described in the POS Registers section.

#### Wait State and Card Channel Ready Generator.

The basic channel cycle time in an IBM PS/2 compatible system is 200 ns. It can be extended by using CDCHRDY signal. There are four ways to extend the cycle: Synchronous, Synchronous wait state 1, Synchronous wait state 2 and External Asynchronous.

During a setup cycle, the 82C575 requires no wait states for read/write operations from the host CPU, CDCHRDY is always active and no

cycle extension is required. In normal IO operation, the bus cycle is always extended either synchronously or asynchronously.

When the peripheral is addressed, CDCHRDY will go low within 55 ns from the time M/IO and Address become valid (25 ns from the time status \$\overline{S0}\$, \$\overline{S1}\$ become valid) and then returns high within 25 ns after \$\overline{CMD}\$ becomes active. The bus cycle is extended from 200 ns to 300 ns, this is called a synchronous extention. This mode is for a peripheral that has a read access delay time of less than 120 ns.

For Synchronous wait state 1 operation, CDCHRDY will go low and stay low for 210 ns to 290 ns from the time CMD goes active. This mode is for a peripheral that has a maximum read access time of 250 ns.

For Synchronous wait state 2 operation, CDCHRDY will go low and stay low for 420 ns to 500 ns after CMD goes active. This can fit the application with the peripheral having read access delay time less than 460 ns.

For External Asynchronous operation, CDCHRDY will go inactive just like synchronous IO access but it will stay low until a low to high transition on pin RDYIN is detected. This mode is for the extremely slow peripheral access.

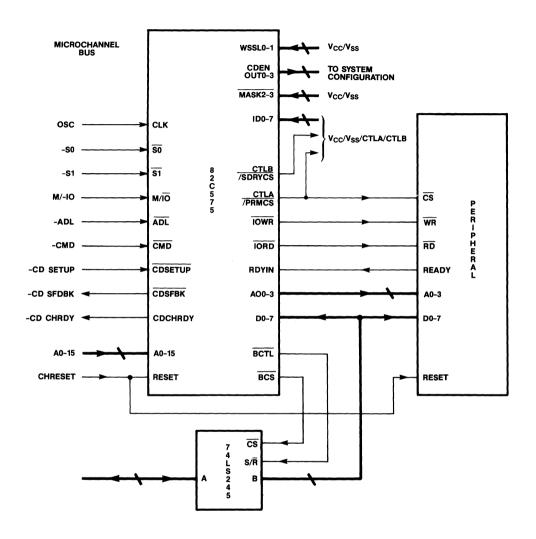

#### Application

Figure 2 show an application diagram for 8 bit IO slave peripherals. The Card ID is selected by tying ID0-7 to  $\mathrm{V}_{\mathrm{CC}},\,\mathrm{V}_{\mathrm{SS}},\,\mathrm{CTLA}$  or CTLB according the table described in the pin description section. This provides a very flexible method for ID selection. Two resource relocaters are supported which make the multiple peripherals per card applications feasible. Address bits 0 to 3 are latched by the 82C575 for these peripherals. The 82C575 also provides the 74LS245 buffer chip select and direction control signals. The OUT0-3 and CDEN can be used for the system configuration such as interrupt level selection. Due to the high integration of the chip, only a few external components are required to implement a low cost, low parts count solution for Microchannel compatible adapter boards.

Figure 2. 82C575 Application Diagram for 8-Bit I/O Slave Peripheral

#### 82C575 Absolute Maximum Ratings

| Parameter             | Symbol           | Min. | Max. | Units |

|-----------------------|------------------|------|------|-------|

| Supply Voltage        | V <sub>cc</sub>  |      | 7.0  | V     |

| Input Voltage         | V <sub>I</sub>   | -0.5 | 5.5  | V     |

| Output Voltage        | v <sub>o</sub>   | -0.5 | 5.5  | V     |

| Operation Temperature | T <sub>op</sub>  | -25  | 85   | °C    |

| Storage Temperature   | T <sub>stg</sub> | -40  | 125  | °C    |

**Note:** Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions described under Operation Conditions.

#### **82C575 Operation Conditions**

| Parameter           | Symbol          | Min. | Max. | Units |

|---------------------|-----------------|------|------|-------|

| Supply Voltage      | V <sub>CC</sub> | 4.75 | 5.25 | ٧     |

| Ambient Temperature | T <sub>A</sub>  | 0    | 70   | °C    |

#### 82C575 DC Characteristics

| Parameter                                                                      | Symbol           | Min. | Max.                  | Units |

|--------------------------------------------------------------------------------|------------------|------|-----------------------|-------|

| Power Supply Current                                                           | I <sub>cc</sub>  |      | 30                    | mA    |

| Input Low Voltage                                                              | V <sub>IL</sub>  | -0.5 | 0.8                   | ٧     |

| Input High Voltage                                                             | V <sub>IH</sub>  | 2.0  | V <sub>CC</sub> + 0.5 | ٧     |

| Output Low Voltage (Note 1)                                                    | V <sub>OL</sub>  |      | 0.4                   | ٧     |

| Output High Voltage (Note 1)                                                   | V <sub>OH</sub>  | 2.4  |                       | ٧     |

| Input Leakage Current For $V_{\rm IN}$ = 0 to $V_{\rm CC}$ Pins ID0-7, MASK2-3 | I <sub>IL1</sub> | -100 | 100                   | μΑ    |

| Input Leakage Current For all other input pins                                 | I <sub>IL2</sub> | -10  | 10                    | μΑ    |

| Output Tri-State Leakage Current for V <sub>O</sub> = 0 to V <sub>CC</sub>     | I <sub>OL</sub>  | -10  | 10                    | μΑ    |

Note 1:  $I_{OL}$  = 6 mA,  $I_{OH}$  = -2 mA for pins CDCHRDY ,  $\overline{\text{CDSFBK}}$ .  $I_{OL}$  = 2.4 mA,  $I_{OH}$  = -400  $\mu\text{A}$  for all other pins.

# Capacitance $(T_A = 25^{\circ}C, V_{CC} = 0)$

| Parameter                                       | Symbol           | Min. | Max. | Units |

|-------------------------------------------------|------------------|------|------|-------|

| Input Capacitance<br>For F <sub>C</sub> = 1 MHz | C <sub>IN</sub>  |      | 10   | pF    |

| Output Capacitance                              | C <sub>OUT</sub> |      | 20   | рF    |

| I/O Capacitance                                 | C <sub>I/O</sub> |      | 20   | pF    |

# 82C575 AC Characteristics

(T\_A = 0°C to 70°C, V\_{CC} = 5V  $\pm$  5% , C\_L = 60 pF for all the output pins)

| Sym | Parameter                                                 | Min | Max | Units |

|-----|-----------------------------------------------------------|-----|-----|-------|

| t1  | RESET Active Pulse Width                                  | 500 |     | ns    |

| t2  | S0, S1 Set-up to CMD Active                               | 50  |     | ns    |

| t3  | A0-15, M/IO Set-up to CMD Active                          | 80  |     | ns    |

| t4  | CDSETUP Set-up to CMD Active                              | 50  |     | ns    |

| t5  | S0, S1, A0-15, M/IO, CDSETUP<br>Hold time from CMD Active | 25  |     | ns    |

| t6  | CDSETUP Setup time from ADL Active                        | 15  |     | ns    |

| t7  | CDSETUP Hold time from ADL Inactive                       | 25  |     | ns    |

| t8  | Write Data Set-up to CMD Inactive                         | 30  |     | ns    |

| t9  | Write Data Hold time from CMD Inactive                    | 15  |     | ns    |

| t10 | OUT0-3, CDEN Delay time from Data Valid                   |     | 50  | ns    |

| t11 | Read Data Delay from CMD Active                           |     | 40  | ns    |

| t12 | Read Data Hold time from CMD Inactive                     | 5   |     | ns    |

| t13 | BCS, BCTL Assert Delay from CMD Active                    |     | 40  | ns    |

| t14 | BCS, BCTL Deassert Delay from CMD Inactive                | 5   | 40  | ns    |

| t15 | CMD Active Pulse Width in SETUP Cycle                     | 90  |     | ns    |

| t16 | CTLA, CTLB Assert and Deassert delay time from ADL Active | 0   | 35  | ns    |

| t21 | ADL Active to CMD Active                                  | 40  |     | ns    |

| t22 | AO0-3 Delay from ADL Active                               | 0   | 25  | ns    |

| t23 | CDSFBK Active Delay from Address, M/IO, Valid             |     | 55  | ns    |

| t24 | CDSFBK Active Delay from Status Active                    |     | 25  | ns    |

| t25 | CDCHRDY Inactive Delay from Status Active                 |     | 25  | ns    |

**82C575 AC Characteristics** (Continued) (T<sub>A</sub> = 0°C to 70°C, V<sub>CC</sub> = 5V  $\pm$  5%, C<sub>L</sub> = 60 pF for all the output pins)

| Sym | Parameter                                                                                                          | Min        | Max        | Units    |

|-----|--------------------------------------------------------------------------------------------------------------------|------------|------------|----------|

| t26 | CDCHRDY Inactive Delay from Address, M/IO, Valid                                                                   |            | 55         | ns       |

| t27 | CDCHRDY Release Delay from CMD Active in Synchronous Extended Cycle                                                |            | 25         | ns       |

| t28 | CMD Active Pulse Width in both Sync and External Asyn Extended Cycles                                              | 190        |            | ns       |

| t29 | IORD, IOWR Active Delay from CMD Active                                                                            |            | 25         | ns       |

| t30 | IORD, IOWR Inactive Delay from CMD Inactive                                                                        |            | 25         | ns       |

| t31 | READ DATA Valid from CMD Active in Sync Extended Cycle                                                             |            | 140        | ns       |

| t32 | PRMCS, SDRYCS Assert and Deassert delay time from ADL Active                                                       |            | 25         | ns       |

| t33 | CLK High time                                                                                                      | 20         |            | ns       |

| t34 | CLK Low time                                                                                                       | 20         |            | ns       |

| t35 | CLK Cycle time                                                                                                     | 69         | 71         | ns       |

| t36 | READ DATA Valid from CDCHRDY Active in External Async Extended, Synch Wait State 1 and Sync Wait State 2 bus cycle |            | 40         | ns       |

| t37 | CDCHRDY Release delay time from IORD, IOWR going Active: For Synchronous Wait State 1 For Synchronous Wait State 2 | 210<br>420 | 290<br>500 | ns<br>ns |

| t38 | CDCHRDY Release delay time from RDYIN Active in External Async Extended cycle                                      | 720        | 40         | ns       |

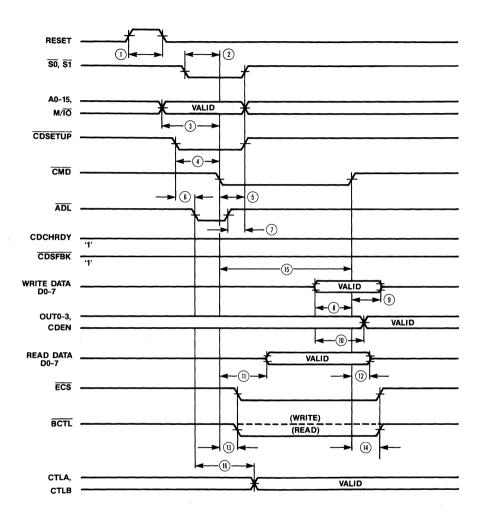

## 82C575 Timing Diagrams

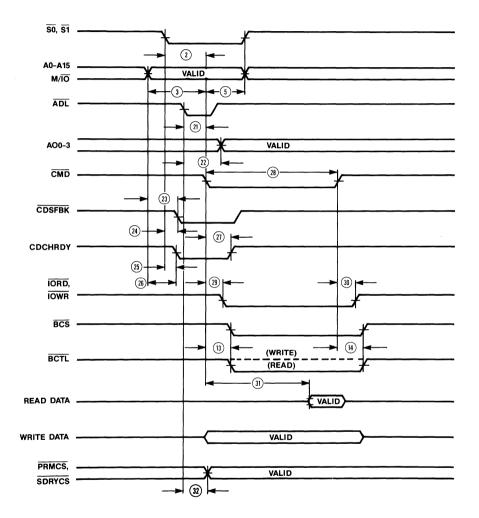

**POS Register Setup Cycle Timing**

### 82C575 Timing Diagrams (Continued)

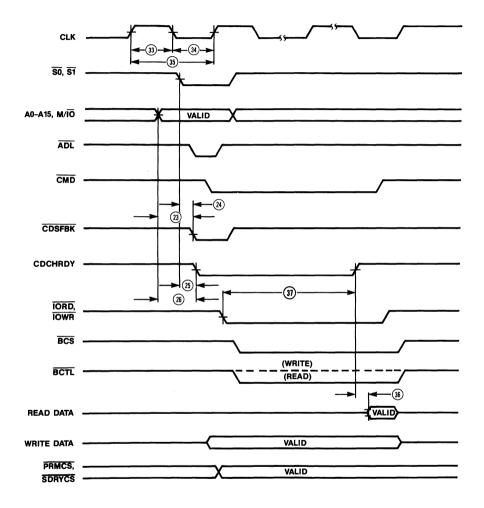

**Synchronous Extended Cycle Timing**

#### 82C575 Timing Diagrams (Continued)

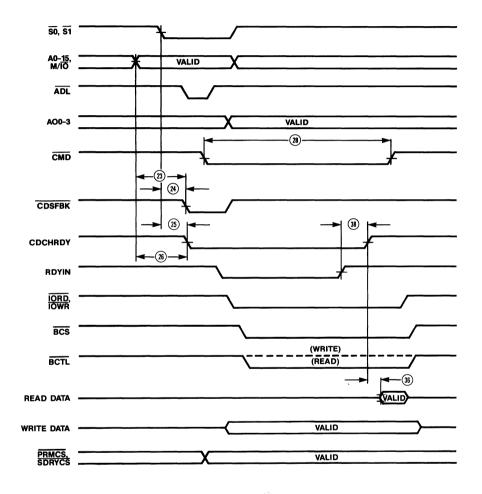

Synchronous Wait State 1 & Wait State 2 Cycle Timing

## 82C575 Timing Diagrams (Continued)

**External Asynchronous Extended Cycle Timing**

## CANADA DISTRIBUTORS

Electro Source, Inc. 39 Robertson Rd., Ste. 233 The Bell Mews Mall Nepean, Ontario Canada K2H 8R2 Phone: 613-726-1452

Electro Source, Inc.

230 Galaxy Blvd. Suite 303 Rexdale, Ontario Canada M9W 5R8 Phone: 416-675-4490

Electro Source, Inc.

6600 TransCanada Hwy. Suite 510 Pointe Claire, Quebec Canada H9R 4S2 Phone: 514-694-0404

ITT Rae Electronics

300 North Riverfmede Road Concord (Toronto) Ontario Canada L4K 2Z4 Phone: 416-736-1144

Valtrie Marketing

910 Roundtree Dairy Road

Unit 12 Woodbridge, Ontario

Canada L4L48 Phone: 416-851-0355

#### U.S. DISTRIBUTORS

**ALABAMA**

**Quality Components** 4900 University Square Suite 20

Huntsville, AL 35816 Phone: 205-830-1881

Hall-Mark

4900 Bradford Drive Huntsville, AL 35816 Phone: 205-837-8700

ARIZONA Anthem

1727 East Webber Drive Tempe, AZ 85281 Phone: 602-966-6600

Hall-Mark

4040 E. Raymond Phoenix, AZ 85040 Phone: 602-437-1200 **CALIFORNIA** Anthem

20640 Bahama Street Chatsworth, CA 91311 Phone: 818-700-1000

Anthem

One Oldfield Drive Irvine, CA 92718-2809 Phone: 714-768-4444

Anthem

4700 Northgate Boulevard Sacramento, CA 95834 Phone: 916-922-6800

Anthem

9369 Carroll Park Drive San Diego, CA 92121 Phone: 619-453-9005

Anthem

10400 East Brokaw San Jose, CA 95131 Phone: 408-295-4200

Hall-Mark

8130 Remmet Avenue Canoga Park, CA 91304 Phone: 818-716-7300

Hall-Mark

6341 Auburn Blvd., Suite D Citrus Heights, CA 95610 Phone: 916-722-8600

Hall-Mark

3878 Ruffin Rd., Suite B San Diego, CA 92123 Phone: 619-268-1201

Hall-Mark

1110 Ringwood Ct. San Jose, CA 95131 Phone: 408-946-0900

Hall-Mark

19220 S. Normandie Avenue Torrance, CA 90502 Phone: 213-217-8400

Hall-Mark

14831 Franklin Avenue Tustin, CA 92680 Phone: 714-669-4700

COLORADO Anthem

373 Inverness Dr. South Englewood, CO 80112 Phone: 303-790-4500

Hall-Mark

6950 S. Tucson Way Englewood, CO 80112 Phone: 303-790-1662

CONNECTICUT

Lionex

170 Research Parkway Meriden, CT 06450 Phone: 203-237-2282

Hall-Mark

33 Village Lane Wallingford, CT 06492 Phone: 203-269-0100

**FLORIDA** Hall-Mark

15302 Roosevelt Blvd.

Suite 303

Clearwater, FL 33520 Phone: 813-530-4543

Hall-Mark

7648 Southland Blvd. Suite 100

Orlando, FL 32809 Phone: 305-855-4020

Hall-Mark

3161 S.W. 15th Street Pompano Beach, FL 33069-4806

Phone: 305-971-9280

**Quality Components** Florida

Phone: 800-241-0037

**GEORGIA** Hall-Mark

6410 Atlantic Blvd.

Suite 115

Norcross, GA 30071 Phone: 404-447-8000

Quality Components 6145 North Bell Pkwy. Suite B

Norcross, GA 30071 Phone: 404-449-9508

**ILLINOIS** Anthem

180 Crossen Elkgrove, IL 60007 Phone: 312-640-6066

Hall-Mark/N.C. Regional Systems Warehouse

210 Mittel Drive Wooddale, IL 60191 Phone: 312-680-3800

#### ΙΝΠΙΔΝΔ Hall-Mark

4275 W. 96th Street Indianapolis, IN 46268 Phone: 317-872-8875 800-423-6638 (INDIANA) 800-772-0112 (KENTUCKY)

#### KANSAS Hall-Mark

10809 Lakeview Drive Lenexa, KS 66215 Phone: 913-888-4747

#### MASSACHUSETTS Hall-Mark

6 Cook Street Bilerica, MA 01821 Boston 617-935-9777 Phone: 617-667-0902

#### Lionex

36 Jonspin Road Wilmington, MA 01887 Phone: 617-657-5170

#### MARYLAND

Hall-Mark/Baltimore 10240 Old Columbia Road Columbia, MD 21046 Phone: 301-988-9800

#### Lionex

9020A Mendenhall Court Columbia, MD 21045 Phone: 301-964-0040

#### **MICHIGAN** Hall-Mark

38027 Schoolcraft Livonia, MI 45810 Phone: 313-462-1205

# MINNESOTA

Anthem 10025 Valley View Rd. #160 Eden Prairie, MN 55344 Phone: 612-944-5454

#### Hall-Mark

10300 Valley View Eden Prairie, MN 55344 Phone: 612-941-2600

#### MISSOURI Hall-Mark

13750 Shoreline Drive Earth City, MO 63045 Phone: 314-291-5350

# **NEW MEXICO**

Hall-Mark

2715 Braidbent Pkwy. NE, Albuquerque, NM 87107 Phone: 505-344-7341

#### NORTH CAROLINA Hall Mark

5237 N. Blvd. Raleigh, NC 27604 Phone: 919-872-0712

## Quality Components

2940-15 Trawick Road Raleigh, NC 27604 Phone: 919-876-7767

#### **NEW JERSEY** Lionex

311 Route 46 West Fairfield, NJ 07006 Phone: 201-227-7960

#### Hall-Mark

107 Fairfield Road Ste. 1B Fairfield, NJ 07006 Phone: 201-575-4415

#### Hall-Mark

1000 Midlantic Drive Mt. Laurel, NJ 08054 Phone: 609-235-1900

#### Hall-Mark

10 Old Bloomfield Avenue Pinebrook, NJ 07058 Phone: 201-882-9773

#### **NEW YORK** Hall-Mark

101 Comac Loop RonKonKoma, NY 11779 Phone: 516-737-0600

#### Lionex

400 Oser Avenue Hauppauge, NY 11787 Phone: 516-273-1660

#### OHIO Hall-Mark

5821 Harper Road Solon, OH 44139 Phone: 216-349-4632

#### Hall-Mark

400 E. Wilson Bridge Road Suite 5 Worthington, OH 43085 Phone: 614-888-3313

# OKLAHOMA

Hall-Mark

2500 No. Hemlock Lane Broken Arrow, OK 74012 Phone: 1-800-327-9989

### Quality Components

9934 E. 21st Street South Tulsa, OK 74129 Phone: 918-664-8812

#### OREGON Anthem

9705 SW Sunshine Ct. #900 Beaverton, OR 97005 Phone: 503-643-1114

# **PENNSYLVANIA**

Lionex

101 Rock Road Horsham, PA 19044 Phone: 215-443-5150

#### TEXAS Hall-Mark

12211 Technology Blvd. Austin, TX 78727 Phone: 512-258-8848

#### Hall-Mark

11420 Page Mill Road Dallas TX 75243 Phone: 214-553-4300

#### Hall-Mark

8000 Westglen Houston, TX 77063 Phone: 713-781-6100

#### Quality Components

4257 Kellway Circle Addison, TX 75001 Phone: 214-733-4300

#### **Quality Components**

2120-M Braker Lane Austin, TX 78758 Phone: 512-835-0220

## Quality Components

1005 Industrial Boulevard Sugar Land, TX 77478 Phone: 713-240-2255

#### UTAH Anthem

1615 West 2200 South Salt Lake City, UT 84119 Phone: 801-973-8555

#### UTAH (con't) Hall-Mark

2265 S. 1300 West West Valley, UT 84119 Phone: 801-972-1008

#### WASHINGTON Anthem

5020 148th Avenue N.E. Redmond, WA 98052 Phone: 206-881-0850

#### WISCONSIN Hall-Mark

16255 W. Lincoln Avenue New Berlin, WI 53151 Phone: 414-797-7844

## FAR EAST DISTRIBUTORS

#### American MITAC Corporation 3385 Viso Court

Santa Clara, CA 95054 U.S.A

Phone: 408-988-0258 Telex: 9103382201 MECTEL

Fax: 408-980-9742

#### AUSTRALIA R&D Electronics

4 Florence Street Burwood, Victoria Australia 3125 Phone: 61-3-288 8911 Fax: 61-3-2889168

#### HONG KONG

Wong's Kong King Ltd. 8/F Sime Darby Ind. Bldg. 420 Kwun Tong Road Kwun Tong, Hong Kong Phone: 852 3-450121 Telex: 36810 WKKL HX Fax: 852 3-7551128

Technology Research Co. 4/F, Block C, Watson's Estate North Point, Hong Kong Phone: 011852 5-8073323

Telex: 80554 TRC HX Fax: 852 5-8073031

#### INDIA

Silicon Electronics 3350 Scott Blvd. #1201 Santa Clara, CA 95054

U.S.A.

Phone: 408-988-4408

#### ISRAEL Hitek Ltd.

5 Haarad St. TEL-AVIV, ISRAEL Phone: 972 03/472005 Telex: 922371984HTK1

#### JAPAN

**ASCII Corporation**

SAT-I Bldg., 3F 2-20-4, Minami Aoyamo Minato-ku

Tokyo 107 Japan Phone: 03-470-0486 Telex: J28764ASCII Fax: 03-740-0522

#### **KOREA**

**Kortronics Enterprises**

Rm. 307 9-Dong B-Block #604-1 Guro-Dong, Guro-Gu Seoul. Korea

Phone: 82 2 635-1043 Fax: 82 2 675-0514

#### SINGAPORE

Chartered Telmos

Design PTE Ltd.

249 Jalan Boonlay

Singapore 261

Phone: 656607359

Phone: 656607359 Fax: 652614913

#### TAIWAN, R.O.C. Chips & Technologies, Inc.

c/o UTC 8th Floor

687 Ming Sheng E., Rd. Rm. 1 Taipei, Taiwan, R.O.C. Phone: 886 250 18170 Ext. 204

Fax: 886 27175595

# EUROPEAN DISTRIBUTORS

#### **BELGIUM**

Auriema Belgium S.A./N.V. Rue Brogniezstraat 172-A

B-1070 Bruxelles

Brussels

Phone: (02) 523-62-95

Telex: 21646

# FINLAND OY Fintronic AB

Melkonkatu 24A SF-00210 Helsinki, Finland

Phone: 358 06926022

Telex: 857124224 FTRON SF

Fax: 358 0 674886

#### FRANCE A2M

6. Av. du General De Gaulle 78150 Le Chesnay France

Phone: 33 39.54.91.13 Telex: 842698376 F Fax: 331 39.54.30.61

#### **GERMANY**

Rein Elektronik GmbH Loetscher Weg 66 Postfach 5160

D-4054 Nettetal 1 West Germany

Phone: 49 (02153) 733-0 Telex: 841854203B REIN D (or 854251B REIN D) Fax: 49 02153-733110

#### ITALY

Eledra S.p.A. Via G. Watt 37

20143 Miliano Viale Elvezia 18

Italy