# CMI-8738/PCI-6CH C3DX series PCI-Based HRTF 3D Extension Positional Audio Chip

#### **Features**

- ✓ 6CH DAC for AC3<sup>®</sup> 5.1CH purpose.

- ✓ HRTF-based 3D positional audio, supporting DirectSound™ 3D interface

- ✓ Supports 4.1/5.1 speakers, C3DX positional audio in 4 / 6 CH speaker mode

- ✓ Legacy audio SBPRO™ compatible

- ✓ DLS-based wavetable music synthesizer, supports DirectMusic<sup>™</sup>

- ✓ Professional digital audio interface supporting 24-bit SPDIF IN and OUT (44.1K and 48K format)

- ✓ Built-in 32ohm Earphone buffer

- ✓ Built-in PCtel® HSP56 Modem™ interface

- ✓ Drivers support EAX<sup>®</sup>, Karaoke Key, Echo...

- ✓ MPU-401 port/ Dual game port

- √ 16-bit full duplex CODEC

- ✓ Built-in ZV port

- √ 32-bit PCI bus master

- ✓ External E²PROM interface

- ✓ Single chip design, digital power +3.3V, analog power +5V, 128 pins QFP

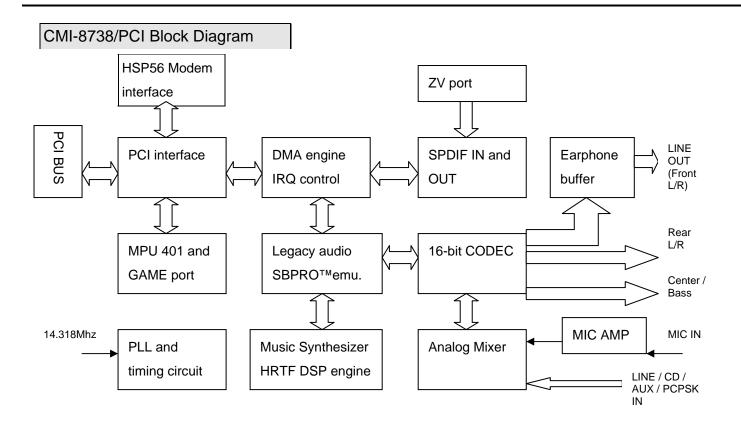

With high speed PCI V2.1 bus controller and legacy audio SBPro® DSPemulator, CMI8738 is designed for PC add-in cards and all-in-one motherboards. No external CODEC is needed in CMI8738: CMI-8738 supports the legacy audio − SBPRO™, FM emulator/DLS wavetable music synthesis, and HRTF 3D positional audio functions. Drivers support EAX®, Karaoke Key, Echo......functions. Above all CMI8738 supports PCtel® HSP56 (1789) interface.

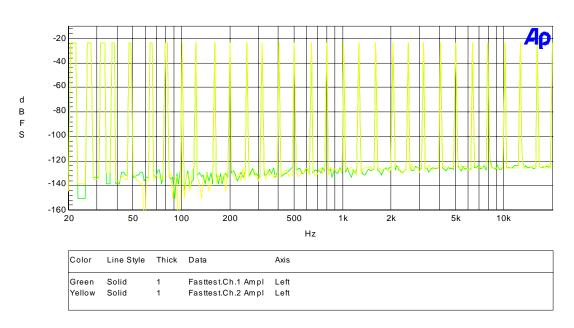

Being compatible with DirectSound™ 3D, CMI8738 meets PC99® requirements, and supports professional digital audio interface such as 16-bit SPDIF IN (0.5V ~ 5V)and OUT(44.1K and 48K format).

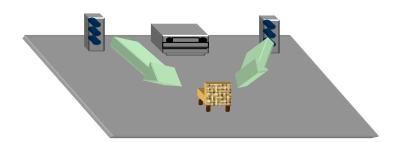

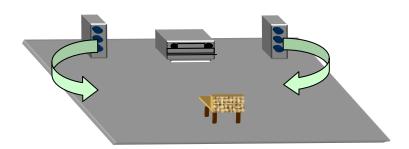

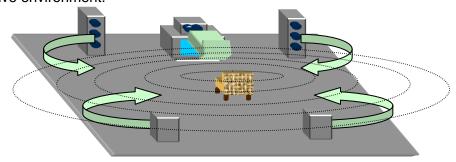

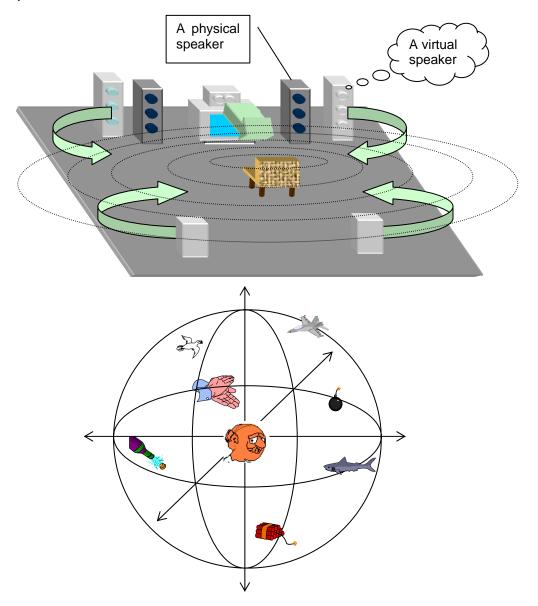

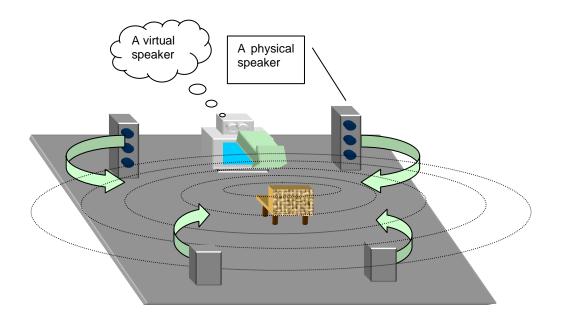

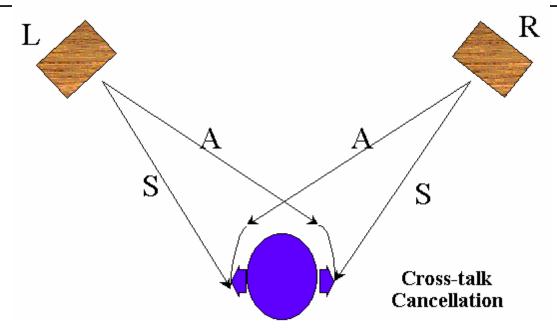

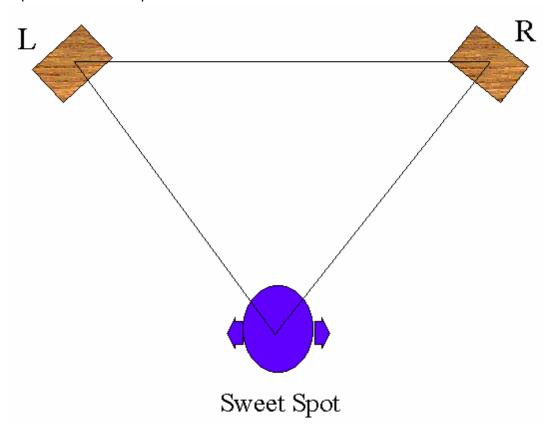

CMI8738 uses HRTF 3D extension technology to enhance traditional HRTF 3D positional audio by substituting two-speaker system by four or six - speaker one (it supports additional 2 ch 16-bit DAC to provide rear side audio and another 2 ch for subwoofer/Center). It greatly improves HRTF 3D positional audio quality and successfully removes the sweet spot limitations: users can enjoy genuine 3D audio gaming effects, and don't have to worry about the environmental confinement any more.

Being outstanding for its full audio functions, competitive price, and power management, CMI-8738 is the best choice for people seeking for optimum use of the PC applications.

# CMI8738/PCI-6CH C3DX Series Chip Function List

| Model              | MODEM | SPDIF/ZVport |

|--------------------|-------|--------------|

| CMI8738/PCI-6CH    | YES   | YES          |

| CMI8738/PCI-6CH-MX | NO    | YES          |

| CMI8738/PCI-6CH-LX | NO    | NO           |

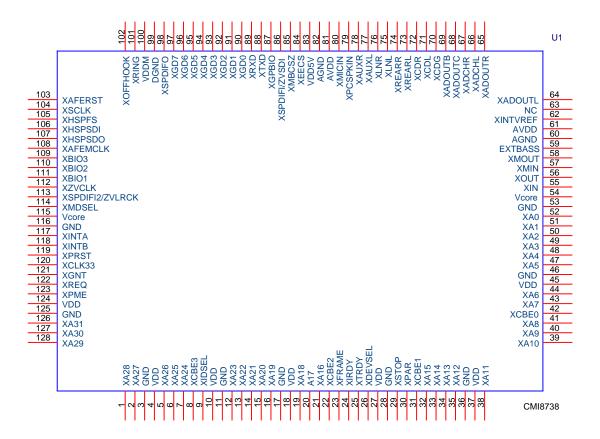

#### **PINOUT**

## CMI8738/PCI-6CH C3DX AUDIO CHIP QFP 128 PINS

## **DIGITAL PIN DESCRIPTION**

| XA31-XA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Name        | Number               | PIN  | Definition                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|------|-----------------------------------------------------------------------------------------------|

| XA31-XA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |                      | Туре |                                                                                               |

| XINTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XA31-XA0    |                      |      | PCI bus address and data lines                                                                |

| Request (optional; unused)   Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XINTA       | 117                  | 0    | Interrupt request, active-low.                                                                |

| Vertical Nation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XINTB       | 118                  | 0    | Independent Modem interrupt                                                                   |

| XCLK33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |                      |      |                                                                                               |

| XGNT   121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | I.                   | l    |                                                                                               |

| XPREQ 122 O Bus master request, tri-state output, active-low.  XPME 123 O Power Management Event pin (optional; unused)  XIDSEL 9 I ID select, active-high.  XFRAME 23 I/O Cycle frame, active-low. The bus master device is ready to transmit or receive data  XTRDY 25 I/O Target ready, active-low. The target device is ready to transmit or receive data  XTRDY 25 I/O Target ready, active-low. The target device is ready to transmit or receive data  XDEVSEL 26 I/O Device select, active-low. The target device has decoded the address of the current transaction as its own chip select range.  XSTOP 29 I/O Stop transaction, active-low. The target device request to the maste to stop the current transaction.  XPAR 30 I/O Parity. The pin indicates even pari across XA31-XA9 and XCBE3-0 for both address and data phases.  XCBE3,2,1,0 8,22,31,42 I/O Multiplexed command/byte enable These pins indicate cycle type during the address phase of a transaction.  VDD 4,10,18,27,37,45,124 +3.3V   PCI I/O power pin Hollow the selection of th |             |                      |      | PCI bus clock.                                                                                |

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | 121                  |      |                                                                                               |

| Coptional; unused)   XIDSEL   9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XREQ        | 122                  | 0    |                                                                                               |

| XFRAME         23         I/O         Cycle frame, active-low. The bus master device is ready to transmit or receive data           XTRDY         25         I/O         Target ready, active-low. The target device is ready to transmit or receive data           XDEVSEL         26         I/O         Device select, active-low. The target device has decoded the address of the current transaction as its own chip select range.           XSTOP         29         I/O         Stop transaction, active-low. The target device request to the maste to stop the current transaction.           XPAR         30         I/O         Parity. The pin indicates even pari across XA31-XA9 and XCBE3-0 for both address and data phases.           XCBE3,2,1,0         8,22,31,42         I/O         Multiplexed command/byte enable These pins indicate cycle type during the address phase of a transaction.           VDD         4,10,18,27,37,45,124         +3.3V/           VCore         54,115         +3.3V/           VCore         54,115         +3.3V/           VCOR         54,115         43.3V/           VCOR         54,115         43.3V/           VCOR         54,115         43.3V/           VCOR         54,115         60           VCOR         54,115         43.3V/           VCOR         54,115         43.3V/ <t< td=""><td>XPME</td><td>123</td><td>0</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XPME        | 123                  | 0    |                                                                                               |

| XIRDY 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XIDSEL      | 9                    | I    | ID select, active-high.                                                                       |

| master device is ready to transmit or receive data  XTRDY 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XFRAME      | 23                   | I/O  | Cycle frame, active-low.                                                                      |

| ADEVSEL  ZOE  ZOE  ZOE  ZOE  ZOE  ZOE  ZOE  Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | XIRDY       | 24                   | I/O  | Initiator ready, active-low. The bus master device is ready to transmit or receive data       |

| target device has decoded the address of the current transaction as its own chip select range.  XSTOP 29 //O Stop transaction, active-low. The target device request to the maste to stop the current transaction.  XPAR 30 //O Parity. The pin indicates even pari across XA31-XA9 and XCBE3-0 fol both address and data phases.  XCBE3,2,1,0 8,22,31,42 //O Multiplexed command/byte enable These pins indicate cycle type during the address phase of a transaction.  VDD 4,10,18,27,37,45,124 +3.3V/ PCI I/O power pin  4,10,18,27,37,45,124 +3.3V/ PCI I/O power pin  GND 3,11,17,28,36,46,53,116,125 GND Digital and PCI I/O ground  XIN 55 I 14.318Mhz crystal, or external clock input  XOUT 56 O 14.318Mhz crystal, or external clock input  XGD7-XGD4 97-94 I Game port switch input pin.  Switch D to switch A  XGD3-XGD0 93-90 //O Game port resistor input pin.  RC3 to RC0  XTXD 88 O MIDI transmit data  XRXD 89 I MIDI receive data  XSPDIFO 98 O 44.1k/48kHZ SPDIF output  XSPDIF1 86 I 44.1k/48kHZ SPDIF input  XSPDIF1 113 I Secondary SPDIF input (5v only)  XBIO3-XBIO 109-112  /O General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XTRDY       | 25                   |      |                                                                                               |

| XSTOP 29 I/O Stop transaction, active-low. The target device request to the maste to stop the current transaction.  XPAR 30 I/O Parity. The pin indicates even pari across XA31-XA9 and XCBE3-0 for both address and data phases.  XCBE3,2,1,0 8,22,31,42 I/O Multiplexed command/byte enable These pins indicate cycle type during the address phase of a transaction.  VDD 4,10,18,27,37,45,124 +3.3V/PCI I/O power pin  Vcore 54,115 +3.3V Core digital circuit power pin  GND 3,11,17,28,36,46,53,116,125 GND Digital and PCI I/O ground  XIN 55 I 14.318Mhz crystal, or external clock input  XOUT 56 O 14.318Mhz crystal, or external clock input  XGD7-XGD4 97-94 I Game port switch input pin.  XGD3-XGD0 93-90 I/O Game port resistor input pin.  RC3 to RC0  XTXD 88 O MIDI transmit data  XRXD 89 I MIDI receive data  XRXD 89 I MIDI receive data  XSPDIFO 98 O 44.1k/48kHZ SPDIF output  XSPDIF1 113 I Secondary SPDIF input (5v only)  XBIO3-XBIO 109-112 I/O General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XDEVSEL     | 26                   | I/O  | target device has decoded the address of the current transaction                              |

| XPAR 30 I/O Parity. The pin indicates even pari across XA31-XA9 and XCBE3-0 for both address and data phases.  XCBE3,2,1,0 8,22,31,42 I/O Multiplexed command/byte enable These pins indicate cycle type during the address phase of a transaction.  VDD 4,10,18,27,37,45,124 +3.3V/ +5V  Vcore 54,115 +3.3V Core digital circuit power pin  GND 3,11,17,28,36,46,53,116,125 GND Digital and PCI I/O ground  XIN 55 I 14.318Mhz crystal, or external clock input  XOUT 56 O 14.318Mhz crystal  XGD7-XGD4 97-94 I Game port switch input pin. Switch D to switch A  XGD3-XGD0 93-90 I/O Game port resistor input pin. RC3 to RC0  XTXD 88 O MIDI transmit data  XRXD 89 I MIDI receive data  XSPDIFO 98 O 44.1k/48kHZ SPDIF output  XSPDIF1 86 I 44.1k/48kHZ SPDIF input  XSPDIF2 113 I Secondary SPDIF input (5v only)  XBIO3-XBIO 109-112 I/O General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | XSTOP       | 29                   | I/O  | Stop transaction, active-low. The target device request to the master                         |

| XCBE3,2,1,0 8,22,31,42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XPAR        | 30                   | I/O  | Parity. The pin indicates even parity across XA31-XA9 and XCBE3-0 for                         |

| VDD         4,10,18,27,37,45,124         +3.3V/<br>+5V         PCI I/O power pin           Vcore         54,115         +3.3V         Core digital circuit power pin           GND         3,11,17,28,36,46,53,116,125         GND         Digital and PCI I/O ground           XIN         55         I         14.318Mhz crystal, or external clock input           XOUT         56         O         14.318Mhz crystal           XGD7-XGD4         97-94         I         Game port switch input pin.           XGD3-XGD0         93-90         I/O         Game port resistor input pin.           XTXD         88         O         MIDI transmit data           XRXD         89         I         MIDI receive data           XSPDIFO         98         O         44.1k/48kHZ SPDIF output           XSPDIFI         86         I         44.1k/48kHZ SPDIF input           XSPDIF2         113         I         Secondary SPDIF input (5v only)           XBIO3-XBIO         109-112         I/O         General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | XCBE3,2,1,0 | 8,22,31,42           | I/O  | Multiplexed command/byte enable. These pins indicate cycle type during the address phase of a |

| Vcore 54,115 +3.3V Core digital circuit power pin GND 3,11,17,28,36,46,53,116,125 GND Digital and PCI I/O ground XIN 55 I 14.318Mhz crystal, or external clock input XOUT 56 O 14.318Mhz crystal XGD7-XGD4 97-94 I Game port switch input pin. Switch D to switch A XGD3-XGD0 93-90 I/O Game port resistor input pin. RC3 to RC0 XTXD 88 O MIDI transmit data XRXD 89 I MIDI receive data XSPDIFO 98 O 44.1k/48kHZ SPDIF output XSPDIFI 86 I 44.1k/48kHZ SPDIF input XSPDIF2 113 I Secondary SPDIF input (5v only) XBIO3-XBIO 109-112 I/O General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VDD         | 4,10,18,27,37,45,124 |      |                                                                                               |

| GND         3,11,17,28,36,46,53,116,125         GND         Digital and PCI I/O ground           XIN         55         I         14.318Mhz crystal, or external clock input           XOUT         56         O         14.318Mhz crystal           XGD7-XGD4         97-94         I         Game port switch input pin. Switch D to switch A           XGD3-XGD0         93-90         I/O         Game port resistor input pin. RC3 to RC0           XTXD         88         O         MIDI transmit data           XRXD         89         I         MIDI receive data           XSPDIFO         98         O         44.1k/48kHZ SPDIF output           XSPDIFI         86         I         44.1k/48kHZ SPDIF input           XSPDIF2         113         I         Secondary SPDIF input (5v only)           XBIO3-XBIO         109-112         I/O         General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Vcore       | 54.115               |      | Core digital circuit power pin                                                                |

| XIN   55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | ·                    |      |                                                                                               |

| XGD7-XGD4         97-94         I         Game port switch input pin. Switch D to switch A           XGD3-XGD0         93-90         I/O         Game port resistor input pin. RC3 to RC0           XTXD         88         O         MIDI transmit data           XRXD         89         I         MIDI receive data           XSPDIFO         98         O         44.1k/48kHZ SPDIF output           XSPDIFI         86         I         44.1k/48kHZ SPDIF input           XSPDIF2         113         I         Secondary SPDIF input (5v only)           XBIO3-XBIO         109-112         I/O         General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |                      | I    | 14.318Mhz crystal, or external clock                                                          |

| Switch D to switch A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | I.                   | 0    |                                                                                               |

| RC3 to RC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XGD7-XGD4   | 97-94                | I    |                                                                                               |

| XTXD         88         O         MIDI transmit data           XRXD         89         I         MIDI receive data           XSPDIFO         98         O         44.1k/48kHZ SPDIF output           XSPDIFI         86         I         44.1k/48kHZ SPDIF input           XSPDIF2         113         I         Secondary SPDIF input (5v only)           XBIO3-XBIO         109-112         I/O         General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XGD3-XGD0   | 93-90                | I/O  | RC3 to RC0                                                                                    |

| XSPDIFO         98         O         44.1k/48kHZ SPDIF output           XSPDIFI         86         I         44.1k/48kHZ SPDIF input           XSPDIF2         113         I         Secondary SPDIF input (5v only)           XBIO3-XBIO         109-112         I/O         General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | XTXD        | 88                   | 0    | MIDI transmit data                                                                            |

| XSPDIFI 86 I 44.1k/48kHZ SPDIF input XSPDIF2 113 I Secondary SPDIF input (5v only) XBIO3-XBIO 109-112 I/O General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | XRXD        | 89                   | I    | MIDI receive data                                                                             |

| XSPDIFI 86 I 44.1k/48kHZ SPDIF input XSPDIF2 113 I Secondary SPDIF input (5v only) XBIO3-XBIO 0 I/O General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XSPDIFO     | 98                   | 0    | 44.1k/48kHZ SPDIF output                                                                      |

| XSPDIF2 113 I Secondary SPDIF input (5v only) XBIO3-XBIO 109-112 I/O General purpose I/O 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XSPDIFI     | 86                   | I    | 44.1k/48kHZ SPDIF input                                                                       |

| XBIO3-XBIO 109-112 I/O General purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | 113                  | I    |                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XBIO3-XBIO  |                      | I/O  |                                                                                               |

| TJV   FOI I/O DUWGI DIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VDD5V       | 83                   | +5V  | PCI I/O power pin                                                                             |

#### **PIN DESCRIPTION**

| VDDM     | 100 | +3.3V/<br>+5V | PCI I/O power pin                      |

|----------|-----|---------------|----------------------------------------|

| DGND     | 99  | GND           | PCI I/O ground                         |

| XEECS    | 84  | 0             | EEPROM chip select                     |

| XGPBIO   | 87  | 0             | General purpose I/O pin (default=high) |

| XMDSEL   | 114 | I             | Modem device enable(high:enable)       |

| XRING    | 101 | I             | Ring detection input                   |

| XOFFHOOK | 102 | 0             | Off-hook control output                |

| XAFERST  | 103 | 0             | Reset signal for MODEM DAA             |

| XHSPFS   | 105 | 0             | DAA frame SYNC                         |

| XHSPSDI  | 106 | I             | DAA data input                         |

| XHSPSDO  | 107 | 0             | DAA data output                        |

| XAFEMCLK | 108 | 0             | DAA master clock                       |

| XSCLK    | 104 | 0             | DAA serial clock                       |

| XMOUT    | 58  | 0             | MODEM crystal output (18.432MHz)       |

| XMIN     | 57  | I             | MODEM crystal input                    |

| XMBCSZ   | 85  | ı             | Audio chip select (low:enable)         |

| ZVCLK    | 112 | ı             | ZV port clock                          |

| ZVLRCK   | 113 | I             | ZV port LR channel clock               |

| ZVSDI    | 86  | ı             | ZV port data input                     |

Remark: All PCI interface I/O pins are 3.3V signal and 5V tolerance.

## **ANALOG PIN DESCRIPTION**

| AVDD      | 61,81    | +5V  | Analog power                                  |

|-----------|----------|------|-----------------------------------------------|

| AGND      | 60,82    | GND  | Analog ground                                 |

| XADOUTL-R | 64,65    | AI/O | Line out (front channels L/R)                 |

| XADCHL-R  | 66,67    | AI/O | ADC sample hold pin                           |

| XADOUTC   | 68       | AI/O | Center channel output                         |

| XADOUTB   | 69       | AI/O | Bass channel output                           |

| XINTVERF  | 62       | AO   | Internal reference voltage (for testing only) |

| NC        | 63       | -    | Not connect                                   |

| XCDL-R    | 71,72,70 | Al   | CD audio differential input                   |

| XCDGND    |          |      |                                               |

| XLNL-R    | 75,76    | Al   | Line in or Rear channels out                  |

| XAUXL-R   | 77,78    | Al   | Aux. Line in                                  |

| XPCSPKIN  | 79       | Al   | PC beep signal or Mono in                     |

| XMICIN    | 80       | Al   | Microphone in                                 |

| XREARL-R  | 73,74    | AO   | Rear channels L/R out                         |

| EXTBASS   | 59       | Al   | External bass channel input                   |

|           |          |      |                                               |

## **POWER ON CONFIGURATION PIN**

| Name  | Number | Definition                                                      |

|-------|--------|-----------------------------------------------------------------|

| XEECS | 84     | 4/6 channel selection. For 4 or 6 channel purpose selection.    |

|       |        | This pin tie high mean 6ch, pull down compatible with 4ch chip. |